Escolar Documentos

Profissional Documentos

Cultura Documentos

Answer-Books.: Your Answer Will Be Valued As A Whole

Enviado por

yogesh_b_kTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Answer-Books.: Your Answer Will Be Valued As A Whole

Enviado por

yogesh_b_kDireitos autorais:

Formatos disponíveis

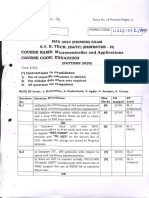

[Total No.

of Questions: 12]

[Total No. o f Pr i n t ed Pag es : 3]

UNIVERSITY OF PUNE [4364]-534 B. E. (ELECTRICAL)(Sem II) Examination - 2013 VLSI DESIGN (Elective - III) (403150) (2008 Course) [Time: 3 Hours] [Max. Marks: 100]

Instructions: 1 Answers to the two sections should be written in separate

answer-books.

2 Black figures to the right indicate full marks. 3 Your answer will be valued as a whole 4 Neat diagrams must be drawn wherever necessary. 5 Use of logarithmic tables, slide rule, Mollier charts, electronic

pocket calculator and steam tables is allowed.

6 Assume suitable data, if necessary.

Q.1

SECTION I Draw state diagram to detect 1111 sequence using mealy and moore model.

Draw the timing diagram of MOD 7 Asynchronous counter and MOD 5 Synchronous counter.

10

OR Q.2 A Implement AND, OR NAND, NOR gate using 4 : 1 multiplexer. B Draw state transition table MOD 6 counter using T flipflop. Also implement its Design diagram. 10 8

Q. 3

A B

Explain EDA tool Design flow using a Flow chart Define the terms : i) ii) iii) iv) Concurrent statement Sub program Component Configuration OR

8 8

Q. 4

State and explain any 4 types of data types & data objects used in VHDL.

Write VHDL code for 8:1 Demultiplexer & also draw its internal circuit diagram.

Q. 5

What do you mean by sub-program overloading? Explain 8 with example using VDHL code.

Write VDHL code for J-K flip-flop using process statement. OR

Q. 6

Which are the nine different values of std-logic? Also write entity to create an array of 8x8 with data types as std-logic vector.

What do you mean by configuration? Explain with an example in VHDL code

SECTION II Q. 7 A Explain voltage transfer characteristics of CMOS inverter B Explain the construction of MOSFET device. 8 8

OR Q. 8 A Define the concept of 1.FAN-IN, FAN-OUT figure of merit and Noise margin w.r.t. CMOS. Also state its standard values. B State standard device specifications of MOSFET. 8 8

Q. 9

A B

Draw and explain Architecture of FPGA. Write a note on simulation and Synthesis. OR

8 8

Q. 10

A B

Differentiate PAL and PLA Draw and explain standard Architecture of CPLD

8 8

Q. 11

A B

Write VHDL code for 4 bit Adder. Write VHDL code for 8 x 8 RAM. OR

8 10

Q. 12

Draw block diagram of ALU & also write its VHDL code

Write VDHL code for 4 bit shift register with parallel load and serial right shift output

10

Você também pode gostar

- Sample-Question-Paper - Digital Electronics and Microcontroller ApplicationsDocumento5 páginasSample-Question-Paper - Digital Electronics and Microcontroller ApplicationsAbhishek ManeAinda não há avaliações

- Digital ElectronicsDocumento7 páginasDigital ElectronicsAlakaaa PromodAinda não há avaliações

- T.E. (E&TC) : Time:3 Hours) (Max. Marks:100 Instructions To The CandidatesDocumento3 páginasT.E. (E&TC) : Time:3 Hours) (Max. Marks:100 Instructions To The Candidatesaniruddhaphatak93Ainda não há avaliações

- Dem QB Ut-1 110120Documento2 páginasDem QB Ut-1 110120ABHI THORATAinda não há avaliações

- Principles of Digital Techniques On Web PDFDocumento5 páginasPrinciples of Digital Techniques On Web PDFmdwalunjkar3095Ainda não há avaliações

- Analog and Digital CircuitsDocumento2 páginasAnalog and Digital CircuitsNipun JainAinda não há avaliações

- Dec 2009Documento8 páginasDec 2009Viswa ChaitanyaAinda não há avaliações

- Me 1Documento436 páginasMe 1Akshay Mane0% (1)

- MicrocontrollerDocumento5 páginasMicrocontrollerRohan RdsAinda não há avaliações

- Microcontoller and Applications-Sample-Question-Paper (Msbte-Study-Resources)Documento5 páginasMicrocontoller and Applications-Sample-Question-Paper (Msbte-Study-Resources)surajmore2368Ainda não há avaliações

- 07a80405 DigitaldesignthroughverilogDocumento4 páginas07a80405 DigitaldesignthroughverilogSharanya ThirichinapalliAinda não há avaliações

- Deld QB EndsemDocumento4 páginasDeld QB EndsemUV New MoviesAinda não há avaliações

- 9A04706 Digital Design Through Verilog HDL PDFDocumento4 páginas9A04706 Digital Design Through Verilog HDL PDFTayyabunnissa BegumAinda não há avaliações

- M.E. (VLSI & Embedded System) : Asic Design and Modelling (2008 Course)Documento9 páginasM.E. (VLSI & Embedded System) : Asic Design and Modelling (2008 Course)Manu SeaAinda não há avaliações

- DEC Lab Experiments - 2017aDocumento5 páginasDEC Lab Experiments - 2017aManjeet SinghAinda não há avaliações

- Digital Fundamentals BE SEM 3Documento2 páginasDigital Fundamentals BE SEM 3Dhwanil BhattAinda não há avaliações

- Sample Question Paper Digital Techniques PDFDocumento5 páginasSample Question Paper Digital Techniques PDFAshutosh PatilAinda não há avaliações

- Scheme - I Sample Question PaperDocumento4 páginasScheme - I Sample Question PaperNaresh KumarAinda não há avaliações

- DLDM Question BankDocumento8 páginasDLDM Question BankMayur PatilAinda não há avaliações

- Digital Design Through Verilog HDLDocumento4 páginasDigital Design Through Verilog HDLmukesh_sonuAinda não há avaliações

- Digital Electronics Question BankDocumento6 páginasDigital Electronics Question BankReshna ShowkathAinda não há avaliações

- Microcontroller App UnipuneTEElecDocumento3 páginasMicrocontroller App UnipuneTEElecjupiteroxAinda não há avaliações

- Microprocessors and InterfacingDocumento4 páginasMicroprocessors and InterfacingVenkatesh RachaAinda não há avaliações

- EE6301-Digital Logic Circuits QBDocumento7 páginasEE6301-Digital Logic Circuits QBariv2009Ainda não há avaliações

- 9A04401 Switching Theory and Logic DesignDocumento4 páginas9A04401 Switching Theory and Logic DesignsivabharathamurthyAinda não há avaliações

- TE 2003&2008 PatternDocumento623 páginasTE 2003&2008 PatternAshashwatmeAinda não há avaliações

- Digital Logic Assignment 3Documento2 páginasDigital Logic Assignment 3nishu chaudharyAinda não há avaliações

- Questions Combinational CircuitDocumento2 páginasQuestions Combinational CircuitVigneswaran VigneshAinda não há avaliações

- Jntu Vlsi Systems DesignDocumento5 páginasJntu Vlsi Systems Design9010469071Ainda não há avaliações

- Scheme - I Sample Question Paper: I. Instruction Set Ii. Applications Iii. Memory Organization. I/O CompatibilityDocumento5 páginasScheme - I Sample Question Paper: I. Instruction Set Ii. Applications Iii. Memory Organization. I/O CompatibilityC052 Diksha PawarAinda não há avaliações

- FY Btech - EX - Electrical & Electronics Engineering - SEM - I - JAN 2023Documento3 páginasFY Btech - EX - Electrical & Electronics Engineering - SEM - I - JAN 2023kumbhalkarvalay8Ainda não há avaliações

- Lab08 Async CountersDocumento6 páginasLab08 Async CountersAlasnuyoAinda não há avaliações

- BTINC401 Digital ElectronicsDocumento2 páginasBTINC401 Digital ElectronicsÑaýaň ŇăwğhårēAinda não há avaliações

- 3 Hours / 100 Marks: Seat NoDocumento4 páginas3 Hours / 100 Marks: Seat NoSiddhesh P GhadigaonkarAinda não há avaliações

- Ae Paper GtuDocumento9 páginasAe Paper GtuMehta HarshAinda não há avaliações

- Lres 53snsDocumento2 páginasLres 53snsSCORPION GAMINGAinda não há avaliações

- Embedded Systems 9168 - Sample Paper of MSBTE For Sixth Semester Final Year Computer Engineering Diploma (80 Marks)Documento2 páginasEmbedded Systems 9168 - Sample Paper of MSBTE For Sixth Semester Final Year Computer Engineering Diploma (80 Marks)Sanjay DudaniAinda não há avaliações

- Aprilmay 2007Documento7 páginasAprilmay 2007Viswa ChaitanyaAinda não há avaliações

- Question Bank: Ec6302 Digital ElectronicsDocumento14 páginasQuestion Bank: Ec6302 Digital ElectronicsBarry SmithAinda não há avaliações

- Adst Jan2010 NewDocumento4 páginasAdst Jan2010 NewVijay GurusamyAinda não há avaliações

- Question Bank For DLCDocumento8 páginasQuestion Bank For DLCAvina AshAinda não há avaliações

- Microcontroller and Applications Sem II Pattern 2020 Endsem Exam May 2023 - ETCDocumento2 páginasMicrocontroller and Applications Sem II Pattern 2020 Endsem Exam May 2023 - ETCradhika.22210203Ainda não há avaliações

- Microcontroller and Applications Sem II Pattern 2020 Endsem Exam May 2023 - ETCDocumento2 páginasMicrocontroller and Applications Sem II Pattern 2020 Endsem Exam May 2023 - ETCradhika.22210203Ainda não há avaliações

- Digital Electronics QBDocumento7 páginasDigital Electronics QBvinaytmkAinda não há avaliações

- Me2255 Electronics and MicroprocDocumento2 páginasMe2255 Electronics and MicroprocBalaji PalanisamyAinda não há avaliações

- MODULE - Wise Question - 2022-ADE-CODocumento4 páginasMODULE - Wise Question - 2022-ADE-COvinayvinayakars313Ainda não há avaliações

- r05410207 Vlsi DesignDocumento7 páginasr05410207 Vlsi Design9010469071Ainda não há avaliações

- 9A04306 Digital Logic DesignDocumento4 páginas9A04306 Digital Logic DesignsivabharathamurthyAinda não há avaliações

- CS 2202 - Digital Principles and Systems DesignDocumento3 páginasCS 2202 - Digital Principles and Systems DesignDhilip PrabakaranAinda não há avaliações

- Microprocessor & Its Interfacing - Ic-403Documento3 páginasMicroprocessor & Its Interfacing - Ic-403Shreemaye DasAinda não há avaliações

- r05321404 Linear and Digital Ic ApplicationsDocumento7 páginasr05321404 Linear and Digital Ic ApplicationsSRINIVASA RAO GANTAAinda não há avaliações

- Ect206-Qp June21Documento2 páginasEct206-Qp June21Rajeena VasudevanAinda não há avaliações

- Gujarat Technological UniversityDocumento1 páginaGujarat Technological UniversityRenieAinda não há avaliações

- DLCDocumento1 páginaDLCrjvenkiAinda não há avaliações

- QP Eee 22 May2010 LdicaDocumento6 páginasQP Eee 22 May2010 LdicaHari PrasadAinda não há avaliações

- EC2203 U Q BankDocumento12 páginasEC2203 U Q Bankvlsi_satheeshAinda não há avaliações

- 21 - 2011 - Dec - R09 - STLDDocumento8 páginas21 - 2011 - Dec - R09 - STLDvasuvlsiAinda não há avaliações

- 9A04504 Digital IC ApplicationsDocumento4 páginas9A04504 Digital IC ApplicationssivabharathamurthyAinda não há avaliações

- Vhdland Digital: The Product Terms Are AllocatedDocumento4 páginasVhdland Digital: The Product Terms Are AllocatedWho KnowsAinda não há avaliações

- Programmable Logic Controllers: A Practical Approach to IEC 61131-3 using CoDeSysNo EverandProgrammable Logic Controllers: A Practical Approach to IEC 61131-3 using CoDeSysAinda não há avaliações

- Department of Mechanical Engineering Mechanical Sandwich: Program Educational Objectives (Peos)Documento1 páginaDepartment of Mechanical Engineering Mechanical Sandwich: Program Educational Objectives (Peos)yogesh_b_kAinda não há avaliações

- 4363 115 ConmDocumento5 páginas4363 115 Conmyogesh_b_kAinda não há avaliações

- 4363 120 RacDocumento8 páginas4363 120 Racyogesh_b_kAinda não há avaliações

- 4363 119 MechatronicsDocumento4 páginas4363 119 Mechatronicsyogesh_b_kAinda não há avaliações

- 4363 116 Machine Design IIDocumento7 páginas4363 116 Machine Design IIyogesh_b_kAinda não há avaliações

- 4363 117 Metrology QCDocumento3 páginas4363 117 Metrology QCyogesh_b_kAinda não há avaliações

- 4363 118 Turbo MachinesDocumento7 páginas4363 118 Turbo Machinesyogesh_b_kAinda não há avaliações

- 4363 114 IetmDocumento3 páginas4363 114 Ietmyogesh_b_kAinda não há avaliações

- 4363 126 Mechatronics SWDocumento3 páginas4363 126 Mechatronics SWyogesh_b_kAinda não há avaliações

- 4363 111 Machine Design IDocumento6 páginas4363 111 Machine Design Iyogesh_b_k100% (2)

- 4363 112 Heat TransferDocumento6 páginas4363 112 Heat Transferyogesh_b_kAinda não há avaliações

- 4363 113 Tom IiDocumento7 páginas4363 113 Tom Iiyogesh_b_kAinda não há avaliações

- 4364 536 DSPDocumento4 páginas4364 536 DSPyogesh_b_kAinda não há avaliações

- Instructions:: Answer-BooksDocumento2 páginasInstructions:: Answer-Booksyogesh_b_kAinda não há avaliações

- Instructions: Separate Answer-Books.: Section IDocumento2 páginasInstructions: Separate Answer-Books.: Section Iyogesh_b_kAinda não há avaliações

- 4364 529 Embedded SystemDocumento2 páginas4364 529 Embedded Systemyogesh_b_kAinda não há avaliações

- 4364 532 SwitchgearDocumento3 páginas4364 532 Switchgearyogesh_b_kAinda não há avaliações

- 4364 535 HighVoltageDocumento4 páginas4364 535 HighVoltageyogesh_b_kAinda não há avaliações

- 4364 533 IdcDocumento3 páginas4364 533 Idcyogesh_b_kAinda não há avaliações

- 4364 530 EhvDocumento5 páginas4364 530 Ehvyogesh_b_kAinda não há avaliações

- 4364 526 IlluminationDocumento2 páginas4364 526 Illuminationyogesh_b_kAinda não há avaliações

- Restrueturing and Deregulation (Course 2008) (Total No. of Questions:12) (Total No. Printed Pages: 2)Documento2 páginasRestrueturing and Deregulation (Course 2008) (Total No. of Questions:12) (Total No. Printed Pages: 2)yogesh_b_kAinda não há avaliações

- 4364 527 Project ManagementDocumento2 páginas4364 527 Project Managementyogesh_b_kAinda não há avaliações

- 4364 524 RoboticsDocumento2 páginas4364 524 Roboticsyogesh_b_kAinda não há avaliações

- 4364 522 PsocDocumento3 páginas4364 522 Psocyogesh_b_kAinda não há avaliações

- Instructions: Q7 or Q8, Q9 or Q10, Q11 or Q12 From Section II. Separate Answer-BooksDocumento3 páginasInstructions: Q7 or Q8, Q9 or Q10, Q11 or Q12 From Section II. Separate Answer-Booksyogesh_b_kAinda não há avaliações

- 4364 523 CsiiDocumento4 páginas4364 523 Csiiyogesh_b_kAinda não há avaliações

- 4364 521 PLC ScadaDocumento3 páginas4364 521 PLC Scadayogesh_b_kAinda não há avaliações

- (Total No. of Questions: 12) (Total No. of Prin Te D Pages: 2)Documento2 páginas(Total No. of Questions: 12) (Total No. of Prin Te D Pages: 2)yogesh_b_kAinda não há avaliações