Escolar Documentos

Profissional Documentos

Cultura Documentos

Pulse and Digital Circuits PDF

Enviado por

rocky4bestTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Pulse and Digital Circuits PDF

Enviado por

rocky4bestDireitos autorais:

Formatos disponíveis

J

N

T

U

W

O

R

L

D

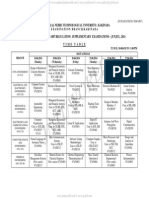

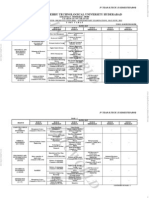

Code No: RR210202

JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY, HYDERABAD

B.Tech II Year I Semester Examinations, May/June-2013

Pulse and Digital Circuits

(Common to EEE, ECE)

Time: 3 hours Max. Marks: 80

Answer any five questions

All questions carry equal marks

- - -

1.a) Prove that an RC low pass circuit behaves as a good integrator if RC >15T where

T is the Period of the input sinusoid E

m

sint.

b) Write about Attenuators. [8+8]

2.a) With a neat diagram explain about Emitter- coupled Clipper.

b) Write about Diode comparator and its applications in pulse time modulation.

[8+8]

3.a) With appropriate diagrams explain about Transistor switching times.

b) Write about Saturation parameters of Transistor and their variation with

temperature. [8+8]

4. Design a bistable multivibrator with following specifications

I

CC

= I

BB

= 12I, I

C

(sot) = 6mA, b

PL

(minimum) = 25, Maximum trigger

frequency = 25KHz. [16]

5.a) Discuss about Transistor Bootstrap time base generators.

b) A Transistor Bootstrap Ramp generator is to produce 15V, 5ms output to a 2K

load resistor the ramp is to be linear with in 2%. Design a suitable circuit using

I

CC

= 22V, -I

LL

= -22V and Transistor with b

PL

(min) = 25. The input pulse has

an amplitude of -5V, pulse width=5ms and space width = 2.5ms. [8+8]

6.a) Write about frequency division by a RC controlled astable blocking oscillator.

b) Explain about (a) Phase delay (b) Phase Jitter. [8+8]

7.a) Derive expression for control voltages and their maximum and minimum values

for a four diode sampling gate.

b) Explain about a six diode sampling gate and mention its values specification.

[8+8]

8.a) With a neat circuit diagram and truth table explain the working of a NOT gate.

b) Draw the logic diagram of the following gates using AOI logic. (i) XOR

(ii) XNOR gates. [8+8]

---oo0oo---

RR

www.jntuworld.com || www.android.jntuworld.com || www.jwjobs.net || www.android.jwjobs.net

www.jntuworld.com || www.jwjobs.net

Você também pode gostar

- JNTU Hyderabad B.Tech II Year I Semester Examinations for Pulse and Digital CircuitsDocumento1 páginaJNTU Hyderabad B.Tech II Year I Semester Examinations for Pulse and Digital CircuitsRajan GantaAinda não há avaliações

- Pulse and Digital CircuitsDocumento8 páginasPulse and Digital CircuitsLalith KumarAinda não há avaliações

- Aprilmay 2009Documento8 páginasAprilmay 2009Viswa ChaitanyaAinda não há avaliações

- Aprilmay 2007Documento7 páginasAprilmay 2007Viswa ChaitanyaAinda não há avaliações

- Pulse and Digital CircuitsDocumento8 páginasPulse and Digital CircuitsSatish SmartAinda não há avaliações

- Linear and Dig Italic Applications Jntu Model Paper WWW Student Yogi Com 100113195343 Phpapp02Documento8 páginasLinear and Dig Italic Applications Jntu Model Paper WWW Student Yogi Com 100113195343 Phpapp02Ranjith ReddyAinda não há avaliações

- Pulse and Digital CircuitsDocumento8 páginasPulse and Digital Circuitssravya sriAinda não há avaliações

- Jntuworld: Electrical and Electronics EngineeringDocumento30 páginasJntuworld: Electrical and Electronics EngineeringRajeev BujjiAinda não há avaliações

- DC Machine Theory and Transformer PrinciplesDocumento32 páginasDC Machine Theory and Transformer PrinciplesPolireddi Gopala KrishnaAinda não há avaliações

- rr310404 Linear Ic ApplicationsDocumento8 páginasrr310404 Linear Ic ApplicationsSRINIVASA RAO GANTAAinda não há avaliações

- Set No. 1: CEO CBODocumento9 páginasSet No. 1: CEO CBO29viswa12Ainda não há avaliações

- Edc 4Documento10 páginasEdc 429viswa12Ainda não há avaliações

- 07a81904 ElectronicsmeasurementsandinstrumentationDocumento7 páginas07a81904 ElectronicsmeasurementsandinstrumentationSharanya ThirichinapalliAinda não há avaliações

- Jntuworld: R07 Set No. 2Documento5 páginasJntuworld: R07 Set No. 2Kasarla Shiva SjAinda não há avaliações

- QP Eee 22 May2010 LdicaDocumento6 páginasQP Eee 22 May2010 LdicaHari PrasadAinda não há avaliações

- Rr310404 Linear Ic ApplicationsDocumento8 páginasRr310404 Linear Ic ApplicationsSrinivasa Rao GAinda não há avaliações

- r05221101 Pulse and Digital CircuitsDocumento9 páginasr05221101 Pulse and Digital CircuitssridiviAinda não há avaliações

- R7220203 Linear Digital IC ApplicationsDocumento2 páginasR7220203 Linear Digital IC ApplicationssivabharathamurthyAinda não há avaliações

- rr102306 Electrical and Electronics EngineeringDocumento1 páginarr102306 Electrical and Electronics EngineeringsivabharathamurthyAinda não há avaliações

- r5210203 Pulse and Digital CircuitsDocumento1 páginar5210203 Pulse and Digital CircuitssivabharathamurthyAinda não há avaliações

- r05321404 Linear and Digital Ic ApplicationsDocumento7 páginasr05321404 Linear and Digital Ic ApplicationsSRINIVASA RAO GANTAAinda não há avaliações

- Edc 7Documento8 páginasEdc 729viswa12100% (1)

- r7210203 Pulse and Digital CircuitsDocumento1 páginar7210203 Pulse and Digital CircuitssivabharathamurthyAinda não há avaliações

- r05221002 Linear Ic ApplicationsDocumento7 páginasr05221002 Linear Ic ApplicationsSRINIVASA RAO GANTAAinda não há avaliações

- 2015: 1) 2) 3) 4) : A) : B) C) D) : A) I) Ii) Iii) B) C) : Ai/Alog Circuits-IDocumento3 páginas2015: 1) 2) 3) 4) : A) : B) C) D) : A) I) Ii) Iii) B) C) : Ai/Alog Circuits-ISaurabh BhiseAinda não há avaliações

- SE 2008 Electronics E&TCDocumento63 páginasSE 2008 Electronics E&TCManish kumar 50Ainda não há avaliações

- Ec05497 Pulse and Digital CircuitsDocumento1 páginaEc05497 Pulse and Digital CircuitssivabharathamurthyAinda não há avaliações

- Pulse and Digital Circuits NotesDocumento8 páginasPulse and Digital Circuits NotesLavanya_123Ainda não há avaliações

- Answer Any Two Full Questions, Each Carries 15 Marks.: Reg No.: - NameDocumento2 páginasAnswer Any Two Full Questions, Each Carries 15 Marks.: Reg No.: - Namesheena mAinda não há avaliações

- Linear and Digital Ic Applications RRDocumento8 páginasLinear and Digital Ic Applications RRNizam Institute of Engineering and Technology LibraryAinda não há avaliações

- Graph Sheets May Be Supplied On Demand: Page 1 of 2Documento2 páginasGraph Sheets May Be Supplied On Demand: Page 1 of 2sarang acAinda não há avaliações

- Digital Pulse and Circuits Exam QuestionsDocumento8 páginasDigital Pulse and Circuits Exam QuestionsKota divyasreeAinda não há avaliações

- Microwave EngineeringDocumento5 páginasMicrowave EngineeringHarikrishna KhariduAinda não há avaliações

- Code No: V0421/R07 II B.Tech II Semester, Regular Examinations, Apr – 2011 PULSE AND DIGITAL CIRCUITS (Com. to ECE, BME, ECCDocumento4 páginasCode No: V0421/R07 II B.Tech II Semester, Regular Examinations, Apr – 2011 PULSE AND DIGITAL CIRCUITS (Com. to ECE, BME, ECCLavanya_123Ainda não há avaliações

- Dec 2009Documento8 páginasDec 2009Viswa ChaitanyaAinda não há avaliações

- rr12302 Electrical and Electronics EngineeringDocumento12 páginasrr12302 Electrical and Electronics EngineeringSRINIVASA RAO GANTAAinda não há avaliações

- Model Question PaperDocumento1 páginaModel Question Paperapi-279049687Ainda não há avaliações

- InstrumentationDocumento7 páginasInstrumentationNagaValliAinda não há avaliações

- JNTU Instrumentation Exam QuestionsDocumento4 páginasJNTU Instrumentation Exam QuestionsDon RahulAinda não há avaliações

- r059210202 Pulse and Digital CircuitsDocumento11 páginasr059210202 Pulse and Digital CircuitsSrinivasa Rao GAinda não há avaliações

- PDC 1Documento3 páginasPDC 1Sravya LakshmiAinda não há avaliações

- FY Btech - EX - Electrical & Electronics Engineering - SEM - I - JAN 2023Documento3 páginasFY Btech - EX - Electrical & Electronics Engineering - SEM - I - JAN 2023kumbhalkarvalay8Ainda não há avaliações

- Power Electronics - Mumbai Univ - Sem 8 ElexDocumento8 páginasPower Electronics - Mumbai Univ - Sem 8 Elex111ashwinAinda não há avaliações

- r05310401 Linear Ic ApplicationsDocumento8 páginasr05310401 Linear Ic ApplicationsSrinivasa Rao GAinda não há avaliações

- KTU EDC Previous Question PapersDocumento12 páginasKTU EDC Previous Question PapersVarun DevAinda não há avaliações

- ADE March 2021Documento1 páginaADE March 2021Roger ZoeAinda não há avaliações

- R5210203 Pulse and Digital CircuitsDocumento1 páginaR5210203 Pulse and Digital CircuitssivabharathamurthyAinda não há avaliações

- r05320204 InstrumentationDocumento6 páginasr05320204 InstrumentationMounikaManuAinda não há avaliações

- r05410207 Vlsi DesignDocumento7 páginasr05410207 Vlsi Design9010469071Ainda não há avaliações

- JNTUH Usedpapers March 2022: C E CODocumento1 páginaJNTUH Usedpapers March 2022: C E COARUN LinuxAinda não há avaliações

- r05220202 Linear and Digital Ic ApplicationDocumento4 páginasr05220202 Linear and Digital Ic ApplicationSRINIVASA RAO GANTAAinda não há avaliações

- NR-221103 - Digital Circuits Design and ApplictionDocumento5 páginasNR-221103 - Digital Circuits Design and ApplictionSrinivasa Rao G100% (1)

- rr312202 Industrial ElectronicsDocumento5 páginasrr312202 Industrial ElectronicsSRINIVASA RAO GANTAAinda não há avaliações

- Power System Transient Analysis: Theory and Practice using Simulation Programs (ATP-EMTP)No EverandPower System Transient Analysis: Theory and Practice using Simulation Programs (ATP-EMTP)Ainda não há avaliações

- Heterojunction Bipolar Transistors for Circuit Design: Microwave Modeling and Parameter ExtractionNo EverandHeterojunction Bipolar Transistors for Circuit Design: Microwave Modeling and Parameter ExtractionAinda não há avaliações

- Organic Light-Emitting Transistors: Towards the Next Generation Display TechnologyNo EverandOrganic Light-Emitting Transistors: Towards the Next Generation Display TechnologyAinda não há avaliações

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysNo EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysAinda não há avaliações

- Fundamentals of Electronics 1: Electronic Components and Elementary FunctionsNo EverandFundamentals of Electronics 1: Electronic Components and Elementary FunctionsAinda não há avaliações

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsNo EverandDigital Electronics 2: Sequential and Arithmetic Logic CircuitsNota: 5 de 5 estrelas5/5 (1)

- JNTU Exam TimetableDocumento6 páginasJNTU Exam Timetablerocky4bestAinda não há avaliações

- 3-1 R10 Time Tables June 2014Documento5 páginas3-1 R10 Time Tables June 2014rocky4bestAinda não há avaliações

- Design of Steel StructuresDocumento8 páginasDesign of Steel Structuresrocky4bestAinda não há avaliações

- Jawaharlal Nehru Technological University HyderabadDocumento3 páginasJawaharlal Nehru Technological University Hyderabadrocky4bestAinda não há avaliações

- Multimedia Application Development PDFDocumento1 páginaMultimedia Application Development PDFrocky4bestAinda não há avaliações

- Automotive Electrical and AutotronicsDocumento8 páginasAutomotive Electrical and Autotronicsrocky4bestAinda não há avaliações

- Biochemical EngineeringDocumento8 páginasBiochemical Engineeringrocky4bestAinda não há avaliações

- Not To Retain Original Certificates and Refund Fees in Case Student Leaves After Joining The CourseDocumento4 páginasNot To Retain Original Certificates and Refund Fees in Case Student Leaves After Joining The Courserocky4bestAinda não há avaliações

- Aerodynamics IDocumento8 páginasAerodynamics Irocky4bestAinda não há avaliações

- Unit 4Documento16 páginasUnit 4rocky4bestAinda não há avaliações

- Design and Analysis of Algorithms PDFDocumento1 páginaDesign and Analysis of Algorithms PDFrocky4bestAinda não há avaliações

- VRO 2012 Solved PaperDocumento11 páginasVRO 2012 Solved Paperrocky4bestAinda não há avaliações

- MBA Regular and Supplementary September 2013Documento4 páginasMBA Regular and Supplementary September 2013rocky4bestAinda não há avaliações

- Eamcet 2013 Preliminary Key EnggDocumento1 páginaEamcet 2013 Preliminary Key Enggrocky4bestAinda não há avaliações

- Aircraft Systems PDFDocumento1 páginaAircraft Systems PDFrocky4bestAinda não há avaliações

- EAMCET 2012 Toppers ListDocumento4 páginasEAMCET 2012 Toppers Listrocky4bestAinda não há avaliações

- Bulk Solids Handling Equipment PDFDocumento1 páginaBulk Solids Handling Equipment PDFrocky4bestAinda não há avaliações

- II Year I Sem Mid Term Exam Time Table 2013Documento4 páginasII Year I Sem Mid Term Exam Time Table 2013rocky4bestAinda não há avaliações

- Iv Year Ii Sem. R09Documento6 páginasIv Year Ii Sem. R09rocky4bestAinda não há avaliações

- BPH - IV - III and II Year I Semester I Mid Exam Time Table 2013Documento1 páginaBPH - IV - III and II Year I Semester I Mid Exam Time Table 2013rocky4bestAinda não há avaliações

- JNTU B.Tech II Sem Mid Exam Timetable for Aircraft MaintenanceDocumento1 páginaJNTU B.Tech II Sem Mid Exam Timetable for Aircraft Maintenancerocky4bestAinda não há avaliações

- BPH - IV - III and II Year I Semester I Mid Exam Time Table 2013Documento1 páginaBPH - IV - III and II Year I Semester I Mid Exam Time Table 2013rocky4bestAinda não há avaliações

- Jntuworld: Jawaharlal Nehru Technological University HyderabadDocumento1 páginaJntuworld: Jawaharlal Nehru Technological University HyderabadKabir Sai Prasanna SuryavanshAinda não há avaliações

- MBA IV SEM June 2012Documento1 páginaMBA IV SEM June 2012rocky4bestAinda não há avaliações

- Iv Year Ii Sem. R07Documento6 páginasIv Year Ii Sem. R07rocky4bestAinda não há avaliações

- Indian Coast Guard Offers Challenging Careers as OfficersDocumento6 páginasIndian Coast Guard Offers Challenging Careers as Officerss5a5Ainda não há avaliações

- Iv Year Ii Sem.r05Documento5 páginasIv Year Ii Sem.r05rocky4bestAinda não há avaliações

- R07 Set No. 2: 5. (A) If A Poisson Distribution Is Such That P (X 1) - P (X 3) - FindDocumento8 páginasR07 Set No. 2: 5. (A) If A Poisson Distribution Is Such That P (X 1) - P (X 3) - Findrocky4bestAinda não há avaliações

- Revised 1st Year B.pharmacy I Mid Exam TimetableDocumento1 páginaRevised 1st Year B.pharmacy I Mid Exam Timetablerocky4bestAinda não há avaliações

- IC 4047 Datasheet, Pinouts, Application Notes: Homemade Circuit ProjectsDocumento4 páginasIC 4047 Datasheet, Pinouts, Application Notes: Homemade Circuit ProjectsankasbilenkaAinda não há avaliações

- Fan Speed Control Using 555 Time IcDocumento33 páginasFan Speed Control Using 555 Time Icritesh chauhanAinda não há avaliações

- End Sem ReportDocumento22 páginasEnd Sem ReportKumar AjitAinda não há avaliações

- Comprehensive Automotive Electronics TrainingDocumento106 páginasComprehensive Automotive Electronics Trainingzaidiazir100% (1)

- Switch-Mode Light Dimmer Using MultivibratorsDocumento4 páginasSwitch-Mode Light Dimmer Using MultivibratorsCaryl Anne BalbasAinda não há avaliações

- ElecDocumento3 páginasElecAnbu SelvanAinda não há avaliações

- This Set of Digital Electronic1-Merged-merged-mergedDocumento1.802 páginasThis Set of Digital Electronic1-Merged-merged-mergedMadhura PansareAinda não há avaliações

- Lic MCQDocumento38 páginasLic MCQSRINIVASANAinda não há avaliações

- Analog Circuits Final Course Handout (Ramadevi)Documento19 páginasAnalog Circuits Final Course Handout (Ramadevi)Anvesh MagantiAinda não há avaliações

- CDIMultisparkDocumento17 páginasCDIMultisparkRandy JurasicAinda não há avaliações

- Part TimeDocumento77 páginasPart TimenarayananAinda não há avaliações

- Periyar University B.Sc. Physics SyllabusDocumento54 páginasPeriyar University B.Sc. Physics SyllabusVithya Sager100% (1)

- LED ChaserDocumento11 páginasLED ChaserRavindran MahadevanAinda não há avaliações

- 555 Timer As Mono Stable Multi VibratorDocumento28 páginas555 Timer As Mono Stable Multi VibratordererAinda não há avaliações

- Remote Controlled Fan RegulatorDocumento23 páginasRemote Controlled Fan RegulatorPradeep100% (5)

- Electronics & Communication EngineeringDocumento242 páginasElectronics & Communication EngineeringRUFUS SHAJIAinda não há avaliações

- BR Magzine1Documento4 páginasBR Magzine1EnricoLiaAinda não há avaliações

- Multivibrators and The 555 Timer: William KleitzDocumento45 páginasMultivibrators and The 555 Timer: William Kleitzmhd kdaimatiAinda não há avaliações

- HCC/HCF4098B Dual Monostable Multivibrator DatasheetDocumento14 páginasHCC/HCF4098B Dual Monostable Multivibrator DatasheetAnbu ArasanAinda não há avaliações

- UOM BSc Physics with Computer Applications RegulationsDocumento37 páginasUOM BSc Physics with Computer Applications RegulationsRajesh JagadeesanAinda não há avaliações

- 555 Timer PDFDocumento76 páginas555 Timer PDFronaldo19940% (1)

- Datasheet PDFDocumento10 páginasDatasheet PDFMohammed AliAinda não há avaliações

- Safety and Arming Device Timer 6-7-1976Documento5 páginasSafety and Arming Device Timer 6-7-1976nguyenhAinda não há avaliações

- PSG ECE SyllabusDocumento81 páginasPSG ECE SyllabusNithesh Chakravarthi NekkantiAinda não há avaliações

- LIA CIRCUITS QBDocumento14 páginasLIA CIRCUITS QBrkkumar07Ainda não há avaliações

- The 555 TimerDocumento14 páginasThe 555 Timergurudatha265100% (4)

- CH270 Service ManualDocumento88 páginasCH270 Service ManualAbu Abdou SiyahyaAinda não há avaliações

- B.SC - Program PhysicsDocumento48 páginasB.SC - Program PhysicsSuvo Mandal Suvo MandalAinda não há avaliações

- Automatic Street LightDocumento13 páginasAutomatic Street LightReymark CrisostomoAinda não há avaliações

- Flip-Flops IndiaDocumento16 páginasFlip-Flops IndiaArvinALAinda não há avaliações