Escolar Documentos

Profissional Documentos

Cultura Documentos

Full Subtractor VHDL Code Using Structural Modeling

Enviado por

OP2RTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Full Subtractor VHDL Code Using Structural Modeling

Enviado por

OP2RDireitos autorais:

Formatos disponíveis

ONLINE PLATFORM FOR PROGRAMMING AND RESEARCH (OP2R)

FULL SUBTRACTOR VHDL CODE USING STRUCTURAL MODELING

Library declaration library IEEE; use IEEE.STD_LOGIC_1164.ALL; --------------------------------------------

Std_logic_1164; package for std_logic (predefined data type).

entity full_subtractor is Port ( a, b, c: in STD_LOGIC; difff ,borrow: out STD_LOGIC); end full_subtractor; --------------------------------------------architecture Behavioral_FS of full_subtractor is ------------------------------------------------------------signal c1, c2, c3, s1: in std_logic; component xor_2 is port (k,d,e: in std_logic; f: out std_logic); end component; component and_1 is Port ( x,y : in STD_LOGIC; z : out STD_LOGIC); end component; component or_1 is Port ( g,h,i : in STD_LOGIC; z : out STD_LOGIC); end component; component not_1 is port (u: in std_logic; v: out std_logic); end component; ----------------------------------------------------begin X0: xor_2 port map (a,b,c, diff); X2: and_1 port map (s1,b,c1); X3: and_1 port map (c,b,c2); X4: and_1 port map (s1,c,c3); x5: or_1 port map (c1, c2, c3, borrow); -------------------------------------------------end Behavioral_FS;

Entity declaration. a, b, c :- input port bits (bits to be added) diff, borrow:- output port bits

Signal declaration. Signal c1, c2, c3 will act as inout port. Component (Ex-or, and, or) declaration. Declarative part of full adders Architecture. Components represent the structure of full adder circuit.

Statements part of the architecture. Components are port mapped to perform full subtraction operation.

INFOOP2R.WIX.COM/OP2R

ONLINE PLATFORM FOR PROGRAMMING AND RESEARCH (OP2R)

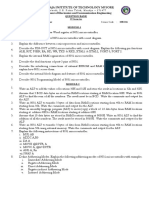

RTL VIEW:-

OUT PUT WAVEFORMS:

INFOOP2R.WIX.COM/OP2R

Você também pode gostar

- Half Adder VHDL Code Using Structrucral ModelingDocumento1 páginaHalf Adder VHDL Code Using Structrucral ModelingOP2R100% (2)

- Half Subtractor VHDL Code Using Structrucral ModelingDocumento2 páginasHalf Subtractor VHDL Code Using Structrucral ModelingOP2R0% (3)

- D Flip Flop - Structural ModelingDocumento2 páginasD Flip Flop - Structural ModelingOP2RAinda não há avaliações

- Full Adder VHDL Code Using Structural ModelingDocumento2 páginasFull Adder VHDL Code Using Structural ModelingOP2R91% (11)

- T Flip-Flop VHDL Code Using Behavioural ModelingDocumento2 páginasT Flip-Flop VHDL Code Using Behavioural ModelingOP2R100% (1)

- Half Subtractor VHDL Code Using Behavioural ModelingDocumento1 páginaHalf Subtractor VHDL Code Using Behavioural ModelingOP2RAinda não há avaliações

- Half Adder VHDL Code Using Behavioural ModelingDocumento1 páginaHalf Adder VHDL Code Using Behavioural ModelingOP2R100% (5)

- Half Adder VHDL Code Using Dataflow ModelingDocumento1 páginaHalf Adder VHDL Code Using Dataflow ModelingOP2RAinda não há avaliações

- Full Subtractor VHDL Code Using Data Flow ModelingDocumento1 páginaFull Subtractor VHDL Code Using Data Flow ModelingOP2R100% (1)

- D - To - J-K Flip Flop Conversion VHDL CodeDocumento2 páginasD - To - J-K Flip Flop Conversion VHDL CodeOP2RAinda não há avaliações

- Full Adder VHDL Code Using Data Flow ModelingDocumento1 páginaFull Adder VHDL Code Using Data Flow ModelingOP2RAinda não há avaliações

- S-R Flip Flop Using Behavioural ModelingDocumento2 páginasS-R Flip Flop Using Behavioural ModelingOP2RAinda não há avaliações

- SR - To - JK Flip Flop Conversion VHDL CodeDocumento2 páginasSR - To - JK Flip Flop Conversion VHDL CodeOP2RAinda não há avaliações

- Binary To Excess 3 VHDL Code Using Structural ModelingDocumento1 páginaBinary To Excess 3 VHDL Code Using Structural ModelingOP2RAinda não há avaliações

- D - To - S-R Flip-Flop Conversion VHDL CodeDocumento1 páginaD - To - S-R Flip-Flop Conversion VHDL CodeOP2RAinda não há avaliações

- J-K - To - D Flip-Flop Conversion VHDL CodeDocumento2 páginasJ-K - To - D Flip-Flop Conversion VHDL CodeOP2RAinda não há avaliações

- VHDL Code For Half Adder by Data Flow ModellingDocumento14 páginasVHDL Code For Half Adder by Data Flow ModellingPrateekKumar96% (24)

- HDL Lab Manual For VTUDocumento93 páginasHDL Lab Manual For VTULavanya Vaishnavi D.A.Ainda não há avaliações

- VHDL Code For 4 Bit ComparatorDocumento2 páginasVHDL Code For 4 Bit Comparatornady220944% (9)

- Digital Electronics Circuits: Experiment: 10Documento9 páginasDigital Electronics Circuits: Experiment: 10movab100% (1)

- VHDL Code For Serial in Serial Out Shift Register Using Behavioral ModellingDocumento3 páginasVHDL Code For Serial in Serial Out Shift Register Using Behavioral Modellingmeaow8886% (7)

- 2x2 Array MultiplierDocumento1 página2x2 Array Multipliermeera1121100% (1)

- Decade CounterDocumento2 páginasDecade Counterkishore981100% (3)

- Expt 4. 16x1 Mux Using 4x1 MuxDocumento6 páginasExpt 4. 16x1 Mux Using 4x1 Muxanon_64997028367% (3)

- Haredare Modeling Using Verilog Assignment-Week 1Documento6 páginasHaredare Modeling Using Verilog Assignment-Week 1krishna414Ainda não há avaliações

- Verilog Lab ManualDocumento27 páginasVerilog Lab Manualjainatush912100% (1)

- Updated - DSDV - BEC302 - LAB MANUAL123Documento54 páginasUpdated - DSDV - BEC302 - LAB MANUAL123Harish G CAinda não há avaliações

- HDL Model of Combinational CircuitsDocumento6 páginasHDL Model of Combinational CircuitsMunwar Ali Sd100% (1)

- 18EC46 Question BankDocumento1 página18EC46 Question Bankdinesh M.A.Ainda não há avaliações

- FPGA Seminar PPT-1Documento30 páginasFPGA Seminar PPT-1Swapna Sarker100% (1)

- Verilog Code For Code ConvertersDocumento5 páginasVerilog Code For Code Convertersseeksudhanshu1100% (1)

- Half and Full SubractorDocumento6 páginasHalf and Full Subractorguru20064040100% (1)

- VHDL Code For 8:1 Multiplexer.Documento5 páginasVHDL Code For 8:1 Multiplexer.Rishikesh Jatekar60% (5)

- Computer Organization and Architecture Lab: G L Bajaj Institute of Technology and Management Greater Noida - 201306Documento28 páginasComputer Organization and Architecture Lab: G L Bajaj Institute of Technology and Management Greater Noida - 201306Anshika Chauhan100% (3)

- VHDL Code For Updown CNTDocumento3 páginasVHDL Code For Updown CNTmeaow88100% (2)

- 15ecl48-VTU-raghudathesh-BJT MIXER PDFDocumento2 páginas15ecl48-VTU-raghudathesh-BJT MIXER PDFraghudatheshgp100% (1)

- Ade Mod5Documento8 páginasAde Mod5BasAinda não há avaliações

- EE El 213 Digital Circuits and Systems Assignment 4Documento3 páginasEE El 213 Digital Circuits and Systems Assignment 4Dhruv Paul100% (1)

- U1 L5 Biasing in MOS Amplifier Circuits.Documento6 páginasU1 L5 Biasing in MOS Amplifier Circuits.Shivani ParhadAinda não há avaliações

- Logic Gates Using Dataflow ModelingDocumento2 páginasLogic Gates Using Dataflow ModelingMurali100% (3)

- Combinational Digital Design Laboratory Manual: Experiment #8 Decoders & EncodersDocumento10 páginasCombinational Digital Design Laboratory Manual: Experiment #8 Decoders & EncodersJaideep Singh100% (1)

- Computer Networks Lab Manual LatestDocumento45 páginasComputer Networks Lab Manual LatestKande Archana K100% (16)

- Hardware Modeling Using Verilog Assignment-Week 3Documento6 páginasHardware Modeling Using Verilog Assignment-Week 3krishna41450% (2)

- 1 Interfacing Stepper Motor To 8086 Using 8255Documento40 páginas1 Interfacing Stepper Motor To 8086 Using 8255api-1932097782% (11)

- SIPO Register VHDL Code With TestbenchDocumento2 páginasSIPO Register VHDL Code With TestbenchJyo Jetti100% (1)

- Verilog Lab ManualDocumento72 páginasVerilog Lab ManualAditya NarayanAinda não há avaliações

- EXPERIMENT No 5 - MuX and DeMuxDocumento6 páginasEXPERIMENT No 5 - MuX and DeMuxSaksham DhawanAinda não há avaliações

- Embedded C Question BankDocumento6 páginasEmbedded C Question BankHarshith Gowda R100% (1)

- Experiment No. 7 4 Bit R - 2R Op-Amp Digital To Analog ConverterDocumento5 páginasExperiment No. 7 4 Bit R - 2R Op-Amp Digital To Analog Converterchaitanya100% (1)

- Question Bank-1913104-Design of Embedded SystemsDocumento12 páginasQuestion Bank-1913104-Design of Embedded SystemsHasib Al-ariki100% (1)

- Verilog Code For Counter With Testbench PDFDocumento1 páginaVerilog Code For Counter With Testbench PDFBien MedinaAinda não há avaliações

- DSDV Lab Manual PDFDocumento15 páginasDSDV Lab Manual PDFÅᴅᴀʀsʜ Rᴀᴍ100% (3)

- ADVANCED DIGITAL SIGNAL PROCESSING Lab ManualDocumento44 páginasADVANCED DIGITAL SIGNAL PROCESSING Lab Manualpravalika100% (1)

- ComputerNetworksLAB 18ECL76 7thsemesterDocumento94 páginasComputerNetworksLAB 18ECL76 7thsemesterPhanindra ReddyAinda não há avaliações

- Pseudo Random Sequence Generator in VerilogDocumento3 páginasPseudo Random Sequence Generator in VerilogAhmed AbduljabbarAinda não há avaliações

- Full Adder Design Using Verilog HDL in Three Modeling StylesDocumento8 páginasFull Adder Design Using Verilog HDL in Three Modeling StylesvijayseshuAinda não há avaliações

- Half Subtractor VHDL Code Using Dataflow ModelingDocumento1 páginaHalf Subtractor VHDL Code Using Dataflow ModelingOP2RAinda não há avaliações

- 1's Complement VHDL Code Using Dataflow ModelingDocumento1 página1's Complement VHDL Code Using Dataflow ModelingOP2RAinda não há avaliações

- 1's Complement VHDL Code Using Structrucral ModelingDocumento1 página1's Complement VHDL Code Using Structrucral ModelingOP2RAinda não há avaliações

- 2's Complement VHDL Code Using Structrucral ModelingDocumento2 páginas2's Complement VHDL Code Using Structrucral ModelingOP2RAinda não há avaliações

- Half Subtractor VHDL Code Using Dataflow ModelingDocumento1 páginaHalf Subtractor VHDL Code Using Dataflow ModelingOP2RAinda não há avaliações

- Ripple Carry Adder VHDL Code Using Structural ModellingDocumento1 páginaRipple Carry Adder VHDL Code Using Structural ModellingOP2R0% (1)

- Half Adder VHDL Code Using Dataflow ModelingDocumento1 páginaHalf Adder VHDL Code Using Dataflow ModelingOP2RAinda não há avaliações

- Half Subtractor VHDL Code Using Behavioural ModelingDocumento1 páginaHalf Subtractor VHDL Code Using Behavioural ModelingOP2RAinda não há avaliações

- Half Adder VHDL Code Using Behavioural ModelingDocumento1 páginaHalf Adder VHDL Code Using Behavioural ModelingOP2R100% (5)

- Decoder VHDL Code Using Behavioural Flow ModelingDocumento1 páginaDecoder VHDL Code Using Behavioural Flow ModelingOP2RAinda não há avaliações

- Full Adder VHDL Code Using Data Flow ModelingDocumento1 páginaFull Adder VHDL Code Using Data Flow ModelingOP2RAinda não há avaliações

- Full Subtractor VHDL Code Using Data Flow ModelingDocumento1 páginaFull Subtractor VHDL Code Using Data Flow ModelingOP2R100% (1)

- Demux VHDL Code Using Behavioural ModelingDocumento1 páginaDemux VHDL Code Using Behavioural ModelingOP2RAinda não há avaliações

- And Gate Beh - ModelingDocumento1 páginaAnd Gate Beh - ModelingOP2RAinda não há avaliações

- Xor Gate Beha - ModelingDocumento1 páginaXor Gate Beha - ModelingOP2RAinda não há avaliações

- Binary To Excess 3 VHDL Code Using Structural ModelingDocumento1 páginaBinary To Excess 3 VHDL Code Using Structural ModelingOP2RAinda não há avaliações

- Binary To Gray Converter VHDL Code Using Structural ModelingDocumento1 páginaBinary To Gray Converter VHDL Code Using Structural ModelingOP2R100% (2)

- 2's Complement VHDL Code Using Structrucral ModelingDocumento2 páginas2's Complement VHDL Code Using Structrucral ModelingOP2RAinda não há avaliações

- 1's Complement VHDL Code Using Structrucral ModelingDocumento1 página1's Complement VHDL Code Using Structrucral ModelingOP2RAinda não há avaliações

- 2's Complement VHDL Code Using Data Flow ModelingDocumento1 página2's Complement VHDL Code Using Data Flow ModelingOP2R67% (3)

- 1's Complement VHDL Code Using Dataflow ModelingDocumento1 página1's Complement VHDL Code Using Dataflow ModelingOP2RAinda não há avaliações

- Xnor Gate Beha - ModelingDocumento1 páginaXnor Gate Beha - ModelingOP2RAinda não há avaliações

- OR Gate Beha - ModelingDocumento1 páginaOR Gate Beha - ModelingOP2RAinda não há avaliações

- NOR Gate Beha - ModelingDocumento1 páginaNOR Gate Beha - ModelingOP2RAinda não há avaliações

- J-K - To - D Flip-Flop Conversion VHDL CodeDocumento2 páginasJ-K - To - D Flip-Flop Conversion VHDL CodeOP2RAinda não há avaliações

- NAND Gate Beh - ModelingDocumento1 páginaNAND Gate Beh - ModelingOP2RAinda não há avaliações

- SR - To - T Flip Flop Conversion VHDL CodeDocumento2 páginasSR - To - T Flip Flop Conversion VHDL CodeOP2RAinda não há avaliações

- J-K Flip Flop Usig Behavioural ModelingDocumento2 páginasJ-K Flip Flop Usig Behavioural ModelingOP2RAinda não há avaliações

- S-R Flip Flop Using Behavioural ModelingDocumento2 páginasS-R Flip Flop Using Behavioural ModelingOP2RAinda não há avaliações

- SR - To - JK Flip Flop Conversion VHDL CodeDocumento2 páginasSR - To - JK Flip Flop Conversion VHDL CodeOP2RAinda não há avaliações

- Impact of Internet Technology On Economic Crime: Veungopalan. R BA0140074Documento3 páginasImpact of Internet Technology On Economic Crime: Veungopalan. R BA0140074Seeralan VenugopalanAinda não há avaliações

- Property Type 242062,242062,242062Documento6 páginasProperty Type 242062,242062,242062An BalAinda não há avaliações

- Part 3 Information and QuantificationDocumento28 páginasPart 3 Information and Quantificationسجاد عناد كاظم البزونيAinda não há avaliações

- Precios Inv Jaspe 26-07-21Documento42 páginasPrecios Inv Jaspe 26-07-21lauraAinda não há avaliações

- Ip Project PDFDocumento64 páginasIp Project PDFKhushi KohliAinda não há avaliações

- Sram Part1Documento36 páginasSram Part1api-285860375Ainda não há avaliações

- Digital Marketing Case StudyDocumento39 páginasDigital Marketing Case StudyYoyoAinda não há avaliações

- Crim Check ReportDocumento1 páginaCrim Check ReportVulani IndlelaAinda não há avaliações

- Guide LC May 2022 - Beelingua For Students (Revision)Documento23 páginasGuide LC May 2022 - Beelingua For Students (Revision)CHRISTOPHERAinda não há avaliações

- Ec2354 Vlsi DesignDocumento13 páginasEc2354 Vlsi Designjgssb85Ainda não há avaliações

- db2 TXT Search 115Documento174 páginasdb2 TXT Search 115TrurlScribdAinda não há avaliações

- D000PTGC10 Activity Guide FinalDocumento360 páginasD000PTGC10 Activity Guide FinalSweater Geek100% (1)

- Embedded MB QRG Mzglkai e 10Documento2 páginasEmbedded MB QRG Mzglkai e 10invaderAinda não há avaliações

- Invoice: Page 1 of 2Documento2 páginasInvoice: Page 1 of 2web supportAinda não há avaliações

- RallybarDocumento4 páginasRallybarTravel TimeAinda não há avaliações

- MultiPOS - Point of Sale (POS) For WooCommerce by Devdiggers - CodeCanyonDocumento4 páginasMultiPOS - Point of Sale (POS) For WooCommerce by Devdiggers - CodeCanyonOBIOMA FRANCWHITEAinda não há avaliações

- Ass1 NormalizationDocumento2 páginasAss1 NormalizationDhana0% (4)

- ASME NQA-1 Quality Assurance Requirements For Nuclear Facility ApplicationsDocumento2 páginasASME NQA-1 Quality Assurance Requirements For Nuclear Facility ApplicationsPrakhar KulshreshthaAinda não há avaliações

- The Flash ADC A Circuit For All SeasonsDocumento5 páginasThe Flash ADC A Circuit For All Seasons于富昇Ainda não há avaliações

- Cloud Computing PolicyDocumento1 páginaCloud Computing PolicyBobby IM SibaraniAinda não há avaliações

- Schneider KNXDocumento1 páginaSchneider KNXRodrigo Pinetta100% (2)

- HN ATC Notes Module 1 Part1Documento10 páginasHN ATC Notes Module 1 Part1Rajath AnAinda não há avaliações

- WDT Installation Use Guide For Subcon For KTK V1.0 3092015Documento37 páginasWDT Installation Use Guide For Subcon For KTK V1.0 3092015Shah Fahad75% (4)

- AmigaAsmTutorial 1Documento174 páginasAmigaAsmTutorial 1Milan ZaninovićAinda não há avaliações

- OpenText Documentum Server CE 22.2 - DQL Reference Guide EnglishDocumento448 páginasOpenText Documentum Server CE 22.2 - DQL Reference Guide EnglishDamoAinda não há avaliações

- Practical 3 - Introduction To Object-Oriented Programming (Amended) PDFDocumento2 páginasPractical 3 - Introduction To Object-Oriented Programming (Amended) PDFDarian ChettyAinda não há avaliações

- Sv-Pro: High-Performance Network Security ApplianceDocumento2 páginasSv-Pro: High-Performance Network Security ApplianceEhsan RohaniAinda não há avaliações

- Final Year Project SRSDocumento25 páginasFinal Year Project SRSNikhil YadavAinda não há avaliações

- DHCP1 Project Report PDFDocumento69 páginasDHCP1 Project Report PDFVinay VyasAinda não há avaliações

- Pan OsDocumento952 páginasPan Osemail2suryaz0% (1)