Escolar Documentos

Profissional Documentos

Cultura Documentos

Conception Des Circuits Intégrés Prédiffusés Précaractérisés Et Sur Mesure v2010

Enviado por

Kaled HabibTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Conception Des Circuits Intégrés Prédiffusés Précaractérisés Et Sur Mesure v2010

Enviado por

Kaled HabibDireitos autorais:

Formatos disponíveis

Laboratoire d’Electronique, Microtechnologie & Communication

Conception des

Circuits Intégrés Prédiffusés

Précaractérisés et sur Mesure

Mohamed MASMOUDI

Professeur à l’ENIS

GE3 Mohamed Masmoudi

Laboratoire d’Electronique, Microtechnologie & Communication

Plan du cours

Introduction

Chapitre I : Techniques de conception des circuits intégrés

Chapitre II : ASIC Semi Spécifique

Chapitre III :ASIC Spécifique

Chapitre IV : Méthodologies pour la conception des circuits intégrés

Chapitre V : Conception de Bibliothèques de cellules

GE3 Mohamed Masmoudi

Chapitre I : Techniques de conception des circuits intégrés

Chapitre I

Techniques de conception des circuits intégrés

Plan du chapitre :

- Classification des Circuits intégrés

- Evolution des techniques de conception

- Classification des ASICs

- Comparaison des ASICs

GE3 Mohamed Masmoudi

Chapitre I : Techniques de conception des circuits intégrés

GE3 Mohamed Masmoudi

Chapitre I : Techniques de conception des circuits intégrés

GE3 Mohamed Masmoudi

Chapitre I : Techniques de conception des circuits intégrés

GE3 Mohamed Masmoudi

Chapitre I : Techniques de conception des circuits intégrés

GE3 Mohamed Masmoudi

Chapitre I : Techniques de conception des circuits intégrés

ASIC : Application Specific Integrated Circuit

Classification des ASICs

ASIC

ASIC ASIC

semi-spécifique spécifique

Programmable Pré-diffusé Pré-caractérisé Sur mesure Système sur

"FPGA" "Gate Array" "Standard Cell" "Full Custum" puce "SoC"

GE3 Mohamed Masmoudi

Chapitre I : Techniques de conception des circuits intégrés

Comparaison des ASICs

GE3 Mohamed Masmoudi

Chapitre II : ASIC Semi Spécifique

Chapitre II

ASIC Semi Spécifique

Plan du chapitre :

- Circuits Programmables

- Circuits prédiffusés

- Comparaison

GE3 Mohamed Masmoudi

Chapitre II : ASIC Semi Spécifique

Programmable "FPGA"

ASIC

ASIC ASIC

semi-spécifique spécifique

Programmable Pré-diffusé Pré-caractérisé Sur mesure Système sur

"FPGA" "Gate Array" "Standard Cell" "Full Custum" puce "SoC"

GE3 Mohamed Masmoudi

Chapitre II : ASIC Semi Spécifique

GE3 Mohamed Masmoudi

Chapitre II : ASIC Semi Spécifique

GE3 Mohamed Masmoudi

Chapitre II : ASIC Semi Spécifique

Critères de choix de la technologie

GE3 Mohamed Masmoudi

Chapitre II : ASIC Semi Spécifique

Les principaux fabriquants

1. ALTERA 30%

2. XILINX 30%

3. LATTICE 10%

4. ACTEL 10%

5. Etc… 20%

GE3 Mohamed Masmoudi

Chapitre II : ASIC Semi Spécifique

GE3 Mohamed Masmoudi

Chapitre II : ASIC Semi Spécifique

Bloc Logique : CLB (Xilinx XC3000)

GE3 Mohamed Masmoudi

Chapitre II : ASIC Semi Spécifique

Technologie de Programmation

Anti-fusible

Flash

SRAM

Caractéristiques : encombrement minimal, non reprogrammable, technologie spécifique

GE3 Mohamed Masmoudi

Chapitre II : ASIC Semi Spécifique

Technologie de Programmation

Anti-fusible

Flash

SRAM

EPROM

Caractéristiques : conserve la configuration, système autonome, technologie spécifique

GE3 Mohamed Masmoudi

Chapitre II : ASIC Semi Spécifique

Technologie de Programmation

Anti-fusible

Flash

SRAM

Caractéristiques : volatile, reconfigurable dynamiquement, technologie spécifique

GE3 Mohamed Masmoudi

Chapitre II : ASIC Semi Spécifique

GE3 Mohamed Masmoudi

Chapitre II : ASIC Semi Spécifique

GE3 Mohamed Masmoudi

Chapitre II : ASIC Semi Spécifique

GE3 Mohamed Masmoudi

Chapitre II : ASIC Semi Spécifique

GE3 Mohamed Masmoudi

Chapitre II : ASIC Semi Spécifique

Pré-diffusé "Gate Array"

ASIC

ASIC ASIC

semi-spécifique spécifique

Programmable Pré-diffusé Pré-caractérisé Sur mesure Système sur

"FPGA" "Gate Array" "Standard Cell" "Full Custum" puce "SoC"

GE3 Mohamed Masmoudi

Chapitre II : ASIC Semi Spécifique

GE3 Mohamed Masmoudi

Chapitre II : ASIC Semi Spécifique

GE3 Mohamed Masmoudi

Chapitre II : ASIC Semi Spécifique

GE3 Mohamed Masmoudi

Chapitre II : ASIC Semi Spécifique

GE3 Mohamed Masmoudi

Chapitre III : ASIC Spécifique

Chapitre III

ASIC Spécifique

Plan du chapitre :

- Circuits Précaractérisés

- Circuits sur Mesure

- Système sur puce

GE3 Mohamed Masmoudi

Chapitre III : ASIC Spécifique

Pré-caractérisé "Standard Cell"

ASIC

ASIC ASIC

semi-spécifique spécifique

Programmable Pré-diffusé Pré-caractérisé Sur mesure Système sur

"FPGA" "Gate Array" "Standard Cell" "Full Custum" puce "SoC"

GE3 Mohamed Masmoudi

Chapitre III : ASIC Spécifique

GE3 Mohamed Masmoudi

Chapitre III : ASIC Spécifique

GE3 Mohamed Masmoudi

Chapitre III : ASIC Spécifique

GE3 Mohamed Masmoudi

Chapitre III : ASIC Spécifique

GE3 Mohamed Masmoudi

Chapitre III : ASIC Spécifique

GE3 Mohamed Masmoudi

Chapitre III : ASIC Spécifique

Sur Masure "Full Custum"

ASIC

ASIC ASIC

semi-spécifique spécifique

Programmable Pré-diffusé Pré-caractérisé Sur mesure Système sur

"FPGA" "Gate Array" "Standard Cell" "Full Custum" puce "SoC"

GE3 Mohamed Masmoudi

Chapitre III : ASIC Spécifique

GE3 Mohamed Masmoudi

Chapitre III : ASIC Spécifique

Procédure Réelle

Spécification du système

Procédure Idéale

Définition architecture

Spécification du système

Simulation fonctionnelle

Conception logique Description comportementale

Simulation logique

Conception électrique Description structurelle

Simulation électrique

Layout

Layout

Extraction

Simulation Fabrication

Comparaison

Fabrication

GE3 Mohamed Masmoudi

Chapitre III : ASIC Spécifique

Système sur Puce "SoC"

ASIC

ASIC ASIC

semi-spécifique spécifique

Programmable Pré-diffusé Pré-caractérisé Sur mesure Système sur

"FPGA" "Gate Array" "Standard Cell" "Full Custum" puce "SoC"

GE3 Mohamed Masmoudi

Chapitre III : ASIC Spécifique

GE3 Mohamed Masmoudi

Chapitre III : ASIC Spécifique

GE3 Mohamed Masmoudi

Chapitre III : ASIC Spécifique

Comparaison FPGA/GA/SC

GE3 Mohamed Masmoudi

Chapitre III : ASIC Spécifique

Migration FPGA h ASIC

Les FPGA diminuent le temps de conception d'un ASIC

Les FPGA permettent d'obtenir rapidement le prototypage rapide d'un ASIC

pour le tester sur carte.

GE3 Mohamed Masmoudi

Chapitre III : ASIC Spécifique

GE3 Mohamed Masmoudi

Chapitre III : ASIC Spécifique

GE3 Mohamed Masmoudi

Chapitre III : ASIC Spécifique

GE3 Mohamed Masmoudi

Chapitre IV : Méthodologies pour la conception des circuits intégrés

Chapitre IV

Méthodologies pour la conception des circuits intégrés

Plan du chapitre :

- Outils de CAO

- Flot de conception des circuits analogiques

- Flot de conception pour les circuits numériques

- Flot de conception des circuits mixtes

GE3 Mohamed Masmoudi

Chapitre IV : Méthodologies pour la conception des circuits intégrés

Rôle de la Conception Assistée par Ordinateur

(CAO - CAD:Computer Aided Design / CAE:Computer Aided Engineering)

- Maîtrise des temps et des coûts.

- Nécessité suite à la complexité croissante des circuits électroniques

- Gérer les immenses volumes de données techniques

- Analyses poussées (stress, fiabilité, thermique, …)

- Réutilisabilité / Intellectual Property / Testabilité

GE3 Mohamed Masmoudi

Chapitre IV : Méthodologies pour la conception des circuits intégrés

Evolution : Méthodes de CAO

1950 : Premier système graphique (MIT)

1969 : SPICE (Berkeley)

#1970 : Dessin des masques à la main

#1980 : Compilation de silicium (portes vers masques)

#1985 : Synthèse logique / Naissance de VHDL

#1990 : Synthèse de haut niveau

#1995 : Synthèse architecturale

Méthodologie ASIC : juste par conception

#2000 : Langage multi-disciplines industriel : VHDL-AMS

Analogique / Numérique / Autres (MOEMS)

Diminution des «Time-to-Market»

et de la durée de vie des produits

Méthodologie / Gestion de projet TRES IMPORTANT

GE3 Mohamed Masmoudi

Chapitre IV : Méthodologies pour la conception des circuits intégrés

Outils de CAO

- Simulateurs Analogiques : SPICE, ELDO, SPECTRE, …

- Simulateurs Logiques : SPICE, ELDO, SPECTRE, …

- Simulateurs Fonctionnels Comportementaux Logiques: MATLAB,

VHDL, VERILOG, …

- Simulateurs Fonctionnels Comportementaux Analogiques et Mixtes :

VHDL-AMS, VERILOG-AMS, …

GE3 Mohamed Masmoudi

Chapitre IV : Méthodologies pour la conception des circuits intégrés

Flot de conception

LAYOUT

Manuel

Synthèse

Logique Compilation

de Si

GE3 Mohamed Masmoudi

Chapitre IV : Méthodologies pour la conception des circuits intégrés

Flot de conception

Conception algorithmique et synthèse de haut niveau

GE3 Mohamed Masmoudi

Chapitre IV : Méthodologies pour la conception des circuits intégrés

Flot de conception des Circuits Intégrés Analogiques

Spécification du système

Conception électrique

Simulation électrique

Layout

Extraction

Netlist

Simulation électrique

Ok

Fabrication

GE3 Mohamed Masmoudi

Chapitre IV : Méthodologies pour la conception des circuits intégrés

Flot de conception des Circuits Intégrés numériques

Spécifications

oui

Modélisation haut niveau Vérification Diagnostic

non

Modélisation RTL Simulation Diagnostic

Synthèse logique Analyse de délais Diagnostic

Analyse de testabilité Performances Diagnostic

Placement-Routage DRC + Extraction Diagnostic

Fabrication d’un prototype

GE3 Mohamed Masmoudi

Chapitre IV : Méthodologies pour la conception des circuits intégrés

Synthèse logique

simulation abstraite simulation logico-temporelle simulation électrique

synthèse logique

HDL Gate level Physique level

Compilation de silicium

if a=‘1’ then + placement/routage

r=v v

else

2 1 r

r = not (p) p

end if

a

N N

P

GE3 Mohamed Masmoudi

Chapitre IV : Méthodologies pour la conception des circuits intégrés

Flow de Conception Typique pour FPGA

GE3 Mohamed Masmoudi

Chapitre IV : Méthodologies pour la conception des circuits intégrés

Modélisation Analogique et Mixte

C’est une description comportementale des circuits analogiques et mixtes

VHDL-AMS, VERILOG-AMS représentent les principaux outils de

modélisation et de simulation analogique et mixte.

Nécessité d’avoir une bibliothèque suffisamment riche de modèles

comportementaux : AOP, Filtres, CAN, CNA, PLL, VCO, etc….

GE3 Mohamed Masmoudi

Chapitre IV : Méthodologies pour la conception des circuits intégrés

Flot de conception des Circuits Intégrés mixtes

Convertisseur A/N

Partie Analogique Partie Numérique

Bibliothèque Bibliothèque

Modèles Analogiques Numérique

Circuit Modèle partie

Architecture Partie

Niveau transistor Analogique

Numérique

Vérification Vérification

Modèle du

& test & test

Convertisseur A/N

Layout partie Synthèse de la partie

Analogique Numérique

Layout du convertisseur A/N

GE3 Mohamed Masmoudi

Chapitre IV : Méthodologies pour la conception des circuits intégrés

Un environnement de CAO mixte : Tanner

GE3 Mohamed Masmoudi

Chapitre IV : Méthodologies pour la conception des circuits intégrés

Un environnement de CAO mixte : Tanner

GE3 Mohamed Masmoudi

Chapitre IV : Méthodologies pour la conception des circuits intégrés

Synthèse Analogique

Jusqu’à ce jour la synthèse des circuits analogiques est manuelle en

attendant l’apparition du premier outil de synthèse analogique.

Plusieurs labo de recherche, dans le monde, travaillent pour développer

des outils de synthèse analogique.

GE3 Mohamed Masmoudi

Chapitre V : Conception de Bibliothèques de cellules

Chapitre V

Conception de Bibliothèques de cellules

Plan du chapitre :

- Choix des critères pour la conception

- Développement d’un Design Kit (Technologie CMOS 0.35µm Puits N)

- Exemples de cellules logiques

- Exemples de cellules analogiques

- Plots d’E/S

GE3 Mohamed Masmoudi

Chapitre V : Conception de Bibliothèques de cellules

Choix des critères de Conception

- Surface minimale

- Consommation minimale

- Fréquence maximale

GE3 Mohamed Masmoudi

Chapitre V : Conception de Bibliothèques de cellules

Design Kit (Technologie CMOS 0.35µm Puits N)

Caractéristiques de la Technologie

GE3 Mohamed Masmoudi

Chapitre V : Conception de Bibliothèques de cellules

Design Kit (Technologie CMOS 0.35µm Puits N)

GE3 Mohamed Masmoudi

Chapitre V : Conception de Bibliothèques de cellules

Design Kit (Technologie CMOS 0.35µm Puits N)

GE3 Mohamed Masmoudi

Chapitre V : Conception de Bibliothèques de cellules

Design Kit (Technologie CMOS 0.35µm Puits N)

Inverseurs

GE3 Mohamed Masmoudi

Chapitre V : Conception de Bibliothèques de cellules

Design Kit (Technologie CMOS 0.35µm Puits N)

NAND (2 entrées)

NOR (2 entrées)

GE3 Mohamed Masmoudi

Chapitre V : Conception de Bibliothèques de cellules

Design Kit (Technologie CMOS 0.35µm Puits N)

CAN (8 bits)

GE3 Mohamed Masmoudi

Chapitre V : Conception de Bibliothèques de cellules

Design Kit (Technologie CMOS 0.35µm Puits N)

DAC (8 bits)

GE3 Mohamed Masmoudi

Chapitre V : Conception de Bibliothèques de cellules

Design Kit (Technologie CMOS 0.35µm Puits N)

DAC (10 bits)

GE3 Mohamed Masmoudi

Chapitre V : Conception de Bibliothèques de cellules

Design Kit (Technologie CMOS 0.35µm Puits N)

Plots d’E/S analogiques

GE3 Mohamed Masmoudi

Chapitre V : Conception de Bibliothèques de cellules

Design Kit (Technologie CMOS 0.35µm Puits N)

Plots d’E/S analogiques

Vdd

Vdd Core Gnd Core

Pad Gnd Pad

Vdd Vdd

In Core In Core

Pad Gnd Pad Gnd

GE3 Mohamed Masmoudi

Chapitre V : Conception de Bibliothèques de cellules

Design Kit (Technologie CMOS 0.35µm Puits N)

Plots d’E/S analogiques

Pad "Gnd" Pad "In" Pad "In" Pad "In" Pad "In" Pad "In" Pad "In" Pad "Vdd"

D D D

D D R D D

GE3 Mohamed Masmoudi

Chapitre V : Conception de Bibliothèques de cellules

Design Kit (Technologie CMOS 0.35µm Puits N)

Plots d’E/S logiques

GE3 Mohamed Masmoudi

Chapitre V : Conception de Bibliothèques de cellules

Design Kit (Technologie CMOS 0.35µm Puits N)

Plots d’E/S logiques

Plot d’entrée :

Vdd Vdd

In Core In Core

Pad Gnd Pad Gnd

Plot de sortie :

Core Out

Pad

GE3 Mohamed Masmoudi

Chapitre V : Conception de Bibliothèques de cellules

Design Kit (Technologie CMOS 0.35µm Puits N)

Plots d’entrées

GE3 Mohamed Masmoudi

Chapitre V : Conception de Bibliothèques de cellules

Design Kit (Technologie CMOS 0.35µm Puits N)

Plots de sortie

GE3 Mohamed Masmoudi

Você também pode gostar

- Grille Intelligente: Échange d'électricité et d'informations entre les maisons et les centrales électriquesNo EverandGrille Intelligente: Échange d'électricité et d'informations entre les maisons et les centrales électriquesAinda não há avaliações

- Cours CIs - 2012Documento174 páginasCours CIs - 2012Ayman OubghachiAinda não há avaliações

- Introduction Circuits Logiques Programmables - Presentation 2010Documento38 páginasIntroduction Circuits Logiques Programmables - Presentation 2010fieea100% (2)

- Twistronics: Le saint graal de la physique, des matériaux quantiques et des nanotechnologiesNo EverandTwistronics: Le saint graal de la physique, des matériaux quantiques et des nanotechnologiesAinda não há avaliações

- Notes de Cours VLSIDocumento198 páginasNotes de Cours VLSIMahmoud Doughan50% (2)

- Systèmes De Communication Véhiculaire: Les perspectives d'avenir du transport intelligentNo EverandSystèmes De Communication Véhiculaire: Les perspectives d'avenir du transport intelligentAinda não há avaliações

- Chapitre 4 Alimentation - Moteur - Pas - À - PasDocumento37 páginasChapitre 4 Alimentation - Moteur - Pas - À - Paskhaled100% (1)

- Nez Électronique: Un appareil innovant fournit aux humains un odorat puissantNo EverandNez Électronique: Un appareil innovant fournit aux humains un odorat puissantAinda não há avaliações

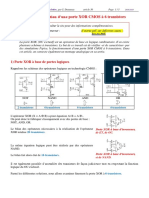

- Xor PDFDocumento5 páginasXor PDFYoussef RagraguiAinda não há avaliações

- Circuit IntegresDocumento7 páginasCircuit IntegresAbd OUAinda não há avaliações

- Fox G20Documento21 páginasFox G20Omar Zemrani100% (1)

- TP 1 Info Indus07Documento15 páginasTP 1 Info Indus07MOHAMED TAMZAITIAinda não há avaliações

- Circuits Integres PDFDocumento8 páginasCircuits Integres PDFMohamed KadiriAinda não há avaliações

- Chapitre 6 Amplificateur de PuissanceDocumento11 páginasChapitre 6 Amplificateur de PuissanceMc R-OneAinda não há avaliações

- CHAP1Documento6 páginasCHAP1riadh hassnaouiAinda não há avaliações

- Alimentation StabiliséeDocumento1 páginaAlimentation StabiliséeMouritaniDakhnawi100% (3)

- Tp2 PhototransistorDocumento7 páginasTp2 PhototransistorSaad RemchaniAinda não há avaliações

- CC Reseaux Et Supervision Roi5 2020Documento2 páginasCC Reseaux Et Supervision Roi5 2020Abdoul Bagui YaoubaAinda não há avaliações

- IjDocumento7 páginasIjAbderrahmane WardiAinda não há avaliações

- Mise en Route Du Compilateur MPLAB XC8Documento11 páginasMise en Route Du Compilateur MPLAB XC8nawzatAinda não há avaliações

- Microcontroleur PIC16F84Documento33 páginasMicrocontroleur PIC16F84redaAinda não há avaliações

- TD-Alternatif Et PuissanceDocumento24 páginasTD-Alternatif Et PuissanceBakr IbrahimiAinda não há avaliações

- 16FXXXDocumento86 páginas16FXXXkhmAinda não há avaliações

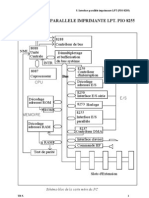

- Port Parallèle Pia 8255Documento11 páginasPort Parallèle Pia 8255alex bbapAinda não há avaliações

- Mini Projet DSP PDFDocumento12 páginasMini Projet DSP PDFSami FarsiAinda não há avaliações

- Ele119 CompletDocumento276 páginasEle119 CompletayoubAinda não há avaliações

- TD Réseau-RLI CorrigéDocumento7 páginasTD Réseau-RLI CorrigéMazen TouaitiAinda não há avaliações

- 727 PDFDocumento93 páginas727 PDFBachir BchiriAinda não há avaliações

- Chapitre I - Introduction À La MicroélectroniqueDocumento7 páginasChapitre I - Introduction À La MicroélectroniqueCy LaiAinda não há avaliações

- 2 ProcessusDocumento114 páginas2 ProcessusBtissamBettyAinda não há avaliações

- 2018chapitre1 6800Documento5 páginas2018chapitre1 6800lyza DZAinda não há avaliações

- Traitement Du Signal Examen SC 12 PDFDocumento2 páginasTraitement Du Signal Examen SC 12 PDFMohamed Aly SowAinda não há avaliações

- TD1 FiltrageDocumento5 páginasTD1 FiltrageAkram Djerrar100% (1)

- Etude D'un Logiciel de Simulation ProteusDocumento30 páginasEtude D'un Logiciel de Simulation ProteusStanley Vianney100% (1)

- Partie-2-Microprocesseur + MemoireDocumento14 páginasPartie-2-Microprocesseur + MemoireyaoAinda não há avaliações

- Programmation de L'interface ParallèleDocumento10 páginasProgrammation de L'interface ParallèleAbdeltif BelquorchiAinda não há avaliações

- CmosDocumento32 páginasCmosDhekra JbeliAinda não há avaliações

- TP TD N2 Microntroleur AssembleurDocumento4 páginasTP TD N2 Microntroleur AssembleurKhaoula EddouibAinda não há avaliações

- TDDocumento10 páginasTDredAinda não há avaliações

- SYSTEMES A TEMPS DISCRET Commande Numérique Des ProcédésDocumento60 páginasSYSTEMES A TEMPS DISCRET Commande Numérique Des ProcédésAymen ChaairaAinda não há avaliações

- Chapitre IV Programmation PIC 16F84Documento12 páginasChapitre IV Programmation PIC 16F84Sanae BOUNOUAAinda não há avaliações

- Cours - Composants Logiques Programmables Et VHDLDocumento141 páginasCours - Composants Logiques Programmables Et VHDLYoussef Elalaoui0% (1)

- Cours DSP AB AsmDocumento23 páginasCours DSP AB AsmIly'as En-naouiAinda não há avaliações

- Questions Pre-Requis DSPDocumento1 páginaQuestions Pre-Requis DSPhasnaeAinda não há avaliações

- TP CmosDocumento17 páginasTP CmosHiba TANTAOUIAinda não há avaliações

- Book 1Documento15 páginasBook 1Hossam EddinAinda não há avaliações

- Examen1 Traitement Du SignalDocumento4 páginasExamen1 Traitement Du SignalAkram DjerrarAinda não há avaliações

- Filtres ActifsDocumento3 páginasFiltres ActifsMouad Elmekaoui100% (1)

- ch1 DSPDocumento53 páginasch1 DSPRami MeshriAinda não há avaliações

- TP N°1 M1 Embarqué MicrocontrôleurDocumento2 páginasTP N°1 M1 Embarqué Microcontrôleurعمر الفاروقAinda não há avaliações

- tp1 Reseaux Des Capteurs-ConvertiDocumento5 páginastp1 Reseaux Des Capteurs-ConvertiRaed SassiAinda não há avaliações

- ch7 Memoires PDFDocumento9 páginasch7 Memoires PDFYoucef Br'sAinda não há avaliações

- Serie 3 SMP5 (2020-2021)Documento4 páginasSerie 3 SMP5 (2020-2021)mohamedAinda não há avaliações

- Les Bascules Et Registres: A.LebrunDocumento30 páginasLes Bascules Et Registres: A.LebrunMouhcine ZianeeAinda não há avaliações

- TP Am+fmDocumento10 páginasTP Am+fmpc hpAinda não há avaliações

- Contrôle N°1Documento3 páginasContrôle N°1Oum SolaymanAinda não há avaliações

- Interface Serie Programmable - ACIA 6850Documento10 páginasInterface Serie Programmable - ACIA 6850Lynda Tli67% (3)

- MMO Corrigé Sujet 1synthèse M21Documento3 páginasMMO Corrigé Sujet 1synthèse M21Abdou KarimAinda não há avaliações

- TP E. Numérique (EEA)Documento38 páginasTP E. Numérique (EEA)Tas ManAinda não há avaliações

- TDelectrocinetiqueCh2v1 0Documento8 páginasTDelectrocinetiqueCh2v1 0Faiçal Saidi100% (2)

- EMD STRM2 - 2019 (Rattrapage) (Corrigé)Documento4 páginasEMD STRM2 - 2019 (Rattrapage) (Corrigé)nait amara zaidAinda não há avaliações

- Cours - Électronique AnalogiqueDocumento11 páginasCours - Électronique Analogiquehnainiamedamine28Ainda não há avaliações

- Cliquer Ici Pour Telecharger Les ExercicesDocumento6 páginasCliquer Ici Pour Telecharger Les ExercicesUlrich DjagbaAinda não há avaliações

- Chap IiiDocumento18 páginasChap IiiMusic LyricsAinda não há avaliações

- FPGADocumento49 páginasFPGAkachAinda não há avaliações

- Chap8-Les RegistresDocumento6 páginasChap8-Les RegistresAhmed GourineAinda não há avaliações

- Chapitre2 Systèmes Logiques BasculesDocumento33 páginasChapitre2 Systèmes Logiques BasculesamenmhedhbiiAinda não há avaliações

- Hadji Circuits SequentielsDocumento21 páginasHadji Circuits SequentielsSami SelatniAinda não há avaliações

- TD Fpga Cs 2015Documento5 páginasTD Fpga Cs 2015hakim100% (1)

- 4 - Filtres ActifsDocumento9 páginas4 - Filtres ActifsaminhardAinda não há avaliações

- Test n2 Correction Reduit2 PDFDocumento10 páginasTest n2 Correction Reduit2 PDFSoufiane BoulachgourAinda não há avaliações

- Solut 8Documento9 páginasSolut 8Ghazi DayehAinda não há avaliações

- Cours LogiqueDocumento6 páginasCours LogiqueMaxence KouessiAinda não há avaliações

- BasculesDocumento19 páginasBasculesMahdi LahdiliAinda não há avaliações

- Manuel D'examens D'en-2020Documento102 páginasManuel D'examens D'en-2020MARYEM CHOUKRIAinda não há avaliações

- Chapitre 2 Electro NumeriqueDocumento26 páginasChapitre 2 Electro NumeriqueMerryAinda não há avaliações

- TD VHDL 1Documento5 páginasTD VHDL 1Zakaria ZineAinda não há avaliações

- Examen Instrumentation2021Documento4 páginasExamen Instrumentation2021salah mermouneAinda não há avaliações

- Acquisition Et Restitution Du SignalDocumento201 páginasAcquisition Et Restitution Du SignalAissa KalacheAinda não há avaliações

- TD-Logique SéquentielleDocumento8 páginasTD-Logique SéquentielleFabrice leonel Toukam PoualeuAinda não há avaliações

- TD3: Synthèse VHDL: Exercice 1Documento5 páginasTD3: Synthèse VHDL: Exercice 1Mohamed Aziz Ben RomdhaneAinda não há avaliações

- F Exel3.20juin2005Documento4 páginasF Exel3.20juin2005Gray AbAinda não há avaliações

- Cours Circuits IntegresDocumento17 páginasCours Circuits Integresemmanuelngass350Ainda não há avaliações

- Les Différentes Familles PDFDocumento14 páginasLes Différentes Familles PDFHarun Le Principal GominaAinda não há avaliações

- Correction TD1-IMT2-MST1-21-22Documento14 páginasCorrection TD1-IMT2-MST1-21-22WISSAL JANAAinda não há avaliações

- Correction Physique Appliquee Juin 2012 Sti ElectroniqueDocumento5 páginasCorrection Physique Appliquee Juin 2012 Sti ElectroniqueLetudiant.fr100% (2)

- TP N°1 Réaliser Par Charfeddine RebhiDocumento6 páginasTP N°1 Réaliser Par Charfeddine RebhiRebhi AchrefAinda não há avaliações

- TD N°1Documento1 páginaTD N°1younes marefAinda não há avaliações