Escolar Documentos

Profissional Documentos

Cultura Documentos

Contador 74193

Enviado por

Manuel Arellano CondeTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Contador 74193

Enviado por

Manuel Arellano CondeDireitos autorais:

Formatos disponíveis

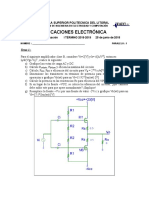

CONTADOR 74193 (LS193/HC193) La Figura 8.1, muestra el smbolo lgico y la descripcin de entrada y salida del contador 74193.

Este contador puede describirse como un contador ascendente/descendente preiniciable MOD-16, con conteo sincrnico, preiniciacin asincrnica y reiniciacin maestra asincrnica.

FIGURA 8.1. Contador ascendente/descendente preiniciable 74193. a) Smbolo lgico, b) Descripcin entrada/salida y c) Tabla de seleccin de modos. Descripcin de la funcin de cada entrada y salida: ENTRADAS DE RELOJ CPU Y CPD. El contador responder a las TPP (Transicin de Pendiente Positiva) en una de las dos entradas de reloj. CPU es la entrada de reloj de conteo ascendente. Cuando se apliquen los pulsos a esta entrada, el contador se incrementar (contar hacia arriba) en cada TPP hasta llegar a un conteo mximo de 1111; entonces se recicla a 0000 y vuelve a comenzar. CPD es la entrada de reloj de conteo descendente. Cuando se apliquen los pulsos a esta entrada, el contador decrementar (contar hacia abajo) en cada TPP hasta llegar a un conteo mnimo de 0000; entonces se recicla a 1111 y vuelve a comenzar. De este modo se usar una entrada de reloj para contar en tanto la otra est inactiva (se conserva en ALTO).

REINICIACIN MAESTRA (MR). Esta es una entrada asincrnica activa en ALTO que reinicia al contador en el estado 0000. MR es un reiniciador de CD (corriente directa), de manera que tendr al contador en 0000 en tanto que MR=1. Tambin elimina todas las otras entradas.

ENTRADAS PREINICIABLES. Los multivibradores , MVB (flip-flop), del contador pueden preiniciarse en los niveles lgicos presentes en las entradas de datos paralelas P0-P3, pulsando momentneamente la entrada

de carga paralela PL' de ALTO a BAJO. Esta es una preiniciacin asincrnica que elimina la operacin de conteo. No obstante, PL' no tendr efecto si la entrada MR se encuentra en su estado activo ALTO.

SALIDAS DEL CONTEO. El conteo regular siempre est presente en las salidas Q0-Q3 de los MVB, donde Q3 es el bit menos significativo (LSB, por sus siglas en ingls) y Q0 es el bit ms significativo (MSB, por sus siglas en ingls).

SALIDAS FINALES DEL CONTEO. Estas salidas se utilizan cuando dos o ms unidades del 74LS193 se conectan como contador con etapas mltiples, para producir un nmero MD mayor. En el modo de conteo ascendente, la salida TC'U del contador de orden inferior se conecta a la entrada CPU del siguiente contador de orden superior. En el modo de conteo descendente, la salida TCD del contador de orden inferior se conecta a la entrada CPD del siguiente contador de orden superior.

FIGURA 8.2 a) Lgica de la unidad 74193 para generar TC'U; b) Lgica para generar TC'D TCU es el conteo ascendente final (tambin llamado acarreo). Se genera en el 74193 utilizando la lgica que se muestra en la Figura 8.2 a). Evidentemente TC'U ser BAJO slo cuando el contador se encuentre en el estado 1111 y CPU sea BAJO. As, TC'U permanecer en ALTO cuando el contador cuente hacia arriba de 0000 a 0001. En la siguiente TPP de CPU, el conteo pasa a 1111, pero TC'U no pasa a BAJO sino hasta que CPU retorna a BAJO. La siguiente TPP en CPU recicla el contador a 0000 y tambin ocasiona que TC'U retorne a ALTO. Esta TPP en TC'U ocurre cuando el contador se recicla de 1111 a 0000 y se puede utilizar para cronometrar un segundo contador ascendente 74193 a su siguiente conteo superior.

TC'D es la salida del conteo descendente final (tambin llamado prstamo). Se genera como se muestra en la Figura 8.2 b). Normalmente es ALTO y no pasa a BAJO sino hasta que el contador haya contado hacia abajo hasta el estado 0000 y CPD sea BAJO. Cuando la siguiente TPP en CPD recicla el contador a 1111, ocasionando que TCD retorne a ALTO. Esta TPP en TCD se puede usar para cronometrar un segundo contador descendente 74193 en su siguiente conteo inferior.

DIRECCIN DEL CONTEO (+ o -). Las entradas CTU y CPD se muestran como dos etiquetas distintas porque tienen efectos internos diferentes. Primero se considerar la etiqueta superior. Esta etiqueta para la entrada CTU es 2+. El signo (+) indica que una TPP en esta entrada incrementar en 1 el conteo; en otras palabras, causar que el contador cuente de manera ascendente. Del mismo modo, la etiqueta superior para la entrada CPD tiene un signo (-) para sealar que esta entrada disminuye en 1 el valor del conteo; en otras palabras, causa que el conteo sea descendente.

Material necesario: Una fuente de voltaje de 5V 9 diodos emisores de luz (LED) Las siguientes resistencias: Una de 1Kohms (R1), cuatro de 220ohms (R2), una de 22Kohms (R3) y nueve de 330ohms (R5) Un preset de 1Mohm (R4) Un push botton (reset o reinicio) 2 tablillas de conexiones (protoboard) Los siguientes circuitos integrados (TTL): Un LM555, dos 74LS193, dos 74LS48, un 74LS04 y un 74LS21 Un capacitor de 1microFarad Alambre para conexiones.

Con el desarmador modificar la resistencia del preset y al mismo tiempo observar los exhibidores (display).

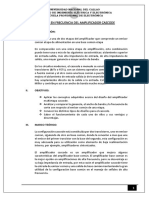

Como las salidas Q0 Q1 Q2 Q3, realizan conteo binario de 0 a 15 y para un conteo decimal nada ms se necesita de 0 a 9; entonces se le adapta una compuerta Y (AND) de 4 entradas al contador, de tal forma que cuando se encuentre el conteo en 10b (1010) se ajusta la conexin con dos inversores para poder activar la compuerta Y y su salida se utiliza para activar a MR (reiniciacin maestra), para poder llevar al contador a 0000 obteniendo un ciclo en el contador de 0 a 9. Esta misma salida invertida incrementar el contador de las decenas (contador 2). Usando el 74LS192 el diseo se hubiera facilitado mucho. De esta misma manera se obtiene el ciclo de 0 a 9 para las decenas, cual se observa en el logigrama siguiente:

Você também pode gostar

- Rectificador Monofásico SemicontroladoDocumento3 páginasRectificador Monofásico SemicontroladoWilmer Cubas Solano100% (1)

- Análisis y simulación de troceadores tipo A, B y CDocumento3 páginasAnálisis y simulación de troceadores tipo A, B y CSamuel ChimborazoAinda não há avaliações

- Proyecto 1 CircuitosDocumento39 páginasProyecto 1 CircuitosJulian MartinezAinda não há avaliações

- 5.3 Inversores CC - CA v1.8Documento17 páginas5.3 Inversores CC - CA v1.8dani385arAinda não há avaliações

- Imforme 5 (Memorias)Documento6 páginasImforme 5 (Memorias)Percy Vicente LeivaAinda não há avaliações

- Resonancia Serie - ParaleloDocumento10 páginasResonancia Serie - ParaleloDavis KailAinda não há avaliações

- Rectificador de Media Onda Controlado Por Fase Con Circuito Detector de Cruce Por CeroDocumento3 páginasRectificador de Media Onda Controlado Por Fase Con Circuito Detector de Cruce Por CeroJosward valdivia butronAinda não há avaliações

- Ejemplos Resueltos Convertidor de CukDocumento12 páginasEjemplos Resueltos Convertidor de CukRonaldRodriguezSantos0% (1)

- Práctica 6Documento14 páginasPráctica 6Calvin CantuAinda não há avaliações

- Informe 5 LABO DIGI 2 EdicionDocumento6 páginasInforme 5 LABO DIGI 2 EdicionlokilloAinda não há avaliações

- Informe de Filtros de Segundo OrdenDocumento16 páginasInforme de Filtros de Segundo OrdenjuanAinda não há avaliações

- SPWM Con PicDocumento2 páginasSPWM Con PicJef Marin0% (1)

- Fourier Media OndaDocumento6 páginasFourier Media OndaLucy Luna100% (1)

- Ejercicios ResueltosDocumento30 páginasEjercicios ResueltosJhordam Maxwell Gómez TorresAinda não há avaliações

- Criterio BarkhausenDocumento2 páginasCriterio BarkhausenChristian OlveraAinda não há avaliações

- # 4 Circuitos AstablesDocumento11 páginas# 4 Circuitos AstablesMarkito Lz100% (1)

- Lab 4 Polarizacion y EstabilizacionDocumento11 páginasLab 4 Polarizacion y EstabilizacionJhon Alex Morales VallesAinda não há avaliações

- Laboratorio Polarización Con TermistorDocumento3 páginasLaboratorio Polarización Con TermistormiguelAinda não há avaliações

- CONCLUSIONESDocumento1 páginaCONCLUSIONESkarenAinda não há avaliações

- Coria Rodrigo PRE LAB10Documento4 páginasCoria Rodrigo PRE LAB10Rodrigo CoriaAinda não há avaliações

- CPST Preparatorio5 ZambranoJ PDFDocumento8 páginasCPST Preparatorio5 ZambranoJ PDFJuan Diego Zambrano TorresAinda não há avaliações

- Control de Un ServomotorDocumento12 páginasControl de Un ServomotorGabriel Atenco100% (1)

- Adc0804 Conversor Analogo DigitalDocumento3 páginasAdc0804 Conversor Analogo DigitalRonald Däviid WarAinda não há avaliações

- Ejercicios Conversion AdcDocumento2 páginasEjercicios Conversion AdcJessica Lorena Forero Castro100% (1)

- Cuestionario Transmisión Por Modulación AMDocumento7 páginasCuestionario Transmisión Por Modulación AMMatius RapAinda não há avaliações

- Ejercicios LTXDocumento3 páginasEjercicios LTXfelipochin0% (6)

- Convertidores Cuk - ResonantesDocumento7 páginasConvertidores Cuk - ResonantesSanty FloresAinda não há avaliações

- Informe Laboratorio4 NMartinezDocumento9 páginasInforme Laboratorio4 NMartinezNicky Martinez SalazarAinda não há avaliações

- Osciladores electrónicos: tipos, circuitos y aplicacionesDocumento14 páginasOsciladores electrónicos: tipos, circuitos y aplicacionesRicardo Fossatti HernandezAinda não há avaliações

- INFORME FINAl MEDINA Ampliicador 3 EtapasDocumento13 páginasINFORME FINAl MEDINA Ampliicador 3 EtapasJean Pierre Medina YatacoAinda não há avaliações

- Control fase TRIAC DIACDocumento6 páginasControl fase TRIAC DIACManu AceAinda não há avaliações

- Ensayo"Inversor DC/AC de Onda Pura para Cargas Monofasicas A Traves de SPWM Con Microcontroladores"Documento4 páginasEnsayo"Inversor DC/AC de Onda Pura para Cargas Monofasicas A Traves de SPWM Con Microcontroladores"Jaime Potes PardoAinda não há avaliações

- Control de Un Triac Un DiacDocumento2 páginasControl de Un Triac Un DiacemimagdaAinda não há avaliações

- Contadores AsíncronosDocumento16 páginasContadores AsíncronosAlberto RuízAinda não há avaliações

- OsciladoresDocumento4 páginasOsciladoresHector Cajilema100% (1)

- Medidas de Impedancia de Entrada y SalidaDocumento8 páginasMedidas de Impedancia de Entrada y SalidaDayber Cruz100% (1)

- Informe Rectificadores ControladosDocumento9 páginasInforme Rectificadores ControladosGiovanny LduAinda não há avaliações

- Conversores ADDocumento7 páginasConversores ADPablo RafaelAinda não há avaliações

- Codigo BCDDocumento9 páginasCodigo BCDGerardo Enrique AlfonsoAinda não há avaliações

- CONTADORES Y REGISTROS ELECTRÓNICOSDocumento16 páginasCONTADORES Y REGISTROS ELECTRÓNICOSLaura VallejoAinda não há avaliações

- ADC Doble RampaDocumento5 páginasADC Doble Rampagagafefawefaef100% (1)

- Retenedor de Orden 0Documento12 páginasRetenedor de Orden 0Rodolfo Fernández GallardoAinda não há avaliações

- Comunicacion Matlab-ArduinoDocumento4 páginasComunicacion Matlab-ArduinoRichard ArturoAinda não há avaliações

- SNubberDocumento7 páginasSNubberCarlos Eduardo SalazarAinda não há avaliações

- Practica2 TermistorDocumento44 páginasPractica2 TermistorVerónica Marisol Barros BurneoAinda não há avaliações

- Convertidores de CA-CD Y CD-CADocumento16 páginasConvertidores de CA-CD Y CD-CAEnrique GarciaAinda não há avaliações

- EJERCICIOS SISTEMAS DIGITAL 2°parcialDocumento7 páginasEJERCICIOS SISTEMAS DIGITAL 2°parciallokilloAinda não há avaliações

- Aplicaciones Electrónica: Títulos de los 12 TemasDocumento13 páginasAplicaciones Electrónica: Títulos de los 12 TemasDouglas Daniel Pincay QuimiAinda não há avaliações

- Informe Final Diodos RectificadoresDocumento10 páginasInforme Final Diodos RectificadoresSergio MarceloAinda não há avaliações

- FET y MOSFET: tipos, regiones de trabajo y curvas característicasDocumento33 páginasFET y MOSFET: tipos, regiones de trabajo y curvas característicasJohana Lagla100% (2)

- Imprimir MicroDocumento10 páginasImprimir MicrorogerAinda não há avaliações

- Laboratorio 2: Espejo Sencilla de Corriente + WilsonDocumento4 páginasLaboratorio 2: Espejo Sencilla de Corriente + WilsonCarlos Hortúa CalderónAinda não há avaliações

- 3.respuesta en Frecuencia Del Amplificador CascodeDocumento9 páginas3.respuesta en Frecuencia Del Amplificador Cascodecarolina abigail jimenez cortezAinda não há avaliações

- Introducción MATLAB SIMULINK control estabilidadDocumento8 páginasIntroducción MATLAB SIMULINK control estabilidadLoanAinda não há avaliações

- Subestacion Villa Tunari Christian Marquez Coordinacion Distancias ApantallamientoDocumento26 páginasSubestacion Villa Tunari Christian Marquez Coordinacion Distancias Apantallamientojesus marquez arvaez50% (2)

- PRACTICA 9 Contadores EJ10Documento4 páginasPRACTICA 9 Contadores EJ10Leobardo Genaro Roque NájeraAinda não há avaliações

- Contador Binario de 4 y 8 BitsDocumento7 páginasContador Binario de 4 y 8 BitsAlan VazquezAinda não há avaliações

- Practica 8Documento6 páginasPractica 8janeth grAinda não há avaliações

- Práctica 8Documento8 páginasPráctica 8Vicente IriarteAinda não há avaliações

- Cont AdoresDocumento9 páginasCont AdoresSprawlgraffeAinda não há avaliações