Escolar Documentos

Profissional Documentos

Cultura Documentos

Amd 2910

Enviado por

Arturo ZanettiDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Amd 2910

Enviado por

Arturo ZanettiDireitos autorais:

Formatos disponíveis

Prez Arcos Jorge Arturo 208333378

Secuenciador AMD2910

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; use ieee.numeric_std.all; entity Registro_cont is port( D : in std_logic_vector(11 downto 0); RLD, CLK : in std_logic; DEC_HOLD_LOAD: in std_logic_vector(1 downto 0); R : out std_logic_vector(11 downto 0); ZERO : out std_logic ); end Registro_cont; architecture Behavioral of Registro_cont is signal REG: std_logic_vector(11 downto 0); begin process(CLK, RLD) begin if CLK'event and CLK = '1' then if RLD = '0' then REG <= D; elsif DEC_HOLD_LOAD = "00" then REG <= D; elsif DEC_HOLD_LOAD = "01" then REG <= REG; elsif DEC_HOLD_LOAD = "10" then REG <= REG-1; end if; end if; end process; R <= REG; with REG select ZERO <= '0' when "000000000000", '1' when others; end Behavioral;

library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity Instruction_Pila is port( CC, CCEN, R: in std_logic; I: in std_logic_vector(3 downto 0); PL, MAPP, VECT: out std_logic; DEC_HOLD_LOAD, SELECTT, PUSH_POP_HOLD_CLEAR, std_logic_vector(1 downto 0) ); end Instruction_Pila; architecture Behavioral of Instruction_Pila is signal temp: std_logic_vector(10 downto 0); begin process(I, CC, CCEN, R) begin case I is when "0000" => temp <= "10001110011"; when "0001" => if CCEN = '0' and CC = '1' then temp <= "10001000100"; elsif CCEN = '1' or CC = '0' then temp <= "10001111100"; end if; when "0010" => temp <= "01001110111"; when "0011" => if CCEN = '0' and CC = '1' then temp <= "10001000100"; elsif CCEN = '1' or CC = '0' then temp <= "10001110100"; end if; when "0100" => if CCEN = '0' and CC = '1' then temp <= "10001001100"; elsif CCEN = '1' or CC = '0' then temp <= "10000001100"; end if; when "0101" => if CCEN = '0' and CC = '1' then temp <= "10001101100";

CLEAR_COUNT:

out

elsif CCEN = '1' or CC = '0' then temp <= "10001111100"; end if; when "0110" => if CCEN = '0' and CC = '1' then temp <= "00101000100"; elsif CCEN = '1' or CC = '0' then temp <= "00101110100"; end if; when "0111" => if CCEN = '0' and CC = '1' then temp <= "10001100111"; elsif CCEN = '1' or CC = '0' then temp <= "10001110111"; end if; when "1000" => if R = '1' then temp <= "10010010111"; else temp <= "10001001000"; end if; when "1001" => if R = '1' then temp <= "10010110111"; else temp <= "10001000100"; end if; when "1010" => if CCEN = '0' and CC = '1' then temp <= "10001000100"; elsif CCEN = '1' or CC = '0' then temp <= "10001011000"; end if; when "1011" => if CCEN = '0' and CC = '1' then temp <= "10001000100"; elsif CCEN = '1' or CC = '0' then temp <= "10001111000"; end if; when "1100" => temp <= "10000000100"; when "1101" => if CCEN = '0' and CC = '1' then temp <= "10001010100"; elsif CCEN = '1' or CC = '0' then temp <= "10001001000"; end if; when "1110" => temp <= "10001000100"; when others => if R = '1' then if CCEN = '0' and CC = '1' then

temp <= "10010010100"; elsif CCEN = '1' or CC = '0' then temp <= "10010001000"; end if; else if CCEN = '0' and CC = '1' then temp <= "10001111000"; elsif CCEN = '1' or CC = '0' then temp <= "10001001000"; end if; end if; end case; end process; PL <= temp(10); MAPP <= temp(9); VECT <= temp(8); DEC_HOLD_LOAD <= temp(7 downto 6); SELECTT <= temp(5 downto 4); PUSH_POP_HOLD_CLEAR <= temp(3 downto 2); CLEAR_COUNT <= temp(1 downto 0); end Behavioral;

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; use ieee.numeric_std.all; entity Multiplexor is port( D, R, F, PC: in std_logic_vector(11 downto 0); SELECTT: in std_logic_vector(1 downto 0); Y: out std_logic_vector(11 downto 0)

); end Multiplexor; architecture Behavioral of Multiplexor is begin process(D, R, F, PC, SELECTT) begin case SELECTT is when "00" => Y <= PC; when "01" => Y <= F; when "10" => Y <= R; when others => Y <= D; end case; end process; end Behavioral;

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; use ieee.numeric_std.all; entity Incrementer is port( Y: in std_logic_vector(11 downto 0); CI, CLK: in std_logic; CLEAR_COUNT: in std_logic_vector(1 downto 0); PC: out std_logic_vector(11 downto 0) ); end Incrementer; architecture Behavioral of Incrementer is signal TEMP: std_logic_vector(11 downto 0); begin process(CLK, CLEAR_COUNT, Y) begin if CLK'event and CLK = '1' then if CLEAR_COUNT = "00" then TEMP <= Y+CI;

elsif CLEAR_COUNT = "01" then TEMP <= "000000000000"; end if; end if; end process; PC <= TEMP; end Behavioral;

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; use ieee.numeric_std.all; entity Pila9x12 is port( PC: in std_logic_vector(11 downto 0); CLK: in std_logic; PUSH_POP_HOLD_CLEAR: in std_logic_vector(1 downto 0); FULL: out std_logic; F: out std_logic_vector(11 downto 0) ); end Pila9x12; architecture Behavioral of Pila9x12 is signal SP: std_logic_vector(3 downto 0) := (others => '0'); signal FLAG: std_logic; signal TEMP: std_logic := '1'; type REG is array(0 to 8) of STD_LOGIC_VECTOR(11 downto 0); signal PILA : REG; begin process(PC, CLK) begin if CLK'event and CLK = '1' then if PUSH_POP_HOLD_CLEAR = "00" then SP <= "0000"; TEMP <= '1'; elsif PUSH_POP_HOLD_CLEAR = "01" then

SP <= SP; elsif PUSH_POP_HOLD_CLEAR = "10" then if SP = "0000" then F <= PILA(conv_integer(SP)); TEMP <= '1'; elsif SP > "0000" and SP < "1001" then F <= PILA(conv_integer(SP)); SP <= SP-1; end if; else if SP = "0000" then if TEMP = '1' then PILA(conv_integer(SP)) <= PC; SP <= "0000"; TEMP <= '0'; else PILA(conv_integer(SP+1)) <= PC; SP <= SP+1; end if; else if FLAG = '1' then PILA(conv_integer(SP+1)) <= PC; SP <= SP+1; else PILA(0) <= PC; end if; end if; end if; end if; end process; process(SP) begin if SP = "1000" then FLAG <= '0'; else FLAG <= '1'; end if; end process; FULL <= FLAG; end Behavioral;

Você também pode gostar

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNo EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNota: 4 de 5 estrelas4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNo EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNota: 4 de 5 estrelas4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItNo EverandNever Split the Difference: Negotiating As If Your Life Depended On ItNota: 4.5 de 5 estrelas4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNo EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNota: 4 de 5 estrelas4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNo EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNota: 4.5 de 5 estrelas4.5/5 (344)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNo EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNota: 4.5 de 5 estrelas4.5/5 (474)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)No EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Nota: 4.5 de 5 estrelas4.5/5 (121)

- The Emperor of All Maladies: A Biography of CancerNo EverandThe Emperor of All Maladies: A Biography of CancerNota: 4.5 de 5 estrelas4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingNo EverandThe Little Book of Hygge: Danish Secrets to Happy LivingNota: 3.5 de 5 estrelas3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyNo EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyNota: 3.5 de 5 estrelas3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)No EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Nota: 4 de 5 estrelas4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNo EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNota: 4.5 de 5 estrelas4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNo EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNota: 3.5 de 5 estrelas3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnNo EverandTeam of Rivals: The Political Genius of Abraham LincolnNota: 4.5 de 5 estrelas4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaNo EverandThe Unwinding: An Inner History of the New AmericaNota: 4 de 5 estrelas4/5 (45)

- Method Statement FINALDocumento61 páginasMethod Statement FINALshareyhou67% (3)

- Economics Exam Technique GuideDocumento21 páginasEconomics Exam Technique Guidemalcewan100% (5)

- PM 50 Service ManualDocumento60 páginasPM 50 Service ManualLeoni AnjosAinda não há avaliações

- ABHA Coil ProportionsDocumento5 páginasABHA Coil ProportionsOctav OctavianAinda não há avaliações

- Law of AttractionDocumento2 páginasLaw of AttractionKate SummersAinda não há avaliações

- SY22-23+Annual+Report FinalDocumento47 páginasSY22-23+Annual+Report FinalNorus LizaAinda não há avaliações

- DP-1520 PMDocumento152 páginasDP-1520 PMIon JardelAinda não há avaliações

- Affidavit of Co OwnershipDocumento2 páginasAffidavit of Co OwnershipEmer MartinAinda não há avaliações

- Monitor 14sepDocumento2 páginasMonitor 14sepabhaymvyas1144Ainda não há avaliações

- FINAL VERSION On Assessment Tool For CDCs LCs Sept. 23 2015Documento45 páginasFINAL VERSION On Assessment Tool For CDCs LCs Sept. 23 2015Edmar Cielo SarmientoAinda não há avaliações

- An Analysis of Students' Error in Using Possesive Adjective in Their Online Writing TasksDocumento19 páginasAn Analysis of Students' Error in Using Possesive Adjective in Their Online Writing TasksKartika Dwi NurandaniAinda não há avaliações

- Present Tenses ExercisesDocumento4 páginasPresent Tenses Exercisesmonkeynotes100% (1)

- Celula de CargaDocumento2 páginasCelula de CargaDavid PaezAinda não há avaliações

- Data Science ProjectsDocumento3 páginasData Science ProjectsHanane GríssetteAinda não há avaliações

- Visi RuleDocumento6 páginasVisi RuleBruce HerreraAinda não há avaliações

- Prediction of CBR From Index Properties of Cohesive Soils: Magdi ZumrawiDocumento1 páginaPrediction of CBR From Index Properties of Cohesive Soils: Magdi Zumrawidruwid6Ainda não há avaliações

- Consumer Protection ActDocumento34 páginasConsumer Protection ActshikhroxAinda não há avaliações

- Kiraan Supply Mesin AutomotifDocumento6 páginasKiraan Supply Mesin Automotifjamali sadatAinda não há avaliações

- Properties of WaterDocumento23 páginasProperties of WaterNiken Rumani100% (1)

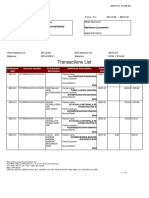

- Transactions List: Marilena Constantin RO75BRDE445SV93146784450 RON Marilena ConstantinDocumento12 páginasTransactions List: Marilena Constantin RO75BRDE445SV93146784450 RON Marilena ConstantinConstantin MarilenaAinda não há avaliações

- Stratum CorneumDocumento4 páginasStratum CorneumMuh Firdaus Ar-RappanyAinda não há avaliações

- Chemical & Ionic Equilibrium Question PaperDocumento7 páginasChemical & Ionic Equilibrium Question PapermisostudyAinda não há avaliações

- Communication Skill - Time ManagementDocumento18 páginasCommunication Skill - Time ManagementChấn NguyễnAinda não há avaliações

- Abas Drug Study Nicu PDFDocumento4 páginasAbas Drug Study Nicu PDFAlexander Miguel M. AbasAinda não há avaliações

- Entrepreneurship - PPTX Version 1 - Copy (Autosaved) (Autosaved) (Autosaved) (Autosaved)Documento211 páginasEntrepreneurship - PPTX Version 1 - Copy (Autosaved) (Autosaved) (Autosaved) (Autosaved)Leona Alicpala67% (3)

- Joomag 2020 06 12 27485398153Documento2 páginasJoomag 2020 06 12 27485398153Vincent Deodath Bang'araAinda não há avaliações

- Catalogo PukangDocumento41 páginasCatalogo PukangClarita Muller LeigueAinda não há avaliações

- Diagnosis ListDocumento1 páginaDiagnosis ListSenyorita KHayeAinda não há avaliações

- Caroline Coady: EducationDocumento3 páginasCaroline Coady: Educationapi-491896852Ainda não há avaliações

- Actron Vismin ReportDocumento19 páginasActron Vismin ReportSirhc OyagAinda não há avaliações