Escolar Documentos

Profissional Documentos

Cultura Documentos

AnalogICAssignmt02 sp2012

Enviado por

gnawazbuttDescrição original:

Título original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

AnalogICAssignmt02 sp2012

Enviado por

gnawazbuttDireitos autorais:

Formatos disponíveis

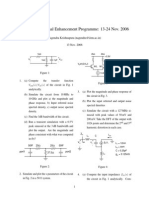

Assignment # 02 Last Date of submission: 30-03-2012

Subject: Analog IC Design Semester: Spring 2012

Problem 01. Using the open-circuit and short-circuit time-constant method, find the two poles of the circuit

shown below (assuming that the poles are far apart from each other).

0

= 1uu, I

c

= u.S mA,

1

= 1 0Ez, C

=

u.2 pF, I

1

= 26 mI, R

L

= 1u k, R

L

= 1.S k .

Problem 02 Derive an expression for the voltage gain for the circuit for the given numerical values and plot the

gain in dBs versus frequency on the semilog-graph paper. From the plot, find the half power and frequency.

0

= 1uu, g

m

= 1u mS, C

= 1 pF, C

n

= 1u pF, C

L

= 1u pF R

L

= 1u k, R

I

= 1 k.

Problem 03 Draw the small signal model for the MOS-transistor shown in the figure, at high frequency and

derive the expression the for the voltage gain. Compute the location of the two poles for the numerical values

R

I

= 1 k, R

L

= 1u kobm, g

m

= 1 mS, C

gs

= S pF, C

gd

= 1 pF. Ignore r

ds

.

Problem 04 Find, for given numerical values, the all poles and the midband gain of the transfer function v

out

/v

in

of the differential amplifier shown. Assume that K

N

i

= 11u AI

2

, I

1N

= u.7 I,

N

= u.u4 I

-1

, C

gs

=

u.2 pF, C

gd

= 2u F. Determine also the common mode rejection ratio (CMRR).

C

I

R

L

R

L

C

out

V

v

m

g

C

r

I

R

L

R out

V

1

v

m

g

1

v in

V

v

Problem 05 Derive expressions for output resistance R

o

and currents I

o

for each of the BJT current mirrors:

Problem 06 Repeat problem 05 for the MOS Transistors current sources.

in

I

o

I

in

I

o

I

in

I

o

I

Hint: the equivalent of the half circuit

is shown below, where v

id

= v

in

and

v

od

= v

out

.

R

1

Q

2

Q

1

Q

2

Q

4

Q

3

Q

1

Q

2

Q

3

Q

in

I

o

I

in

I

o

I

in

I

o

I

1

M

2

M

1

M

2

M 4

M

3

M 1

M

2

M

3

M

3

M

6

M

5

M

4

M

Você também pode gostar

- MIT6 012S09 Ex03 Final 07Documento18 páginasMIT6 012S09 Ex03 Final 07Gopi KrishnaAinda não há avaliações

- Task - 1 (Assessment - 3)Documento3 páginasTask - 1 (Assessment - 3)Dhinakaran BalakrishnanAinda não há avaliações

- End Term E3 238Documento6 páginasEnd Term E3 238bommena vishwa tejaAinda não há avaliações

- 13 - Analysis and Design of A Two-Stage CMOS Operational Amplifier in 150 NM TechnologyDocumento6 páginas13 - Analysis and Design of A Two-Stage CMOS Operational Amplifier in 150 NM Technologysohailasghar_tAinda não há avaliações

- University of Edinburgh College of Science and Engineering School of Engineering and ElectronicsDocumento15 páginasUniversity of Edinburgh College of Science and Engineering School of Engineering and ElectronicsSyed Fasih Ur RehmanAinda não há avaliações

- Mec 10ec63 Ssic Unit3Documento10 páginasMec 10ec63 Ssic Unit3Noorullah ShariffAinda não há avaliações

- Electronics MQP Ii Puc 2023-24Documento4 páginasElectronics MQP Ii Puc 2023-24sanjaykashiAinda não há avaliações

- Elettu Darmstadt SampleDocumento4 páginasElettu Darmstadt SampleMuhammad Abuzer ImranAinda não há avaliações

- Blue Print For: Model Question PaperDocumento8 páginasBlue Print For: Model Question PaperfrosterapAinda não há avaliações

- Frequency Multipilier Using A Charge-Storage Diode in An Inductive CircuitDocumento2 páginasFrequency Multipilier Using A Charge-Storage Diode in An Inductive CircuitharishkumarsinghAinda não há avaliações

- Series RC Circuit: Electrical and Electronic EngineeringDocumento7 páginasSeries RC Circuit: Electrical and Electronic Engineeringخہٰہٰالہٰد ۦ' ۦ'Ainda não há avaliações

- EC3058D-VLSI Circuits and Systems Winter Semester-2020-21Documento2 páginasEC3058D-VLSI Circuits and Systems Winter Semester-2020-21Gamer AnonymousAinda não há avaliações

- Electronics: June/July, 2010Documento7 páginasElectronics: June/July, 2010Prasad C MAinda não há avaliações

- Questions On Small Signal Model of AmpDocumento2 páginasQuestions On Small Signal Model of AmpdevsrivastavaAinda não há avaliações

- CBSE Board-XII Physics - Paper - SolutionDocumento15 páginasCBSE Board-XII Physics - Paper - SolutionMichelle DennisAinda não há avaliações

- Electrical, Digital and Industrial Circuits: Second Sequence ExamDocumento4 páginasElectrical, Digital and Industrial Circuits: Second Sequence ExamNGOUNEAinda não há avaliações

- Bài Tập Số 4 - Tiểu Luận: Trường Đại Học Tôn Đức Thắng Khoa Điện - Điện TửDocumento25 páginasBài Tập Số 4 - Tiểu Luận: Trường Đại Học Tôn Đức Thắng Khoa Điện - Điện TửNguyễn Hồng HạnhAinda não há avaliações

- No 1Documento7 páginasNo 1Basel HantashAinda não há avaliações

- UBC ELEC 301 MP Report 4Documento7 páginasUBC ELEC 301 MP Report 4ednangiaAinda não há avaliações

- Ex 05 STS1 RedresseursDocumento35 páginasEx 05 STS1 RedresseursRajhiHoussem100% (2)

- Analog Integrated Circuits Exercise 4: Common-Source and Differential AmplifiersDocumento9 páginasAnalog Integrated Circuits Exercise 4: Common-Source and Differential Amplifiersubuntu 13.04Ainda não há avaliações

- Tutorial 5Documento10 páginasTutorial 5bayman66Ainda não há avaliações

- RF Electronic Preparatory Ii: Amplifier and Filter Laboratory ExerciseDocumento12 páginasRF Electronic Preparatory Ii: Amplifier and Filter Laboratory ExercisesvinqtaAinda não há avaliações

- SMDP Instructional Enhancement Programme: 13-24 Nov. 2006: Nagendra Krishnapura (Nagendra@iitm - Ac.in) 13 Nov. 2006Documento2 páginasSMDP Instructional Enhancement Programme: 13-24 Nov. 2006: Nagendra Krishnapura (Nagendra@iitm - Ac.in) 13 Nov. 2006alkjhlkjlkAinda não há avaliações

- 07 08 II ms2Documento6 páginas07 08 II ms2Mahmoud FariedAinda não há avaliações

- E5 Post-LabDocumento4 páginasE5 Post-LabBea DucaoAinda não há avaliações

- Push Pull Ampilfier - c9Documento4 páginasPush Pull Ampilfier - c9quynh04cdt1Ainda não há avaliações

- Physics (Theory) : General Instructions: All Questions Are CompulsoryDocumento7 páginasPhysics (Theory) : General Instructions: All Questions Are CompulsoryJames RossAinda não há avaliações

- Solving Differential Equation Using OPAMPDocumento4 páginasSolving Differential Equation Using OPAMPRekhamtrAinda não há avaliações

- Lab 2Documento4 páginasLab 2Muhammad TehreemAinda não há avaliações

- LAB Manual - Modern Physics - Cycle-2 ExperimentsDocumento14 páginasLAB Manual - Modern Physics - Cycle-2 ExperimentsTobiAinda não há avaliações

- Preboard Practical Exam Answersheet Ele1Documento15 páginasPreboard Practical Exam Answersheet Ele1Rounak PagareAinda não há avaliações

- 2 in One LabDocumento5 páginas2 in One LabEnock KachokolaAinda não há avaliações

- 10 12 Physics CBSE Paper SolutionDocumento20 páginas10 12 Physics CBSE Paper SolutionnafehakhanAinda não há avaliações

- Electromagnetic Waves in Guided Media: Cristian VillegasDocumento18 páginasElectromagnetic Waves in Guided Media: Cristian VillegasCristian VillegasAinda não há avaliações

- Exp 4Documento7 páginasExp 4mohmmad othmanAinda não há avaliações

- Exercise 2Documento3 páginasExercise 2momolololilo4Ainda não há avaliações

- 電子學 (三) 蕭敏學1Documento21 páginas電子學 (三) 蕭敏學1scribbyscribAinda não há avaliações

- Homework Assignment 8 SolutionDocumento8 páginasHomework Assignment 8 SolutionKL Chiang100% (1)

- Zero and Span CircuitsDocumento2 páginasZero and Span CircuitsMourougapragash Subramanian100% (1)

- EEC110A Win 2010 Final Exam: Name: ID #Documento35 páginasEEC110A Win 2010 Final Exam: Name: ID #Zoro ZhaoAinda não há avaliações

- AS-74.4180 Automatic Modelling of Industrial Plants Using Semantic SpecificationsDocumento24 páginasAS-74.4180 Automatic Modelling of Industrial Plants Using Semantic SpecificationsAram SimonianAinda não há avaliações

- L #1: T F R S C: Sfsu - E 301 - E L AB Ime and Requency Esponses of Eries IrcuitsDocumento8 páginasL #1: T F R S C: Sfsu - E 301 - E L AB Ime and Requency Esponses of Eries IrcuitsRudra MishraAinda não há avaliações

- Eece251 Final Exam 2010Documento2 páginasEece251 Final Exam 2010VikasAroraAinda não há avaliações

- Q1. Cellular Mobile Communication System: N I Ij+ JDocumento13 páginasQ1. Cellular Mobile Communication System: N I Ij+ JSifun PadhiAinda não há avaliações

- Series & Parallel Circuiting of Capacitors: Ctot C1 C2 + CNDocumento5 páginasSeries & Parallel Circuiting of Capacitors: Ctot C1 C2 + CNمحمد زبنAinda não há avaliações

- 12 2005 Physics 4Documento4 páginas12 2005 Physics 4ShubhamBhardwajAinda não há avaliações

- Exam Questions-Section 1Documento38 páginasExam Questions-Section 1Gecca VergaraAinda não há avaliações

- Exercises in Electronics: Operational Amplifier CircuitsNo EverandExercises in Electronics: Operational Amplifier CircuitsNota: 3 de 5 estrelas3/5 (1)

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1No EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Nota: 4.5 de 5 estrelas4.5/5 (3)

- Fundamentals of Electronics 1: Electronic Components and Elementary FunctionsNo EverandFundamentals of Electronics 1: Electronic Components and Elementary FunctionsAinda não há avaliações

- Electronic Devices and Circuits: The Commonwealth and International Library: Electrical Engineering Division, Volume 1No EverandElectronic Devices and Circuits: The Commonwealth and International Library: Electrical Engineering Division, Volume 1Ainda não há avaliações

- Audio IC Circuits Manual: Newnes Circuits Manual SeriesNo EverandAudio IC Circuits Manual: Newnes Circuits Manual SeriesNota: 5 de 5 estrelas5/5 (1)

- Feynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterNo EverandFeynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterAinda não há avaliações