Escolar Documentos

Profissional Documentos

Cultura Documentos

On-Chip Implementation of High Speed and High Resolution Pipeline Radix 2 FFT Algorithm

Enviado por

Dr. Rozita teymourzadeh, CEng.Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

On-Chip Implementation of High Speed and High Resolution Pipeline Radix 2 FFT Algorithm

Enviado por

Dr. Rozita teymourzadeh, CEng.Direitos autorais:

Formatos disponíveis

On-Chip Implementation of High Speed and High resolution Pipeline Radix 2 FFT Algorithm

N. Mahdavi, R. Teymourzadeh, IEEE Student Member, Masuri Bin Othman

Arak university, Iran, VLSI Design Center, Institute of Microengineering and Nanoelectronics (IMEN) Universiti Kebengsaan Malaysia, 43600 Bangi, Selangor, Malaysia mahdavi_n2@yahoo.com , rozita60@vlsi.eng.ukm.my , masuri@vlsi.eng.ukm.my

Abstract- A new on-chip implementation of Fast Fourier Transform (FFT) based on Radix 2 is presented. The pipeline and parallel approaches are combined to introduce a new high speed FFT algorithm which increases resolution by using floating point calculations in its structures. The design has the merits of low complexity and high speed performance. Furthermore, latency reduction is an important issue to implement the high speed FFT on FPGA. The proposed FFT algorithm shows the latency of N 2 log 2 N 11 . Moreover, this algorithm has the advantage of low mean squared error (MSE) of 0.0001 which is preferable to Radix 2 FFT.

The proposed method shows high performance of the FFT algorithm. The principle architecture is based on using a memory to keep input and output data. Thus, it reduces hard ware complexity. All the blocks are designed to operate with the same clock frequency. These stages implement as pipeline and parallel to reduce FFT calculations time. III. FFT BLOCK DIAGRAM DESCRIPTION Fig. 1, shows the main block diagram of the FFT algorithm. Each block will be investigated separately. A. Radix-2 Butterfly Algorithm First, the RAM is initialized by external microprocessor and the data are loaded to the RAM by bit reserve address pin. The Radix 2 Butterfly block is the primary prefatory step taken in DIT FFT [8,9]. This block calculates the complex number in (1) and (2), as follow.

I.

INTRODUCTION

Fast Fourier transform is a faster version of DFT which was invented by Cooley & Tuky in 1965 [1]. There are several types of FFT algorithms. Radix-2 is a practical algorithm to calculate FFT by using decimation in time (DIT) method. The main idea of decimation in time is to sunder the input string of hn with length of N 2 v into two substrings with odd and even indexes. The N-point DFT of hn can be achieved by suitable combining to N 2 -point DFT of each substring. Each one of them can be reduced to N 4 -point DFTs. This procedure will continue till only 2-point DFTs remains [2]. The final result is the formation of FFT algorithm. In 2006 petrovsky [3] implemented Radix 2-4 based on parallel-pipeline FFT-processors at structural level. He achieved 0.00201 MSE on his FFT algorithm. This paper shows the implementation of high speed and high resolution FFT based on parallel pipeline and floating point Radix-2 with the minimum MSE of 0.0001. The next section describes the principle of the FFT structure. The mathematical formulation and block diagram of pipeline FFT algorithm is described in section III. Section IV shows implementation and design result in brief. Finally, conclusion is expressed in section V. II. PRINCIPLE OF THE FFT STRUCTURE The computation of N-point FFT via decimation-in-time algorithm requires ON log 2 N complex multiplication time [7] and it will be increased if basic butterfly computation is used for adder and multiplication in decimation-in-time FFT algorithm. Additionally a complicated controller is also required. Furthermore, implementing fixed point FFT algorithm, results the output differs significantly in comparison to the expected output. To obtain the high speed and high resolution FFT algorithm, implementation of the floating point pipeline FFT is applied.

output1 input1 W k input 2

(1) (2)

output 2 input1 W input 2

k

Figure 1. The FFT block diagram

Hence, one complex multiplication and two complex additions are required in this calculation. If output1 X 01 iYo1 , output 2 X o 2 iYo 2 and

W k X wk iYW k we have:

X o1 iYo1 X i1 X W k X i 2 YW k Yi 2

X o 2 iYo 2 X i1 X W k X i 2 YW k Yi 2

iYi1 X W k Yi 2 YW k X i 2

(3) (4)

iYi1 X W k Yi 2 YW k X i 2

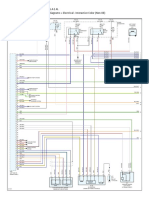

Thus, each butterfly requires four real multiplications and six real additions. If the above equations are implemented using fixed point calculations, the error possibility of the result will increase. These errors [4] consist of round-off, overflow and coefficient quantization errors. To reduce the errors and provide high resolution, floating point adder/subtractor is replaced. This adder/subtractor operates in 3 stages including mantis alignment, mantis addition/ subtraction and normalization. Thus, each of the above phases can be used as stages for pipeline implementation. We convert the first phase into two stages in order to achieve higher clock frequency [5], [6]. Fig. 2, and Fig. 3, show the block diagram of the pipeline adder/subtractor and multiplier. It is not necessary to adjust the exponents in multiplier. Since the normalized inputs are loaded to the multiplier, the mantises are multiplied and the exponents are added and amended. The result may be shifted one bit leftward. Thus the exponent will be decremented one unit.

Fig. 4, shows the internal schematic of the pipeline butterfly algorithm. To improve speed calculations in the Radix-2 butterfly algorithm, the pipeline registers are located after each addition, subtraction and multiplication blocks. Hence, the pipeline butterfly algorithm keeps the final result in the register to transfer it to the RAM by the next clock cycle. This FFT algorithm is exactly executed after N 2 Log 2 N 11 clock pulses. The 11 clock pulses delay is created by 11 pipeline registers in adder, subtractor and multiplier in a serial butterfly block. Additionally, parallel design of the FFT algorithm decreases the calculation time significantly. B. ROM and RAM Blocks The ROM in Radix-2 FFT algorithm has two look-up k tables to save W coefficients. These coefficients are inherently complex numbers so the real & imaginary parts are separately kept on that. Since the amplitude of the sine and cosine are the same in the four quarters, (they only k differ in the signs) W are calculated just for k 0 to k N 4 and related sign are saved for k 0 to N into the ROM. Thus, it avoids using a large number of gates in the FPGA board. There is a RAM in the FFT block diagram. According to the system workflow, two complex data must be read from the RAM simultaneously and loaded to the butterfly block. Meanwhile, the two outputs of the butterfly block have to be written in the RAM at the same time. Fig. 5, shows the internal structure of the RAM with the capability of reading and writing the two complex data simultaneously.

Figure 2. Pipeline floating point adder/ subtractor

Figure 3. Pipeline floating point multiplier

Figure 5. Internal structure of the RAM

Figure 4. Internal schematic of the pipeline butterfly algorithm

IV. IMPLEMENTATION RESULT The new architecture of the Radix-2 FFT algorithm Verilog code was written and simulated by Matlab software. The design code is downloaded to the Virtax-2 FPGA board. From Xilinx ISE synthesize report, it was shown minimum clock period is 9.94 ns (Maximum Frequency is 100.6 MHz). The chip layout on Virtex 2 FPGA board is shown in Fig. 6. Fig. 7, shows the output digital signal of the new Radix-2 FFT algorithm which simulated by Modelsim software. Fig. 8, shows the measured signal spectrum achieved by Radix-2 FFT algorithm for 1024 floating point complex data.

The output result appeared after 5131 clock pulses which proved the complex calculation of N 2 log 2 N 11 in the system. The System MSE was measured by Matlab software. It shows the mean squared error (MSE) of 0.0001.

V.

CONCLUSION

The new architecture of the high speed and high resolution of the parallel, pipeline and floating point Radix2 FFT algorithm was designed and investigated. High Speed FFT architecture was obtained by two methods. The pipeline structure and parallel design lead us to have high speed FFT algorithm. Additionally, using a internal RAM makes the design compatible with different type of FPGA board. The implementation result shows the maximum throughput of the 100.6 MHz in Virtex 2 FPGA board. Meanwhile, the resolution was increased by floating point calculation during the FFT process. The proposed FFT algorithm proves the latency of N 2 Log 2 N 11 , 5131 clock pulses for N 1024 with the mean squared error (MSE) of 0.0001. ACKNOWLEDGMENT We wish to thank our friend, Dr. Mohamad Amir Amini who has assisted us for completion of this dissertation. REFERENCES

[1] J. W. Cooley, J. W. Tukey, An Algorithm for the Machine Calculation of Complex Fourier series," Math of comp Vol. 19, pp. 297-301, 1965. A. Saidi, Decimation-in-time frequency FFT algorithm. Acoustics, Speech, and Signal Processing , ICASS-94, IEEE International Conference. Vol. 3, pp. 453-456, 1994 A.A. Petrovsky, S. L. Shkredov, Automatic Generation of SplitRadix 2-4 Parallel-Pipeline FFT Processors: Hardware Reconfiguration and Core Optimization, Proceeding of the international symposium on parallel computing in Electrical engineering (PARELEC06), pp.181-186, 2006. E. C. Ifeachor, B. V. Jervis, Digital Signal Processing: A Practical Approch. Second Editiond. Prantice Hall, 2002. M. Morris Mano, Computer System Architectur. Third Edition. Prantice Hall. 1992. D. A. Patterson & J. L. Hennssy. Computer Organization & Design: the Hardware/ Software Interface. Second Edition. Morgan Kaufman Publishere Inc. 1998. Lo sing Cheng, A. Miri, Tet Hinb Yeap, Efficient FPGA Implementation of FFT based Multipliers, IEEE Conference Electrical and Computer Engineering, pp. 1300-1303, 2005. K. S. Hemmert, K. D. Underwood, An Analysis of The DoublePrecision Floating-point FFT on FPGAs, 13th IEEE Symposium on Field-Programmable Custom Computing Machines, pp. 171-180, April 2005. Shiqun Zheng, Dunshan Yu, Design and implementation of a parallel real-time FFT processor, 7th IEEE conference on Solid-State and Integrated Circuits Technology, Vol. 3, pp. 165-168, Oct 2004.

Figure 6. The core layout on FPGA board

[2] [3]

[4] [5] [6] [7] Figure 7. The output digital signal of the system [8]

30

[9]

25

20

Signal Amplitude

15

10

2000

4000

6000 8000 Frequency (Hz)

10000

12000

14000

Figure 8. Signal spectrum of high speed radix-2 FFT algorithm

Você também pode gostar

- Tyron Butson (Order #37627400)Documento74 páginasTyron Butson (Order #37627400)tyron100% (2)

- Introduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationNo EverandIntroduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationAinda não há avaliações

- Railway RRB Group D Book PDFDocumento368 páginasRailway RRB Group D Book PDFAshish mishraAinda não há avaliações

- Multiple Choice Question (MCQ) of Alternator and Synchronous Motors PageDocumento29 páginasMultiple Choice Question (MCQ) of Alternator and Synchronous Motors Pagekibrom atsbha0% (1)

- LTE Signaling: Troubleshooting and Performance MeasurementNo EverandLTE Signaling: Troubleshooting and Performance MeasurementAinda não há avaliações

- UW Computational-Finance & Risk Management Brochure Final 080613Documento2 páginasUW Computational-Finance & Risk Management Brochure Final 080613Rajel MokAinda não há avaliações

- FFTDocumento4 páginasFFTJasim ArAinda não há avaliações

- Efficient FPGA Implementation of FFT/IFFT Processor: Ahmed Saeed, M. Elbably, G. Abdelfadeel, and M. I. EladawyDocumento8 páginasEfficient FPGA Implementation of FFT/IFFT Processor: Ahmed Saeed, M. Elbably, G. Abdelfadeel, and M. I. Eladawyfadhil78Ainda não há avaliações

- Implementation of Fast Fourier Transform (FFT) On FPGA Using Verilog HDLDocumento21 páginasImplementation of Fast Fourier Transform (FFT) On FPGA Using Verilog HDLNikitaPrabhu0% (1)

- International Journal of Engineering Research and DevelopmentDocumento5 páginasInternational Journal of Engineering Research and DevelopmentIJERDAinda não há avaliações

- Design and Implementation of Pipelined FFT Processor: D.Venkata Kishore, C.Ram KumarDocumento4 páginasDesign and Implementation of Pipelined FFT Processor: D.Venkata Kishore, C.Ram KumarShakeel RanaAinda não há avaliações

- Design and Simulation of 32-Point FFT Using Radix-2 Algorithm For FPGA 2012Documento5 páginasDesign and Simulation of 32-Point FFT Using Radix-2 Algorithm For FPGA 2012mohamedAinda não há avaliações

- Implementation of Efficient 64-Point FFT/IFFT Block For OFDM Transreciever of IEEE 802.11aDocumento6 páginasImplementation of Efficient 64-Point FFT/IFFT Block For OFDM Transreciever of IEEE 802.11aInternational Journal of Application or Innovation in Engineering & ManagementAinda não há avaliações

- Frequency AnalyzerDocumento4 páginasFrequency AnalyzerJosnaveAinda não há avaliações

- VLSI Implementation of Pipelined Fast Fourier TransformDocumento6 páginasVLSI Implementation of Pipelined Fast Fourier TransformIjarcet JournalAinda não há avaliações

- A Low Power Radix-2 FFT Accelerator For FPGADocumento5 páginasA Low Power Radix-2 FFT Accelerator For FPGAMuhammad Majid AltafAinda não há avaliações

- On-Chip Implementation of High Resolution High Speed Low Area Floating Point AdderSubtractor With Reducing Mean Latency For OFDM ApplicationsDocumento6 páginasOn-Chip Implementation of High Resolution High Speed Low Area Floating Point AdderSubtractor With Reducing Mean Latency For OFDM ApplicationsDr. Rozita teymourzadeh, CEng.Ainda não há avaliações

- An Efficient 64-Point Pipelined FFT Engine: November 2010Documento6 páginasAn Efficient 64-Point Pipelined FFT Engine: November 2010sbtc sbtcAinda não há avaliações

- Base Paper FPR FFTDocumento5 páginasBase Paper FPR FFTOleti GowthamiAinda não há avaliações

- 12 - Chepter 5Documento11 páginas12 - Chepter 5KhaireddineAinda não há avaliações

- Vlsi Architecture For r2b r4b r8bDocumento81 páginasVlsi Architecture For r2b r4b r8bvsangvai26Ainda não há avaliações

- VHDL Implementation of FFT/IFFT Blocks For OFDM: Pawan Verma Harpreet Kaur Mandeep Singh Balwinder SinghDocumento3 páginasVHDL Implementation of FFT/IFFT Blocks For OFDM: Pawan Verma Harpreet Kaur Mandeep Singh Balwinder SinghParamesh WaranAinda não há avaliações

- Hardware Implementation Low Power High Speed FFT CoreDocumento7 páginasHardware Implementation Low Power High Speed FFT CoreAndrew TheKanenasAinda não há avaliações

- Designing and Simulation of 32 Point FFT Using Radix-2 Algorithm For FpgaDocumento9 páginasDesigning and Simulation of 32 Point FFT Using Radix-2 Algorithm For FpgaInternational Organization of Scientific Research (IOSR)Ainda não há avaliações

- 1 (R2MDC) A Low Power Radix-2 FFT Accelerator For FPGADocumento5 páginas1 (R2MDC) A Low Power Radix-2 FFT Accelerator For FPGAyunqi guanAinda não há avaliações

- Fpga Implementation of FFT Algorithm For Ieee 802.16E (Mobile Wimax)Documento7 páginasFpga Implementation of FFT Algorithm For Ieee 802.16E (Mobile Wimax)soumyaAinda não há avaliações

- Easic Ipds 08 FFT v2 1 DatasheetDocumento64 páginasEasic Ipds 08 FFT v2 1 DatasheetcnbattsonAinda não há avaliações

- DIT Radix-2Documento7 páginasDIT Radix-2Suha NoriAinda não há avaliações

- Microcontroller Synthesized Function Generator: Visa M. Ibrahim .Oni Taiwo .Uyoata E. UyoataDocumento7 páginasMicrocontroller Synthesized Function Generator: Visa M. Ibrahim .Oni Taiwo .Uyoata E. UyoataIJERDAinda não há avaliações

- 2003 A 2048 Complex Point FFT Processor Using A Novel Data Scaling ApproachDocumento4 páginas2003 A 2048 Complex Point FFT Processor Using A Novel Data Scaling ApproachRajesh BathijaAinda não há avaliações

- Design of An Efficient FFT Processor For OFDM Systems: Haining Jiang, Hanwen Luo, Jifeng Tian and Wentao SongDocumento5 páginasDesign of An Efficient FFT Processor For OFDM Systems: Haining Jiang, Hanwen Luo, Jifeng Tian and Wentao SongJana Bhaskar RaoAinda não há avaliações

- Low-Power, High-Speed FFT Processor For MB-OFDM UWB ApplicationDocumento10 páginasLow-Power, High-Speed FFT Processor For MB-OFDM UWB ApplicationPhuc HoangAinda não há avaliações

- FFT Implementation for High-Speed Astrophysics on FPGAsDocumento54 páginasFFT Implementation for High-Speed Astrophysics on FPGAsAnonymous VBGaySkxAinda não há avaliações

- VHDL Implementation of A Flexible and Synthesizable FFT ProcessorDocumento5 páginasVHDL Implementation of A Flexible and Synthesizable FFT ProcessorHarrySchrovskiAinda não há avaliações

- High-Throughput VLSI Architecture For FFT ComputationDocumento5 páginasHigh-Throughput VLSI Architecture For FFT ComputationSureshAinda não há avaliações

- Comparative Study of Various FFT Algorithm Implementation On FPGADocumento4 páginasComparative Study of Various FFT Algorithm Implementation On FPGAInternational Journal of Emerging Trends in Signal Processing (IJETSP)Ainda não há avaliações

- Implementation of Digital QPSK Modulator by Using VHDL / MatlabDocumento5 páginasImplementation of Digital QPSK Modulator by Using VHDL / Matlabblesson123Ainda não há avaliações

- FFT128 ProjectDocumento70 páginasFFT128 ProjectBảo Ngọc LêAinda não há avaliações

- Implementation of Double Precision Floating Point Radix-2 FFT Using VHDLDocumento7 páginasImplementation of Double Precision Floating Point Radix-2 FFT Using VHDLFerdiKaraAinda não há avaliações

- Design and Implementation of An Optimized Double Precision Floating Point Divider On FPGADocumento8 páginasDesign and Implementation of An Optimized Double Precision Floating Point Divider On FPGAPrathyusha DileepAinda não há avaliações

- FFT PaperDocumento6 páginasFFT Paperpavankumar438pAinda não há avaliações

- FFT Algorithms for RISC Processors Optimize FMA InstructionsDocumento38 páginasFFT Algorithms for RISC Processors Optimize FMA InstructionsManish JeswalAinda não há avaliações

- Eff Arch For Dit FFTDocumento10 páginasEff Arch For Dit FFThemanthbbcAinda não há avaliações

- 1.6-2005 India 3rd IITKanpur-WebDocumento16 páginas1.6-2005 India 3rd IITKanpur-WebSuresh KumarAinda não há avaliações

- SSRN-id3869494Documento5 páginasSSRN-id3869494Prabhu SAinda não há avaliações

- FIR Filter Design On Chip Using VHDL: IPASJ International Journal of Computer Science (IIJCS)Documento5 páginasFIR Filter Design On Chip Using VHDL: IPASJ International Journal of Computer Science (IIJCS)International Journal of Application or Innovation in Engineering & ManagementAinda não há avaliações

- PTFFT 2Documento6 páginasPTFFT 2obula863Ainda não há avaliações

- Butterfly Unit Supporting Radix-4 and Radix-2 FFTDocumento8 páginasButterfly Unit Supporting Radix-4 and Radix-2 FFTanon_145312040Ainda não há avaliações

- High Speed Reconfigurable FFT Design by Vedic Mathematics: Ashish Raman, Anvesh Kumar and R.K.SarinDocumento5 páginasHigh Speed Reconfigurable FFT Design by Vedic Mathematics: Ashish Raman, Anvesh Kumar and R.K.SarinDrSakthivelAinda não há avaliações

- FFT Fast Fourier Transform ChapterDocumento20 páginasFFT Fast Fourier Transform ChapterrohitrvnAinda não há avaliações

- Design of 16-Point Radix4 Fast Fourier Transform IDocumento7 páginasDesign of 16-Point Radix4 Fast Fourier Transform IAyush anandAinda não há avaliações

- Implementation of Low Power and High Speed Multiplier-Accumulator Using SPST Adder and VerilogDocumento8 páginasImplementation of Low Power and High Speed Multiplier-Accumulator Using SPST Adder and Verilogsujaganesan2009Ainda não há avaliações

- Design and Implementation of Early-Late Gate Bit Synchronizer For Satellite CommunicationDocumento4 páginasDesign and Implementation of Early-Late Gate Bit Synchronizer For Satellite CommunicationMatthew CarterAinda não há avaliações

- 1ea7 PDFDocumento6 páginas1ea7 PDFSwetha VanamAinda não há avaliações

- Radix-4 and Radix-8 Multiplier Using Verilog HDLDocumento6 páginasRadix-4 and Radix-8 Multiplier Using Verilog HDLIJARTETAinda não há avaliações

- Real Time Voice OFDMDocumento131 páginasReal Time Voice OFDMlequangdn91Ainda não há avaliações

- Ass 9Documento4 páginasAss 9VLSIAinda não há avaliações

- HW-Efficient Reduced-Latency Configurable Mixed-Radix FFTDocumento7 páginasHW-Efficient Reduced-Latency Configurable Mixed-Radix FFTnikolicnemanjaAinda não há avaliações

- (IJCST-V3I2P16) :harpreet KaurDocumento6 páginas(IJCST-V3I2P16) :harpreet KaurEighthSenseGroupAinda não há avaliações

- Modular Design of Adders With Domino Logic 1: M.B.Damle 2 DR S.S.LimayeDocumento5 páginasModular Design of Adders With Domino Logic 1: M.B.Damle 2 DR S.S.LimayeIjarcet JournalAinda não há avaliações

- Radio Frequency Identification and Sensors: From RFID to Chipless RFIDNo EverandRadio Frequency Identification and Sensors: From RFID to Chipless RFIDAinda não há avaliações

- Software Radio: Sampling Rate Selection, Design and SynchronizationNo EverandSoftware Radio: Sampling Rate Selection, Design and SynchronizationAinda não há avaliações

- VLSI Implementation of High Speed and High Resolution FFT Algorithm Based On Radix 2 For DSP ApplicationDocumento4 páginasVLSI Implementation of High Speed and High Resolution FFT Algorithm Based On Radix 2 For DSP ApplicationDr. Rozita teymourzadeh, CEng.Ainda não há avaliações

- On-Chip Implementation of Pipeline Digit-Slicing Multiplier-Less Butterfly For Fast Fourier Transform ArchitectureDocumento8 páginasOn-Chip Implementation of Pipeline Digit-Slicing Multiplier-Less Butterfly For Fast Fourier Transform ArchitectureDr. Rozita teymourzadeh, CEng.Ainda não há avaliações

- VLSI Implementation of Novel Class of High Speed PipelinedDocumento7 páginasVLSI Implementation of Novel Class of High Speed PipelinedDr. Rozita teymourzadeh, CEng.Ainda não há avaliações

- VLSI Implementation of High Resolution High Speed Low Latency Pipeline Floating Point Adder Subtractor For FFT ApplicationsDocumento5 páginasVLSI Implementation of High Resolution High Speed Low Latency Pipeline Floating Point Adder Subtractor For FFT ApplicationsDr. Rozita teymourzadeh, CEng.Ainda não há avaliações

- On-Chip Implementation of Cascaded Integrated Comb Filters (CIC) For DSP ApplicationsDocumento12 páginasOn-Chip Implementation of Cascaded Integrated Comb Filters (CIC) For DSP ApplicationsDr. Rozita teymourzadeh, CEng.Ainda não há avaliações

- The Effect of The Digit Slicing Architecture On The FFT ButterflyDocumento4 páginasThe Effect of The Digit Slicing Architecture On The FFT ButterflyDr. Rozita teymourzadeh, CEng.Ainda não há avaliações

- Universal Computer Aided Design For Electrical MachinesDocumento6 páginasUniversal Computer Aided Design For Electrical MachinesDr. Rozita teymourzadeh, CEng.Ainda não há avaliações

- VLSI Implementation of Cascaded Integrator Comb Filters For DSP ApplicationsDocumento5 páginasVLSI Implementation of Cascaded Integrator Comb Filters For DSP ApplicationsDr. Rozita teymourzadeh, CEng.Ainda não há avaliações

- Optimised Toolbox For The Design of Rotary Reluctance MotorsDocumento7 páginasOptimised Toolbox For The Design of Rotary Reluctance MotorsDr. Rozita teymourzadeh, CEng.Ainda não há avaliações

- FPGA Implementation of Pipeline Digit-Slicing Multiplier-Less Radix 22 DIF SDF Butterfly For Fast Fourier Transform StructureDocumento5 páginasFPGA Implementation of Pipeline Digit-Slicing Multiplier-Less Radix 22 DIF SDF Butterfly For Fast Fourier Transform StructureDr. Rozita teymourzadeh, CEng.Ainda não há avaliações

- On-Chip Implementation of High Resolution High Speed Low Area Floating Point AdderSubtractor With Reducing Mean Latency For OFDM ApplicationsDocumento6 páginasOn-Chip Implementation of High Resolution High Speed Low Area Floating Point AdderSubtractor With Reducing Mean Latency For OFDM ApplicationsDr. Rozita teymourzadeh, CEng.Ainda não há avaliações

- An Enhancement of Decimation Process Using Fast Cascaded Integrator Comb (CIC) FilterDocumento5 páginasAn Enhancement of Decimation Process Using Fast Cascaded Integrator Comb (CIC) FilterDr. Rozita teymourzadeh, CEng.100% (1)

- Design of Automatic Soil Humidity Control Using Maximum Power Point Tracking ControllerDocumento5 páginasDesign of Automatic Soil Humidity Control Using Maximum Power Point Tracking ControllerDr. Rozita teymourzadeh, CEng.Ainda não há avaliações

- An Overview of The Decimation Process and Its VLSI ImplementationDocumento7 páginasAn Overview of The Decimation Process and Its VLSI ImplementationDr. Rozita teymourzadeh, CEng.Ainda não há avaliações

- An Improved Recursive and Non-Recursive Comb Filter For DSP ApplicationsDocumento5 páginasAn Improved Recursive and Non-Recursive Comb Filter For DSP ApplicationsDr. Rozita teymourzadeh, CEng.Ainda não há avaliações

- Palmetto Bay's Ordinance On Bird RefugeDocumento4 páginasPalmetto Bay's Ordinance On Bird RefugeAndreaTorresAinda não há avaliações

- Philippine Architecture, Film Industry EvolutionDocumento4 páginasPhilippine Architecture, Film Industry EvolutionCharly Mint Atamosa IsraelAinda não há avaliações

- Credentials List with Multiple Usernames, Passwords and Expiration DatesDocumento1 páginaCredentials List with Multiple Usernames, Passwords and Expiration DatesJOHN VEGAAinda não há avaliações

- Logistic Regression to Predict Airline Customer Satisfaction (LRCSDocumento20 páginasLogistic Regression to Predict Airline Customer Satisfaction (LRCSJenishAinda não há avaliações

- Top 35 Brokerage Firms in PakistanDocumento11 páginasTop 35 Brokerage Firms in PakistannasiralisauAinda não há avaliações

- Well Control Kill Sheet (Low Angle Wells)Documento8 páginasWell Control Kill Sheet (Low Angle Wells)Tatita ValenciaAinda não há avaliações

- Fujitsu Spoljni Multi Inverter Aoyg45lbt8 Za 8 Unutrasnjih Jedinica KatalogDocumento4 páginasFujitsu Spoljni Multi Inverter Aoyg45lbt8 Za 8 Unutrasnjih Jedinica KatalogSasa021gAinda não há avaliações

- 3.4 Spending, Saving and Borrowing: Igcse /O Level EconomicsDocumento9 páginas3.4 Spending, Saving and Borrowing: Igcse /O Level EconomicsRingle JobAinda não há avaliações

- Information Pack For Indonesian Candidate 23.06.2023Documento6 páginasInformation Pack For Indonesian Candidate 23.06.2023Serevinna DewitaAinda não há avaliações

- NAC Case Study AnalysisDocumento25 páginasNAC Case Study AnalysisSushma chhetriAinda não há avaliações

- 7th Kannada Science 01Documento160 páginas7th Kannada Science 01Edit O Pics StatusAinda não há avaliações

- POS CAL SF No4 B2 BCF H300x300 7mmweld R0 PDFDocumento23 páginasPOS CAL SF No4 B2 BCF H300x300 7mmweld R0 PDFNguyễn Duy QuangAinda não há avaliações

- Lec - Ray Theory TransmissionDocumento27 páginasLec - Ray Theory TransmissionmathewAinda não há avaliações

- 13-07-01 Declaration in Support of Skyhook Motion To CompelDocumento217 páginas13-07-01 Declaration in Support of Skyhook Motion To CompelFlorian MuellerAinda não há avaliações

- Nature and Effects of ObligationsDocumento5 páginasNature and Effects of ObligationsIan RanilopaAinda não há avaliações

- Question Paper Code: 31364Documento3 páginasQuestion Paper Code: 31364vinovictory8571Ainda não há avaliações

- Globalisation - Theories of Digital CommunicationDocumento12 páginasGlobalisation - Theories of Digital CommunicationDiya Patel-10SAinda não há avaliações

- As 1769-1975 Welded Stainless Steel Tubes For Plumbing ApplicationsDocumento6 páginasAs 1769-1975 Welded Stainless Steel Tubes For Plumbing ApplicationsSAI Global - APACAinda não há avaliações

- SDNY - Girl Scouts V Boy Scouts ComplaintDocumento50 páginasSDNY - Girl Scouts V Boy Scouts Complaintjan.wolfe5356Ainda não há avaliações

- EU Letter To Liz Truss 2016Documento2 páginasEU Letter To Liz Truss 2016MadeleineAinda não há avaliações

- Ieee Research Papers On Software Testing PDFDocumento5 páginasIeee Research Papers On Software Testing PDFfvgjcq6a100% (1)

- Engine Controls (Powertrain Management) - ALLDATA RepairDocumento4 páginasEngine Controls (Powertrain Management) - ALLDATA Repairmemo velascoAinda não há avaliações

- Photoshop Tools and Toolbar OverviewDocumento11 páginasPhotoshop Tools and Toolbar OverviewMcheaven NojramAinda não há avaliações

- TX Set 1 Income TaxDocumento6 páginasTX Set 1 Income TaxMarielle CastañedaAinda não há avaliações

- Broker Name Address SegmentDocumento8 páginasBroker Name Address Segmentsoniya_dps2006Ainda não há avaliações

- 2JA5K2 FullDocumento22 páginas2JA5K2 FullLina LacorazzaAinda não há avaliações