Escolar Documentos

Profissional Documentos

Cultura Documentos

A Novel High Performance CMOS Cascoded Operational Amplifier For Process Instrumentation Based Applications

Enviado por

IDESTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

A Novel High Performance CMOS Cascoded Operational Amplifier For Process Instrumentation Based Applications

Enviado por

IDESDireitos autorais:

Formatos disponíveis

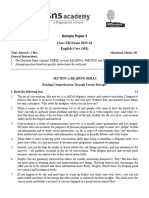

Full Paper

2012 ACEEE

DOI: 01.IJRTET.7.2.

Int. J. on Recent Trends in Engineering and Technology, Vol. 7, No. 2, July 2012

545

A Novel High Performance CMOS Cascoded

Operational Amplifier for Process Instrumentation

Based Applications

Rajinder Tiwari

Department of Electronics & Comm. Engineering,

Kumaon Engineering College (KEC),

Dawarahat (Almora), Uttarakhand

Email: trajan@rediffmail.com

Abstract In this contribution, a highly efficient CMOS based

operational amplifier has been presented that uses the circuit

arrangement so as to provide an extra bias current into a

conventional CMOS dif ferential input signal which is

required for high performance of the system. The design of a

high performance CMOS operational amplifier (op-amp) with

level 3 parameters at 0.2m CMOS technology, that makes

the use of stacked (cascode) current source techniques. This

innovative approach benefits the chances operated by full

complementary implementations of well known sub-circuits,

to enhance the speed of such an operational amplifier and to

better organize and economize layout generation. Unlike

conventional techniques such as the cascoding, which

increases the gain by increasing the output resistance, the

replica-amp technique increases the gain by matching the

main and the replica amps. Among the advantages of the replica

op-amp technique are low supply, high swing, and effectiveness

with resistive loads. The pSpice simulations of the op-amp

shows a unity gain bandwidth of 30 MHz and a DC gain of 62

dB, when using a bias current of 90 A and a load capacitance

of 10 pF.

Keywords: Standard CMOS op-amp, Circuit, design

methodology, transistor sizing, optimization,Op-Amp, Slew

Rate, Optimized Amplifier, CMOS, Cascoded,PSpice

Simulation.

I. INTRODUCTION

The time required to settle down is an important aspect of an

operational amplifier that has to be discussed while designing

an optimized performance of the device. Although, it has been

quite tedious to do the analytical analysis, thus, the analysis

procedure can be well understood that it can be easily determined

in terms of the collective behavior of the slew rate and frequency

response of the device [1, 2]. It has been well defined that for a

pre-calculated capacitive load, the voltage step applied at the

input terminals of the device and the power dissipation, there

always exist a physical limitation to determine and calculate the

settling time of the device. Thus, with this assumption, it very

much true holds for a time period that exists at the final stage of

the settling process of an op-amp which can be easily obtained

from the response of the device that depicts the operational

behavior of the amplifier [3]. And the initial time period of this

device provides the operational action of a large signal amplifier.

The general expression of the slew rate of an op-amp is

R. K. Singh

Department of Electronics & Comm. Engineering,

Kumaon Engineering College (KEC),

Dawarahat (Almora), Uttarakhand

Email: rksinghkec12@rediffmail.com

determined as the maximum available current to charge up the

capacitive loads of the system (including load and compensation

capacitors):

m

I

ax

R

tot

S

C

=

(1)

From this above expression (i.e. equation 1), it has been

observed that for a predetermined value of the capacitance, the

amount of power consumed by the device in all will put a cap on

the performance of the slew rate of the operational amplifier. The

various probable methods of overcoming this limitation have

been discussed in the various research papers [4, 7].

Figure 1: Basic Schematic Approach of Op-Amp

Now, when a large amount of signal is available to the circuit

of the op-amp at the differential end terminals, it will certainly

deteriorate the slew rate performance of the device. In order to

overcome this problem, the amount of the bias current has been

subsequently increased temporarily so as to obtain a

satisfactorily performance of the slew rate of the op-amp.

For this methodology of obtaining the desired performance

of the operational amplifier, the circuit arrangement of the device

should contain the followings:

- A small chip area

- Low power dissipation

- No degradation of the electrical characteristics

Thus, from this above discussions, it has been observed

that the technique of obtaining the desired performance of the

operational amplifier with minimum and optimized degradation

of the electrical characteristics of the various components and

devices of the circuit has been implemented [8, 9]. The basic

concept in the discussion of the performance of an op-amp

thus, relies on the strategy and the methodology considered in

77

Full Paper

Int. J. on Recent Trends in Engineering and Technology, Vol. 7, No. 2, July 2012

2012 ACEEE

DOI: 01.IJRTET.7.2.

biasing the circuit i.e. the static as well as dynamic biasing the

amplifier.

It means that the static biasing is deployed so as to

accomplish the flow of the current through the circuit for the

determination of the small signal operational behavior,

whereas, the dynamic biasing of the circuit is used to discuss

the performance of the op-amp as a large signal amplifier. [10,

12]. A high performance op-amp has been designed and

implemented by merging the single-ended stacked mirror op-

amp and the high drive class AB output stage that has been

described with the above compromises of the circuit, which

provides a large output resistance and thus a high gain and

the output buffer stage [13]. The dominant pole p

1

that is

located at a frequency

1

and determined by the total output

resistance R

o

and the load capacitance C

L

. The

1

frequency

is determined as:

1

1

o L

R C

=

(2)

The non-dominant pole p

2

has been determined by the

first stage input resistance R

i

, and the input capacitance to

the current gain stage C

i

. The non-dominant pole frequency

2

is approximately determined by [14]:

2

1

i i

RC

=

(3)

provided r

o

>>R

i

, where r

o

is the output resistance of the

input stage.

II. BASIC OPERATIONAL AMPLIFIERS CIRCUITS& OPERATION

545

Figure 2 Possible Configurations of Op-Amp (a) Standard Op-Amp (b)

Active Cascode Circuit & Inverting Op-Amp (c) Folded Cascoded

Circuit & Standard Block of Op-Amp

The figure (1a) shows the schematic arrangement of a standard

operational amplifier, figure (1b), shows the possible

combinations of the active cascode circuit of operational amplifier

with the inverting configuration and figure (1c) shows the folded

low frequency model & the block representation of the traditional

operational amplifier. The low frequency small signal model of

the folded-cascode approach is shown in fig (1c), whose DC

gain is given as [15, 16]:

1 011 09 9 07 7 01 05

1

( || ( || ))

'

v m m m

v m out

A g r r g r g r r

A g R

=

=

(4)

And the transfer function of this approach of the

operational amplifier is given as:

1 12

12 13

( ) (1 )

( ) ( )( (1 ' ) ' )

o m m c c

in L m o c out c out

V S g g SC R

V S SC g g SC G R G

+

=

+ + +

(5)

On solving this above expression, the zero which is added

to the systems transfer function so as to improve the phase

margin of the operational amplifier is given as [17]:

1

c c

Z

C R

=

(6)

The mathematical expressions that determine the two

dominant poles of the system are given as:

1

1 1

'

' (1 )

'

c

out c

out c

out

P

R

R C

R C

R

= ~

+ (7)

12 13 12

2

( ) 1

'

m o m

L out L L

g g g

P

C R C C

+

= = ~

(8)

Also the slew rate of the standard operational amplifier is

given by the maximum available current to charge up all the

capacitances i.e. [18]

m

I

ax

R

c

S

C

=

(9)

The dynamic analysis of the standard operational

amplifier gives the mathematical behavior of various

parameters say dc gain, bandwidth and the slew rate [19, 20].

1,2 5

1,2 3,4 5 6

( )( )

m m

o

ds ds ds ds

g g

A

g g g g

~

+

(10)

1,2 m

c

g

GB

C

~

(11)

where the compensating capacitor is given as:

5

2 2

5

( )

md m L

c

m md

g g C

C

Q g g

~

(12)

And Q is the resonance factor of the op-amp with a unity

gain feedback.

78

Full Paper

2012 ACEEE

DOI: 01.IJRTET.7.2.

Int. J. on Recent Trends in Engineering and Technology, Vol. 7, No. 2, July 2012

545

III. PROPOSED HIGH PERFORMANCE OPERATIONAL AMPLIFIER

Figure 3 Proposed Circuit of High Performance Operational

Amplifi er

A high performance op-amp circuit has been designed

and put forward with its best performance. The complete

schematic arrangement of the circuit is shown in above figure

3. It comprises of the CMOS devices, which has a large output

resistance and thus a high gain. The transistors M17 and

M20 are used to bias M18 and M19 which drive the push-

pull output stage, where as M22, M21 and M23 transistors

has a low W/L ratio and thus, acts as a large linear

resistor.

The output stage of the circuit is biased such that the

current flowing through M22 is matched by the current in

M21 during quiescent operation. The biasing transistors are

controlled by the high frequency gain stage and provide the

necessary inputs for the push-pull output stage. The minimum

value for the load capacitance which provides the dominant

pole compensation is given as [21, 25]

1 L i i m i

C C R g A = (13)

where gm1 is the transconductance of the input stage

and Ai is the current gain. Generally, some of the dominant

parameters of the circuit such as power consumption are

imposed and must be fixed during the design and

implementation process. The designing steps and procedure

of sizing of the transistors are classically obtained after

determining the saturation drain source voltage determined

by V

ONi

for transistor (T

i

). Based on this concept, one can

determine the most required and dominant parameters of the

op-amp as [26, 28]:

( )( ) 1

ss

DD SS

P

I

V V m

~

+

(14)

where m is the bias current modulation factor between the

differential and the gain stage of the circuit.

5 6

7

bias

ss

W

I L

m

W I

L

| |

|

\ .

= =

| |

|

\ .

(15)

The slewing-rate of the op-amp is determined as the maximum

available current required to charge up all capacitances (i.e.

the compensation capacitance load C

C

) i.e. [29, 30]

m

I

ax

R

C

S

C

=

(16)

Thus , based on this above relation, the value and the

performance of the I

max

can be easily enhanced and improved

since the C

C

is always kept constant for this particular

approach and design.

( ) ( ) ( )

2

4

m 4 4max 3 2

I

2

ax D G DD Th Th

K

I V V V V = =

(17)

The variation in the capacitive load will vary the unity

gain bandwidth as desired by the circuit design and

performance of the 3 dB gain amplifier. The differential input

stage of the circuit performs the differential-to-single ended

conversion with the help of the transistors M6, M7 [31, 32].

The output stage of the circuit is based on a novel approach

of design that provides solution so as to provide the driven

capability of a simple inverter stage with an accurate current

control. In quiescent condition, the transistors M17, M18 are

in cut-off mode, and M 16, M19 are in saturation region,

which perform a highly linear operation of the amplifier. As

the gate of the transistor M13 increases, say in the positive

direction, the current i

DM13

becomes equal to bias current,

and the transistor M14 and M16 turns off and the gate of

M16 is driven close to V

SS

. Thus, transistor the transistor

M17 turns on and delivers a high current to the output load

[33, 35].

IV. SIMULATION RESULTS & DISCUSSION

Figure 4 Step Response of the Op-amp

The simulation of the proposed ciruit has been done by

using pSPICE software with 0.18n CMOS technology with level

3 modeled parameters for the best possible performance. The

above figure 4 shows the step response of the proposed op-

amp with and without effetct of the enhancement circuit having

the total load capacitance of approximately 10pF i.e functioning

as the feedback loop and the load of the circuit.

The average positive slew rate for both circuits is about

55V/s and the negative slew rate is 54V/sec with 5pF capacitor

and 8.5V/s and 9.0V/s for a capacitive load of 10pF. This

behaviour of the high performance op-amp simulation results is

shown in figure 5 (a & b).

79

Full Paper

Int. J. on Recent Trends in Engineering and Technology, Vol. 7, No. 2, July 2012

2012 ACEEE

DOI: 01.IJRTET.7.2.545

Figure 5 Slew Rate of the Op-amp (a) Positive (b) Negative

Figure 6 Frequency Response

The above figure 6 shows the frequency response of the

high performance op-amp circuit with a bandwith of approx 3 db

that provides a approx value of frequency as 30 KHz.

Figure 7 DC Analysis of Op-amp

The above figure 7 shows the dc analyzing behavior of the

proposed circuit which reflects that the amplifier has got

minimized or almost optimized noise or distortion free

performance since it replicated the input at the put with minimum

possible noise and delay.

Figure 8 Time Response of Op-amp

The above figure 8 shows the transient or simply time

response of the circuit with different possible capacitive loads.

It reflects clearly that the behavior of the signal at the capacitive

load output almost follow the step input applied at the input

with minimum possible distortion.

V. CONCLUSION

In this discussion an innovative approach and methodology

has been proposed using CMOS. The proposed approach of

performance is basically depends upon the mathematical

modeling of the parameters of the CMOS and then simulation of

the same using level 3 pSPICE model of 0.18n CMOS

technology. The key advantages of this proposed circuit is to

implement a high performance op-amp circuit that can be most

suitably used in the design of analog integrated circuits and

high frequency switch-capacitor filters. The main and the desired

features of this innovative circuit is that it performs as per the

modeled parameters and provides the results as shown in table

I.

TABLE I. MODELED PARAMETERS FOR PROPOSED CIRCUIT

VI. ACKNOWLEDGEMENT

The authors are thankful to Prof. D. S. Chauhan (Vice Chancellor,

UTU) for providing the environment for this work, Mr. Aseem

Chauhan (Additional President, RBEF), Major General K. K. Ohri,

80

Full Paper

2012 ACEEE

DOI: 01.IJRTET.7.2.

Int. J. on Recent Trends in Engineering and Technology, Vol. 7, No. 2, July 2012

545

AVSM, Retd. (Director General, AUUP, Lucknow campus), Prof.

S. T. H. Abidi (Director, ASET) and Brig. Umesh K. Chopra, Retd.

(Dy. Director, ASET) for their kind cooperation, motivation, kind

and most valuable suggestions.

REFERENCES

[1] P. R. Gray and R. G. Meyer, Recent advances in monolithic

operational amplifier design, IEEE Truns. Circuits Syst.,

vol. CAS-21. pp. 317-327, May 1974.

[2] J.-C. Lin and J. H. Nevin, A modified time domain model

for nonlinear analysis of an operational amplifier, IEEE J.

Solid-Store Circuits, vol. SC-21, pp. 478-483, June 1986.

[3] K. Matsui, T. Matsuura, and K. Iwasahi, 2 pm CMOS

switched capacitor circuits for analog video LSI. in Proc.

ISCAS, May 1982. pp. 241-244

[4] P. R. Gray and R. G. Meyer, Anulysis and Design of Anulog

Integruted Circuits. 2nd ed.

[5] J. N. Babanezhad and G. C. Temes, A 20-V four-quadrant

CMOS analog multiplier, IEEE J. Solid-Store Circuits,

vol. SC-20, pp. 1157-1168, Dec. 1985.

[6] M. G. Degrauwe, J. Rijmenants, E. A. Vittoz, and H. J. De

Man. Adaptive biasing CMOS amplifiers, IEEE J. Solid-

Stute Circuits. vol. SC-17, pp. 522-528, June 1982.

[7] B. J. Hosticka. Dynamic CMOS amplifiers, IEEE J. Solid-

state Circuits, vol. SC-15, pp. 887-894, Oct. 1980.

[8] W. E. Hearn. Fast slewing monolithic operational amplifier.

IEEE J. Solid-Stute Circuits. vol. SC-6, pp. 20-24, Feb. 1971.

[9] B. J. Hosticka, R. Klinke, and H. -J. Pfleiderer,

Differenzverstarker mitsteuerbarer Leistungsaufnuhme,

Patent pending.

[10] J. Eichholz, Entwicklung eines schnellen Abtast-Halte-

Gliedes in CMOS-Technik, Studienarbeit, Universitat-

Gesamthochschule- Duisburg. Feb. 1988. New York: Wiley,

1984, pp. 755-756.

[11] R. W. Brodersen, P. R. Gray, and D. A. Hodges, I MOS

Switched-Capacitor Filters , Proc. IEEE, Vol. 67, NO. 1, pp.

61-75, January l9?9.

[12] K. Nakayama, and Y. Kuraishi, Resent and,Futun

Applications of Switched-Capacitor Circuits , IEFiE Circuits

and Devices, Vol. 3, No. 5, pp. 10-21, September 1987.

[13] C. W. Solomon, Sw$ched-capacitor filters: precise, compact,

inexpensive , IEEE Spectrum, Vol. 25, No. 6, pp. 28-32,

June 1988.

[14] M. Milkovic, Current Gain High-Frequency CMOS

Operational-amplifiers 0 EEiE J. Solid-state Circuits, Vol.

SC-20, No. 4, pp. 845-851. August 1985.

[15] M. Milkovic, VLSI High Frequency CMOS Operational-

amplifiers for Communications Applications , Proc. 27th

Midwest Symp. Circuits 67, NO. 1, pp. 61-75, January

l9?9. bias &t. 1988.

[16] R. Gregorian, G. C. Temes, ANALOG MOS INTEGRATED

CIRCUITS FOR SIGNAL PROCESSING, John Wiley &

Sons Inc., Chapter Four, 1986.

[17] S. L. Wong, C. A. T. Salama, An Efficie:t CMOS Buffer for

Driving Large Capacitive Loads , IEEE J. Solid-state Circuits,

Vol. SC-21, No. 3, pp. 464-469, June 1986.

[18] C. A. Laber, P. R. Gray, A Positive-Feedback

Transconductance Amplifier with Applications to High-

Fyquency, High-Q CMOS Switched-Capacitor Filters , IEEE

J. Solid-state Circuits, Vol. SC-23, No. 6. pp. 1370-1378.

Dec. 1988.

[19] PP.R. Gray and R.G. Meyer MOS Operational Amplifier

Design -A Tutorial Overview IEEE J. Solid-state Circuits,

Vol. SC-17, no. 6,pp.969-982,Dec.1982.

[20] R. B. Steck, A. Kostka, K.Lehmann; A Versatile Building-

Block for High-speed Current-Mode Analog ICs, Proc.

EuroAsic Conference, Pans, 1991.

[21] K. Dzahini, F. Gaffiot, B. Boutherin, M. Le Helley; Layout

Automation of CMOS Analog Building Blocks with

CADENCE, Proc. EuroAsic Conference, Paris, 1990.

[22] R. Klinke, B. J. Hosticka, H.-J. Pfleiderer; A Very High

Slew-Rate Dynamic CMOS Operational Amplifier, Proc.

ESSCIRC Conference, pp. 203-206, 1988.

[23] J. Babanezhad; A Rail-to-Rail CMOS OpAmp , IEEE

Joumal of Solid State Circuits,Vol. 23, Dec. 1988.

[24] P. R. Gray, R. G. Meyer; Analysis and Design of Analog

Integrated Circuits, J. Wiley and sons, 1984.

[25] S. M. Schwehr; Conception dun Amplificateur

OpCrationnel pour un Systhme de Mesure en Technologie

2pm, Masters Thesis, EC Lyon/TH Darmstadt, July 1989.

[26] P. R. Gray and R. G. Meyer, Analysis and Design of Analog

Integrated Circuits. New York: Wiley, 1984.

[27] E. Sackinger and W. Guggenbuhl, A high-swing high-

impedance MOS cascode circuit, IEEE J. So/id-State

Circuits,, vol. 25, pp. 289-298, Feb. 1990.

[28] K. Bult and G. J. G. M. Geelen, A fast-settling CMOS op

amp for SC circuits with 90-dB dc gain, IEEE J. Solid-State

Circuits, vol. 25, pp. 1379-1 384, Dec. 1990.

[29] C. A. Laber and P. R. Gray, A positive-feedback

transconductance amplifier with applications to high-

frequency high-Q CMOS switched- capacitor filters, IEEE

J. Solid-Stare Circuits, vol. 13, pp. 1370-1378, Dec. 1988.

[30] A. A. Abidi, An analysis of bootstrapped gain enhancement

techniques, IEEE J. Solid-Stare Circuits,, vol. SC-22, pp.

1200-1204, Dec. 1987.

[31] S. L. Wong, C. A. T. Salama, C. Simson, and D. A. Smith,

Voltage gain enhancement by conductance cancellation in

CMOS op-amp, in Proc. I984 IEEE Int. Symp. Circuits

and Sysrems, Montrkal, Canada, pp. 1207-1210, May 1984.

[32] A. D. L. Plaza, High-frequency switched-capacitor filter

using unit gain buffers, IEEE J. Solid-State Circuirs, vol.

SC-21, pp. 470477, June 1986.

[33] B.3. Song, M. F. Tompsett, and K. R. Lakshmikumar, A

12-bit 1- Msamples/s capacitor error-averaging pipelined A/

D converter, IEEE J. Solid-%ate Circuits, vol. 23, pp. 1324-

1333, Dec. 1988.

[34] F. Maloberti, G. Palmisano, and G. Torelli, A novel

approach for high-frequency gain-compensated sample-and-

hold circuits, in IEEE Int. Symp. Circuits and Systems. San

Diego, pp. 2049-2052, May 1992.

[35] P. C. Yu and H.-S. Lee, Setting-time analysis of a replica-

amp gain enhanced operational amplifier, IEEE Trans.

Circuits and Systems, to be published.

81

Você também pode gostar

- Study of Structural Behaviour of Gravity Dam With Various Features of Gallery by FEMDocumento8 páginasStudy of Structural Behaviour of Gravity Dam With Various Features of Gallery by FEMIDESAinda não há avaliações

- 1010Documento6 páginas1010Wil LamAinda não há avaliações

- Line Losses in The 14-Bus Power System Network Using UPFCDocumento6 páginasLine Losses in The 14-Bus Power System Network Using UPFCIDESAinda não há avaliações

- Selfish Node Isolation & Incentivation Using Progressive ThresholdsDocumento8 páginasSelfish Node Isolation & Incentivation Using Progressive ThresholdsIDESAinda não há avaliações

- Cloud Security and Data Integrity With Client Accountability FrameworkDocumento13 páginasCloud Security and Data Integrity With Client Accountability FrameworkIDESAinda não há avaliações

- Power System State Estimation - A ReviewDocumento9 páginasPower System State Estimation - A ReviewIDESAinda não há avaliações

- Artificial Intelligence Technique Based Reactive Power Planning Incorporating FACTS Controllers in Real Time Power Transmission SystemDocumento7 páginasArtificial Intelligence Technique Based Reactive Power Planning Incorporating FACTS Controllers in Real Time Power Transmission SystemIDESAinda não há avaliações

- Permutation of Pixels Within The Shares of Visual Cryptography Using KBRP For Enhanced SecurityDocumento9 páginasPermutation of Pixels Within The Shares of Visual Cryptography Using KBRP For Enhanced SecurityIDESAinda não há avaliações

- Design and Performance Analysis of Genetic Based PID-PSS With SVC in A Multi-Machine System Considering Detailed ModelDocumento9 páginasDesign and Performance Analysis of Genetic Based PID-PSS With SVC in A Multi-Machine System Considering Detailed ModelIDESAinda não há avaliações

- Optimal Placement of DG For Loss Reduction and Voltage Sag Mitigation in Radial Distribution Systems Using ABC AlgorithmDocumento6 páginasOptimal Placement of DG For Loss Reduction and Voltage Sag Mitigation in Radial Distribution Systems Using ABC AlgorithmIDESAinda não há avaliações

- Secure Multi-Party Negotiation: An Analysis Forelectronic Payments in Mobile ComputingDocumento8 páginasSecure Multi-Party Negotiation: An Analysis Forelectronic Payments in Mobile ComputingIDESAinda não há avaliações

- Various OSI Layer Attacks and Countermeasure To Enhance The Performance of WSNs During Wormhole AttackDocumento6 páginasVarious OSI Layer Attacks and Countermeasure To Enhance The Performance of WSNs During Wormhole AttackIDESAinda não há avaliações

- Band Clustering For The Lossless Compression of AVIRIS Hyperspectral ImagesDocumento14 páginasBand Clustering For The Lossless Compression of AVIRIS Hyperspectral ImagesIDESAinda não há avaliações

- Enhancing Data Storage Security in Cloud Computing Through SteganographyDocumento7 páginasEnhancing Data Storage Security in Cloud Computing Through SteganographyIDESAinda não há avaliações

- Responsive Parameter Based An AntiWorm Approach To Prevent Wormhole Attack in Ad Hoc NetworksDocumento8 páginasResponsive Parameter Based An AntiWorm Approach To Prevent Wormhole Attack in Ad Hoc NetworksIDESAinda não há avaliações

- High Density Salt and Pepper Impulse Noise RemovalDocumento10 páginasHigh Density Salt and Pepper Impulse Noise RemovalIDESAinda não há avaliações

- Genetic Algorithm Based Layered Detection and Defense of HTTP BotnetDocumento12 páginasGenetic Algorithm Based Layered Detection and Defense of HTTP BotnetIDESAinda não há avaliações

- Low Energy Routing For WSN'sDocumento4 páginasLow Energy Routing For WSN'sIDESAinda não há avaliações

- 3-D FFT Moving Object Signatures For Velocity FilteringDocumento5 páginas3-D FFT Moving Object Signatures For Velocity FilteringIDESAinda não há avaliações

- Rotman Lens Performance AnalysisDocumento6 páginasRotman Lens Performance AnalysisIDESAinda não há avaliações

- Microelectronic Circuit Analogous To Hydrogen Bonding Network in Active Site of - LactamaseDocumento8 páginasMicroelectronic Circuit Analogous To Hydrogen Bonding Network in Active Site of - LactamaseIDESAinda não há avaliações

- Comparative Study of Morphological, Correlation, Hybrid and DCSFPSS Based Morphological & Tribrid Algorithms For GFDDDocumento10 páginasComparative Study of Morphological, Correlation, Hybrid and DCSFPSS Based Morphological & Tribrid Algorithms For GFDDIDESAinda não há avaliações

- Texture Unit Based Monocular Real-World Scene Classification Using SOM and KNN ClassifierDocumento8 páginasTexture Unit Based Monocular Real-World Scene Classification Using SOM and KNN ClassifierIDESAinda não há avaliações

- Optimized Neural Network For Classification of Multispectral ImagesDocumento6 páginasOptimized Neural Network For Classification of Multispectral ImagesIDESAinda não há avaliações

- Mental Stress Evaluation Using An Adaptive ModelDocumento8 páginasMental Stress Evaluation Using An Adaptive ModelIDESAinda não há avaliações

- Efficient Architecture For Variable Block Size Motion Estimation in H.264/AVCDocumento9 páginasEfficient Architecture For Variable Block Size Motion Estimation in H.264/AVCIDESAinda não há avaliações

- Genetic Algorithm Based Mosaic Image Steganography For Enhanced SecurityDocumento12 páginasGenetic Algorithm Based Mosaic Image Steganography For Enhanced SecurityIDESAinda não há avaliações

- Ontology-Based Semantic Approach For Learning Object RecommendationDocumento10 páginasOntology-Based Semantic Approach For Learning Object RecommendationIDESAinda não há avaliações

- Blind Source Separation of Super and Sub-Gaussian Signals With ABC AlgorithmDocumento10 páginasBlind Source Separation of Super and Sub-Gaussian Signals With ABC AlgorithmIDESAinda não há avaliações

- Opportunities and Challenges of Software CustomizationDocumento11 páginasOpportunities and Challenges of Software CustomizationIDESAinda não há avaliações

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNo EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNota: 4 de 5 estrelas4/5 (5783)

- The Yellow House: A Memoir (2019 National Book Award Winner)No EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Nota: 4 de 5 estrelas4/5 (98)

- Never Split the Difference: Negotiating As If Your Life Depended On ItNo EverandNever Split the Difference: Negotiating As If Your Life Depended On ItNota: 4.5 de 5 estrelas4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerNo EverandThe Emperor of All Maladies: A Biography of CancerNota: 4.5 de 5 estrelas4.5/5 (271)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNo EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNota: 4 de 5 estrelas4/5 (890)

- The Little Book of Hygge: Danish Secrets to Happy LivingNo EverandThe Little Book of Hygge: Danish Secrets to Happy LivingNota: 3.5 de 5 estrelas3.5/5 (399)

- Team of Rivals: The Political Genius of Abraham LincolnNo EverandTeam of Rivals: The Political Genius of Abraham LincolnNota: 4.5 de 5 estrelas4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNo EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNota: 4.5 de 5 estrelas4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNo EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNota: 3.5 de 5 estrelas3.5/5 (231)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNo EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNota: 4.5 de 5 estrelas4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNo EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNota: 4.5 de 5 estrelas4.5/5 (344)

- The Unwinding: An Inner History of the New AmericaNo EverandThe Unwinding: An Inner History of the New AmericaNota: 4 de 5 estrelas4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyNo EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyNota: 3.5 de 5 estrelas3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNo EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNota: 4 de 5 estrelas4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)No EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Nota: 4.5 de 5 estrelas4.5/5 (119)

- Full Download Scientific American Environmental Science For A Changing World 3rd Edition Karr Test BankDocumento36 páginasFull Download Scientific American Environmental Science For A Changing World 3rd Edition Karr Test Bankdanielgraya5g100% (14)

- Wapka TagDocumento32 páginasWapka Tagalokraj4uuAinda não há avaliações

- Biology of Halobates (Heteroptera: Gerridae)Documento25 páginasBiology of Halobates (Heteroptera: Gerridae)anubiz2450Ainda não há avaliações

- Tips For Attempting The Question On Poster Making: Issuing Authority: Title: A Sketch: Date, Time and VenueDocumento6 páginasTips For Attempting The Question On Poster Making: Issuing Authority: Title: A Sketch: Date, Time and VenueBibha KumariAinda não há avaliações

- Concept Rationale PaperDocumento2 páginasConcept Rationale Paperjason_277624092Ainda não há avaliações

- Selecc Primitive-Culture-1 PDFDocumento15 páginasSelecc Primitive-Culture-1 PDFguadalupe_51947962100% (1)

- Delamination With AbaqusDocumento13 páginasDelamination With AbaqusSchmetterling TraurigAinda não há avaliações

- Level I Radiography TestDocumento33 páginasLevel I Radiography Testndi101100% (1)

- Paragraph Writing of Academic Texts in An EFL Context: Foreign Language Teaching & LearningDocumento12 páginasParagraph Writing of Academic Texts in An EFL Context: Foreign Language Teaching & LearningMary MazeeAinda não há avaliações

- ANN Mini Project on Artificial Neural Networks (40Documento16 páginasANN Mini Project on Artificial Neural Networks (40amithbalu100% (1)

- Module 2Documento9 páginasModule 2Uday Prakash SahuAinda não há avaliações

- Dmbok2 Henderson IrmacDocumento37 páginasDmbok2 Henderson IrmacWilliam Archila100% (1)

- Erdas Imagine 2018: Product Features and ComparisonsDocumento53 páginasErdas Imagine 2018: Product Features and ComparisonsSaad AliAinda não há avaliações

- Consumer Satisfaction Level of Bajaj Bike Project ReportDocumento72 páginasConsumer Satisfaction Level of Bajaj Bike Project ReportBabasab Patil (Karrisatte)100% (9)

- D 6032 - 96 - Determining Rock Quality Designation (RQD) of Rock CoreDocumento4 páginasD 6032 - 96 - Determining Rock Quality Designation (RQD) of Rock Corezuheib63Ainda não há avaliações

- SQP Eng 3Documento12 páginasSQP Eng 3tasmitha98Ainda não há avaliações

- Sandeep ResumeDocumento3 páginasSandeep ResumeSandeep ElluubhollAinda não há avaliações

- Dstl Tests New Multi-Terrain Camouflage Improving Soldier ConcealmentDocumento5 páginasDstl Tests New Multi-Terrain Camouflage Improving Soldier ConcealmentAdrian BottomleyAinda não há avaliações

- Outcomes UpperInt VocabBuilder Unit3 0Documento9 páginasOutcomes UpperInt VocabBuilder Unit3 0ronaldobatista_engAinda não há avaliações

- 1 ETA July August 2014Documento100 páginas1 ETA July August 2014Igor VasiljevicAinda não há avaliações

- Technical Analysis Around The WorldDocumento30 páginasTechnical Analysis Around The Worldshorttermblog100% (1)

- Release 2: May 2001 J. Ronald EastmanDocumento16 páginasRelease 2: May 2001 J. Ronald EastmanbrayanalarconAinda não há avaliações

- Martha Crampton Guided Imagery PDFDocumento75 páginasMartha Crampton Guided Imagery PDFamimaimiuta100% (3)

- AdvancedCSharpForLowLevelProgramming PDFDocumento104 páginasAdvancedCSharpForLowLevelProgramming PDFdktk2013Ainda não há avaliações

- Macro Environment of The Mobile IndustryDocumento2 páginasMacro Environment of The Mobile IndustryAbhinandanMalhotraAinda não há avaliações

- Grade 5 Nstech Term 1 Practical 2019Documento6 páginasGrade 5 Nstech Term 1 Practical 2019teeAinda não há avaliações

- Expansion of English OverseasDocumento14 páginasExpansion of English OverseasАида ГатауллинаAinda não há avaliações

- Vocabulary - Active and Passive Vocabulary - Various Techniques of Teaching Vocabulary - The Criterion - An International Journal in English PDFDocumento4 páginasVocabulary - Active and Passive Vocabulary - Various Techniques of Teaching Vocabulary - The Criterion - An International Journal in English PDFaknithyanathan100% (1)

- СОР - Английский язык - ОГН - 11 класс - finalDocumento39 páginasСОР - Английский язык - ОГН - 11 класс - finalНаргиз АбайкеноваAinda não há avaliações

- Thyexperiments Towards Truth: The Exalted Jupiter'S Punch by Saptarishis AstrologyDocumento13 páginasThyexperiments Towards Truth: The Exalted Jupiter'S Punch by Saptarishis AstrologyAkash KumarAinda não há avaliações