Escolar Documentos

Profissional Documentos

Cultura Documentos

Array Multiplier

Enviado por

Varsha LalapuraDescrição original:

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Array Multiplier

Enviado por

Varsha LalapuraDireitos autorais:

Formatos disponíveis

E C E N

6 2 6 3

A d v a n c e d

V L S I

D e s i g n

Array Multiplier

a a a a a a

b b b b b b p1p1p1p1p1p1 p2p2p2p2p2p2 longest delay

pnpnpnpnpnpn

delay ~ # digits in word + # partial products # partial products can be reduced by using radix > 2 multiplier

0 1 0 0 0 0 0 0 1 1

0 0 1 0 0

1 0 0 1 0 1

1 0 1 0 0 0 1 0 1

0 1 0 1 0 0 0

1 0 1 1 0 0

1 0 1 1 0

1 0 1 1 1 0 0

multiplicand multiplier 1 0 10 1 0 0 11 0 0 0 1 1

1 0 1 0 0 0 0 1 0 1 0

1 1 1 0 0 3 1 0 1 0 0 0 1 0 1 0

0 1 0 1 0 1 0 1 1 1 0 3 1 0 1 1 1 0 1 0 1 1 1 0 1 0 0 0 1 0 1 0

must pre-calculate 3 x multiplicand

Could take 3 bits at time (radix 8), but need 3x, 5x, 6x, 7x multiplicand.

Array Multiplier October 20, 2000 page 1 of 10

E C E N

6 2 6 3

A d v a n c e d

V L S I

D e s i g n

Trick: recode multiplier changing all 3s to 4 - 1. This can be done with a shifter and 2s complement hardware and does not need an extra adder. Example 101110 (+1)(+1)(-1) 1 1 1 1 1 1 1 0 1 0 0 1 1 0 1 0 1 1 0 1 1 1 1 0 0 1 0 1 1 0 0 0 1 0 1 0

sign extension of negative partial product

103

1 1 -1

Booth algorithm replaces any string of 1s (including 3s) with single digits isolated by strings of 0s. 01111110 10000000 10000010 00000010 Booth recoding (original) b i b i 1 b i (recoded) 0 0 1 1 Example assume zero multiplier recoded multiplier 010011 110101 (+1) (+1) (-1) Now that 3s are gone, combine each pair bits into single recorded digit to reduce number of partial products.

Array Multiplier October 20, 2000 page 2 of 10

0 1 0 1

0 1 left side of string of 1s 1 right side of string of 1s 0

E C E N

6 2 6 3

A d v a n c e d

V L S I

D e s i g n

Modified Booth Recoding

bi+1 0 0 0 0 1 1 1 1

bi 0 0 1 1 0 0 1 1

bi-1 0 1 0 1 0 1 0 1

Booth Recoding bi+1 bi 0 0 1 1 1 1 0 0 0 1 1 0 0 1 1 0

Modified Booth Recoding 0 +1 +1 +2 -2 -1 -1 0

implemented by shift, comp, zero The modified Booth recoded multiplier digits are -2, -1, 0, 1, 2 (never 3). When the multiplicand is multiplied by one of these digits to get the partial product, the partial product is generated by a combination of shifting, complementing or zero-ing without any extra adders. Suppose we try to use an even higher number base to further reduce the number of partial products. Consider base 8 which combines three binary bits into one digit which produces only 1/3 of the original partial products. However, we must find ways to recode the base 8 digits so that there are no non-powers of 2. 0 is OK 1 is OK 2 is OK 3=? 4 is OK 5=? 6 = 8 - 2 is OK 7 = 8 - 1 is OK Since there is no way to recode the 3 and 5 digits, extra adders must be provided to precompute multplying by these digits. This negates most of the advantage of going to the higher number base. Most multiplier designs use modified Booth recoding and multiply by two bits at a time which is what we will assume from now on.

Array Multiplier October 20, 2000 page 3 of 10

E C E N

6 2 6 3

A d v a n c e d

V L S I

D e s i g n

Implementation

Multiplicand (A)

Adder Multiplier Encoder Partial Product Gen Carry

multiplier (B)

Adder (Carry Save)

Multiplier Encoder

Partial Product Gen

Carry

Adder (Carry Save)

Fast Adder

Product

Array Multiplier

October 20, 2000

page 4 of 10

E C E N

6 2 6 3

A d v a n c e d

V L S I

D e s i g n

Carry Save Adder (CSA)

FA

FA

FA

CSA

FA

FA

FA

CSA

No carry delay! (within a CSA stage) CSA array

CS

CS

CS

CS

Fast Adder

Partial Product Generator recoded digit 0 +1 +2 -1 -2 operation 0 => partial product multiplicand => partial product shifted multiplicand => partial product complemented multiplicand => partial product shifted & complemented multiplicand => partial product

Array Multiplier

October 20, 2000

page 5 of 10

E C E N

6 2 6 3

A d v a n c e d

V L S I

D e s i g n

Ai

Ai-1

ZERO

COMP

SHIFT

MUX P.P.i

MUX P.P.i-1

Carry Generation

ZERO COMP SHIFT

.

Cin two ways to get a zero p.p. p.p. bits Cin 000 0 0 111 1 1

Array Multiplier

October 20, 2000

page 6 of 10

E C E N

6 2 6 3

A d v a n c e d

V L S I

D e s i g n

Multiplier Encoder

bi+1 0 0 0 0 1 1 1 1

bi 0 0 1 1 0 0 1 1

bi-1 0 1 0 1 0 1 0 1

Recoded Digit 0 +1 +1 +2 -2 -1 -1 0

COMP x 0 0 0 1 1 1 x

SHIFT x 0 0 1 1 0 0 x

ZERO 1 0 0 0 0 0 0 1

COMP = b i + 1 SHIFT = b i b i 1 + b i b i 1 ZERO = b i + 1 b i b i 1 + b i + 1 b i b i 1 Sign Extension Problem original example

sign extension

1 1 0 0 1 0 1

1 1 0 0 1 0 1

1 1 0 0 1 0 1

1 1 0 0 0 0 0

1 1 0 0 1 0 1

1 1 0 0 1 0 0

1 0 1 0 0 0 1 0 1

0 1 0 1 0 0 0

1 0 1 1 0 0

1 0 1 1 0 0

1 1 1 0 0 0

0 1 0 0 0

regard as negative number

0 1 0 1 0

Array Multiplier

October 20, 2000

page 7 of 10

E C E N

6 2 6 3

A d v a n c e d

V L S I

D e s i g n

recoded example 10 11 10 (+1)(+1)(-1) 0 1 1 1 0 1 1 1 0 1 1 1 0 1 0 0 0 1 1 1 0 0 1 0 0 1 1 1 1 0 0 1 0 1 1 0 0 0 1 0 1 0

can rewrite the first non-zero sign extension as 1111 10001 The sign extension part of the partial products for a Booth encoded multiplier can be written as S0 S0 S0 S0 S0 S1 S1 S1 Sn-1Sn-1 Sn SSSS S 00 trick 1-S=S 0(-S) S 1-S 0 1 1 0 S 1 0

Array Multiplier

SS

October 20, 2000

page 8 of 10

E C E N

6 2 6 3

A d v a n c e d

V L S I

D e s i g n

+1 111 0 0 111 1 0 0(-S0) 0(-S1)

adding zero

0(-Sn-1) +1 0 0 0 1 S0 0 1 S1 1 Sn-1 Partial Product Generation for Sign Extension An-1 ZERO COMP 1 SHIFT Si MUX Sign bit of multiplicand PPn+1 PPn PPn-1 Note: the remaining bits are always zero even when P.P. < 0. No adder inputs are needed for these zeroes.

Array Multiplier October 20, 2000 page 9 of 10

Array Multiplier October 20, 2000 page 10 of 10

6 X 6 Booth Multiplier Example

A5 3 B.E. 1

PPG

A4

PPG

A3

PPG

A2

PPG

A1

PPG

A0

PPG

B0 B1

E C E N

B2 B3

B.E.

3

PPG PPG PPG PPG PPG PPG

1

HA

1

FA HA HA HA HA

6 2 6 3 A d v a n c e d

B4 B5

B.E.

3

PPG PPG PPG PPG PPG PPG

V L S I

HA 0

FA

FA

FA

FA

FA 0

D e s i g n

Look Ahead Carry Adder P11 P10 P9 P8 97 P6 P5 P4 P3 P2 P1 P0

Você também pode gostar

- Computer Architecture: ALU (2) - Integer ArithmeticDocumento24 páginasComputer Architecture: ALU (2) - Integer ArithmeticSulochana JangraAinda não há avaliações

- PPTDocumento9 páginasPPTsindhuvindhya100% (1)

- Simple Shift-Add Multiplier: ELE 4550 ASIC Technologies Project TutorialDocumento3 páginasSimple Shift-Add Multiplier: ELE 4550 ASIC Technologies Project TutorialramyarakiAinda não há avaliações

- COA Mod 3Documento30 páginasCOA Mod 3BasithAinda não há avaliações

- Simple Shift-Add Multiplier: ELE 4550 ASIC Technologies Project TutorialDocumento3 páginasSimple Shift-Add Multiplier: ELE 4550 ASIC Technologies Project Tutorialdeepakkr22781Ainda não há avaliações

- Addition and SubtractionDocumento26 páginasAddition and SubtractionRam GaneshAinda não há avaliações

- Comb CircDocumento63 páginasComb Circm.sangeethjaAinda não há avaliações

- Arithmetic For Computers: Chapter-4Documento67 páginasArithmetic For Computers: Chapter-4Jahangir AlamAinda não há avaliações

- Number Representation: CHAPTER 3 - Part 3Documento52 páginasNumber Representation: CHAPTER 3 - Part 3rqwrqwrAinda não há avaliações

- 1 - Bit ALUDocumento13 páginas1 - Bit ALUSouvik BasuAinda não há avaliações

- CS205 Assignment1 SolutionDocumento7 páginasCS205 Assignment1 SolutionjohnnybyzhangAinda não há avaliações

- Cpe626 MultipliersDocumento37 páginasCpe626 Multipliersmdzakir_hussainAinda não há avaliações

- BoothDocumento14 páginasBoothFarhat VooDooAinda não há avaliações

- Pipelining - Basic Principles, Classification of Pipeline ProcessorsDocumento30 páginasPipelining - Basic Principles, Classification of Pipeline ProcessorsJoel K SanthoshAinda não há avaliações

- COA Mod 3Documento25 páginasCOA Mod 3Rosh Roy GeorgeAinda não há avaliações

- Practice Problems 12Documento32 páginasPractice Problems 12suduku007Ainda não há avaliações

- Chapter 04Documento33 páginasChapter 04Iqbal Ashfaq Joiya100% (1)

- 8X8 BitmultiplierDocumento26 páginas8X8 BitmultiplierRenju TjAinda não há avaliações

- Binary Arithmetic - Negative Numbers and Subtraction: Not All Integers Are PositiveDocumento7 páginasBinary Arithmetic - Negative Numbers and Subtraction: Not All Integers Are PositiveBharath ManjeshAinda não há avaliações

- FALLSEM2019-20 CSE2001 TH VL2019201000585 Reference Material I 13-Aug-2019 Data Representation and Computer Arithmetic 2019 2010Documento34 páginasFALLSEM2019-20 CSE2001 TH VL2019201000585 Reference Material I 13-Aug-2019 Data Representation and Computer Arithmetic 2019 2010Puneeth SaiAinda não há avaliações

- 10-Floating Point Representation With IEEE Standards and Algorithms For Common Arithmetic operations-30-Jul-2019Material - IDocumento34 páginas10-Floating Point Representation With IEEE Standards and Algorithms For Common Arithmetic operations-30-Jul-2019Material - Ividhi agarwalAinda não há avaliações

- 198:211 Computer Architecture: TopicsDocumento35 páginas198:211 Computer Architecture: TopicsJaswant SinghAinda não há avaliações

- Computer Science 37 Lecture 9Documento17 páginasComputer Science 37 Lecture 9Alexander TaylorAinda não há avaliações

- Arithmetic Operations On Binary Numbers: Two's Complement AdditionDocumento11 páginasArithmetic Operations On Binary Numbers: Two's Complement AdditionAjay RavuriAinda não há avaliações

- Module 6 DldcaDocumento45 páginasModule 6 Dldcasneha chauhanAinda não há avaliações

- Chapter Bit ManipulationDocumento14 páginasChapter Bit ManipulationSWAPNILAinda não há avaliações

- Topic #2 - Data RepresentationDocumento61 páginasTopic #2 - Data RepresentationDavidAinda não há avaliações

- DSD Lectures 13 14Documento13 páginasDSD Lectures 13 14ammar abbasAinda não há avaliações

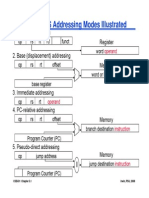

- Review: MIPS Addressing Modes Illustrated: 1. Register Addressing Register 2. Base (Displacement) Addressing MemoryDocumento31 páginasReview: MIPS Addressing Modes Illustrated: 1. Register Addressing Register 2. Base (Displacement) Addressing MemoryAdip ChyAinda não há avaliações

- CS302 2005 2010 Midterm - Solved - MEGA FILEDocumento91 páginasCS302 2005 2010 Midterm - Solved - MEGA FILEAli QureshiAinda não há avaliações

- CS302 2005 2010 Midterm - Solved - MEGA FILEDocumento91 páginasCS302 2005 2010 Midterm - Solved - MEGA FILEattiqueAinda não há avaliações

- CSC340 - HW3Documento28 páginasCSC340 - HW3Daniel sAinda não há avaliações

- Pooja VashisthDocumento51 páginasPooja VashisthApurva SinghAinda não há avaliações

- ECE2030 Introduction To Computer Engineering Lecture 13: Building Blocks For Combinational Logic (4) Shifters, MultipliersDocumento30 páginasECE2030 Introduction To Computer Engineering Lecture 13: Building Blocks For Combinational Logic (4) Shifters, MultipliersNguyễn Nam HảiAinda não há avaliações

- Booth MultiplierDocumento13 páginasBooth MultiplierVimalAinda não há avaliações

- Computer Arithmetic in Computer Organization and ArchitectureDocumento41 páginasComputer Arithmetic in Computer Organization and ArchitectureEswin AngelAinda não há avaliações

- CS M151B / EE M116C: Computer Systems ArchitectureDocumento29 páginasCS M151B / EE M116C: Computer Systems ArchitecturetinhtrilacAinda não há avaliações

- (CSM51A / EE16 S10) Solutions For Midterm: Problem Points Score 1 15 2 10 3 20 4 20 5 15 6 20 Total 100Documento10 páginas(CSM51A / EE16 S10) Solutions For Midterm: Problem Points Score 1 15 2 10 3 20 4 20 5 15 6 20 Total 100krazykrnxboyAinda não há avaliações

- Arth CirDocumento105 páginasArth Cirnoor_dcetAinda não há avaliações

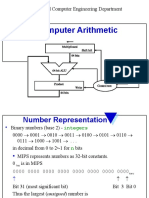

- Computer Arithmetic: Electrical and Computer Engineering DepartmentDocumento72 páginasComputer Arithmetic: Electrical and Computer Engineering Departmentmadhu.nandha9285Ainda não há avaliações

- ALU Inputs and OutputsDocumento63 páginasALU Inputs and OutputsattappAinda não há avaliações

- Vlsi Iiest SBDocumento45 páginasVlsi Iiest SBUshaRaniDashAinda não há avaliações

- William Stallings Computer Organization and ArchitectureDocumento37 páginasWilliam Stallings Computer Organization and ArchitecturereinaldoopusAinda não há avaliações

- Bit Manipulation PDFDocumento16 páginasBit Manipulation PDFmarkAinda não há avaliações

- CH 3Documento30 páginasCH 3Khan AfridiAinda não há avaliações

- CSE 140 Midterm 3 - SolutionDocumento15 páginasCSE 140 Midterm 3 - SolutionyonasAinda não há avaliações

- ARITHMETIC and LOGIC UNIT - in This Lecture, We Will Examine HowDocumento12 páginasARITHMETIC and LOGIC UNIT - in This Lecture, We Will Examine HowbokadashAinda não há avaliações

- Unit 1Documento36 páginasUnit 1Srilekha BolisettiAinda não há avaliações

- Practice Problems 1Documento34 páginasPractice Problems 1akbisoi1Ainda não há avaliações

- Operator: A Set of Symbol Which Deals With Some Operand To Perform Some TaskDocumento15 páginasOperator: A Set of Symbol Which Deals With Some Operand To Perform Some TaskRohan KumarAinda não há avaliações

- 02 SubtractorsDocumento21 páginas02 SubtractorsSarita AninditaAinda não há avaliações

- Tree and Array Multipliers: ECE 645-Computer Arithmetic 3/18/08Documento65 páginasTree and Array Multipliers: ECE 645-Computer Arithmetic 3/18/08Binoy NambiarAinda não há avaliações

- Computer Architecture ECE 361 Lecture 6: ALU DesignDocumento33 páginasComputer Architecture ECE 361 Lecture 6: ALU DesignRahul SinghAinda não há avaliações

- Verilog Updated ProgramsDocumento47 páginasVerilog Updated Programsanand_duraiswamy100% (1)

- GRP 21Documento18 páginasGRP 21tarun_fiemAinda não há avaliações

- Fir Filter Verilog FpgaDocumento10 páginasFir Filter Verilog FpgatkbattulaAinda não há avaliações

- Booth MultiplierDocumento5 páginasBooth Multiplierrahul rAinda não há avaliações

- Unit 2: 18CSC203J-Computer Organization and ArchitectureDocumento106 páginasUnit 2: 18CSC203J-Computer Organization and ArchitectureJEEVAA K G (RA1911043010060)Ainda não há avaliações

- Design For 4-Bit Vedic Multiplier Using VHDL ModuleDocumento12 páginasDesign For 4-Bit Vedic Multiplier Using VHDL Modulekathik goudAinda não há avaliações

- Lecture4 MultiplierDocumento60 páginasLecture4 MultiplierYiAinda não há avaliações

- Assignment 2Documento10 páginasAssignment 2lavish100% (3)

- Vlsi Major ProjectsDocumento2 páginasVlsi Major Projectsinfo.ambesttechnovationAinda não há avaliações

- Radix-4 and Radix-8 Multiplier Using Verilog HDLDocumento6 páginasRadix-4 and Radix-8 Multiplier Using Verilog HDLIJARTETAinda não há avaliações

- Binary To BCDDocumento6 páginasBinary To BCDJamil WolfAinda não há avaliações

- Project ReportDocumento6 páginasProject Report21902492Ainda não há avaliações

- Booth RecodingDocumento3 páginasBooth RecodingJournalNX - a Multidisciplinary Peer Reviewed JournalAinda não há avaliações

- Coa Assignment 2 PDFDocumento3 páginasCoa Assignment 2 PDFVyshnavDuttAinda não há avaliações

- Wallace Tree MultiplierDocumento11 páginasWallace Tree MultiplierdinuarslanAinda não há avaliações

- Ug LPM Alt MfugDocumento133 páginasUg LPM Alt MfugSisuso Sisa SisusoAinda não há avaliações

- Arithmetic and Logic Unit (ALU) PDFDocumento13 páginasArithmetic and Logic Unit (ALU) PDFnathulalusaAinda não há avaliações

- Canonical Signed Digit Representation For FIR Digital FiltersDocumento11 páginasCanonical Signed Digit Representation For FIR Digital FiltersPhuc HoangAinda não há avaliações

- VLSI Design of Low Power Booth MultiplierDocumento3 páginasVLSI Design of Low Power Booth MultiplierPardhasaradhi DamarlaAinda não há avaliações

- 34605284816196ts201 PGRDocumento896 páginas34605284816196ts201 PGRসঞ্জয় মাহাতোAinda não há avaliações

- DSP Lab DemoDocumento37 páginasDSP Lab Demosurendraloya99Ainda não há avaliações

- VLSI Design of Radix-4 Signed-Digit Encoding Based Pre-Encoded MultipliersDocumento20 páginasVLSI Design of Radix-4 Signed-Digit Encoding Based Pre-Encoded Multiplierssurya pratapAinda não há avaliações

- Parallel Implementation of A 4 X 4-Bit MultiplierDocumento4 páginasParallel Implementation of A 4 X 4-Bit MultiplierMathew GeorgeAinda não há avaliações

- 16-Bit Low Power ALUDocumento10 páginas16-Bit Low Power ALUManu KashyapAinda não há avaliações

- Cs 404 Coa Unit II Computer ArithmeticDocumento31 páginasCs 404 Coa Unit II Computer Arithmeticmanali100% (5)

- Design A Low Power Built in Self-Test (BIST) Architecture For Fast Multiplier and Optimize in Terms of Real Time FunctionalityDocumento5 páginasDesign A Low Power Built in Self-Test (BIST) Architecture For Fast Multiplier and Optimize in Terms of Real Time FunctionalityHitesh PradhanAinda não há avaliações

- Arithmetic Unit: Dr. Sowmya BJDocumento146 páginasArithmetic Unit: Dr. Sowmya BJtinni09112003Ainda não há avaliações

- DSP Processors: Circular BufferingDocumento22 páginasDSP Processors: Circular BufferingfidematAinda não há avaliações