Escolar Documentos

Profissional Documentos

Cultura Documentos

Parallel Algorithm For Computing Edt With New Architecture

Enviado por

IAEME PublicationDescrição original:

Título original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Parallel Algorithm For Computing Edt With New Architecture

Enviado por

IAEME PublicationDireitos autorais:

Formatos disponíveis

International Journal of of Electronics and Communication International JournalElectronics and Communication Engineering & Technology (IJECET), ISSN 0976

& Technology (IJECET) Engineering 6464(Print), ISSN 0976 6472(Online) Volume 1, Number 1, Sep - Oct (2010), IAEME ISSN 0976 6464(Print), ISSN 0976 6472(Online) Volume 1, Number 1, Sep - Oct (2010), pp. 01-17 IAEME IAEME, http://www.iaeme.com/ijecet.html

IJECET

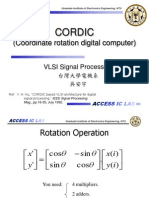

PARALLEL ALGORITHM FOR COMPUTING EDT WITH NEW ARCHITECTURE

Er. Kirti Rawal Lecturer, RIEIT,Railmajra Punjab, E-Mail: erkirti.rawal@gmail.com Er. Sonia Lecturer, BBSBEC Fatehgarh Sahib Er. Rajeev Kumar Patial Sr.Lecturer, LPU Phagwara Mahesh Mudavath Lecturer, RIEIT, Railmajra Punjab, E-Mail: mahesh_chauhan22@yahoo.com

ABSTRACT

A distance transformation converts a binary image consisting of foreground and background pixels into one in where each pixel has a value equal to its nearest background pixel (alternatively, distances could be the to the nearest foreground pixel). This paper provides an area-efficient hardware solution to the computation of EDT on a binary image. A Parallel algorithm for computing EDT of an nn image is presented. Pipelined 2D array architecture for hardware implementation is designed. The architecture has a regular structure with locally connected identical processing elements. Further, pipelining reduces hardware resources. Such array architecture is easily scalable to handle images of different sizes. Keywords Distance Transforms, Euclidean Distance Transform, Parallel Algorithm, Pipelined Architecture.

International Journal of Electronics and Communication Engineering & Technology (IJECET), ISSN 0976 6464(Print), ISSN 0976 6472(Online) Volume 1, Number 1, Sep - Oct (2010), IAEME

1. INTRODUCTION

A distance transform, also known as distance map or distance field, is a representation of a digital image. Applications of distance transform are numerous. These include shape analysis of objects [2], machine vision [3] and image matching [4].

Figure 1 distance transformation Three different distance metrics are commonly used which are following [1]:

Manhattan distance Chessboard distance Euclidean distance

A. Manhattan Distance Transform

The Distance between two points measured along axes at right angles. In a plane with p1 at (x1, y1) and p2 at (x2, y2), it is |x1 - x2| + |y1 - y2|. Manhattan distance is often used in integrated circuits where wires only run parallel to the x or y axis Manhattan distance is often used in integrated circuits where wires only run parallel to the x or y axis. Also known as rectilinear distance, Minkowski's L1 distance, taxi cab metric, or city block distance. The formula for this distance between a point x= (x1, x2, etc.) and a point

n

y= (y1, y2, etc.) is

d = xi yi

i =1

Figure 2 Manhattan distance transformation 2

International Journal of Electronics and Communication Engineering & Technology (IJECET), ISSN 0976 6464(Print), ISSN 0976 6472(Online) Volume 1, Number 1, Sep - Oct (2010), IAEME

B. Chessboard Distance Transform

The Chessboard distance between two spaces on a chess board is the minimum number of moves a king requires to move between them. Below are the Chessboard distances of each square from the square f6. Chessboard Distance is also called maximum value distance or Chebyshev distance. Mathematically it can be written as DChebyshev(p, q) = maxi(| pi qi |).The city block distance, chessboard distance or the combination of those two are used for the benefit of their simplified architectures and integer computations[5-7].

Figure 3 Chessboard Distance Transformations

C. Euclidean Distance Transform

Euclidean Distance Transformation (EDT) is used to convert a digital binary image consisting of object (foreground) and non object (background) pixels into another image where each pixel has a value of the minimum Euclidean distance from non object pixels. Considerable research has been done on development of algorithms for computation of the EDT. Several sequential [8-11] and parallel [12-16] algorithms are available. Some work on parallel algorithms targeted to general-purpose processors is also known [17, 18]. Out of these three distance transforms EDT find widespread use.

2. PARALLEL ALGORITHM

In this paper, a parallel algorithm is presented. The salient feature of this algorithm is that the computation of EDT involves only integer arithmetic operations within a small neighbourhood of each pixel and hence it is suitable for mapping onto high

International Journal of Electronics and Communication Engineering & Technology (IJECET), ISSN 0976 6464(Print), ISSN 0976 6472(Online) Volume 1, Number 1, Sep - Oct (2010), IAEME

speed array architecture. The Euclidean distance is given by dp = r 2 + c 2 [19]. ( r, c) of background pixels are initialized to (0, 0) and those of foreground pixels are computed iteratively starting from the pixels nearby background and moving towards the far away pixels. That is, dp lies within (k - 0.5, k + 0.5] i.e. for k =1 its value lies between 0.5 to 1.5.Hence dp is not integer because from 0.5 to 1.5 there are some floating point numbers i.e. 0.7, 0.9 etc. So we take d2p whose values lies within ( k2 - k, k2 + k) since d2p is an integer. However, d2p is quite large in magnitude and it requires a large storage space in hardware. For K=1, value lies within k2-k to k2+k = (12 -1) to (12 +1) = 0 to 2. Thus range of d2p is from 0 to 2. For K=2, value lies within k2-k to k2+k = (22 -2) to (22 +2) = 2 to 6. So we take (p) which is less than d2p is given by (p) = k2+k - d2p. Here d2p is derived first and then substituted to find (p). A new integer quantity (p) which is much smaller than d2(p) is defined as (k2 + k) - d2p. d2p can be derived using the already computed ( r, c) of eight neighbors pi, i = 18, surrounding p. It is given by [min ri2 + ci2] where ri = (pi) if pi is in the same row of p. Otherwise, terms of c(pi). ri = r(pi) + 1. The increment by 1 is due to p being displaced from pi by one row. Similarly, ci is given in

3. STEPS OF PARALLEL ALGORITHM

There are three steps of parallel algorithm which are used to compute Euclidean distance transform. Step 1: Compute ri, ci and i , i = 1 to 8.

Figure 4 Euclidean distance from reference value to the same column (above)

International Journal of Electronics and Communication Engineering & Technology (IJECET), ISSN 0976 6464(Print), ISSN 0976 6472(Online) Volume 1, Number 1, Sep - Oct (2010), IAEME

Euclidean Distance dp= d2 p = r2 + c2 d2 p = 12 + 02 = 1

r 2 + c 2

(p) = k2+k - d2p = 12+1 1 = 1 In this way all values of Euclidean distance for k = 1 are computed.

Figure 5 Euclidean distance values for k=1

Figure 6 Euclidean distance from Reference value to the different row (Above) and different column (L.H.S) Euclidean Distance dp= d2p = r2 + c2 d2p = 22 + 12 = 5 (p) = k2+k - d2p = 22+2 5 = 1 In this way all values of Euclidean distance for k = 2 are computed.

r 2 + c 2

International Journal of Electronics and Communication Engineering & Technology (IJECET), ISSN 0976 6464(Print), ISSN 0976 6472(Online) Volume 1, Number 1, Sep - Oct (2010), IAEME

Figure 7 Euclidean distance values for k=2

Figure 8 Euclidean distance values from reference value to corner side (above) Euclidean Distance dp= d2 p = r2 + c2 d2 p = 22 + 22 = 8 (p) = k2+k - d2p = 32+3 8 = 4 In this way all values of Euclidean distance for k = 3 are computed.

r 2 + c 2

International Journal of Electronics and Communication Engineering & Technology (IJECET), ISSN 0976 6464(Print), ISSN 0976 6472(Online) Volume 1, Number 1, Sep - Oct (2010), IAEME

Figure 9 Euclidean distance values for k = 3

Step 2: To find Maximum values

Consider i values corresponding to neighbors pi whose done (pi) = 1. Find the maximum, say m. In step 2 , d2(p) can be rewritten as min[d2(pi) + Ri + Ci] where Ri = 0 if pi is in the same row of p. Otherwise, Ri = 2 r(pi) + 1. (p) is now derived as follows. (p) = k2+k - d2p = max [ k2+k - d2 pi - Ri - Ci] = max [ pi - Ri - Ci] = max [i ] Consider iteration k = 2. of those twelve pixels whose ( r, computed at k =1 are incremented by 2k (i.e. 4). c) have been

Figure 10 Maximum value of Euclidean distance from reference value to different row and different column (L.H.S)

International Journal of Electronics and Communication Engineering & Technology (IJECET), ISSN 0976 6464(Print), ISSN 0976 6472(Online) Volume 1, Number 1, Sep - Oct (2010), IAEME

= 5 - 3 3 = -1 Where Ri = 2 rpi + 1 and = 2 1+1 = 3 Ci = 2 cpi + 1 = 2 1+1 = 3

Step 3: To find overlapped delta values, If done(p) = 0 and m 0, then r(p)= rm, c(p)= cm, (p) =m and done(p) =1. If done(p) = 1, then (p) = (p) + 2k.

To keep track of pixels whose ( r, c) have been computed, a flag done is assigned to each pixel, whose value is set to 1 when the transform values of pixels are computed at any iteration. Overlapped values for k=1 are computed as follows If previous value of (p) is 0 (for k=0), then value for k=1 are computed by using the formula (p) = (p) + 2k. = 0 + 21 = 2

Figure 11 Overlapped value in k = 1 Similarly overlapped values for k=2 are computed as follows If previous value of (p) is 2 (for k=1), then value for k=2 are computed by using the formula max (i ) = max (pi ) - Ri - Ci (p) = (p) + 2k. = 2 + 22 = 6

International Journal of Electronics and Communication Engineering & Technology (IJECET), ISSN 0976 6464(Print), ISSN 0976 6472(Online) Volume 1, Number 1, Sep - Oct (2010), IAEME

Figure 12 Overlapped value in k = 2 Similarly overlapped values for k=3 are also computed by using the formula. (p) = (p) + 2k. = 6 + 23 = 12 In this way all the overlapped values of delta are computed.

4. PIPELINED ARCHITECTURE FOR COMPUTING EDT

The computation of i, Ri and Ci are computed first based on the position of neighbors pi. Ri (or Ci) takes either 0 or 2 r(pi) + 1 (or 2 c(pi) + 1). Therefore, the computation of ri and ci requires incrementers while the computation of i requires adders and subtractors [32]. Pipelined Architecture for computing EDT is as shown in figure 13

Squaring Circuit for r and c:

Squaring circuit is used to square the inputs of r and c in order to get the output rsq and csq. The maximum value of r and c is 2 so only two bits are required to represent 0,1and 2. The maximum value of rsq and csq is 4 so four bits are used to represent 0,1and 4.

Squaring Circuit for k:

Squaring circuit is used to square the inputs of k in order to get the output ksq. The maximum value of k is 3 so only two bits are required to represent 0, 1, 2 and 3. The maximum value of ksq is 9 so four bits are used to represent 0, 1, 4 and 9.

International Journal of Electronics and Communication Engineering & Technology (IJECET), ISSN 0976 6464(Print), ISSN 0976 6472(Online) Volume 1, Number 1, Sep - Oct (2010), IAEME

Full Adder for k and ksq:

Here 4bit full adder is used to add the values of k and ksq in order to get the output tot. The maximum value of k is 3 and ksq is 9 so four bits are required to represent ksq. The maximum value of tot is 12 so four bits are used to represent tot values. In this case there is no carry input i.e. cin1 and no carry output i.e. cout1 so both will remain zero.

Subtractor for dp and total:

Here subtractor is used to subtract the values of dp and tot in order to get the output del_p. The maximum value of dp is 8 and tot is 12 so four bits are required to represent dp and tot values. Del_p (delta) comes at the output through wire del_p_1.

Pipelined Register1:

Pipelined register1 is used to store all the r, c and delta values which are calculated in stage 1.The inputs of pipelined register1 is r1_0 to r1_29, c1_0 to c1_29 and del1_p0 to del1_p29 and output of pipelined register 1 is r0 to r29, c0 to c29 and del_p0 to del_p29.The main advantage of using pipelined register1 is the moment at which value is stored at the input, it comes at the output of pipelined register instantly. It does not wait to fill all the values in the register. These r and c values are those values which we are applying at the input of stage 1 and delta values are coming from the output of subtractor. With the help of wire we are using r and c values at the input of pipelined register1. So that EDT is computed only for those r and c values rather than any other value.

Counter:

Five bit counter is used to give output of subtractor i.e. delta values to input of pipelined register1.The inputs of five bit counter is clk_1 and clear having 1bit each. The output of counter is q_1 (5bit). Now q_1 is assigned to address of pipelined register1 so that when the output of counter is incremented then address is also incremented by filling delta values (del_p_1) one by one. When output of counter reach at 29th value, at that time pipelined register is completely filled. By giving next clk_1 again output of counter and address comes at zero position.

10

International Journal of Electronics and Communication Engineering & Technology (IJECET), ISSN 0976 6464(Print), ISSN 0976 6472(Online) Volume 1, Number 1, Sep - Oct (2010), IAEME

Figure 13 Pipelined Architecture for computing EDT 11

International Journal of Electronics and Communication Engineering & Technology (IJECET), ISSN 0976 6464(Print), ISSN 0976 6472(Online) Volume 1, Number 1, Sep - Oct (2010), IAEME

In this way all values of delta i.e. EDT are computed with this new architecture. The pipelined architecture consists of various blocks such as squaring circuit, full adder, full subtractor, pipelined registers, comparators and multiplexers. Out of these blocks, output of each block has to be computed individually

5.

SIMULATION RESULTS

In order to obtain results Verilog language has been used. Verilog Hardware

Description Language (HDL) is used for computing EDT, which can describe hardware requirements of the architecture not only at the gate level, register level but at the algorithmic level [20]. Verilog HDL is one of the two most common Hardware

Description Languages (HDL) used by integrated circuit (IC) designers [21]. For writing the code Xilinx is used and for simulation or to see the output waveforms Modelsim has been used. Figure 14, 15, 16 explains how the r_t, c_t, k_t, q_5_t, k_new_t, c_in1_t, cin1_t, clk_1_t, clear_1_t, and flag_t inputs are applied to produce output output_data. Here we consider 30 cases, in which different values of r_t and c_t are applied in order to produce different values of delta. Carry inputs are always zero and clk_t and flag_t is always 1. The value of k_t varies from 1 to 3. Here we take k_t = 01, q_5_t and k_new_t=11.Giving all these inputs we get complete delta values for 30 inputs i.e. output_data.

Figure 14 Waveform of Calculation of overlapped delta operation 12

International Journal of Electronics and Communication Engineering & Technology (IJECET), ISSN 0976 6464(Print), ISSN 0976 6472(Online) Volume 1, Number 1, Sep - Oct (2010), IAEME

Figure 15 Waveform of Calculation of overlapped delta operation

Figure 16 Waveform of Calculation of overlapped delta operation

13

International Journal of Electronics and Communication Engineering & Technology (IJECET), ISSN 0976 6464(Print), ISSN 0976 6472(Online) Volume 1, Number 1, Sep - Oct (2010), IAEME

6. CONCLUSIONS

A distance transformation converts a binary image consisting of foreground and background pixels into one in where each pixel has a value equal to its nearest background pixel (alternatively, distances could be the to the nearest foreground pixel). The types of transforms used generally are city block distance transform, chessboard distance transform and Euclidean distance transform. Of these EDT find widespread use in view of the natural metric employed. The pipelined architecture is presented in this dissertation proved to be applicable for computation of Euclidean distance transform. It comprises two dimensional arrays of locally interconnected processing elements where each element is a sequential logic and all elements are operated synchronously. This architecture is designed in such a way that it works on the steps of parallel algorithm. The algorithm involves only integer arithmetic operations. The architecture is fully digital and it is easily scalable for an image of any nn size.

7. FUTURE SCOPE

Proposed methodology can be used as an important tool in image analysis. Keeping in view the importance of image processing, it is required that the architecture should be robust, accurate as well as faster in order to handle images of different sizes. So, there is always perpetual need for improvements. 1. The ideas presented for the case of 4 pixels per processing element readily extend to the case of more than 4 pixels per processing element (such as 9,16 and so on). 2. 3. 4. 5. The given architecture can be further modified to handle 3D images. The work can be carried out to make it more robust. The given architecture can be implemented on FPGA device. The given source code is optimized to get synthesizable results.

14

International Journal of Electronics and Communication Engineering & Technology (IJECET), ISSN 0976 6464(Print), ISSN 0976 6472(Online) Volume 1, Number 1, Sep - Oct (2010), IAEME

8.

[1]

REFERENCES

C. Tony Huang and O. Robert Mitchell (1991), Rapid Euclidean distance transform using grayscale morphology decomposition, IEEE Computer Society Conference on Pattern Analysis and Machine Intelligence ,1991,vol.14, pp. 695697.

[2]

P. Danielsson (1978), A new shape factor, Computer Graphics and Image Processing 1978, vol.2, pp. 292299.

[3]

D.Paglieroni (1992), Distance transforms: properties and machine vision applications, CVGIP: Graphical Models and Image Processing, vol.54, 1992, pp. 5674.

[4]

D.P. Huttenlocher, G.A. Klanderman, W.J. Rucklidge (1993), Comparing images using the Hausdorff distance, IEEE Transactions on Pattern Analysis and Machine Intelligence, vol. 15 ,1993, pp. 850863.

[5]

P. A. Maragos and R. W. Schafer, Morphological skeleton representation and coding of binary images, IEEE Trans. Acoustic Speech, Signal Processing, vol. ASSP-34, no.5, 1986, pp. 1228-1244.

[6]

S. R. Stemberg, Grayscale morphology, Computer Vision Graphics and Image Processing, vol. 35, 1986, pp. 333-355.

[7]

J. Toriwaki and S. Yokoi. Distance transformations and skeletons of digitized pictures with applications, in Progress in Pattern Recognition, 1981, pp. 187-264.

[8]

H. Breu, J. Gil, D. Kirkpatrick, M. Werman (1995), Linear time Euclidean distance transform algorithms, IEEE Transactions on Pattern Analysis and Machine Intelligence, vol.17 ,1995, pp. 529 533.

[9]

S. Pavel, S.G. Akl (1995), Efficient algorithms for the Euclidean distance transform, Parallel Processing Letters, vol.5, 1995, pp. 205212.

[10] Hinnik Eggers (1998), Two fast Euclidean distance transformations in z2 based on sufficient propagation, Computer Vision and Image Understanding vol.69, 1998, pp. 106116. [11] J. Maurer, R. Calvin, R. Qi, V. Raghavan (2003), A linear time algorithm for computing exact Euclidean distance transforms of binary images in arbitrary

15

International Journal of Electronics and Communication Engineering & Technology (IJECET), ISSN 0976 6464(Print), ISSN 0976 6472(Online) Volume 1, Number 1, Sep - Oct (2010), IAEME

dimensions, IEEE Transactions on Pattern Analysis and Machine Intelligence, vol.25, 2003, pp. 265270. [12] Hugo Embrechts, Dirk Roose (1996), Parallel Euclidean distance transformation algorithm, Computer Vision and Image Understanding vol.63, 1996, pp. 1526. [13] Hinnik Eggers (1996), Parallel Euclidean distance transformations in zng, Parallel Recognition Letters, vol. 17, 1996, pp. 751757. [14] T. Hirata, A unified linear-time algorithm for computing distance maps(1996), Information Processing Letters, vol.58, 1996, pp. 129133. [15] N. Sudha, S. Nandi, K. Sridharan (1998), Efficient computation of Euclidean distance transform for applications in image processing, Proceedings of IEEE TENCON vol.2,1998, pp. 4952. [16] Yu-Hua Lee, Shi-Jinn Horng, Jennifer Seitzer (2003), Parallel computation of the Euclidean distance transform on a three-dimensional image array, IEEE Transactions on Parallel and Distributed Systems, vol. 14,2003, pp. 203212. [17] L. Chen, H.Y.H. Chuang (1995), An efficient algorithm for complete Euclidean distance transform on mesh-connected SIMD, Parallel Computing, vol. 21, 1995, pp. 841852. [18] Y. Pan, M. Hamdi, K. Li (2000), Euclidean distance transform for binary images on reconfigurable mesh-connected computers, IEEE Transactions on Systems, Man Cybernetics, vol. 30 ,2000, pp. 240244. [19] N. Sudha (2005), A pipelined array architecture for Euclidean distance transformation and its FPGA implementation, Microprocessors and Microsystems, vol. 29, 2005, pp. 405410. [20] J. Bhaskar (1998), Verilog HDL Synthesis a Practical Primer, second edition, 1998, pp.1-230. [21] Peter M. Nyasulu (2001), Introduction to Verilog, third edition, 2001, pp.1-30.

16

International Journal of Electronics and Communication Engineering & Technology (IJECET), ISSN 0976 6464(Print), ISSN 0976 6472(Online) Volume 1, Number 1, Sep - Oct (2010), IAEME

BIO DATA OF AUTHORS

Ms. Kirti Rawal is working as an Lecturer in the Electronics and Communications Engineering Department, R.I.E.I.T, Railmajra (Punjab). She earned her M.Tech (ECE) Degree from BBSBEC Fatehgarh Sahib (Punjab) in 2010 and B.Tech (ECE) Degree from IITT Pojewal (Nawanshahr). She has published 2 research papers in International Conferences and national Conferences. She is a Life Membership of the Indian Society for Technical Education (ISTE).

Mr. Mahesh Mudavath is working as an Lecturer in the Electronics and Communications Engineering Department, R.I.E.I.T, Railmajra (Punjab). He earned his M.Tech (VLSI Design) Degree from C-DAC, Mohali (Punjab) in 2009 and B.Tech (ECE) Degree from JNTU, Hyderabad (Andhra Pradesh). He has published 6 research papers in International Journals and International Conferences. He is a Life Membership of the Indian Society for Technical Education (ISTE).

17

Você também pode gostar

- OOP - C# Exercises: Excercise 1: Write A Program To Calculate The Area, The Perimeter of The RectangleDocumento4 páginasOOP - C# Exercises: Excercise 1: Write A Program To Calculate The Area, The Perimeter of The RectangleLong HípAinda não há avaliações

- NG - Argument Reduction For Huge Arguments: Good To The Last BitDocumento8 páginasNG - Argument Reduction For Huge Arguments: Good To The Last BitDerek O'ConnorAinda não há avaliações

- Envision Algebra 1 AnswersDocumento64 páginasEnvision Algebra 1 AnswersMahmoud SolimanAinda não há avaliações

- A Fast Algorithm of The DCT and IDCT For VLSI ImplementationDocumento4 páginasA Fast Algorithm of The DCT and IDCT For VLSI ImplementationTom MathewAinda não há avaliações

- IT6501 Notes RejinpaulDocumento109 páginasIT6501 Notes RejinpaulSuraj KumarAinda não há avaliações

- Lee Yang ReportDocumento14 páginasLee Yang ReportauroshisdasAinda não há avaliações

- On The K-Ary Hypercube: Theoretical Computer Science 140 (1995) 333-339Documento7 páginasOn The K-Ary Hypercube: Theoretical Computer Science 140 (1995) 333-339Khánh DuyAinda não há avaliações

- Dce: A N Ovel D Elay C Orrelation M Easurement For T Omography With P Assive R EalizationDocumento11 páginasDce: A N Ovel D Elay C Orrelation M Easurement For T Omography With P Assive R EalizationijdpsAinda não há avaliações

- Computer GraphicsDocumento59 páginasComputer GraphicsKanika KadianAinda não há avaliações

- Computer Graphics Notes Unit - 1 & 2Documento41 páginasComputer Graphics Notes Unit - 1 & 2Gowtham SKAinda não há avaliações

- 883 1304 2 PBDocumento6 páginas883 1304 2 PBchandrasekhar akkapeddiAinda não há avaliações

- Elliptic Curve Cryptography On Embedded Multicore SystemsDocumento6 páginasElliptic Curve Cryptography On Embedded Multicore SystemsYuri ShukhrovAinda não há avaliações

- An Algorithm For Line Drawing Using Parametric Equation PDFDocumento8 páginasAn Algorithm For Line Drawing Using Parametric Equation PDFLee Chan PeterAinda não há avaliações

- A Computational Method With MAPLE For A Piecewise Polynomial Approximation To The Trigonometric FunctionsDocumento11 páginasA Computational Method With MAPLE For A Piecewise Polynomial Approximation To The Trigonometric FunctionsAurangZaib LaghariAinda não há avaliações

- Filtering Techniques Applied To Streaming Video and Control ApplicationsDocumento15 páginasFiltering Techniques Applied To Streaming Video and Control ApplicationsMarek SzczepanskiAinda não há avaliações

- Fuculty of Informatics Departement of Computer ScienceDocumento16 páginasFuculty of Informatics Departement of Computer Sciencesamuel fikiruAinda não há avaliações

- 14Documento13 páginas14admin2146Ainda não há avaliações

- Image Characterization by Fast Calculation of Low-Order: Legendre MomentsDocumento6 páginasImage Characterization by Fast Calculation of Low-Order: Legendre MomentsPinku MeenaAinda não há avaliações

- 4041-Article Text PDF-7799-1-10-20130718Documento13 páginas4041-Article Text PDF-7799-1-10-20130718Miloš BasarićAinda não há avaliações

- IT6501 Notes PDFDocumento109 páginasIT6501 Notes PDFsowrishalAinda não há avaliações

- Ijgip: DWT-DCT Based Iris Recognition Technique Using Self Organizing Map Neural NetworkDocumento7 páginasIjgip: DWT-DCT Based Iris Recognition Technique Using Self Organizing Map Neural Networkprofessor_manojAinda não há avaliações

- The Fuze Doppler Echo Algorithm of Near-Field Electromagnetic Scattering ModelDocumento5 páginasThe Fuze Doppler Echo Algorithm of Near-Field Electromagnetic Scattering Modelتپل خستهAinda não há avaliações

- Analysis of Simple CORDIC Algorithm Using MATLABDocumento3 páginasAnalysis of Simple CORDIC Algorithm Using MATLABamit.18.singh2466Ainda não há avaliações

- Brent and McMillan - 2021 - Some New Algorithms For High-Precision ComputationDocumento9 páginasBrent and McMillan - 2021 - Some New Algorithms For High-Precision ComputationsizukhuranaAinda não há avaliações

- R, (A) L (A) : 1, R I (A) 1, (01) Z (1 0) (0 1) 3, I 2 (B) 1, I I (B)Documento4 páginasR, (A) L (A) : 1, R I (A) 1, (01) Z (1 0) (0 1) 3, I 2 (B) 1, I I (B)Arun KumarAinda não há avaliações

- Square Rooting Algorithms For Integer and Floating-Point NumbersDocumento5 páginasSquare Rooting Algorithms For Integer and Floating-Point NumbersJayaram KumarAinda não há avaliações

- Pipelined Cordic Architecture and Its Implementation On SimulinkDocumento10 páginasPipelined Cordic Architecture and Its Implementation On SimulinkMohamed GanounAinda não há avaliações

- Implementation of Cordic Algorithm Using Matlab & VHDL For Wlan ReceiverDocumento3 páginasImplementation of Cordic Algorithm Using Matlab & VHDL For Wlan ReceiverHemant SaraswatAinda não há avaliações

- Scaling Free CORDIC Algorithm Implementation of Sine and Cosine FunctionDocumento4 páginasScaling Free CORDIC Algorithm Implementation of Sine and Cosine FunctionharivarahiAinda não há avaliações

- 2003 CILAMCE On The Visualization of Domain Results Boundary Element AnalysisDocumento15 páginas2003 CILAMCE On The Visualization of Domain Results Boundary Element AnalysisRemo Magalhães de SouzaAinda não há avaliações

- Daa Unit 3Documento22 páginasDaa Unit 3Rahul GusainAinda não há avaliações

- CMPE 300 PROJECT Spring 2005 Branch and Bound Algorithm For Multiuser Detection in Synchronous Cdma SystemsDocumento3 páginasCMPE 300 PROJECT Spring 2005 Branch and Bound Algorithm For Multiuser Detection in Synchronous Cdma Systemsmatlab1983Ainda não há avaliações

- Cordic: (Coordinate Rotation Digital Computer)Documento25 páginasCordic: (Coordinate Rotation Digital Computer)santhiyadevAinda não há avaliações

- Cordic: (Coordinate Rotation Digital Computer)Documento25 páginasCordic: (Coordinate Rotation Digital Computer)Magdalene MilanAinda não há avaliações

- Solution Lab 1 DN2221, KTHDocumento17 páginasSolution Lab 1 DN2221, KTHleSebaAinda não há avaliações

- Artículo 1 - Identification of Control Parameters of The Permanent MagneticDocumento8 páginasArtículo 1 - Identification of Control Parameters of The Permanent MagneticANDERSON ADONIS SOSA LOPEZAinda não há avaliações

- A 4 Point Interpolatory Subdivision Scheme For Curve DesignDocumento13 páginasA 4 Point Interpolatory Subdivision Scheme For Curve DesignFarhana MehmoodAinda não há avaliações

- Computer Graphics Lec - 1Documento27 páginasComputer Graphics Lec - 1west_lmnAinda não há avaliações

- The International Journal of Engineering & ScienceDocumento8 páginasThe International Journal of Engineering & SciencetheijesAinda não há avaliações

- International Journal of Computational Engineering Research (IJCER)Documento6 páginasInternational Journal of Computational Engineering Research (IJCER)International Journal of computational Engineering research (IJCER)Ainda não há avaliações

- Steering and Visualization of Electro-Magnetic Simulations Using The Globus Implementation of A Computational GridDocumento16 páginasSteering and Visualization of Electro-Magnetic Simulations Using The Globus Implementation of A Computational GridIdris TarwalaAinda não há avaliações

- Design of Multichannel AP-DCD Algorithm Using Matlab: Sasmita DeoDocumento5 páginasDesign of Multichannel AP-DCD Algorithm Using Matlab: Sasmita DeoParamesh WaranAinda não há avaliações

- Sampling and Quantization Theory For Image Processing: IraldiDocumento5 páginasSampling and Quantization Theory For Image Processing: Iraldihub23Ainda não há avaliações

- DCT Presentation1Documento39 páginasDCT Presentation1party0703Ainda não há avaliações

- "K Nearest and Furthest Points in M-Dimensional SpaceDocumento3 páginas"K Nearest and Furthest Points in M-Dimensional SpaceYeshwanth KumarAinda não há avaliações

- Implementation and Performance Analysis PDFDocumento5 páginasImplementation and Performance Analysis PDFMohamed GanounAinda não há avaliações

- Lecture03 GraphicsPrimitivesDocumento66 páginasLecture03 GraphicsPrimitivesBeer ThunradaAinda não há avaliações

- The Finite-Difference Time-Domain (FDTD) Algorithm: James R. NagelDocumento7 páginasThe Finite-Difference Time-Domain (FDTD) Algorithm: James R. NagelRajesh UpadhyayAinda não há avaliações

- Kernel Isomap: Heeyoul Choi and Seungjin ChoiDocumento6 páginasKernel Isomap: Heeyoul Choi and Seungjin ChoiMaria LomeliAinda não há avaliações

- Pixel-Based Change Detection Methods: 2.1 Image DifferencingDocumento16 páginasPixel-Based Change Detection Methods: 2.1 Image DifferencingEmil TengwarAinda não há avaliações

- Points, Lines, Circles and Ellipses As Primitives, Conversion Algorithms For PrimitivesDocumento26 páginasPoints, Lines, Circles and Ellipses As Primitives, Conversion Algorithms For Primitivesn9166254105Ainda não há avaliações

- On Discrete Cosine Transform: Jianqin ZhouDocumento6 páginasOn Discrete Cosine Transform: Jianqin ZhoumacosxloverAinda não há avaliações

- CGL Lab ManualDocumento30 páginasCGL Lab Manualdecember buenoAinda não há avaliações

- Comparison of Omega-K and Backprojecction Regarding Spatial Resolution For Squinted Spotlight SAR With Motion ErrorsDocumento5 páginasComparison of Omega-K and Backprojecction Regarding Spatial Resolution For Squinted Spotlight SAR With Motion ErrorsWesley GeorgeAinda não há avaliações

- A High-Speed and Low-Latency Reed-Solomon Decoder Based On A Dual-Line StructureDocumento2 páginasA High-Speed and Low-Latency Reed-Solomon Decoder Based On A Dual-Line Structure22kishor1111Ainda não há avaliações

- On The Capacitated Vehicle Routing Problem: Springer-Verlag 2002Documento17 páginasOn The Capacitated Vehicle Routing Problem: Springer-Verlag 2002Kevin FinkenzellerAinda não há avaliações

- Direct Digital Frequency Synthesizer With CORDIC AlgorithmDocumento12 páginasDirect Digital Frequency Synthesizer With CORDIC AlgorithmYermakov Vadim IvanovichAinda não há avaliações

- RK4 MethodDocumento6 páginasRK4 MethodfurqanhamidAinda não há avaliações

- Design & Analysis of Algorithms (DAA) Unit - IIIDocumento17 páginasDesign & Analysis of Algorithms (DAA) Unit - IIIYogi NambulaAinda não há avaliações

- Ten-Decimal Tables of the Logarithms of Complex Numbers and for the Transformation from Cartesian to Polar Coordinates: Volume 33 in Mathematical Tables SeriesNo EverandTen-Decimal Tables of the Logarithms of Complex Numbers and for the Transformation from Cartesian to Polar Coordinates: Volume 33 in Mathematical Tables SeriesAinda não há avaliações

- Determinants Affecting The User's Intention To Use Mobile Banking ApplicationsDocumento8 páginasDeterminants Affecting The User's Intention To Use Mobile Banking ApplicationsIAEME PublicationAinda não há avaliações

- Broad Unexposed Skills of Transgender EntrepreneursDocumento8 páginasBroad Unexposed Skills of Transgender EntrepreneursIAEME PublicationAinda não há avaliações

- Voice Based Atm For Visually Impaired Using ArduinoDocumento7 páginasVoice Based Atm For Visually Impaired Using ArduinoIAEME PublicationAinda não há avaliações

- Modeling and Analysis of Surface Roughness and White Later Thickness in Wire-Electric Discharge Turning Process Through Response Surface MethodologyDocumento14 páginasModeling and Analysis of Surface Roughness and White Later Thickness in Wire-Electric Discharge Turning Process Through Response Surface MethodologyIAEME PublicationAinda não há avaliações

- Impact of Emotional Intelligence On Human Resource Management Practices Among The Remote Working It EmployeesDocumento10 páginasImpact of Emotional Intelligence On Human Resource Management Practices Among The Remote Working It EmployeesIAEME PublicationAinda não há avaliações

- Analyse The User Predilection On Gpay and Phonepe For Digital TransactionsDocumento7 páginasAnalyse The User Predilection On Gpay and Phonepe For Digital TransactionsIAEME PublicationAinda não há avaliações

- A Study On The Reasons For Transgender To Become EntrepreneursDocumento7 páginasA Study On The Reasons For Transgender To Become EntrepreneursIAEME PublicationAinda não há avaliações

- Visualising Aging Parents & Their Close Carers Life Journey in Aging EconomyDocumento4 páginasVisualising Aging Parents & Their Close Carers Life Journey in Aging EconomyIAEME PublicationAinda não há avaliações

- Influence of Talent Management Practices On Organizational Performance A Study With Reference To It Sector in ChennaiDocumento16 páginasInfluence of Talent Management Practices On Organizational Performance A Study With Reference To It Sector in ChennaiIAEME PublicationAinda não há avaliações

- Attrition in The It Industry During Covid-19 Pandemic: Linking Emotional Intelligence and Talent Management ProcessesDocumento15 páginasAttrition in The It Industry During Covid-19 Pandemic: Linking Emotional Intelligence and Talent Management ProcessesIAEME PublicationAinda não há avaliações

- Gandhi On Non-Violent PoliceDocumento8 páginasGandhi On Non-Violent PoliceIAEME PublicationAinda não há avaliações

- A Study of Various Types of Loans of Selected Public and Private Sector Banks With Reference To Npa in State HaryanaDocumento9 páginasA Study of Various Types of Loans of Selected Public and Private Sector Banks With Reference To Npa in State HaryanaIAEME PublicationAinda não há avaliações

- A Study On The Impact of Organizational Culture On The Effectiveness of Performance Management Systems in Healthcare Organizations at ThanjavurDocumento7 páginasA Study On The Impact of Organizational Culture On The Effectiveness of Performance Management Systems in Healthcare Organizations at ThanjavurIAEME PublicationAinda não há avaliações

- Role of Social Entrepreneurship in Rural Development of India - Problems and ChallengesDocumento18 páginasRole of Social Entrepreneurship in Rural Development of India - Problems and ChallengesIAEME PublicationAinda não há avaliações

- A Proficient Minimum-Routine Reliable Recovery Line Accumulation Scheme For Non-Deterministic Mobile Distributed FrameworksDocumento10 páginasA Proficient Minimum-Routine Reliable Recovery Line Accumulation Scheme For Non-Deterministic Mobile Distributed FrameworksIAEME PublicationAinda não há avaliações

- A Study On Talent Management and Its Impact On Employee Retention in Selected It Organizations in ChennaiDocumento16 páginasA Study On Talent Management and Its Impact On Employee Retention in Selected It Organizations in ChennaiIAEME PublicationAinda não há avaliações

- A Multiple - Channel Queuing Models On Fuzzy EnvironmentDocumento13 páginasA Multiple - Channel Queuing Models On Fuzzy EnvironmentIAEME PublicationAinda não há avaliações

- Various Fuzzy Numbers and Their Various Ranking ApproachesDocumento10 páginasVarious Fuzzy Numbers and Their Various Ranking ApproachesIAEME PublicationAinda não há avaliações

- Knowledge Self-Efficacy and Research Collaboration Towards Knowledge Sharing: The Moderating Effect of Employee CommitmentDocumento8 páginasKnowledge Self-Efficacy and Research Collaboration Towards Knowledge Sharing: The Moderating Effect of Employee CommitmentIAEME PublicationAinda não há avaliações

- EXPERIMENTAL STUDY OF MECHANICAL AND TRIBOLOGICAL RELATION OF NYLON/BaSO4 POLYMER COMPOSITESDocumento9 páginasEXPERIMENTAL STUDY OF MECHANICAL AND TRIBOLOGICAL RELATION OF NYLON/BaSO4 POLYMER COMPOSITESIAEME PublicationAinda não há avaliações

- Application of Frugal Approach For Productivity Improvement - A Case Study of Mahindra and Mahindra LTDDocumento19 páginasApplication of Frugal Approach For Productivity Improvement - A Case Study of Mahindra and Mahindra LTDIAEME PublicationAinda não há avaliações

- Dealing With Recurrent Terminates in Orchestrated Reliable Recovery Line Accumulation Algorithms For Faulttolerant Mobile Distributed SystemsDocumento8 páginasDealing With Recurrent Terminates in Orchestrated Reliable Recovery Line Accumulation Algorithms For Faulttolerant Mobile Distributed SystemsIAEME PublicationAinda não há avaliações

- Optimal Reconfiguration of Power Distribution Radial Network Using Hybrid Meta-Heuristic AlgorithmsDocumento13 páginasOptimal Reconfiguration of Power Distribution Radial Network Using Hybrid Meta-Heuristic AlgorithmsIAEME PublicationAinda não há avaliações

- Analysis of Fuzzy Inference System Based Interline Power Flow Controller For Power System With Wind Energy Conversion System During Faulted ConditionsDocumento13 páginasAnalysis of Fuzzy Inference System Based Interline Power Flow Controller For Power System With Wind Energy Conversion System During Faulted ConditionsIAEME PublicationAinda não há avaliações

- Quality of Work-Life On Employee Retention and Job Satisfaction: The Moderating Role of Job PerformanceDocumento7 páginasQuality of Work-Life On Employee Retention and Job Satisfaction: The Moderating Role of Job PerformanceIAEME PublicationAinda não há avaliações

- A Review of Particle Swarm Optimization (Pso) AlgorithmDocumento26 páginasA Review of Particle Swarm Optimization (Pso) AlgorithmIAEME PublicationAinda não há avaliações

- Moderating Effect of Job Satisfaction On Turnover Intention and Stress Burnout Among Employees in The Information Technology SectorDocumento7 páginasModerating Effect of Job Satisfaction On Turnover Intention and Stress Burnout Among Employees in The Information Technology SectorIAEME PublicationAinda não há avaliações

- Financial Literacy On Investment Performance: The Mediating Effect of Big-Five Personality Traits ModelDocumento9 páginasFinancial Literacy On Investment Performance: The Mediating Effect of Big-Five Personality Traits ModelIAEME PublicationAinda não há avaliações

- Prediction of Average Total Project Duration Using Artificial Neural Networks, Fuzzy Logic, and Regression ModelsDocumento13 páginasPrediction of Average Total Project Duration Using Artificial Neural Networks, Fuzzy Logic, and Regression ModelsIAEME PublicationAinda não há avaliações

- Analysis On Machine Cell Recognition and Detaching From Neural SystemsDocumento9 páginasAnalysis On Machine Cell Recognition and Detaching From Neural SystemsIAEME PublicationAinda não há avaliações

- Lesson Plan - Substances and MixturesDocumento3 páginasLesson Plan - Substances and Mixturesapi-380830801Ainda não há avaliações

- Unit 1 Buying A New CarDocumento13 páginasUnit 1 Buying A New Carnorma0% (2)

- Terminal OutputDocumento2 páginasTerminal OutputJunmar AbaldeAinda não há avaliações

- ISDB-T Frequency TableDocumento2 páginasISDB-T Frequency Tabletryu40Ainda não há avaliações

- (VirtualBoxImages - Com) CentOS 6.0 I386 Gnome DesktopDocumento1 página(VirtualBoxImages - Com) CentOS 6.0 I386 Gnome DesktopUeltth N. CostaAinda não há avaliações

- MPL BasicsDocumento20 páginasMPL BasicsaunwaqasAinda não há avaliações

- Remote Sensing 1Documento5 páginasRemote Sensing 1Nazirul RahimAinda não há avaliações

- CS1101-DF-Unit 5 - Strings and IterationsDocumento7 páginasCS1101-DF-Unit 5 - Strings and IterationsJeremiah AdeyemiAinda não há avaliações

- BLD209 - What - S New in Cloud-Native CI - CD - Speed, Scale, SecurityDocumento15 páginasBLD209 - What - S New in Cloud-Native CI - CD - Speed, Scale, SecurityDzul FadliAinda não há avaliações

- Filipino, The Language That Is Not OneDocumento7 páginasFilipino, The Language That Is Not OneRyan Christian BalanquitAinda não há avaliações

- Extra Activity - Materials: Impress (V) Impression (N) Impressive (Adj)Documento2 páginasExtra Activity - Materials: Impress (V) Impression (N) Impressive (Adj)Boa BajabaAinda não há avaliações

- Lab Manual: @@name@@ College of Technology, BhopalDocumento19 páginasLab Manual: @@name@@ College of Technology, Bhopalthuraga saidhirajAinda não há avaliações

- Assignment: Bachelor'S of Arts Programme (B.A.G)Documento4 páginasAssignment: Bachelor'S of Arts Programme (B.A.G)Linthoi NganbiAinda não há avaliações

- MTAP Grade 2 Session 1Documento2 páginasMTAP Grade 2 Session 1Marites James - LomibaoAinda não há avaliações

- 21st Century Lit Q2Documento5 páginas21st Century Lit Q2lyra colladoAinda não há avaliações

- Gei 50261Documento24 páginasGei 50261Aquilino Sanchez FosadoAinda não há avaliações

- Gre VocabsDocumento11 páginasGre VocabsSaidur RahmanAinda não há avaliações

- Introduction To English PhoneticDocumento10 páginasIntroduction To English PhoneticPhuongTa0% (1)

- Principles of Academic Writing IDocumento9 páginasPrinciples of Academic Writing IGodwin ZengeniAinda não há avaliações

- Poem Analysis 21stDocumento1 páginaPoem Analysis 21stAshley SorianoAinda não há avaliações

- Endless OS JournalDocumento110 páginasEndless OS JournalAntonioAinda não há avaliações

- Curriculum Map TleDocumento2 páginasCurriculum Map TleReynalyn Mercado Pineda-CarabocAinda não há avaliações

- University of Cambridge International Examinations Cambridge International Primary Achievement TestDocumento12 páginasUniversity of Cambridge International Examinations Cambridge International Primary Achievement TestSusanne KrishnanAinda não há avaliações

- Guia Virtual 2 - Grado 6°1, 6°2, 6°3, Inglés, Zarith GómezDocumento5 páginasGuia Virtual 2 - Grado 6°1, 6°2, 6°3, Inglés, Zarith Gómezmariafernanda carreñoAinda não há avaliações

- Question Bank: Class: Tycm Chapter No. 01 Introduction To AWTDocumento9 páginasQuestion Bank: Class: Tycm Chapter No. 01 Introduction To AWT332 Prathamesh SonawaneAinda não há avaliações

- Transformation Assignment 5 Psyu 306 Summary Project Instructions and WorksheetDocumento4 páginasTransformation Assignment 5 Psyu 306 Summary Project Instructions and Worksheetapi-490946499Ainda não há avaliações

- The Spanish Creation of The Philippines: The Birth of A NationDocumento30 páginasThe Spanish Creation of The Philippines: The Birth of A NationTricia May Cagaoan100% (1)

- Ea C461 458Documento3 páginasEa C461 458Nhi TruongAinda não há avaliações