Escolar Documentos

Profissional Documentos

Cultura Documentos

Scaling Effects in MOS Devices

Enviado por

Vikram KumarDescrição original:

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Scaling Effects in MOS Devices

Enviado por

Vikram KumarDireitos autorais:

Formatos disponíveis

Scaling effects in MOS devices We will consider the effect of applying a unitless scale factor of to the geometric parameters

of a MOS transistor. In order to allow the technology to ``scale'', one constraint we can apply is to insist that the total power consumed per unit area remain constant. (This means that, as the density of circuitry in a technology increases, the amount of cooling required for the circuits will remain constant --- if this was allowed to increase, after some point, the circuits would melt!) If we scale the following parameters in the way indicated, the power consumed per unit area will remain constant:

We can see from the relations previously developed that the following parameters scale in the manner indicated:

The following parameters also scale as shown, but the effects are undesirable:

MOSFET models

As mentioned earlier, an enhancement mode MOSFET can be modeled as a simple switch, through which current can flow in either direction. A slightly more complex model could be to consider the device to act as a resistor on its output, and a capacitor at its input. More sophisticated models can be readily derived, but the two mentioned above are useful for logic and approximate timing simulations of the behavior of a MOS integrated circuit. A number of circuit simulation programs have been written which allow the simulation of MOS integrated circuits with a wide range of transistor models. Some of the more sophisticated models have many parameters which can be varied, and can produce quite accurate simulation results. Most of these circuit simulators have been derived from the SPICE circuit simulation program, developed at UCB. SPICE has 3 sophisticated models for MOS transistors, and is generally considered to be quite an accurate circuit simulator. We can derive the simplest (and least accurate) of the SPICE models from simple physics; this exercise is useful because it provides some ``rules of thumb'' for the design of VLSI devices. In particular, it allows us to see how devices ``scale''; that is, how important properties such as the switching speed of a transistor vary with the linear dimensions of the transistor. One of the most important parameters for a transistor is its ``switching time''. We might expect this to be related to the transit time, , for a charge carrier (an electron, for an N channel MOSFET or a hole, for a P channel MOSFET) to cross the channel region from the source to the drain region . If we consider a transistor as shown in Figure , the transit time, , is simply speed of the charge carrier. where v is the average

Figure: Under simple conditions, we can calculate the average speed, v, for a charge carrier. If no nuclei were present in the channel region, and there was no voltage applied between the source and the drain ( i.e., no applied electric field) across the channel, then the average velocity would be zero. If there was an electric field in the channel region, the charge carriers would accelerate with an

acceleration , where e is the charge of the charge carrier, E is the magnitude of the applied electric field, and m is the mass of the charge carrier. (The quantity e is equal in magnitude to the charge of an electron). For free charge carriers, the average speed would be , where t is the time for the charge carrier to travel across the channel region. In reality, however, the charge carriers will collide with the nuclei in the channel region quite frequently. This collision is inelastic, the charge carrier gives up some of its energy to the nucleus. We will assume that the collisions are totally inelastic, and that each collision brings the charge carrier to a stop. The electron, therefore, accelerates only in the interval between collisions with nuclei. There will be an ``average time between collisions'', , and the average speed of the charge carrier will be given by

The parameter

is called the ``mobility''; there is an ``electron mobility'', . For silicon,

, and a

corresponding ``hole mobility``,

and, . (Actually, there are two types of mobility; a ``bulk'' mobility and a ``surface'' mobility. For MOSFET's, the surface mobility is important, and corresponds to the values quoted. For bipolar transistors, the bulk mobility is important.) So, the characteristic time, , for the transistor is

Although this is not a rigorous derivation, there are two important things to note: 1. The characteristic time length. 2. is proportional to the square of the channel .

is inversely proportional to

These are ``scaling rules'' for MOS devices, and are believed to be approximately valid for device sizes (channel dimensions) down to about 0.5 microns.

We can also calculate, approximately, some of the important electrical properties of the MOS transistor; e.g., the current which can flow through the channel region, and the impedance of the channel. These will be functions of both the size of the channel region and of the voltages applied to the gate ( ) of the device. ), drain ( ) and source (

Figure: Referring to Figure boundary is simply voltage, and , the charge, Q, which will be available at the oxide/channel where C is the capacitance of the is the gate-to-source is the

capacitor formed between the gate and the substrate, is the threshold voltage. (The quantity

``effective'' voltage applied to the gate). For a parallel plate capacitor, where A = LW is the area of the gate over the channel of width W and length L, D is the distance between the gate and the substrate ( i.e., the oxide thickness) and is the permittivity of the material (for .) So,

The current flowing in the channel is

(Note that this analysis neglects some important effects; for example, it implicitly assumes that there is a uniform electric field in the entire channel region.) A more sophisticated analysis gives slightly different values for the current in the channel region:

in the linear (ohmic) region, and

in the saturation region. These expressions are often written in terms of the ``process transconductance parameter'', , where the capacitance per unit area of the oxide. The gate capacitance The quantity is a SPICE parameter for MOS transistors. We can now calculate the effective impedance of the channel region as: where is .

if the transistor is operated in the linear region, and

in the saturation region. The fact that the impedance, Z, for a MOS transistor is proportional to the ratio in both their linear and saturated regions means that we can use these transistors as resistors; the relative resistances scale with the device size. This is true for both P- and N- channel devices, as well as for both enhancement and depletion mode transistors. In fact, a ``permanently turned on'' transistor is often used as a resistor, for example as a ``pull-up resistor'' for a logic gate, to provide a current limit for the gate output. We can also calculate the time constant for a transistor to charge the gate of another identical transistor. This time is very important, since it will be related to the ``gate delay'' for a logic device.

assuming that the transistor providing the charge is operating in its saturation region. Although this result is not rigorously correct, it is worth noting that the delay time for a transistor to switch on a second transistor has a simple relationship to the transit time . Figure transistor current, shows a plot of the current in the channel region of a MOS , the current between the source and drain) against the potential for various values of the applied gate for a typical MOS transistor .

difference across the channel

Figure: Note that three different regions are distinguished; the ``cutoff'' region, in which the transistor effectively passes no current; the ``linear'' region, in which the behavior is ohmic, and the ``saturation'' region, in which the current is nearly constant. Effectively, then, we have modelled the current in the channel region of a MOS transistor (either enhancement mode or depletion mode, P- or N- channel) as

The quantity

is often written as , and is called the ``gain factor'' for a is proportional to . is not completely

MOS transistor. Note that

Actually, in the saturation region, the drain current,

independent of , partly because ``depletes'' charge carriers from the vicinity of the well as shown in Figure . This effect both shortens the effective channel length and adds more charge carriers to the channel region.

Figure: These effects, which increase the drain current are usually modelled empirically by the parameter , the ``channel length modulation factor'', giving the following expression for the saturation current

is typically quite small, term as well, to ensure that

. It is a Level 1 SPICE parameter. The in the linear region is continuous from the linear to the saturation region.

is often included with the expression for

One remaining parameter for MOS devices which can readily be derived using simple physical reasoning is , the threshold voltage .

We start by looking again at a schematic of the cross-section of an NMOS enhancement mode transistor, as in Figure (similar arguments apply for a PMOS transistor.)

Figure: Note that if no charge is applied to the gate, the source and drain regions are separated by reverse biased PN junctions, and no current can flow between the

source and drain of the transistor. (The ``off'' impedance is normally of the order of thousands of megohms.) When a positive charge is applied to the gate of the transistor, however, mobile charge carriers are attracted from the bulk of the P-doped substrate to the surface of the channel region immediately below the insulating oxide under the gate. These mobile charge carriers leave behind fixed (immobile) charges in the ``depletion'' region in the channel, as shown in Figure . The thickness, of the depletion region below the gate can be calculated as a function of , the electrostatic potential just inside the depletion layer at the oxide-semiconductor interface. In Ptype semiconductors, this depletion layer is made by ``pushing back'' mobile holes.

Figure: The number of holes, dQ, originally contained in a thin horizontal layer of thickness is

The change in surface potential

is

integrating,

where

is the constant of integration. Solving for

where

is the permittivity of silicon, q is the charge of a single charge carrier (|q| is the density of P-type ions in the

= e, the charge of an electron), and substrate.

The quantity of charge per unit area in the channel region due to the immobile ions which have been stripped of their charge carriers (in this case, ions which have been stripped of their mobile holes) is

The threshold is defined as , i.e., the induced surface potential is equal in magnitude to the original, unbiased surface potential; the density of mobile negative charge carriers (electrons) at the surface is equal to the density of holes in the original, unbiased substrate. In effect, the channel region has been ``induced'' to become as strongly N-doped as it was originally P-doped. In order to calculate the gate voltage required to attain threshold, we need to know the concentration of charge carriers N in the unbiased substrate. This is normally equal to the dopant concentration of the substrate. We can define the equilibrium (electrostatic) potential as inside a semiconductor

where or are the equilibrium concentrations of P or N type mobile charge carriers ( i.e. the dopant concentration) in the substrate, and is the equilibrium mobile charge concentration for pure (or ``intrinsic'') silicon, at room temperature. Note that the potential is a surface potential, possibly arising from the diffusion of charge carriers across a surface. This potential is, of course, present independent of the gate voltage by to allow conduction in the channel. then the is . Moreover, it must be ``overcome''

If the substrate is not biased by any ``substrate body bias'' immobile charge in the depletion region at threshold

If the substrate is biased by a voltage

between the source and body, the , and

surface potential required to produce inversion is

We can now calculate the gate voltage required to produce inversion, the threshold voltage . The threshold voltage consists of several components: , to change the surface potential and offset . is the capacitance per unit

1. A voltage

the immobile depletion layer charge

area of the gate oxide; 2. A voltage representing the difference in the work function between the gate material and the channel material silicon gate devices, . 3. Additional charge at the oxide-semiconductor interface due to impurities, etc. This is modelled as Therefore the threshold voltage is given by . . For

Since the last term in the previous expression is difficult to evaluate it is usual to express the threshold voltage as a function of the substrate bias voltage, and measure the unbiased threshold voltage:

where . The parameter is the zero bias threshold voltage and is called the ``body effect coefficient factor''. We have now derived the most important relationships used in the simplest of the SPICE models (Level 1) of the MOS transistor. The following table lists estimates of these parameters for the CMOS3DLM and CMOS4S processes available to us:

Circuit simulators include the capacitance between the various elements of the transistor as components of the models. SPICE calculates the nonlinear capacitance between the gate and channel region. SPICE uses a set of parasitic capacitances modeled as constant capacitors as shown in Figure , in which the parasitic capacitors are named as in the SPICE parameter list. Also shown are the capacitances between the source and body, and the drain and body. These are each considered as two separate nonlinear capacitors, a bottom capacitance and a sidewall capacitance, calculated from the perimeters of the source and drain areas.

Figure:

FULL FORM OF MOBILE RELATED WORDS 1G - First Generation 2.5G - Second and a half generation 2G - Second Generation 3G - Third Generation 3GPP - 3rd Generation Partnership Project 3GPP2 - 3rd Generation Partnership Project 4G - Fourth Generation AAA - Authentication Authorization, Account ACC - Analog Control Channel AMPS - Advanced Mobile Phone Service AUC - Authentication Center BC - Billing Center BCH - Broadcast Channel BER - Bit Error Rate BS - Base Station BSC - Base Station Controller BTS - Base Transceiver Station CBR - Constant Bit Rate CDG - CDMA Development Group CDMA - Code Division Multiple Access CDMA2000 - Code Division Multiple Access CDR - Call Detail Record CN - Core Network D/R - Distance to Reuse Ratio DAMPS - Digital Advance Mobile Phone Service DCC - Digital Color Code DTA - Data Transfer Adapter DTC - Digital Traffic Channel EDGE - Enhanced Data for Global Evolution EDI - Electronic Data Interchange EIR - Equipment Identity Register ESMR - Enhanced Specialized Mobile Radio ETACS - Extended TACS ETDMA - Extended Time Division Multiple Access FDD - Frequency Division Duplex FDM - Frequency Division Multiplexing FDMA - Frequency Division Multiple Access FM - Frequency Modulation FSK - Frequency Shift Keying FTMD - Full Track Music Download GGSN - Gateway GPRS Support Node GMSC - Gateway Mobile Switching Center GMSK - Gaussian Minimum Shift Keying GPRS - General Packet Radio Service GPS - Global Positioning System GSM - Global System for Mobile Communication GSN - GPRS Support Node HLR - Home Location Register IC - Interchange Carrier iDEN - Integrated Dispatch Enhanced Network

IMEI - International Mobile Equipment Identity IMSI - International Mobile Subscriber Identity ITU - International Telecommunication Union IVRS - Interactive Voice Response System IWF Inter Working Function LBS - Location-Based Services LMR - Land Mobile Radio MC - Message Center MC Multi Carrier Mode MCS - Mobile Cellular System ME - Mobile Equipment MIN - Mobile Identification Number MIRS - Motorola Integrated Radio system MSC - Mobile Station Class MSC - Mobile Switching Center MTS - Mobile Telephone Service NAMPS - Narrowband Advanced Mobile Phone Service NMT - Nordic Mobile Telephone NPDB - Number Portability Database NTACS - Narrowband Total Access Communication Service PAD - Packet Assembler And Disassembler PCM - Pulse Coded Modulation PCN - Personal Communications Network PCS - Personal Communication Services PDA - Personal Digital Assistant PDC - Personal Digital Cellular PDSN - Packet Data Switched Network PM - phase modulation PM - pulse modulation PN - Packet Number PN - pseudorandom noise PPDN - Public Packet Data Network PSTN - Public Switched Telephone Network PTT - Post Telephone and Telegraph PTT - Push to Talk QoS - Quality of Service RAN - Radio Access Network RNC - Radio Network Controller SCH - Synchronization Channel SDMA - Spatial Division Multiple Access SGSN - Serving GPRS Support Node SIM - Subscriber Identity Module SIS - Subscriber Identity Security SMS - Short Message Service SMSC - Short Message Service Center TACS - Total Access Communications System TCH - traffic channel TD-SCDMA - Time Division Synchronous Cod TDD - Time Division Duplex

TDMA - Time Division Multiple Access TFT - Thin Film Transistor TIA - Telecommunications Industry Association UE - User Equipment UMTS - Universal Mobile Telecommunication System UPR - User Performance Requirements USB - Universal Serial Bus VLR - Visitor Location Register VMS - Voice Mail System WCDMA - Wideband Code Division Multiple Access WLAN - Wireless Local Area Network

Você também pode gostar

- Mos Transistor Theory: Figure 1: Symbols of Various Types of TransistorsDocumento16 páginasMos Transistor Theory: Figure 1: Symbols of Various Types of TransistorsKirthi RkAinda não há avaliações

- Unit 1.2 VLSI NotesDocumento16 páginasUnit 1.2 VLSI NotesElston RyanAinda não há avaliações

- CH2Documento45 páginasCH2himanshukatyal7Ainda não há avaliações

- Complete Vlsi NotesDocumento160 páginasComplete Vlsi NotesTarun SinghalAinda não há avaliações

- What Is LatchupDocumento15 páginasWhat Is LatchupNagendra BoyellaAinda não há avaliações

- Chapter 3 Metal Oxide Semiconductor (MOS)Documento64 páginasChapter 3 Metal Oxide Semiconductor (MOS)Jay Chandra DharAinda não há avaliações

- Unit-I VLSI & CDDocumento39 páginasUnit-I VLSI & CD21EC17- JAYA PRASAD.PAinda não há avaliações

- Mini ProjectDocumento25 páginasMini Projectcharan524Ainda não há avaliações

- VLSI Design: Dr. K. Srinivasa RaoDocumento39 páginasVLSI Design: Dr. K. Srinivasa Raoshen shahAinda não há avaliações

- Question 1 and 4Documento5 páginasQuestion 1 and 4ShakikAinda não há avaliações

- Vlsi - Unit 1 NotesDocumento41 páginasVlsi - Unit 1 NotesmyavananAinda não há avaliações

- J3b PDFDocumento13 páginasJ3b PDFSrikrishna JanaAinda não há avaliações

- VLSI Unit 1 - MOSDocumento86 páginasVLSI Unit 1 - MOSskh_19870% (1)

- VLSI V Lab N-1Documento20 páginasVLSI V Lab N-1Dhiraj PrakashAinda não há avaliações

- Complete Vlsi NotesDocumento159 páginasComplete Vlsi NotesSUNIL MP75% (4)

- VLSIDocumento130 páginasVLSIMrinal Sinha100% (2)

- VLSI NotesDocumento130 páginasVLSI NotesOrcus DantalianAinda não há avaliações

- Ec8095-Vlsi Design-607796847-Ec 8095 NotesDocumento163 páginasEc8095-Vlsi Design-607796847-Ec 8095 Noteshmpudur1968Ainda não há avaliações

- LPVLSI III UnitDocumento19 páginasLPVLSI III UnitrakeshAinda não há avaliações

- Vlsi DesignDocumento31 páginasVlsi Designajas777BAinda não há avaliações

- Lecture 1Documento39 páginasLecture 1Nuniwal JyotiAinda não há avaliações

- Lpvlsi - V Unit Q & ADocumento17 páginasLpvlsi - V Unit Q & ANarasimhulu MaddireddyAinda não há avaliações

- Lecture NotesDocumento28 páginasLecture NotesEE22M306 Manvi ChaudharyAinda não há avaliações

- VLSI Unit 1 NotesDocumento41 páginasVLSI Unit 1 Notes210801059Ainda não há avaliações

- Chapter 4: Circuit CharacterizationDocumento9 páginasChapter 4: Circuit Characterizationbikash routAinda não há avaliações

- Linear: CMOS Voltage-to-Current ConverterDocumento4 páginasLinear: CMOS Voltage-to-Current ConverterdycsteiznAinda não há avaliações

- Bhwna Unit 5Documento9 páginasBhwna Unit 5Pradeep KumarAinda não há avaliações

- Chapter 3Documento46 páginasChapter 3Mayank KumarAinda não há avaliações

- VLSI Design TechniquesDocumento119 páginasVLSI Design Techniquesrajesh26julyAinda não há avaliações

- Design Issues in CMOS OscillatorsDocumento4 páginasDesign Issues in CMOS OscillatorsdhrubAinda não há avaliações

- MOS Field Effect Transistors (MOSFETs)Documento4 páginasMOS Field Effect Transistors (MOSFETs)enigmangoAinda não há avaliações

- DLC LAB - 08 - Student - ManualDocumento10 páginasDLC LAB - 08 - Student - ManualImtiaj SajinAinda não há avaliações

- Assignment 3Documento7 páginasAssignment 3Arnon PukhrambamAinda não há avaliações

- VLSI Design Lecture NotesDocumento117 páginasVLSI Design Lecture NotesRaji SharmiAinda não há avaliações

- Mosfet Differential AmplifierDocumento7 páginasMosfet Differential AmplifierSunil PandeyAinda não há avaliações

- EC6601 VLSI Design Model QBDocumento44 páginasEC6601 VLSI Design Model QBxperiaashAinda não há avaliações

- CMOS BasicDocumento11 páginasCMOS BasicSujit KumarAinda não há avaliações

- Hawkins CH 3Documento35 páginasHawkins CH 3Rinat EzerAinda não há avaliações

- Ring Osc Phase NoiseDocumento4 páginasRing Osc Phase NoiseHosein ZadeAinda não há avaliações

- Microelectronics Lab ReportsDocumento75 páginasMicroelectronics Lab ReportsAmArbir SinghAinda não há avaliações

- EI2301-IE - Unit 1 - Part A and Part B - With Answers PDFDocumento21 páginasEI2301-IE - Unit 1 - Part A and Part B - With Answers PDFsartpgitAinda não há avaliações

- From Wikipedia, The Free Encyclopedia: CMOS Inverter (NOT Logic Gate)Documento9 páginasFrom Wikipedia, The Free Encyclopedia: CMOS Inverter (NOT Logic Gate)bas_cbkAinda não há avaliações

- STEM: Science, Technology, Engineering and Maths Principles Teachers Pack V10No EverandSTEM: Science, Technology, Engineering and Maths Principles Teachers Pack V10Ainda não há avaliações

- MOS Integrated Circuit DesignNo EverandMOS Integrated Circuit DesignE. WolfendaleAinda não há avaliações

- Analysis and Design of Multicell DC/DC Converters Using Vectorized ModelsNo EverandAnalysis and Design of Multicell DC/DC Converters Using Vectorized ModelsAinda não há avaliações

- Power Electronics Applied to Industrial Systems and Transports, Volume 3: Switching Power SuppliesNo EverandPower Electronics Applied to Industrial Systems and Transports, Volume 3: Switching Power SuppliesAinda não há avaliações

- Customizing The ADFS Sign-In PagesDocumento4 páginasCustomizing The ADFS Sign-In Pagesmicu0% (1)

- PSC Girder MethodologyDocumento12 páginasPSC Girder MethodologySaurabh KumarAinda não há avaliações

- Exception Handling Notes For Vtu StudentsDocumento42 páginasException Handling Notes For Vtu StudentshelloAinda não há avaliações

- Key Features Boilermaker Proven, Legendary ReliabilityDocumento2 páginasKey Features Boilermaker Proven, Legendary ReliabilityManuel Cantoral CortazarAinda não há avaliações

- Steam Boiler Technology (2003)Documento218 páginasSteam Boiler Technology (2003)Majid Sattar100% (3)

- Dataproducts - LZR 1260 Laser Printer (1989)Documento6 páginasDataproducts - LZR 1260 Laser Printer (1989)Bobby ChippingAinda não há avaliações

- Method Statement of Pipeline WorksDocumento13 páginasMethod Statement of Pipeline Worksमनिसभेटुवाल86% (21)

- Below Which Not More Than 5 Percent of The Test Results Are Expected To Fall"Documento13 páginasBelow Which Not More Than 5 Percent of The Test Results Are Expected To Fall"shravan iitmAinda não há avaliações

- Advanced Techniques in Power System Protective Relaying PDFDocumento332 páginasAdvanced Techniques in Power System Protective Relaying PDFshashikant yadavAinda não há avaliações

- HHW 35 m6 GBDocumento6 páginasHHW 35 m6 GBSuper WhippedAinda não há avaliações

- Cover Letter Mechanical Engineering Nondestructive TestingDocumento1 páginaCover Letter Mechanical Engineering Nondestructive TestingGagandeep SinghAinda não há avaliações

- Home,: A Solace To Which A Journey Is Never Too Long..Documento25 páginasHome,: A Solace To Which A Journey Is Never Too Long..Duvonto RealtyAinda não há avaliações

- HP40 NBDocumento13 páginasHP40 NBTarun ChandraAinda não há avaliações

- Millikan Oil Drop ExperimentDocumento6 páginasMillikan Oil Drop ExperimentruleevanAinda não há avaliações

- Wood Magazine Issue #189Documento96 páginasWood Magazine Issue #189bangbang63100% (1)

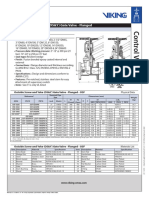

- Outside Screw and Yoke (OS&Y) Gate Valve - Flanged: Technical FeaturesDocumento2 páginasOutside Screw and Yoke (OS&Y) Gate Valve - Flanged: Technical FeaturesMark Louie GuintoAinda não há avaliações

- Light Object DSP Controller Setup GuideDocumento20 páginasLight Object DSP Controller Setup Guideblondu0070% (1)

- 462116-01 AA - 1510 Excel ESI Command Codes Addendum - 10 Feb 2009Documento103 páginas462116-01 AA - 1510 Excel ESI Command Codes Addendum - 10 Feb 2009quyenducqdc100% (1)

- A Study On The Design Optimization of An AUV by Using Computational Fluid Dynamic AnalysisDocumento7 páginasA Study On The Design Optimization of An AUV by Using Computational Fluid Dynamic AnalysisSalma SherbazAinda não há avaliações

- Hela Bojuna - Comparative StatementDocumento27 páginasHela Bojuna - Comparative StatementNadeeshani MunasingheAinda não há avaliações

- Acidizing TreatmentsDocumento93 páginasAcidizing TreatmentsPeña Lucia100% (2)

- Pile Cap Design 4pilesDocumento6 páginasPile Cap Design 4pilesabshawAinda não há avaliações

- Carpentry: Exploratory CourseDocumento25 páginasCarpentry: Exploratory CourseJohn Nelson Picones100% (3)

- Various Allowances Referred To 7th CPCDocumento73 páginasVarious Allowances Referred To 7th CPCGiri KumarAinda não há avaliações

- CFD Analysis of First Stage Nozzle Cooling Optimization in Gas TurbinesDocumento7 páginasCFD Analysis of First Stage Nozzle Cooling Optimization in Gas TurbinesMahmood ElnagarAinda não há avaliações

- Procurement Guideline For ATL SchoolsDocumento4 páginasProcurement Guideline For ATL SchoolsManKapAinda não há avaliações

- 101.S-4501 Steamer Cyclone Cleaning ProcedureDocumento6 páginas101.S-4501 Steamer Cyclone Cleaning ProcedureTRONGKIMAinda não há avaliações

- Liquid Gas Absorption ProcessDocumento89 páginasLiquid Gas Absorption ProcessMohd Masri A. RazakAinda não há avaliações

- Civil Engineering PDFDocumento3 páginasCivil Engineering PDFchetan c patilAinda não há avaliações

- Introduccion To PhysicsDocumento475 páginasIntroduccion To PhysicsLyvsAinda não há avaliações