Escolar Documentos

Profissional Documentos

Cultura Documentos

So Do Chan STM32 F103Rx 64pin

Enviado por

Trung PhamTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

So Do Chan STM32 F103Rx 64pin

Enviado por

Trung PhamDireitos autorais:

Formatos disponíveis

Pin 1 2 3 4 5 6 7 8 9 10 11 12 13 14

Pin name VBAT PC13-TAMPER PC14OSC32_IN(4) PC15OSC32_OUT(4) OSC_IN OSC_OUT NRST PC0 PC1 PC2 PC3 VSSA VDDA PA0-WKUP

Type S I/O I/O I/O I O I/O I/O I/O I/O I/O S S I/O

Main function (after reset) VBAT PC13(5) PC14(5) PC15(5) OSC_IN OSC_OUT NRST PC0 PC1 PC2 PC3 VSSA VDDA PA0

Default

Remap

TAMPER-RTC OSC32_IN OSC32_OUT

ADC123_IN10 ADC123_IN11 ADC123_IN12 ADC123_IN13

15

PA1

I/O

PA1

16

PA2

I/O

PA2

17

PA3

I/O

PA3

WKUP/USART2_CTS(6) ADC123_IN0 TIM2_CH1_ETR TIM5_CH1/TIM8_ETR USART2_RTS(6) ADC123_IN1/TIM5_CH2 TIM2_CH2(6) USART2_TX(6)/ TIM5_CH3/ADC123_IN2/ TIM2_CH3 (6) USART2_RX(6)/ TIM5_CH4/ADC123_IN3 TIM2_CH4(6)

18 19 20

VSS_4 VDD_4 PA4

S S I/O

VSS_4 VDD_4 PA4

21 22

PA5 PA6

I/O I/O

PA5 PA6

23

PA7

I/O

PA7

24 25 26

PC4 PC5 PB0

I/O I/O I/O

PC4 PC5 PB0

SPI1_NSS(6)/DAC_OUT1 USART2_CK(6) ADC12_IN4 SPI1_SCK(6) DAC_OUT2 ADC12_IN5 SPI1_MISO(6) TIM8_BKIN/ADC12_IN6 TIM3_CH1(6) SPI1_MOSI(6) TIM8_CH1N/ADC12_IN7 TIM3_CH2(6) ADC12_IN14 ADC12_IN15 ADC12_IN8/TIM3_CH3 TIM8_CH2N

TIM1_BKIN

TIM1_CH1N

TIM1_CH2N

1

27

PB1

I/O

PB1

ADC12_IN9 TIM3_CH4(6) TIM8_CH3N I2C2_SCL USART3_TX(6) I2C2_SDA USART3_RX(6)

TIM1_CH3N

28 29 30 31 32 33

PB2/BOOT1 PB10 PB11 VSS_1 VDD_1 PB12

I/O I/O I/O S S I/O

PB2/BOOT1 PB10 PB11 VSS_1 VDD_1 PB12

TIM2_CH3 TIM2_CH4

34

PB13

I/O

PB13

35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50

PB14 PB15 PC6 PC7 PC8 PC9 PA8 PA9 PA10 PA11 PA12 PA13/JTMSSWDIO VSS_2 VDD_2 PA14/JTCKSWCLK PA15/JTDI

I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O I/O S S I/O I/O

PB14 PB15 PC6 PC7 PC8 PC9 PA8 PA9 PA10 PA11 PA12 FT JTMSSWDIO VSS_2 VDD_2 JTCKSWCLK JTDI

SPI2_NSS/I2S2_WS/ I2C2_SMBAl/ USART3_CK(6)/ TIM1_BKIN(6) SPI2_SCK/I2S2_CK USART3_CTS(6)/ TIM1_CH1N SPI2_MISO/TIM1_CH2N USART3_RTS(6) SPI2_MOSI/I2S2_SD TIM1_CH3N(6) I2S2_MCK/ TIM8_CH1/SDIO_D6 I2S3_MCK/ TIM8_CH2/SDIO_D7 TIM8_CH3/SDIO_D0 IM8_CH4/SDIO_D1 USART1_CK/ TIM1_CH1(6)/MCO USART1_TX(6)/ TIM1_CH2(6) USART1_RX(6)/ TIM1_CH3(6) USART1_CTS/CANRX(6) TIM1_CH4(6)/USBDM USART1_RTS/USBDP/ CANTX(6)/TIM1_ETR(6) PA13

TIM3_CH1 TIM3_CH2 TIM3_CH3 TIM3_CH4

PA14 PA15/SPI3_NSS/ I2S3_WS UART4_TX/SDIO_D2 UART4_RX/SDIO_D3 TIM2_CH1_ET R SPI1_NSS USART3_TX USART3_RX

2

51 52

PC10 PC11

I/O I/O

PC10 PC11

53 54 55

PC12 PD2 PB3/JTDO

I/O I/O I/O

PC12 PD2 JTDO

56 57 58 59

PB4/JNTRST PB5 PB6 PB7

I/O I/O I/O I/O

JNTRST PB5 PB6 PB7

UART5_TX/SDIO_CK TIM3_ETR/UART5_RX SDIO_CMD PB3/TRACESWO JTDO SPI3_SCK/I2S3_CK/ PB4/SPI3_MISO I2C1_SMBAl/ SPI3_MOSI/I2S3_SD I2C1_SCL(6)/ TIM4_CH1(6) I2C1_SDA(6)/ FSMC_NADV/ TIM4_CH2(6) TIM4_CH3(6)/SDIO_D4 TIM4_CH4(6)/SDIO_D5

USART3_CK

TIM2_CH2 / SPI1_SCK TIM3_CH1 / SPI1_MISO TIM3_CH2 / SPI1_MOSI USART1_TX USART1_RX

60 61 62 63 64

BOOT0 PB8 PB9 VSS_3 VDD_3

I I/O I/O S S

BOOT0 PB8 PB9 VSS_3 VDD_3

I2C1_SCL/ CANRX I2C1_SDA / CANTX

1. I = input, O = output, S = supply, HiZ = high impedance. 2. FT = 5 V tolerant. 3. Function availability depends on the chosen device. 4. PC13, PC14 and PC15 are supplied through the power switch and since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 is restricted: only one I/O at a time can be used as an output, the speed has to be limited to 2 MHz with a maximum load of 30 pF and these I/Os must not be used as a current source (e.g. to drive an LED). 5. Main function after the first backup domain power-up. Later on, it depends on the contents of the Backup registers even after reset (because these registers are not reset by the main reset). For details on how to manage these IOs, refer to the Battery backup domain and BKP register description sections in the STM32F10xxx reference manual, available from the STMicroelectronics website: www.st.com. 6. This alternate function can be remapped by software to some other port pins (if available on the used package). For more details, refer to the Alternate function I/O and debug configuration section in the STM32F10xxx reference manual, available from the STMicroelectronics website: www.st.com. 7. For the LQFP64 package, the pins number 5 and 6 are configured as OSC_IN/OSC_OUT after reset, however the functionality of PD0 and PD1 can be remapped by software on these pins. For the LQFP100/BGA100 and LQFP144/BGA144 packages, PD0 and PD1 are available by default, so there is no need for remapping. For more details, refer to Alternate function I/O and debug configuration section in the STM32F10xxx reference manual. 8. For devices delivered in LQFP64 packages, the FSMC function is not available.

3

Você também pode gostar

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNo EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNota: 3.5 de 5 estrelas3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)No EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Nota: 4.5 de 5 estrelas4.5/5 (121)

- Never Split the Difference: Negotiating As If Your Life Depended On ItNo EverandNever Split the Difference: Negotiating As If Your Life Depended On ItNota: 4.5 de 5 estrelas4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingNo EverandThe Little Book of Hygge: Danish Secrets to Happy LivingNota: 3.5 de 5 estrelas3.5/5 (400)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNo EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNota: 4.5 de 5 estrelas4.5/5 (266)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNo EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNota: 4 de 5 estrelas4/5 (5795)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNo EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNota: 4 de 5 estrelas4/5 (1091)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyNo EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyNota: 3.5 de 5 estrelas3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNo EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNota: 4.5 de 5 estrelas4.5/5 (345)

- The Emperor of All Maladies: A Biography of CancerNo EverandThe Emperor of All Maladies: A Biography of CancerNota: 4.5 de 5 estrelas4.5/5 (271)

- Team of Rivals: The Political Genius of Abraham LincolnNo EverandTeam of Rivals: The Political Genius of Abraham LincolnNota: 4.5 de 5 estrelas4.5/5 (234)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNo EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNota: 4 de 5 estrelas4/5 (895)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNo EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNota: 4.5 de 5 estrelas4.5/5 (474)

- The Yellow House: A Memoir (2019 National Book Award Winner)No EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Nota: 4 de 5 estrelas4/5 (98)

- Simple EDM CircuitDocumento2 páginasSimple EDM Circuitkwayneolson608150% (2)

- The Unwinding: An Inner History of the New AmericaNo EverandThe Unwinding: An Inner History of the New AmericaNota: 4 de 5 estrelas4/5 (45)

- Mcintosh Laboratory: by Paul SeydorDocumento6 páginasMcintosh Laboratory: by Paul SeydorEdward KokAinda não há avaliações

- Intelligent Addressable Fire Alarm System: GeneralDocumento8 páginasIntelligent Addressable Fire Alarm System: GeneralAmr El-Deeb100% (1)

- Acoustics of Small RoomsDocumento44 páginasAcoustics of Small RoomseskilerdenAinda não há avaliações

- Manually Programming The Wouxun KG-UV6DDocumento17 páginasManually Programming The Wouxun KG-UV6DEric Vought100% (1)

- Communication Standards IEEE 802 - 3Documento3 páginasCommunication Standards IEEE 802 - 3Trung PhamAinda não há avaliações

- Problemas Parte I Comunicaciones DigitalesDocumento17 páginasProblemas Parte I Comunicaciones DigitalesNano GomeshAinda não há avaliações

- Bo So 2014Documento1 páginaBo So 2014Trung PhamAinda não há avaliações

- Command Table SSD1963Documento2 páginasCommand Table SSD1963Trung PhamAinda não há avaliações

- Pin STM32F103Vx: STT Pin Name Alternate Functions RemapDocumento3 páginasPin STM32F103Vx: STT Pin Name Alternate Functions RemapTrung PhamAinda não há avaliações

- AcronymsDocumento1 páginaAcronymsTrung PhamAinda não há avaliações

- Hitron-CGN2 Residential Cable ModemDocumento113 páginasHitron-CGN2 Residential Cable ModemMaxPowerLaserAinda não há avaliações

- Product Characteristics: Inductive SensorsDocumento2 páginasProduct Characteristics: Inductive SensorsWahana CiptaAinda não há avaliações

- 42CRC Color Registration ControlDocumento24 páginas42CRC Color Registration Controldiego lagunaAinda não há avaliações

- Micron 7Documento32 páginasMicron 7tsdcnAinda não há avaliações

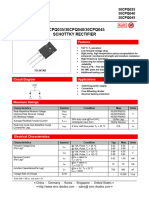

- 30CPQ035-45 N0612 Rev.aDocumento4 páginas30CPQ035-45 N0612 Rev.atakahashikeisuke505Ainda não há avaliações

- Codevision AVR Serial Parallel Parallel CodevisionDocumento8 páginasCodevision AVR Serial Parallel Parallel Codevisionmehrdad heydariAinda não há avaliações

- AHP4518R7v06: Antenna SpecificationsDocumento2 páginasAHP4518R7v06: Antenna SpecificationsRNNicoll100% (1)

- ICS501 RevQDocumento9 páginasICS501 RevQreteversiliaAinda não há avaliações

- Addresses of Cursor Position For 16x2 HD44780 LCDDocumento7 páginasAddresses of Cursor Position For 16x2 HD44780 LCDJayanta PaulAinda não há avaliações

- Flair SeriesDocumento2 páginasFlair SeriesSse ikolaha SubstationAinda não há avaliações

- Iversor EpeverDocumento32 páginasIversor Epeverjohn marcosAinda não há avaliações

- Corning® Infinicor® 62.5 Μm Optical Fibers Product InformationDocumento4 páginasCorning® Infinicor® 62.5 Μm Optical Fibers Product InformationparkplatinumAinda não há avaliações

- ME172Documento2 páginasME172Amine LakouismiAinda não há avaliações

- Rogowski PDFDocumento9 páginasRogowski PDFEmir JusićAinda não há avaliações

- CVM-C10: Technical FeaturesDocumento2 páginasCVM-C10: Technical FeaturesInstaller Kimonz1Ainda não há avaliações

- Pantum M6700 M6800 M7100 M7200 Series User Guide en V1 0 PDFDocumento148 páginasPantum M6700 M6800 M7100 M7200 Series User Guide en V1 0 PDFDan MoldovanAinda não há avaliações

- Reading Capacitor CodesDocumento2 páginasReading Capacitor Codesfurious143Ainda não há avaliações

- WEEK 5 Circuit Diagram and Layout of An AM and AM Receiver.pDocumento23 páginasWEEK 5 Circuit Diagram and Layout of An AM and AM Receiver.pJhoncarlo AliadoAinda não há avaliações

- Aplication Note For TOP SwitchDocumento9 páginasAplication Note For TOP SwitchSunil SonavaneAinda não há avaliações

- Comparison Frequency Modulation and Phase ModulationDocumento13 páginasComparison Frequency Modulation and Phase ModulationAMIT KUMAR SINGHAinda não há avaliações

- Comp Arch and Org - Lec 1Documento27 páginasComp Arch and Org - Lec 1abatesolomon17Ainda não há avaliações

- 2-Whole-Digital Data Processing in Radio AstronomyDocumento396 páginas2-Whole-Digital Data Processing in Radio AstronomyМарко Д. СтанковићAinda não há avaliações

- Motion Controlled Robotic Arm Using Flex SensorsDocumento5 páginasMotion Controlled Robotic Arm Using Flex SensorsNitin Somanathan0% (1)

- 3.8m C Band Circ. Pol RXTXDocumento6 páginas3.8m C Band Circ. Pol RXTXJoseph EdwardsAinda não há avaliações