Escolar Documentos

Profissional Documentos

Cultura Documentos

Organizacion Del Procesador

Enviado por

jjgl1989Descrição original:

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Organizacion Del Procesador

Enviado por

jjgl1989Direitos autorais:

Formatos disponíveis

ORGANIZACION DEL PROCESADOR La parte procesadora de un computador CPU se trata algunas veces como el canal de datos del CPU

porque el procesador formula los canales de trasferencia de datos entre los registros de la unidad. Los diferentes caminos son controlados supuestamente por medio de compuertas que abren los caminos necesarios y cierran otros. Una unidad procesadora puede disearse para satisfacer un conjunto de canales de datos para una aplicacin especfica. En una unidad procesadora bien organizada, los canales de datos se forman por medio de buses y otras lneas comunes. Las compuertas de control que formulan los canales de datos son esencialmente multiplexores y decodificadores cuyas lneas de seleccin especifican el camino requerido. El proceso de informacin se hace mediante una funcin digital comn cuyo canal de datos puede ser especificado por un conjunto de variables de seleccin comunes. Una unidad procesadora que tiene una organizacin bien estructurada puede usarse en una gran cantidad de operaciones. Si se construye dentro de un circuito integrado, se har disponible para muchos usuarios ya que para cada uno se puede tener una aplicacin diferente. Memoria "scratchpad" o memoria tapn Los registros de una unidad procesadora pueden ser metidos dentro de una unidad pequea de memoria. Cuando estos se incluyen en la unidad de proceso, la memoria pequea se llama memoria tapn o de borrado. El uso de una pequea memoria es una alternativa muy econmica para conectar los registros procesadores a travs del sistema de bus. La diferencia entre dos sistemas es la manera en la cual la informacin se selecciona para la trasferencia al ALU. En el sistema de bus, la trasferencia de informacin se selecciona por medio de los multiplexores que forman los buses. Por otra parte, un solo registro dentro de un grupo de registros organizados como una pequea memoria puede ser seleccionado por medio de una direccin de la unidad de memoria. Un registro de memoria puede funcionar justamente como cualquier otro registro procesador ya que su nica funcin es almacenar informacin binaria para ser procesada en el ALU. Una memoria tapn o de borrado debe distinguirse de la memoria principal del computador. En contraste con la memoria principal, la cual almacena instrucciones y datos, una pequea memoria de una unidad de proceso es meramente una alternativa para conectar un nmero de registros procesadores por medio de un camino de trasferencia comn. La informacin almacenada en una memoria tapn o de borrado debe venir normalmente de la memoria principal por medio de instrucciones en el programa.

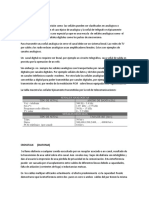

Considrese, por ejemplo, una unidad procesadora que emplea ocho registros de 16 bits cada uno. Los registros pueden incluirse dentro de una memoria pequea de ocho palabras de 16 bits cada una, o un RAM de 8 x 16. Las ocho palabras de memoria pueden designarse como RO hasta Rl, correspondiendo a las direcciones 0 hasta 7 y constituyen los registros para el procesador. Una unidad procesadora que usa una memoria tapn o de borrado se muestra en la Figura 9-2. Un registro fuente se selecciona de la memoria y se carga al registro A. Un segundo registro fuente se selecciona de la memoria y se carga al registro B. La seleccin se hace especificando las direcciones de palabra correspondientes y activando la entrada de lectura de la memoria. La informacin de A y B se manipula en el ALU y en el registro de desplazamiento. El resultado de la operacin se trasfiere a un registro de memoria especificando su direccin de palabra y activando el control de entrada de escritura en memoria. El multiplexor a la entrada de la memoria puede seleccionar datos de entrada de una fuente externa.

Registro acumulador Algunas unidades procesadoras separan un registro de otros y se le llama registro acumulador, abreviado AC o registro A. El nombre de este registro se deriva del proceso de adicin aritmtica que se encuentra en los computadores digitales. El proceso de sumar muchos nmeros se lleva a cabo almacenando inicialmente esos nmeros en otros registros procesadores o en la unidad de memoria del computador y borrando el acumulador a 0. Los nmeros se agregan al acumulador uno a uno en orden consecutivo. El primer nmero se agrega a 0 y la suma se trasfiere al acumulador. El segundo nmero se agrega a los contenidos del acumulador y la suma formada de nuevo remplaza su valor previo. Este proceso se contina hasta que todos los nmeros se agregan y se forma la suma total. As, el registro "acumula" la suma paso a paso haciendo sumas secuenciales entre un nmero nuevo y la suma acumulada previamente. El registro acumulador en una unidad de proceso es un registro mulnpropsito capaz de realizar no solamente la microoperacin de suma sino tambin otras microoperaciones de la misma forma. De hecho, las compuertas asociadas con un registro acumulador suministran todas las funciones digitales encontradas en un ALU. En algunos casos toda la unidad procesadora es justamente el registro acumulador y el ALU asociado. El registro en s puede funcionar como un registro de desplazamiento para suministrar las microoperaciones de desplazamiento. La entrada B suministra una fuente de informacin externa.

Esta informacin puede provenir de otros registros procesadores o directamente de la memoria principal del computador. El registro A suministra la otra fuente de informacin al ALU por el terminal A. El resultado de una operacin se trasfiere de nuevo al registro A y se remplaza su contenido previo. La salida del registro A puede ir a un destino externo o a los terminales de entrada de otros registros procesadores o unidad de memoria. UNIDAD LOGICA ARITMETICA Una unidad lgica aritmtica (ALU) es una funcin multioperacin digital de lgica combinacional. Esta puede realizar un conjunto de operaciones aritmticas bsicas y un conjunto de operaciones lgicas. El ALU tiene un numero de lineas de seleccin para seleccionar una operacin particular de la unidad. Las lineas de seleccin se decodifican dentro del ALU de manera que las k variables de seleccin pueden especificar hasta 2* operaciones diferentes. DISEO DEL CIRCUITO LOGICO Las microoperaciones lgicas manipulan los bits de los operandos separadamente y tratan cada bit como una variable binaria. La Tabla 2-6 lista 16 operaciones lgicas que pueden ser realizadas con dos variables binarias. Las 16 operaciones lgicas pueden ser generadas en un circuito y seleccionadas por medio de cuatro lneas de seleccin. Como todas las operaciones lgicas pueden obtenerse por medio de operaciones AND, OR y NOT (complemento), podra ser ms conveniente emplear un circuito lgico justamente con esas operaciones. Para tres operaciones se necesitan dos variables de seleccin. Pero dos lneas de seleccin pueden seleccionar entre cuatro operaciones lgicas, de manera que se escoge tambin la funcin ORexclusiva (XOR) para el circuito lgico que va a disearse en esta y en la siguiente seccin. El mtodo ms simple y directo de disear un circuito lgico se muestra en la Figura 9-11. El diagrama muestra una etapa tpica designada por l suscrito i. El circuito debe repetirse n veces para un circuito lgico de n bits. Las cuatro compuertas generan las cuatro operaciones lgicas OR, OR-exclusiva, AND y NOT. Las dos variables de seleccin en el multiplexor seleccionan una de las compuertas de la salida. La tabla de funcin lista la lgica de salida generada como una funcin de dos variables de seleccin. El circuito lgico puede ser combinado en el circuito aritmtico para producir una unidad lgica aritmtica. Las variables de seleccin Si y s0 pueden hacerse comunes a ambas secciones siempre y cuando se use una tercera variable de seleccin s2 para diferenciar entre los dos. Esta configuracin se ilustra en la Figura 9-12. Las salidas de los circuitos lgicos y aritmticos de

cada estado pasan por un multiplexor con la variable de seleccin s2 Cuando s2 = 0 se selecciona la salida aritmtica, pero cuando s2 = 1 se selecciona la salida lgica. Aunque los dos circuitos pueden combinarse de esta manera, sta no es la mejor forma de disear un ALU. Un ALU ms eficiente puede obtenerse si se investiga la posibilidad de generar operaciones lgicas de un circuito aritmtico ya disponible. Esto puede hacerse inhibiendo todos los arrastres de entrada de los circuitos del sumador completo del sumador en paralelo. Considrese la funcin de Boole que genera la suma de salida de un circuito sumador completo: F, = X C,

Organizacin de un procesador. Unidad lgica / aritmtica. Diseo de un circuito lgico y aritmtico. Diseo del alu. Registro de condicin. Diseo de un acumulador comn.

2.1. Organizacin del procesador. Unidad aritmtico-lgica. 2.2. Diseo de Procesadores: Diseo de un circuito aritmtico. Diseo del circuito lgico. Diseo de una unidad lgica aritmtica. Registro de condicin. Diseo de un registro de desplazamiento. 2.3. Unidad procesadora . Diseo del acumulador.

Você também pode gostar

- Ejercicios de Programacic3b3n Con s7 300 1c2aa Parte PDFDocumento7 páginasEjercicios de Programacic3b3n Con s7 300 1c2aa Parte PDFefrenvoAinda não há avaliações

- Sistemas de control integrados en bienes de equipo y maquinaria industrial y elaboración de la documentación técnica. FMEE0208No EverandSistemas de control integrados en bienes de equipo y maquinaria industrial y elaboración de la documentación técnica. FMEE0208Ainda não há avaliações

- Prácticas de redes de datos e industrialesNo EverandPrácticas de redes de datos e industrialesNota: 4 de 5 estrelas4/5 (5)

- UJNIDAD 5 Simulación de Sistemas ContinuosDocumento8 páginasUJNIDAD 5 Simulación de Sistemas Continuosjjgl19890% (1)

- UF0852 - Instalación y actualización de sistemas operativosNo EverandUF0852 - Instalación y actualización de sistemas operativosNota: 5 de 5 estrelas5/5 (1)

- Unidad Aritmetica LogicaDocumento12 páginasUnidad Aritmetica LogicaDillis Yordan Gomez LarezAinda não há avaliações

- Examen de Ingenieria ElectricaDocumento2 páginasExamen de Ingenieria Electricaangel eduardo prado solorzanoAinda não há avaliações

- Tarea 5Documento5 páginasTarea 5juan mezaAinda não há avaliações

- Tarea 5Documento11 páginasTarea 5juan mezaAinda não há avaliações

- Organización Del ProcesadorDocumento4 páginasOrganización Del ProcesadorJosé YañezAinda não há avaliações

- Alu - 8085Documento18 páginasAlu - 8085Walter David CunalataAinda não há avaliações

- Primer Corte 2da Asignacion 12-08Documento3 páginasPrimer Corte 2da Asignacion 12-08GabrielaAinda não há avaliações

- Escenario 5Documento12 páginasEscenario 5Iquito mosi conleAinda não há avaliações

- Bus de DatosDocumento2 páginasBus de DatosRodrigo AriasAinda não há avaliações

- Diseño de Microcomputadores1Documento5 páginasDiseño de Microcomputadores1Carlos VenegasAinda não há avaliações

- Como Realiza Las Operaciones Aritmeticas El MicroprocesadorDocumento9 páginasComo Realiza Las Operaciones Aritmeticas El MicroprocesadorComandante Gomez YeahAinda não há avaliações

- Diseño Lógico de ProcesadoresDocumento9 páginasDiseño Lógico de ProcesadoresMayerlin A Diaz GAinda não há avaliações

- El HardwareDocumento54 páginasEl HardwareALEX DANTE MENDOZA JARAAinda não há avaliações

- 04 Nivel de La Microprogramacion Parte III Datos IDocumento38 páginas04 Nivel de La Microprogramacion Parte III Datos IGersson MoralesAinda não há avaliações

- Diseño Del Sistema Del MicrocomputadorDocumento4 páginasDiseño Del Sistema Del MicrocomputadorOmerAinda não há avaliações

- Prác.1y2 SoporteDocumento27 páginasPrác.1y2 SoporteJerykozAinda não há avaliações

- Procesador Didactico PDFDocumento50 páginasProcesador Didactico PDFJuan Diego Pachon PovedaAinda não há avaliações

- Unidad II. Estructura y Funcionamiento de La CPUDocumento35 páginasUnidad II. Estructura y Funcionamiento de La CPUSergioJairMeridaCortes80% (5)

- Controlador Lógico Programable PLCDocumento8 páginasControlador Lógico Programable PLCRodolfo RuaroAinda não há avaliações

- Resumen ArquitecturaDocumento5 páginasResumen ArquitecturaJavier PucciniAinda não há avaliações

- II. Microprocesadores de 8 y 16 BitsDocumento7 páginasII. Microprocesadores de 8 y 16 BitsPhaan PevensieAinda não há avaliações

- Trabajo 1 MicroprocesadorDocumento13 páginasTrabajo 1 MicroprocesadorvanessajpAinda não há avaliações

- Unidad Ii Estructura y Funcionamiento de La CpuDocumento18 páginasUnidad Ii Estructura y Funcionamiento de La CpuYURIDIA ANAYA RIOSAinda não há avaliações

- Segunda Parcial Arquitectura de Computadoras.Documento23 páginasSegunda Parcial Arquitectura de Computadoras.alexisllamasAinda não há avaliações

- Curso PLC Sena PDFDocumento5 páginasCurso PLC Sena PDFAndres UrbanoAinda não há avaliações

- Sistemas DigitalesDocumento70 páginasSistemas DigitalesFede CX5AAAinda não há avaliações

- Arquitectura Del Microprocesador z80Documento9 páginasArquitectura Del Microprocesador z80Nilyan BertiAinda não há avaliações

- Unidad Lógico Aritmética (ALU) : UNEFA - CaracasDocumento25 páginasUnidad Lógico Aritmética (ALU) : UNEFA - CaracasMAVAREZAinda não há avaliações

- 10 Fundamentos de La Logica Digital SecuencialDocumento12 páginas10 Fundamentos de La Logica Digital SecuencialJavier Angulo OsorioAinda não há avaliações

- 5.2 Diseño Utilizando Memorias.Documento7 páginas5.2 Diseño Utilizando Memorias.SukiCafeAinda não há avaliações

- Sistemas I Informe 1Documento21 páginasSistemas I Informe 1alexAinda não há avaliações

- Fundamentos de Diseno Logico y de Computadoras Charles R Kime y M Morris Min Parte2Documento304 páginasFundamentos de Diseno Logico y de Computadoras Charles R Kime y M Morris Min Parte2luz sAinda não há avaliações

- Componentes Del MicroprocesadorDocumento25 páginasComponentes Del Microprocesadorel_cuate1883% (6)

- Tarea1 Investigacion MicrocontroladoresDocumento19 páginasTarea1 Investigacion MicrocontroladoresGIOVANIAinda não há avaliações

- Partes MicroprocesadorDocumento14 páginasPartes MicroprocesadorJuan Sebastian Parrado RomeroAinda não há avaliações

- Un Microprocesador de 8 Bits Z80Documento85 páginasUn Microprocesador de 8 Bits Z80Sebastián SandovalAinda não há avaliações

- Arquitectura ParalelaDocumento17 páginasArquitectura ParalelamamamboAinda não há avaliações

- Actividad T1-04-Serie de Ejercicios 2Documento10 páginasActividad T1-04-Serie de Ejercicios 2Hecsali SalinasAinda não há avaliações

- Actividad 5Documento9 páginasActividad 5juan mezaAinda não há avaliações

- Bus de Datos Del Microprocesador 8086Documento4 páginasBus de Datos Del Microprocesador 8086Ernesto Ezequiel Lamby DelgadoAinda não há avaliações

- Apunte Unidad #2 2022 - FUNCIONAMIENTO DE LA CPU PDFDocumento32 páginasApunte Unidad #2 2022 - FUNCIONAMIENTO DE LA CPU PDFDiego ArgañarazAinda não há avaliações

- Act2 Unidad Logica Aritmetica (Alu)Documento15 páginasAct2 Unidad Logica Aritmetica (Alu)Hector QuiñonesAinda não há avaliações

- Resumen MicroprocesadoresDocumento6 páginasResumen MicroprocesadoresAndres ChagllaAinda não há avaliações

- El Microprocesador 8085Documento11 páginasEl Microprocesador 8085neptuno97Ainda não há avaliações

- Microprocesadores 1Documento16 páginasMicroprocesadores 1Luis Alfonso CabreraAinda não há avaliações

- Estructura y Funcionamiento de Una ALUDocumento17 páginasEstructura y Funcionamiento de Una ALUhernández hernández richard leonardoAinda não há avaliações

- TP 5Documento10 páginasTP 5Nacho NotaAinda não há avaliações

- Capi 5 TemaaDocumento17 páginasCapi 5 TemaaNacho RomanelloAinda não há avaliações

- Exp No 8 El Microprocesador Z80Documento18 páginasExp No 8 El Microprocesador Z80Richy Ploneda100% (1)

- Introducción A Los MicroprocesadoresDocumento10 páginasIntroducción A Los MicroprocesadoresBibiano Cortés ToledoAinda não há avaliações

- El UP 8086 Fue de Los Primeros en Utilizar Un Bus de 16Documento4 páginasEl UP 8086 Fue de Los Primeros en Utilizar Un Bus de 16Annie UniAinda não há avaliações

- Lecciòn 1 Estructura y Caracterìsticas de Un PICDocumento8 páginasLecciòn 1 Estructura y Caracterìsticas de Un PICErick 'CzAinda não há avaliações

- Elementos Del ProcesadorDocumento29 páginasElementos Del ProcesadorEmanuel QuimAinda não há avaliações

- Aplicaciones de Las MemoriasDocumento6 páginasAplicaciones de Las MemoriasFederico Camargo HerreraAinda não há avaliações

- Bloques FuncionalesDocumento17 páginasBloques FuncionalesOscar RmzAinda não há avaliações

- Partes Que Integran Los MicroprocesadoresDocumento10 páginasPartes Que Integran Los MicroprocesadoresJennifer McclainAinda não há avaliações

- Arquitectura ConvencionalDocumento13 páginasArquitectura ConvencionalAnyi GAinda não há avaliações

- Cómo Utilizar UltrasurfDocumento21 páginasCómo Utilizar Ultrasurfjjgl1989Ainda não há avaliações

- Estimación de Los Parámetros de La PoblaciónDocumento9 páginasEstimación de Los Parámetros de La Poblaciónjjgl1989Ainda não há avaliações

- IUTIRLA Sede Punto FijoDocumento28 páginasIUTIRLA Sede Punto Fijojjgl1989Ainda não há avaliações

- Parámetros No Ideales Del Sistema SatelitalDocumento1 páginaParámetros No Ideales Del Sistema Satelitaljjgl1989Ainda não há avaliações

- Interface 8255Documento14 páginasInterface 8255Yosbel Jemi Reyes RojasAinda não há avaliações

- Reductor de 12 A 5 VoltiosDocumento4 páginasReductor de 12 A 5 VoltiosAlejandro ZavalaAinda não há avaliações

- Practica 03 - Amplificadores de Una EtapaDocumento10 páginasPractica 03 - Amplificadores de Una EtapaVictor QuevedoAinda não há avaliações

- ProcesadoresDocumento6 páginasProcesadoresYuseth De Jesus Jimenez VillanuevaAinda não há avaliações

- Guia de Primer Grado 2Documento6 páginasGuia de Primer Grado 2Eunice CaballeroAinda não há avaliações

- DiafoniaDocumento3 páginasDiafoniakuinonyAinda não há avaliações

- Amplificadores Tema 2Documento23 páginasAmplificadores Tema 2Chelito De Jesus Villalobos GtzAinda não há avaliações

- Ejercicios Elementos AuxiliaresDocumento10 páginasEjercicios Elementos AuxiliaresblubluAinda não há avaliações

- Características de La Onda en Líneas de Transmisión FinitasDocumento2 páginasCaracterísticas de La Onda en Líneas de Transmisión FinitasIgnacio Moises LopezAinda não há avaliações

- Compuertas Básicas - Introduccià NDocumento2 páginasCompuertas Básicas - Introduccià NDiana MeraAinda não há avaliações

- Resumen Recursos TecnológicosDocumento7 páginasResumen Recursos TecnológicosGRACE CERDAAinda não há avaliações

- Proyecto Elevador MecatronicaDocumento14 páginasProyecto Elevador MecatronicaAdolfo Alvarez BlancoAinda não há avaliações

- 07 Señales Moduladas en ÁnguloDocumento42 páginas07 Señales Moduladas en ÁnguloOrlando JuarezAinda não há avaliações

- LTE - Balance Enlace DL LTEDocumento13 páginasLTE - Balance Enlace DL LTECarlos Gonzales100% (1)

- Componentes de Equipo de Computo DDocumento33 páginasComponentes de Equipo de Computo Djucaba76Ainda não há avaliações

- Detnov Abril 2016Documento44 páginasDetnov Abril 2016kmAinda não há avaliações

- Preparatorio 3.2Documento9 páginasPreparatorio 3.2Carlos JumboAinda não há avaliações

- Examen Final Corriente Alterna.: Nombre: Jovani Patricio Navarro Ramos RUT: 19.895.802-6 Carrera: Tecnico IndustriaDocumento12 páginasExamen Final Corriente Alterna.: Nombre: Jovani Patricio Navarro Ramos RUT: 19.895.802-6 Carrera: Tecnico IndustriaGonzalo DíazAinda não há avaliações

- Informe - Rectificador Trifasico de Onda CompletaDocumento6 páginasInforme - Rectificador Trifasico de Onda CompletaJulian Andres Echeverry100% (1)

- Practica 4Documento3 páginasPractica 4EMANUEL RUIZ HERNANDEZAinda não há avaliações

- Innovacion Tecnologica It5: - Aplicaciones de Electrónica AnalógicaDocumento13 páginasInnovacion Tecnologica It5: - Aplicaciones de Electrónica Analógicadbarrio2011Ainda não há avaliações

- Manual Tristation 15-04-10Documento75 páginasManual Tristation 15-04-10JuCeMoOr100% (1)

- Antena YagiDocumento8 páginasAntena YagiMiguel ZambranoAinda não há avaliações

- Practicas FullDocumento31 páginasPracticas FullLEMNI100% (1)

- Teoria TCMDocumento4 páginasTeoria TCMAdriana BucioAinda não há avaliações

- Clase Transistores ACDocumento9 páginasClase Transistores ACJ Pablo Torres CAinda não há avaliações

- Experimento 6Documento9 páginasExperimento 6STEPHANY HANCCO CHANCOAinda não há avaliações

- Dispositivo de Entrada y SalidaDocumento1 páginaDispositivo de Entrada y Salidayerly100% (1)