Escolar Documentos

Profissional Documentos

Cultura Documentos

Lab3 - Eng - 10simulation of A Matrix-Vector Multiplication PDF

Enviado por

hieuhuech1Descrição original:

Título original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Lab3 - Eng - 10simulation of A Matrix-Vector Multiplication PDF

Enviado por

hieuhuech1Direitos autorais:

Formatos disponíveis

Halmstad University IDE

Hardware Design using VHDL Lab 3 10-06-29

Hardware Design using VHDL Lab 3 1. Introduction This laboratory consists of two parts. In part 1, the use of structural VHDL. The design is simulated and implemented in a gate array. Part 2 consists of simulation of a matrix-vector multiplication. 2. Preparation Read Sjoholm-Lindh chapter 6 and 7. Read the lab-PM. Perform design work for problem 1-2. 3. Details Problem 1: Structural VHDL x a) Design a component FA (Full Adder), and compile. x + y + c_in = 2 c_out + s c_out b) Design a 3-bits full adder using the component FA, using structural VHDL. c) Simulate. Write the test bench carefully! d) Synthesize. Note the maximum delay time and area consumption (number of LUT:s). e) Implement. DIP1-3 to X = <x2, x1, x0> and DIP6-8 to Y = <y2, y1, y0>. c_in to DIP4. The result c_out and S = <s2, s1, s0> is detected in decimal form on the 7-segment displays. FA s c_in y

Halmstad University IDE

Hardware Design using VHDL Lab 3 10-06-29

Problem 2: Matrix-vector multiplication in a systolic array Introduction A systolic array is a type of parallel architecture in which data is "pumped" through a series of processors linked by a field. The word "systolic" is the same as those used in medicine to enter the (systolic) blood pressure. A global clock set the pace, i.e. when data is shifted from one processor to the next. All processors perform the same operation. In this problem a matrix-vector multiplication on a systolic array is going to be studied by simulation in VHDL. Preparation before lab-moment Make a solution "on paper" before you come to the lab. Matrix-vector multiplication Mathematically, we can take out the matrix-vector multiplication as: Ck = Aki x Bi Here, A is a n x n matrix, B and C are vectors of dimension n x 1. If for example we shall multiply a 3 x 3 matrix with a 3 x 1 vector, we can give this as: A11 A12 A13 b1 c1 c2 = A21 A22 A23 x b2 c3 A31 A32 A33 b3

Halmstad University IDE

Hardware Design using VHDL Lab 3 10-06-29

Systolic array The systolic arrays in this case consists of five processor elements. Each element performs the same operation(s). These are:

1) Input from the left is copied out to the right (Right_out <= Left_in). 2) Output to the left is calculated as: Left_out <= (Left_in * Top_in) + Right_in. The B-vector is pumped in from the left in the sequence: b1, 0, b2, 0, b3. The A-matrix is pumped into from above as the sequence shown in the figure. Utdatavektorn C comes out to left under the sequence c1, 0, c2, 0, c3. Let the output of each processor be delayed eg 7 ns after clock flank. Clock the model with 10 ns periodtid (100 MHz).

Halmstad University IDE

Hardware Design using VHDL Lab 3 10-06-29

VHDL modeling A processor element is described in figure below. All signals, except for clock and reset, must be of type integer. Top_in Left_in Right_out Left_out Right_in Reset Clock

The complete array of five PE, is shown in the figure on the previous page. Execution This lab is based on knowledges and methods that was trained in the previous labs. It may therefore be good to look at lab1 Dice. Start the symbol editor and create symbol PE as shown in Fig. All signals, except clock and reset, must be of type integer. When the PE component is created, it shall be tested. Start the schematic editor and place one PE. Create the I/O ports required and then save the schematic with the name onepe. Create a symbol of this schematic, and then quit the schematic editor. Create the test bench and edit it.Add the appropriate VHDL code that tests the component PE Compile and run the simulator. Check that the component PE works as it was thought. Correct any errors. When the PE works the full matrix-vector multiplier is going to be created. Create a new schematic with an appropriate name (i.e. systolic) with five PE connected as shown in fig. Create a new test bench to test the whole array and simulate this. Test the component with the following values: 3 1 0 4 2 6 5 1 26 3 x 2 = 14 7 3 33

Accounting Plot the schematic and wave form.

Halmstad University IDE

a11 a21 a31 t=7: t=6: t=5: t=4: t=3: t=2: t=1: b3,0,b2,0,b1 c1,0,c2,0,c3 t=7: t=6: t=5: t=4: t=3: t=2: b3,0,b2,0 0 0 a13 0 0 0 b1 PE t=7: t=6: t=5: t=4: t=3: b3,0,b2 0 0 a13 0 0 0 PE t=7: t=6: t=5: t=4: b3,0 0 0 a13 0 b2 PE t=7: t=6: t=5: b3 0 0 a13 0 PE PE b1*a11+ 0 b2*a12 0 a23 b3 PE b1*a11+ b2*a12+ b3*a13 =c1 0 0 PE a21*b1+ PE b1*a11 0 a23 0 b2 PE a21*b1 a33 0 b2 PE 0 a31*b1 a22*b2 0 a33 0 a22 0 b1 PE 0 0 a23 0 a12 0 PE 0 PE 0 a33 0 a22 0 b1 PE 0 a23 0 a12 0 PE a33 0 a22 0 a11 0 a23 0 a12 0 0 a33 0 a22 0 a11 0 a12 a22 a32 0 0 a13 0 0 0 0 PE a13 b1 a11 b1 a23 x b2 = a21 b1 a33 b3 a31 b1 0 a23 0 a12 0 0 0 PE a33 0 a22 0 a11 0 0 PE

+ a12 b2 + a13 b3 + a22 b2 + a23 b3 + a32 b2 + a33 b3 0 a32 0 a21 0 0 0 PE

Hardware Design using VHDL Lab 3 10-06-29 Appendix 1.

0 0 a31 0 0 0 0 PE 0

0 a32 0 a21 0 0 PE 0 0 a32 0 a21 0 PE 0 a32 0 a21 PE 0 0 a32 0 b1 PE

0 0 a31 0 0 0 PE 0 0 a31 0 0 PE 0 0 a31 0 PE 0 0 a31 PE 0 0 0 0

t=7: t=6:

0 0

0 a32 0 PE

0 0 PE b1 0

Halmstad University IDE

Hardware Design using VHDL Lab 3 10-06-29

Library

IEEE;

Use IEEE.std_logic_1164.all; Use IEEE.std_logic_unsigned.all; constant numb_addr: integer := 7; type pe_data is array (0 to numb_addr - 1, 0 to 4) of integer; constant pe_matrix: pe_data:=pe_data ( 6=> (0, 0, 7, 0, 0), 5=> (0, 3, 0, 6, 0), 4=> (5, 0, 2, 0, 0), 3=> (0, 4, 0, 1, 0), 2=> (0, 0, 3, 0, 0), 1=> (0, 0, 0, 0, 0), 0=> (0, 0, 0, 0, 0); type vec is array (0 to numb_addr-1) of integer; constant pe_vec: vec := vec (1, 0, 2, 0, 3, 0, 0);

ex. integer

col1<=pe_matrix(0, 3)

Você também pode gostar

- MIPS Processor ImplementationDocumento92 páginasMIPS Processor ImplementationlilisoloAinda não há avaliações

- How To Improve Your IQ With Brain Exerci PDFDocumento2 páginasHow To Improve Your IQ With Brain Exerci PDFJunior Enchaki100% (1)

- Ideal Diode Circuit Analysis StepsDocumento4 páginasIdeal Diode Circuit Analysis StepsPhaniendra KundetiAinda não há avaliações

- Hodgkin Huxley Neuron ModelDocumento9 páginasHodgkin Huxley Neuron ModelSomnath SandeepAinda não há avaliações

- Electric Field Vs Magnetic FieldDocumento10 páginasElectric Field Vs Magnetic FieldCrisbern GozunAinda não há avaliações

- Differences Between Mup and MucDocumento2 páginasDifferences Between Mup and Mucrihatrivedi_069Ainda não há avaliações

- Microwind 3.5 BRDocumento2 páginasMicrowind 3.5 BRammayi9845_930467904Ainda não há avaliações

- Meh ENG2 PDFDocumento37 páginasMeh ENG2 PDFInkeAinda não há avaliações

- From Polymers To Plastics Problems and Solved ExercisesDocumento93 páginasFrom Polymers To Plastics Problems and Solved ExercisesGonzalo MazaAinda não há avaliações

- Linear Inverted Pendulum - Workbook (Student) PDFDocumento23 páginasLinear Inverted Pendulum - Workbook (Student) PDFDeepthi Priya BejjamAinda não há avaliações

- Lab 591 - B Analysis and Design of CSDocumento2 páginasLab 591 - B Analysis and Design of CSDevine WriterAinda não há avaliações

- Numerical MethodsDocumento2 páginasNumerical MethodsJeoff Libo-on0% (1)

- Meh ENGDocumento20 páginasMeh ENGTama ReadAinda não há avaliações

- (Please The Slide Show To Begin) : StartDocumento32 páginas(Please The Slide Show To Begin) : StartSatish RaoAinda não há avaliações

- MC0082 - Theory of Computer ScienceDocumento235 páginasMC0082 - Theory of Computer SciencePurushottam KumarAinda não há avaliações

- Matlab Lab ReportDocumento7 páginasMatlab Lab Reportসামস উজ জামান সন্ধিAinda não há avaliações

- Introduction To LTspiceDocumento24 páginasIntroduction To LTspiceSanjay GuptaAinda não há avaliações

- hw3 2014 r0 KeyDocumento10 páginashw3 2014 r0 KeyOlivia ChoiAinda não há avaliações

- Sample SOPDocumento2 páginasSample SOPnikAinda não há avaliações

- 08 - Forward and Backward ChainingDocumento12 páginas08 - Forward and Backward ChainingShanthi GanesanAinda não há avaliações

- StudyGuide001 2015 4 B STA1502Documento116 páginasStudyGuide001 2015 4 B STA1502JasonAinda não há avaliações

- Introduction To Algorithms: Dynamic ProgrammingDocumento25 páginasIntroduction To Algorithms: Dynamic ProgrammingjaydipAinda não há avaliações

- ECE5710 Notes01Documento32 páginasECE5710 Notes01FREDERICKAinda não há avaliações

- Course Notes For Unit 4 of The Udacity Course ST101 Introduction To StatisticsDocumento25 páginasCourse Notes For Unit 4 of The Udacity Course ST101 Introduction To StatisticsIain McCullochAinda não há avaliações

- Fiber Optics NotesDocumento12 páginasFiber Optics NotesMonika HansdaAinda não há avaliações

- 555 Timer IC and OpampDocumento36 páginas555 Timer IC and OpampDummyAinda não há avaliações

- Chapter 1 - Medical PHYSICS - 2019 PDFDocumento20 páginasChapter 1 - Medical PHYSICS - 2019 PDFعبدالعزيز محمد عابد العابدAinda não há avaliações

- Memory AidsDocumento7 páginasMemory Aidsdwnldr2000Ainda não há avaliações

- COMP90038 Practice Exam Paper (2) : Dit?usp SharingDocumento15 páginasCOMP90038 Practice Exam Paper (2) : Dit?usp SharingAnupa AlexAinda não há avaliações

- TI Tech Questions and Answers PDFDocumento26 páginasTI Tech Questions and Answers PDFSANJEEV KUMARAinda não há avaliações

- Chapter 1 - Analog Integrated Circuit Design by John ChomaDocumento87 páginasChapter 1 - Analog Integrated Circuit Design by John ChomaAriana Ribeiro LameirinhasAinda não há avaliações

- Pericyclic ReactionsDocumento53 páginasPericyclic ReactionsSF ShagorAinda não há avaliações

- Diode Circuit AnalysisDocumento20 páginasDiode Circuit AnalysisAsmaa WajeahAinda não há avaliações

- Biomedical Engg Project SolveDocumento10 páginasBiomedical Engg Project Solveasif0% (2)

- Advanced SensorsDocumento23 páginasAdvanced SensorsAzharuddin MansooriAinda não há avaliações

- Z-Transform: - Using Fourier Transform For LTI System Analysis IsDocumento36 páginasZ-Transform: - Using Fourier Transform For LTI System Analysis IsMarcelo Luis Ruiz RodriguezAinda não há avaliações

- Bernoulli's Theorem ProofDocumento2 páginasBernoulli's Theorem ProofSourav Das50% (4)

- Due: Monday September 17: Homework 2 - Solution ECE 445 Biomedical Instrumentation, Fall 2012Documento3 páginasDue: Monday September 17: Homework 2 - Solution ECE 445 Biomedical Instrumentation, Fall 2012amastasia salsaAinda não há avaliações

- Assumed Modes MethodsDocumento17 páginasAssumed Modes MethodsYsharath Chandramouli100% (1)

- Senior Design I DocumentationDocumento138 páginasSenior Design I DocumentationAnonymous 0Jy86kAinda não há avaliações

- Storyboard StickmanDocumento5 páginasStoryboard StickmannvndrptrAinda não há avaliações

- Group19 SemaphoreDocumento68 páginasGroup19 Semaphoreksenthil77Ainda não há avaliações

- RC Charging CircuitDocumento43 páginasRC Charging Circuitleonard1971Ainda não há avaliações

- Electrical MachinesDocumento245 páginasElectrical MachinesMELVIN67% (3)

- Data Structure QuestionsDocumento176 páginasData Structure QuestionsEzhil Vendhan0% (1)

- 156 - Engineering - Drawing - EE-155 - Lab - Manual Final-2Documento24 páginas156 - Engineering - Drawing - EE-155 - Lab - Manual Final-2Hamza AkhtarAinda não há avaliações

- Chapter One: DebremarkosuniversityDocumento110 páginasChapter One: DebremarkosuniversityFaizAinda não há avaliações

- PDFDocumento38 páginasPDFshady boyAinda não há avaliações

- Single Slit Diffraction ExperimentDocumento30 páginasSingle Slit Diffraction ExperimentRajneilAinda não há avaliações

- Brain Structure and FunctionDocumento37 páginasBrain Structure and FunctionVijay Shanthi100% (1)

- ML Lab ObservationDocumento44 páginasML Lab Observationjaswanthch16100% (1)

- A Monostable MultivibratorDocumento7 páginasA Monostable Multivibratorammayi9845_930467904Ainda não há avaliações

- Ulta Stepup DC To DC Conveter With Reduced Switch StressDocumento21 páginasUlta Stepup DC To DC Conveter With Reduced Switch StressDRISHYAAinda não há avaliações

- Lab Manual - EEE 402 - Exp01 July2014Documento7 páginasLab Manual - EEE 402 - Exp01 July2014AhammadSifatAinda não há avaliações

- Chapter 1b DeMoivres TheoremDocumento16 páginasChapter 1b DeMoivres Theoremsofia combateAinda não há avaliações

- Maximum-Subarray Problem, Matrix Multiplication and Strassen's AlgorithmDocumento18 páginasMaximum-Subarray Problem, Matrix Multiplication and Strassen's AlgorithmPaksmilerAinda não há avaliações

- BrainGizer BookDocumento102 páginasBrainGizer BookRania NabilAinda não há avaliações

- KEY LAB DFT: I D F T (10 Points)Documento8 páginasKEY LAB DFT: I D F T (10 Points)mrithyunjaysivAinda não há avaliações

- Lab 07Documento10 páginasLab 07api-241454978Ainda não há avaliações

- CSE Lab Manual Final 2019-20 P-IDocumento42 páginasCSE Lab Manual Final 2019-20 P-IJerry boyAinda não há avaliações

- Real-Time Interface Dspace DSDocumento12 páginasReal-Time Interface Dspace DShieuhuech1Ainda não há avaliações

- Advantest r6441 DMM User ManualDocumento263 páginasAdvantest r6441 DMM User Manualhieuhuech1Ainda não há avaliações

- 2SP0115T Control IGBT ManualDocumento21 páginas2SP0115T Control IGBT Manualhieuhuech1Ainda não há avaliações

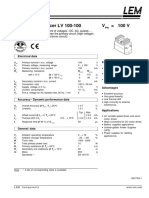

- Lem Voltage 100-500Documento2 páginasLem Voltage 100-500hieuhuech1Ainda não há avaliações

- Tektronix A6303 070390504Documento34 páginasTektronix A6303 070390504hieuhuech1Ainda não há avaliações

- TDS7000 SeriesDocumento254 páginasTDS7000 Serieshieuhuech1Ainda não há avaliações

- Sanwa pc500Documento42 páginasSanwa pc500hieuhuech1Ainda não há avaliações

- Design of A Microcontroller-Based Circuit For Software ProtectionDocumento6 páginasDesign of A Microcontroller-Based Circuit For Software Protectionhieuhuech1Ainda não há avaliações

- Simulation Study On Speed Control of Permanent Magnet Direct-Driven System For Mining ScraperDocumento11 páginasSimulation Study On Speed Control of Permanent Magnet Direct-Driven System For Mining Scraperhieuhuech1Ainda não há avaliações

- Msp-Exp430G2 Launchpad Workshop: - Meet The Launchpad - Lab 1: Blink Launchpad LedsDocumento16 páginasMsp-Exp430G2 Launchpad Workshop: - Meet The Launchpad - Lab 1: Blink Launchpad Ledshieuhuech1Ainda não há avaliações

- Fod8316 108263Documento30 páginasFod8316 108263hieuhuech1Ainda não há avaliações

- Stator Flux and Speed - HADocumento6 páginasStator Flux and Speed - HAhieuhuech1Ainda não há avaliações

- Sensorless Foc of PMSM Chu YDocumento42 páginasSensorless Foc of PMSM Chu Yhieuhuech1Ainda não há avaliações

- Nonlinear Model of Permanent-Magnet Synchronous MotorsDocumento8 páginasNonlinear Model of Permanent-Magnet Synchronous Motorshieuhuech1Ainda não há avaliações

- Ansys Chu y Chicago Modeling and Simulation of Brushless DC Motor Drive SystemDocumento25 páginasAnsys Chu y Chicago Modeling and Simulation of Brushless DC Motor Drive Systemhieuhuech1Ainda não há avaliações

- Speed Control Design of A PMSM Based On Functional Model Predictive ApproachDocumento15 páginasSpeed Control Design of A PMSM Based On Functional Model Predictive Approachhieuhuech1Ainda não há avaliações

- RiSC PipeDocumento9 páginasRiSC PipeAir Oddy Air OddyAinda não há avaliações

- UG130 ArchOverview TILE GXDocumento58 páginasUG130 ArchOverview TILE GXchrismorleyAinda não há avaliações

- Microprocessor 80286Documento4 páginasMicroprocessor 80286xorxorxorAinda não há avaliações

- Ktu s2 Mtech Cse SyllabusDocumento32 páginasKtu s2 Mtech Cse SyllabussamushabuAinda não há avaliações

- MCS 22 em 2023 24 MPDocumento15 páginasMCS 22 em 2023 24 MPwg1xachrr8Ainda não há avaliações

- Unit Ii - Embedded Processor and Computing PlatformDocumento118 páginasUnit Ii - Embedded Processor and Computing PlatformkalimuthukumarAinda não há avaliações

- Control System LabDocumento78 páginasControl System LabkittuAinda não há avaliações

- VV - III B.Tech II SemR16 RegularSupplementary Examinations April 2019Documento59 páginasVV - III B.Tech II SemR16 RegularSupplementary Examinations April 2019kowshik voodaAinda não há avaliações

- Microprocessor System (3 + 1)Documento15 páginasMicroprocessor System (3 + 1)noumanAinda não há avaliações

- Corelink Sse200 Subsystem For Embedded Technical Reference Manual 101104 0200 00 enDocumento187 páginasCorelink Sse200 Subsystem For Embedded Technical Reference Manual 101104 0200 00 enStudent of VIT 20MVD0047Ainda não há avaliações

- Zero Address InstructionsDocumento3 páginasZero Address InstructionsSalman MuhammadAinda não há avaliações

- 8085 ALP Five ALP To Count Even or and Odd Data ByteDocumento5 páginas8085 ALP Five ALP To Count Even or and Odd Data Bytejeffrinsamuel2006Ainda não há avaliações

- TVL CSS12 - q2 - w4 - Maintaining and Repairing Computer Systems and Networks Part 3 - v3Documento19 páginasTVL CSS12 - q2 - w4 - Maintaining and Repairing Computer Systems and Networks Part 3 - v3EVELYN GRACE TADEOAinda não há avaliações

- TI C5510 Assembly ProgrammingDocumento21 páginasTI C5510 Assembly ProgrammingWinsweptAinda não há avaliações

- Function (FC) and Function Block (FB) Similarities/Differences in Siemens PLC-S7 ProgrammingDocumento2 páginasFunction (FC) and Function Block (FB) Similarities/Differences in Siemens PLC-S7 Programminganacer55Ainda não há avaliações

- Assignment 2Documento2 páginasAssignment 2omer khanAinda não há avaliações

- Unit-6: Pipeline & Vector ProcessingDocumento41 páginasUnit-6: Pipeline & Vector ProcessingThabo NdasheAinda não há avaliações

- GP Rating Online Test - Quiz, Trivia & QuestionsDocumento8 páginasGP Rating Online Test - Quiz, Trivia & Questionssherief2023samsAinda não há avaliações

- M.E. (Comp. Scien. & Engg.) June 2013Documento44 páginasM.E. (Comp. Scien. & Engg.) June 2013barakAinda não há avaliações

- Softwired ControllerDocumento4 páginasSoftwired ControllerShreya SinghAinda não há avaliações

- Am 3517Documento221 páginasAm 3517mudit9_mAinda não há avaliações

- RDB 5453 PDFDocumento1 páginaRDB 5453 PDFhasan raisAinda não há avaliações

- Unit - I: Basic Structure of A Computer System Computer SystemDocumento25 páginasUnit - I: Basic Structure of A Computer System Computer Systempuli sivaAinda não há avaliações

- Rebus 3Documento2 páginasRebus 3andrei madaAinda não há avaliações

- Assignment: Bangladesh University of Engineering and TechnologyDocumento3 páginasAssignment: Bangladesh University of Engineering and TechnologyAli WaqasAinda não há avaliações

- IBM and Novell: The SLES 10 Success StoryDocumento9 páginasIBM and Novell: The SLES 10 Success StoryJayaram KalluriAinda não há avaliações

- (NXP) .1-Day Hands-On Arm TrainingDocumento208 páginas(NXP) .1-Day Hands-On Arm TrainingNataliya Rytova100% (2)

- Best Deals 2012Documento18 páginasBest Deals 2012mshopowAinda não há avaliações

- Clover Health PatentDocumento20 páginasClover Health PatentCharles GrossAinda não há avaliações

- Neogeo Programmer GuideDocumento220 páginasNeogeo Programmer GuidesudoAinda não há avaliações