Escolar Documentos

Profissional Documentos

Cultura Documentos

LN 09 Sequential Logic Modules

Enviado por

Srilekha VallabhaneniTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

LN 09 Sequential Logic Modules

Enviado por

Srilekha VallabhaneniDireitos autorais:

Formatos disponíveis

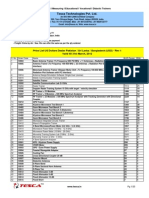

Chapter 9: Sequential Logic Modules

Chapter 9: Sequential Logic Modules

Prof. Ming-Bo Lin

Department of Electronic Engineering National Taiwan University of Science and Technology

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-1

Chapter 9: Sequential Logic Modules

Syllabus

Objectives Fundamentals of sequential logic modules Flip-flops Memory elements Shift registers Counters Sequence generators Timing generators

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-2

Chapter 9: Sequential Logic Modules

Objectives

After completing this chapter, you will be able to: Describe how to model asynchronous and synchronous D-type flip-flops Describe how to model registers (data register, register file, and synchronous RAM) Describe how to model shift registers Describe how to model counters (ripple/synchronous counters and modulo r counters) Describe how to model sequence generators Describe how to model timing generators

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley 9-3

Chapter 9: Sequential Logic Modules

Syllabus

Objectives Fundamentals of sequential logic modules Flip-flops Memory elements Shift registers Counters Sequence generators Timing generators

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-4

Chapter 9: Sequential Logic Modules

Basic Sequential Logic Modules

Synchronizer Finite state machine Sequence detector Data register Shift register CRC generator Register file Counters (binary, BCD, Johnson) Timing generator Clock generator Pulse generator

9-5

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

Chapter 9: Sequential Logic Modules

Options for Modeling Sequential Logic

Behavioral statement Task with delay or event control Sequential UDP Instantiated library register cell Instantiated modules

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-6

Chapter 9: Sequential Logic Modules

Syllabus

Objectives Fundamentals of sequential logic modules Flip-flops Memory elements Shift registers Counters Sequence generators Timing generators

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-7

Chapter 9: Sequential Logic Modules

Asynchronous Reset D-Type Flip-Flops

// asynchronous reset D-type flip-flop module DFF_async_reset (clk, reset_n, d, q); output reg q; always @(posedge clk or negedge reset_n) if (!reset_n) q <= 0; else q <= d;

Q: How would you model a D-type latch?

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley 9-8

Chapter 9: Sequential Logic Modules

Synchronous Reset D-Type Flip-Flops

// synchronous reset D-type flip-flop module DFF_sync_reset (clk, reset, d, q); output reg q; always @(posedge clk) if (reset) q <= 0; else q <= d;

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-9

Chapter 9: Sequential Logic Modules

Syllabus

Objectives Fundamentals of sequential logic modules Flip-flops Memory elements Shift registers Counters Sequence generators Timing generators

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-10

Chapter 9: Sequential Logic Modules

Types of Memory Elements

Data registers Register files Synchronous RAMs

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-11

Chapter 9: Sequential Logic Modules

Registers

Registers (or data registers) A flip-flop

Area: 10 to 20x of an SRAM cell

In Xilinx FPGAs

Flip-flops Distributed memory Block memory

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-12

Chapter 9: Sequential Logic Modules

Data Registers

// an n-bit data register module register(clk, din, qout); parameter N = 4; // number of bits input [N-1:0] din; output reg [N-1:0] qout; always @(posedge clk) qout <= din;

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley 9-13

Chapter 9: Sequential Logic Modules

Data Registers

// an n-bit data register with asynchronous reset module register_reset (clk, reset_n, din, qout); parameter N = 4; // number of bits input [N-1:0] din; output reg [N-1:0] qout; always @(posedge clk or negedge reset_n) if (!reset_n) qout <= {N{1'b0}}; else qout <= din;

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-14

Chapter 9: Sequential Logic Modules

Data Registers

// an N-bit data register with synchronous load and // asynchronous reset parameter N = 4; // number of bits input clk, load, reset_n; input [N-1:0] din; output reg [N-1:0] qout; always @(posedge clk or negedge reset_n) if (!reset_n) qout <= {N{1'b0}}; else if (load) qout <= din;

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-15

Chapter 9: Sequential Logic Modules

A Register File

// an N-word register file with one-write and two-read ports parameter M = 4; // number of address bits parameter N = 16; // number of words, N = 2**M parameter W = 8; // number of bits in a word input clk, wr_enable; input [W-1:0] din; output [W-1:0] douta, doutb; input [M-1:0] rd_addra, rd_addrb, wr_addr; reg [W-1:0] reg_file [N-1:0]; assign douta = reg_file[rd_addra], doutb = reg_file[rd_addrb]; always @(posedge clk) Try to synthesize it and see if (wr_enable) reg_file[wr_addr] <= din; what happens!!

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-16

Chapter 9: Sequential Logic Modules

An Synchronous RAM

// a synchronous RAM module example parameter N = 16; // number of words parameter A = 4; // number of address bits parameter W = 4; // number of wordsize in bits input [A-1:0] addr; input [W-1:0] din; input cs, wr, clk; // chip select, read-write control, and clock signals output reg [W-1:0] dout; reg [W-1:0] ram [N-1:0]; // declare an N * W memory array always @(posedge clk) if (cs) if (wr) ram[addr] <= din; else dout <= ram[addr];

Try to synthesize it and see what happens!!

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-17

Chapter 9: Sequential Logic Modules

Syllabus

Objectives Fundamentals of sequential logic modules Flip-flops Memory elements Shift registers Counters Sequence generators Timing generators

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-18

Chapter 9: Sequential Logic Modules

Shift Registers

Shift registers Parallel/serial format conversion

SISO (serial in serial out) SIPO (serial in parallel out) PISO (parallel in serial out) PIPO (parallel in parallel out)

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-19

Chapter 9: Sequential Logic Modules

Shift Registers

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-20

Chapter 9: Sequential Logic Modules

Shift Registers

// a shift register module example module shift_register(clk, reset_n, din, qout); Parameter N = 4; // number of bits . output reg [N-1:0] qout; always @(posedge clk or negedge reset_n) if (!reset_n) qout <= {N{1'b0}}; else qout <= {din, qout[N-1:1]};

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-21

Chapter 9: Sequential Logic Modules

A Shift Register with Parallel Load

// a shift register with parallel load module example module shift_register_parallel_load (clk, load, reset_n, din, sin, qout); parameter N = 8; // number of bits . input [N-1:0] din; output reg [N-1:0] qout; always @(posedge clk or negedge reset_n) if (!reset_n) qout <= {N{1'b0}}; else if (load) qout <= din; else qout <= {sin, qout[N-1:1]};

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley 9-22

Chapter 9: Sequential Logic Modules

Universal Shift Registers

A universal shift register can carry out

SISO SIPO PISO PIPO

The register must have the following capabilities

Parallel load Serial in and serial out Shift left and shift right

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-23

Chapter 9: Sequential Logic Modules

Universal Shift Registers

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-24

Chapter 9: Sequential Logic Modules

Universal Shift Registers

// a universal shift register module module universal_shift_register (clk, reset_n, s1, s0, ); parameter N = 4; // define the default size always @(posedge clk or negedge reset_n) if (!reset_n) qout <= {N{1'b0}}; else case ({s1,s0}) 2'b00: ; // qout <= qout; // No change 2'b01: qout <= {lsi, qout[N-1:1]}; // Shift right 2'b10: qout <= {qout[N-2:0], rsi}; // Shift left 2'b11: qout <= din; // Parallel load endcase

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley 9-25

Chapter 9: Sequential Logic Modules

Syllabus

Objectives Fundamentals of sequential logic modules Flip-flops Memory elements Shift registers Counters Sequence generators Timing generators

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-26

Chapter 9: Sequential Logic Modules

Counters

Counter Types

Counters Timers

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-27

Chapter 9: Sequential Logic Modules

Types of Counters

Types of counters

Asynchronous Synchronous

Asynchronous (ripple) counters

Binary counter (up/down counters)

Synchronous counters

Binary counter (up/down counters) BCD counter (up/down counters) Gray counters (up/down counters)

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-28

Chapter 9: Sequential Logic Modules

Binary Ripple Counters

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-29

Chapter 9: Sequential Logic Modules

Binary Ripple Counters

// a 3-bit ripple counter module example module ripple_counter(clk, qout); output reg [2:0] qout; wire c0, c1; // the body of the 3-bit ripple counter assign c0 = qout[0], c1 = qout[1]; always @(negedge clk) Try to synthesize it and see what qout[0] <= ~qout[0]; happens!! always @(negedge c0) The output cannot be observed from qout[1] <= ~qout[1]; simulators due to lacking initial always @(negedge c1) values of qout. qout[2] <= ~qout[2];

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley 9-30

Chapter 9: Sequential Logic Modules

Binary Ripple Counters

// a 3-bit ripple counter with enable control module ripple_counter_enable(clk, enable, reset_n, qout); output reg [2:0] qout; wire c0, c1; assign c0 = qout[0], c1 = qout[1]; always @(posedge clk or negedge reset_n) if (!reset_n) qout[0] <= 1'b0; else if (enable) qout[0] <= ~qout[0]; always @(posedge c0 or negedge reset_n) if (!reset_n) qout[1] <= 1'b0; else if (enable) qout[1] <= ~qout[1]; always @(posedge c1 or negedge reset_n) if (!reset_n) qout[2] <= 1'b0; else if (enable) qout[2] <= ~qout[2];

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley 9-31

Chapter 9: Sequential Logic Modules

A Binary Ripple Counter

// an N-bit ripple counter using generate blocks parameter N = 4; // define the size of counter output reg [N-1:0] qout; genvar i; generate for (i = 0; i < N; i = i + 1) begin: ripple_counter if (i == 0) // specify LSB always @(negedge clk or negedge reset_n) if (!reset_n) qout[0] <= 1'b0; else qout[0] <= ~qout[0]; else // specify the rest bits always @(negedge qout[i-1]or negedge reset_n) if (!reset_n) qout[i] <= 1'b0; else qout[i] <= ~qout[i]; end endgenerate

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley 9-32

Chapter 9: Sequential Logic Modules

A Binary Counter Example

module binary_counter(clk, enable, reset, qout, cout); parameter N = 4; output reg [N-1:0] qout; output cout; // carry output always @(posedge clk) if (reset) qout <= {N{1b0}}; else if (enable) qout <= qout + 1; // generate carry output assign #2 cout = &qout; // Why #2 is required ?

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-33

Chapter 9: Sequential Logic Modules

Binary Up/Down Counters --- version 1

module binary_up_down_counter_reset (clk, enable, reset, upcnt, qout, cout, bout); parameter N = 4; output reg [N-1:0] qout; output cout, bout; // carry and borrow outputs always @(posedge clk) if (reset) qout <= {N{1'b0}}; else if (enable) begin if (upcnt) qout <= qout + 1; else qout <= qout - 1; end assign #2 cout = &qout; // Why #2 is required ? assign #2 bout = |qout;

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley 9-34

Chapter 9: Sequential Logic Modules

Binary Up/Down Counters --- version 2

module up_dn_bin_counter (clk, reset, eup, edn, qout, cout, bout); Parameter N = 4; output reg [N-1:0] qout; output cout, bout; always @(posedge clk) if (reset) qout <= {N{1'b0}}; // synchronous reset else if (eup) qout <= qout + 1; else if (edn) qout <= qout - 1; assign #1 cout = (&qout)& eup; // generate carry out assign #1 bout = (~|qout)& edn; // generate borrow out

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley 9-35

Chapter 9: Sequential Logic Modules

Binary Up/Down Counters --- version 2

// the cascade of two up/down counters module up_dn_bin_counter_cascaded(clk, reset,eup, ); parameter N = 4; output [2*N-1:0] qout; output cout, bout; wire cout1, bout1; up_dn_bin_counter #(4) up_dn_cnt1 (clk, reset,eup, edn, ); up_dn_bin_counter #(4) up_dn_cnt2 (clk, reset, );

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-36

Chapter 9: Sequential Logic Modules

A Modulo r Binary Counter

module modulo_r_counter(clk, enable, reset, qout, cout); parameter N = 4; parameter R= 10; // BCD counter output reg [N-1:0] qout; assign cout = (qout == R - 1); always @(posedge clk) if (reset) qout <= {N{1'b0}}; else begin if (enable) if (cout) qout <= 0; else qout <= qout + 1; end

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley 9-37

Chapter 9: Sequential Logic Modules

Syllabus

Objectives Fundamentals of sequential logic modules Flip-flops Memory elements Shift registers Counters Sequence generators Timing generators

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-38

Chapter 9: Sequential Logic Modules

Sequence Generators

We only focus on the following three circuits

PR (pseudo random)-sequence generator Ring counter Johnson counter

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-39

Chapter 9: Sequential Logic Modules

Primitive Polynomials

f ( x) = ai x i = a0 + a1 x + a2 x 2 + + an x n

i =0

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-40

Chapter 9: Sequential Logic Modules

Maximal Length Sequence Generators

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-41

Chapter 9: Sequential Logic Modules

A PR-Sequence Generator Example

A 4-bit example

primitive polynomial: 1 + x + x4

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-42

Chapter 9: Sequential Logic Modules

A PR-Sequence Generator Example

// an N-bit pr_sequence generator module --- in standard form module pr_sequence_generate (clk, qout); parameter N = 4; // define the default size parameter [N:0] tap = 5'b10011; output reg [N-1:0] qout = 4b0100; wire d; assign d = ^(tap[N-1:0] & qout[N-1:0]); always @(posedge clk) qout <= {d, qout[N-1:1]}; Q: Write an N-bit pr_sequence generator in modular form.

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley 9-43

Chapter 9: Sequential Logic Modules

A PR-Sequence Generator Example

// an N-bit pr_sequence generator module --- in standard form module pr_sequence_generate (clk, start, qout); parameter N = 4; // define the default size parameter [N:0] tap = 5'b10011; output reg [N-1:0] qout; wire d; assign d = ^(tap[N-1:0] & qout[N-1:0]); always @(posedge clk or posedge start) if (start) qout <= {1'b1, {N-1{1'b0}}}; else qout <= {d, qout[N-1:1]};

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley 9-44

Chapter 9: Sequential Logic Modules

Ring Counters

// a ring counter with initial value module ring_counter(clk, start, qout); parameter N = 4; output reg [0:N-1] qout; always @(posedge clk or posedge start) if (start) qout <= {1'b1,{N-1{1'b0}}}; else qout <= {qout[N-1], qout[0:N-2]};

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley 9-45

Chapter 9: Sequential Logic Modules

Johnson Counters

// Johnson counter with initial value module ring_counter(clk, start, qout); parameter N = 4; // define the default size output reg [0:N-1] qout; always @(posedge clk or posedge start) if (start) qout <= {N{1'b0}}; else qout <= {~qout[N-1], qout[0:N-2]};

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley 9-46

Chapter 9: Sequential Logic Modules

Syllabus

Objectives Fundamentals of sequential logic modules Flip-flops Memory elements Shift registers Counters Sequence generators Timing generators

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-47

Chapter 9: Sequential Logic Modules

Timing Generators

A timing generator Multiphase clock signals

Ring counter Binary counter with decoder

Digital monostable circuits

Retriggerable Nonretriggerable

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-48

Chapter 9: Sequential Logic Modules

Multiphase Clock Signals

Ways of generation

Ring counter approach Binary counter with decoder approach

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-49

Chapter 9: Sequential Logic Modules

Multiphase Clock Generators

Binary counter with decoder approach

n = 4 and m =2

clk

[1:0]

enable reset

[1:0]

[1:0]

D[1:0] R

Q[1:0]

[1:0] [1:0]

decode

D[1:0] EQ[3:0]

[3:0] [3:0]

qout[3:0]

bcnt_out_5[1:0]

qout[3:0]

bcnt_out[1:0]

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley

9-50

Chapter 9: Sequential Logic Modules

Multiphase Clock Generators

// a binary counter with decoder serve as a timing generator module binary_counter_timing_generator(clk, reset, enable, qout); parameter N = 8; // the number of phases parameter M = 3; // the bit number of binary counter output reg [N-1:0] qout; reg [M-1:0] bcnt_out; always @(posedge clk or posedge reset) if (reset) bcnt_out <= {M{1'b0}}; else if (enable) bcnt_out <= bcnt_out + 1; always @(bcnt_out) qout = {N-1{1'b0},1'b1} << bcnt_out;

Digital System Designs and Practices Using Verilog HDL and FPGAs @ 2008~2010, John Wiley 9-51

Você também pode gostar

- Chapter 9: Sequential Logic Modules: Prof. Soo-Ik ChaeDocumento51 páginasChapter 9: Sequential Logic Modules: Prof. Soo-Ik ChaeeceaitsrajampetAinda não há avaliações

- DigitalDocumento60 páginasDigitalawadhesh.kumarAinda não há avaliações

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemNo EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemAinda não há avaliações

- LN 06 Hierarchical ModelingDocumento37 páginasLN 06 Hierarchical ModelingChauHuynhAinda não há avaliações

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxNo EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxNota: 4 de 5 estrelas4/5 (1)

- Chapter 7: Advanced Modeling Techniques: Prof. Ming-Bo LinDocumento42 páginasChapter 7: Advanced Modeling Techniques: Prof. Ming-Bo Linvimal_raj205Ainda não há avaliações

- Foundation Course for Advanced Computer StudiesNo EverandFoundation Course for Advanced Computer StudiesAinda não há avaliações

- DDCA Ch4 VHDLDocumento35 páginasDDCA Ch4 VHDLYerhard Lalangui FernándezAinda não há avaliações

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Ainda não há avaliações

- VLSI Lab ManualDocumento83 páginasVLSI Lab ManualSri SandhiyaAinda não há avaliações

- Multicore DSP: From Algorithms to Real-time Implementation on the TMS320C66x SoCNo EverandMulticore DSP: From Algorithms to Real-time Implementation on the TMS320C66x SoCAinda não há avaliações

- VerilogDocumento34 páginasVerilogromeoalvzAinda não há avaliações

- Floating Point ALU Using VHDLDocumento32 páginasFloating Point ALU Using VHDLzooni shaikAinda não há avaliações

- Verilog HDL: A Guide To Digital Design DS TH I and SynthesisDocumento62 páginasVerilog HDL: A Guide To Digital Design DS TH I and SynthesisSharan ChaitanyaAinda não há avaliações

- Digital Design Using VerilogDocumento60 páginasDigital Design Using VerilogSriju RajanAinda não há avaliações

- LN 14 Arithmetic ModulesDocumento42 páginasLN 14 Arithmetic ModulesYermakov Vadim IvanovichAinda não há avaliações

- L5 - Combinational Logic Design With VerilogDocumento17 páginasL5 - Combinational Logic Design With VerilogYogen SharmaAinda não há avaliações

- Introduction To VerilogDocumento51 páginasIntroduction To Verilogsft007Ainda não há avaliações

- VLSI Lab Manual - 2022-1Documento54 páginasVLSI Lab Manual - 2022-1SuhailAinda não há avaliações

- DSD ReportDocumento14 páginasDSD Report22051774Ainda não há avaliações

- You Could Download File D - FF.VDocumento133 páginasYou Could Download File D - FF.VPradeep BabuAinda não há avaliações

- Ece5017 Digital-Design-with-fpga Eth 1.0 40 Ece5017Documento3 páginasEce5017 Digital-Design-with-fpga Eth 1.0 40 Ece5017Daniel MAinda não há avaliações

- Verilog HDL Introduction: TextbookDocumento41 páginasVerilog HDL Introduction: TextbookAbhishek RanjanAinda não há avaliações

- Chapter 07 NotesDocumento50 páginasChapter 07 NotesIvanah Tannica DesolocAinda não há avaliações

- VHDL Come Strumento Di Progettazione Per Circuiti Digitali VLSIDocumento23 páginasVHDL Come Strumento Di Progettazione Per Circuiti Digitali VLSIunibfeAinda não há avaliações

- Ds First LatestDocumento31 páginasDs First LatestZohaib KhanAinda não há avaliações

- Flip-Flops and Latches (MyHDL)Documento6 páginasFlip-Flops and Latches (MyHDL)VIJAYPUTRAAinda não há avaliações

- Verilog 1Documento15 páginasVerilog 1Christina josephine malathiAinda não há avaliações

- VerilogDocumento80 páginasVeriloggenx142Ainda não há avaliações

- Verilog Part1Documento77 páginasVerilog Part1Ravi VarmaAinda não há avaliações

- Verilog AssignDocumento8 páginasVerilog Assignafodcwdycgpena100% (1)

- Vlsi Unit 5 NotesDocumento21 páginasVlsi Unit 5 NotesRamana Sekar100% (1)

- EC 303 Chapter 2Documento48 páginasEC 303 Chapter 2PrevenaManiamAinda não há avaliações

- Exercises Lg1 Lg6Documento4 páginasExercises Lg1 Lg6Helga PravinAinda não há avaliações

- Chapter 2b: Modeling: Switch-LevelDocumento27 páginasChapter 2b: Modeling: Switch-LevelAshish PuraniAinda não há avaliações

- FPGA Design Flow & Experiment 1Documento5 páginasFPGA Design Flow & Experiment 1Faid MuzahidAinda não há avaliações

- Verilog Tutorial For BeginnersDocumento4 páginasVerilog Tutorial For BeginnersNovelyn RabinoAinda não há avaliações

- Physical Design Via Place-and-Route - RTL To GDSDocumento39 páginasPhysical Design Via Place-and-Route - RTL To GDSJoseph HuangAinda não há avaliações

- Design Examples-Digital System Designs and Practices Using Verilog HDL and FPGAsDocumento69 páginasDesign Examples-Digital System Designs and Practices Using Verilog HDL and FPGAsyamaha640Ainda não há avaliações

- Ec3561-Vlsi Design LabDocumento144 páginasEc3561-Vlsi Design LabperiyasamyAinda não há avaliações

- DDCAarm Ch4Documento40 páginasDDCAarm Ch4SebaAinda não há avaliações

- VHDL - Introduction: CP323L1: Advance Logic DesignDocumento20 páginasVHDL - Introduction: CP323L1: Advance Logic Designartnetw0rkAinda não há avaliações

- Simulation SeminarDocumento45 páginasSimulation SeminarKapasi TejasAinda não há avaliações

- Ecad and Vlsi Lab ManualDocumento125 páginasEcad and Vlsi Lab Manualsameer7mohammadAinda não há avaliações

- Verilog Basic ExperimentsDocumento62 páginasVerilog Basic ExperimentsGaurav Soni0% (1)

- VTU - Practical Book - Part A - 04-08-2009Documento42 páginasVTU - Practical Book - Part A - 04-08-2009Kishore KumarAinda não há avaliações

- 09 AcceleratorsDocumento47 páginas09 AcceleratorsgkudrethayaAinda não há avaliações

- L12: Reconfigurable Logic ArchitecturesDocumento30 páginasL12: Reconfigurable Logic ArchitecturesGaurav UpadhyayAinda não há avaliações

- Lec3Documento38 páginasLec3love639111Ainda não há avaliações

- CountersDocumento13 páginasCountersmuthubeAinda não há avaliações

- VHDL Coding Tips and Tricks - VHDL Code For BCD To 7-Segment Display ConverterDocumento4 páginasVHDL Coding Tips and Tricks - VHDL Code For BCD To 7-Segment Display Convertermrithyunjaysiv100% (1)

- Combinational Logic Design With Verilog: Reading AssignmentDocumento15 páginasCombinational Logic Design With Verilog: Reading AssignmentRaghvendra SinghAinda não há avaliações

- Birla Institute of Technology & Science, Pilani Lab Sheet - 1Documento7 páginasBirla Institute of Technology & Science, Pilani Lab Sheet - 1SATYAVRAT SHARMAAinda não há avaliações

- Verilog-HDL: Verilog HDL: A Guide To Digital Design and Synthesis, Palnitkar, SamirDocumento23 páginasVerilog-HDL: Verilog HDL: A Guide To Digital Design and Synthesis, Palnitkar, SamirAnonymous jxm0WNS7QaAinda não há avaliações

- Vlsi Manual 2013-2014Documento36 páginasVlsi Manual 2013-2014hr_suresh_kAinda não há avaliações

- Cong Nghe FPGADocumento29 páginasCong Nghe FPGANguyen Tuong ThanhAinda não há avaliações

- 8085 Simulator IDE Main FeaturesDocumento9 páginas8085 Simulator IDE Main FeaturesMohamed YousufAinda não há avaliações

- FALLSEM2022-23 BECE102L TH VL2022230102875 Reference Material I 17-09-2022 Shift Registers CountersDocumento28 páginasFALLSEM2022-23 BECE102L TH VL2022230102875 Reference Material I 17-09-2022 Shift Registers CountersAakashAinda não há avaliações

- Rfic ProjectDocumento28 páginasRfic ProjectSrilekha VallabhaneniAinda não há avaliações

- Homework 3 of EE226Documento1 páginaHomework 3 of EE226Srilekha VallabhaneniAinda não há avaliações

- 11 - PPT S2015Documento34 páginas11 - PPT S2015Srilekha VallabhaneniAinda não há avaliações

- Homework 4 EE226Spring2011Documento1 páginaHomework 4 EE226Spring2011Srilekha VallabhaneniAinda não há avaliações

- Homework 2 of EE226Documento1 páginaHomework 2 of EE226Srilekha VallabhaneniAinda não há avaliações

- EE203: Homework Assignment #3: Answer: I + I + I 0 Therefore I 516 Ua. 85. 0.9883Documento10 páginasEE203: Homework Assignment #3: Answer: I + I + I 0 Therefore I 516 Ua. 85. 0.9883Srilekha VallabhaneniAinda não há avaliações

- Guidelines For Preparing Term PaperDocumento7 páginasGuidelines For Preparing Term PaperSrilekha VallabhaneniAinda não há avaliações

- DPSDDocumento16 páginasDPSDDhilip PrabakaranAinda não há avaliações

- Arduino Experimenters GuideDocumento32 páginasArduino Experimenters Guiderudyzarzoff100% (1)

- Minor ProjectDocumento34 páginasMinor ProjectDiksha SharmaAinda não há avaliações

- Tcoil SST TX Kossel JSSC 2008Documento16 páginasTcoil SST TX Kossel JSSC 2008顏敬賢Ainda não há avaliações

- PL USD DLRDocumento20 páginasPL USD DLRIkram ArifAinda não há avaliações

- PLC Programming Course1 KMXDocumento55 páginasPLC Programming Course1 KMXtitohemanAinda não há avaliações

- DTMF Using FPGADocumento16 páginasDTMF Using FPGATejas DharaniAinda não há avaliações

- Fairchild by Element14 Batch 1Documento9 páginasFairchild by Element14 Batch 1aoctaAinda não há avaliações

- Avionics Databus PDFDocumento18 páginasAvionics Databus PDFAnonymous C9ZNFkrb6100% (3)

- LED Solar ProjectDocumento102 páginasLED Solar ProjectBrandy RomanAinda não há avaliações

- 3.1.3.A FlipFlopApplications - Shift Registers-1Documento4 páginas3.1.3.A FlipFlopApplications - Shift Registers-1HenryAinda não há avaliações

- BC 1500Documento22 páginasBC 1500venkatAinda não há avaliações

- Flip Flop MultivibratorDocumento161 páginasFlip Flop MultivibratorMuhammad Rizani RusliAinda não há avaliações

- DM74LS194A 4-Bit Bidirectional Universal Shift RegisterDocumento6 páginasDM74LS194A 4-Bit Bidirectional Universal Shift Registerhayssam100% (1)

- DatasheetDocumento5 páginasDatasheetDavid Alanoca100% (8)

- Verilog QuestionsDocumento2 páginasVerilog QuestionsSAI SREEKANTHAinda não há avaliações

- ELTR145 Sec2Documento105 páginasELTR145 Sec2Midori HiroshiAinda não há avaliações

- Lab7 State MachineDocumento7 páginasLab7 State MachineardserAinda não há avaliações

- Digital Principle and System DesignDocumento26 páginasDigital Principle and System Designainugiri100% (4)

- VLSIDocumento5 páginasVLSIAnurag MishraAinda não há avaliações

- Member of The Ams Group: Cmosis / AwaibaDocumento41 páginasMember of The Ams Group: Cmosis / AwaibaMichael KöhlerAinda não há avaliações

- Medidor de Fly Backs k7205Documento6 páginasMedidor de Fly Backs k7205Alejandro ChiappesoniAinda não há avaliações

- MC33385 - Atm36bDocumento11 páginasMC33385 - Atm36btason07Ainda não há avaliações

- Cao-Notess by Girdhar Gopal Gautam 3gDocumento130 páginasCao-Notess by Girdhar Gopal Gautam 3gGirdhar Gopal GautamAinda não há avaliações

- Exam1 (Example With Solutions)Documento5 páginasExam1 (Example With Solutions)Rüya Gïbî100% (1)

- Toshiba 74HC595D (X34TTD-410-02) E 20160209-909557Documento10 páginasToshiba 74HC595D (X34TTD-410-02) E 20160209-909557Vanesa RiveraAinda não há avaliações

- An Integrated Circuit TesterDocumento6 páginasAn Integrated Circuit TesterlvrevathiAinda não há avaliações

- Shift Register Teknik DigitalDocumento25 páginasShift Register Teknik DigitalMIlhamMaulana100% (1)

- Sequential Digital Circuits: Flip FlopsDocumento27 páginasSequential Digital Circuits: Flip FlopsSubrahmanyam GuduruAinda não há avaliações