Escolar Documentos

Profissional Documentos

Cultura Documentos

SEP - Procesoare Digitale de Semnal in Virgula Mobila-Cap15

Enviado por

Mops LightTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

SEP - Procesoare Digitale de Semnal in Virgula Mobila-Cap15

Enviado por

Mops LightDireitos autorais:

Formatos disponíveis

Procesoare digitale de semnal in virgula mobila

Principalele limitari ale procesoarelor in virgula fixa sunt precizia si gama dinamica redusa. De aceea in cazul implementarilor in virgula fixa este necesara scalarea atenta a valorii datelor pentru a evita depasirile de scala. Deoarece scalarea implica reducerea gamei dinamice ea este insotita de scaderea raportului semnal/zgomot in sistemele pentru prelucrarea semnalelor. In schimb folosirea aritmeticii in virgula mobila ofera o precizie si o gama dinamica mai buna decit aritmetica in virgula fixa, utila in special in aplicatiile care cer o precizie mare de calcul cum ar fi actionarile electrice, sistemele pentru comanda robotilor, grafica pe calculator, s.a. O comparatie privind avantajele si dezavantajele celor doua mari familii de procesoare de semnal este data in Tabelul 1. Tabelul 1 Virgula fixa Arhitectura de sistem mai simpla Programare mai dificila Memorie interna extinsa Cost mai redus Precizie limitata Gama dinamica redusa Erorile de calcul sunt rapid acumulabile Virgula mobila Arhitectura de sistem complexa Programare eficienta in limbajele de nivel inalt Necesita extinderea memoriei in afara cipului Cost mai ridicat Precizie ridicata si mentinuta fara operatii suplimentare Gama dinamica ridicata

Procesoarele cu aritmetica in virgula mobila folosesc de regula cuvinte de 32 de biti. De exemplu, un procesor pe 32 de biti care foloseste 24 de biti pentru reprezentarea mantisei si 8 biti pentru reprezentarea exponentului ofera o gama dinamica de 1530 dB. Procesoarele in virgula mobila executa operatiile cu viteza de prelucrarea a datelor intregi, evitind totodata aparitia unor situatii delicate (de exemplu, depasirea de scala, scalarea semnalelor, alinierea operanzilor) care se manifesta in cazul virgulei fixe. Datorita gamei dinamice mari oferita de aceasta reprezentare, anumite operatii (calculul TRF, realizarea filtrelor RII in cascada) care conduc la cresterea valorii datelor la propagarea de la etaj la etaj nu produc usor

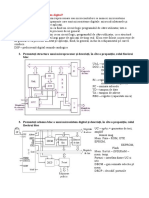

depasirea scalei cum se intimpla in cazul virgulei fixe. In plus efectele de cuantizare sunt mai putin prezente. Deoarece lungimea cuvintelor cu care opereaza procesoarele in virgula mobila este mai mare decit la virgula fixa, aceste procesoare accepta un numar mai mare de moduri de adresare precum si un grad mai mare de paralelism in executie. Folosirea limbajelor de nivel inalt pentru programare este mai eficienta datorita arhitecturii orientate pe registri, a folosirii instructiunilor in virgula mobila, a spatiului mai mare de adrese, a numarului mai mare de moduri de adresare, a flexibilitatii setului de instructiuni, etc. In plus virgula mobila permite o trecere mai directa de la mediul de simulare pe un calculator gazda folosind programele MatLab sau C, catre o implementare in timp real pe un sistem tinta cu procesor DSP. In mod curent procesoarele in virgula mobila sunt folosite pentru aplicatii performante, ca de exemplu sisteme pentru videoconferinta, retele de comunicatii cu comutare de pachete, statii de baza pentru telefonia celulara, sisteme radar si sonar, imagistica digitala, etc. Familia TMS320 contine trei generatii de procesoare in virgula mobila, respectiv C3x, C4x si C67x. TMS320C3x Structura interna este prezentata in Fig. 1 (5.1). Generatia C3x foloseste o arhitectura Harvard pe 32 de biti, cu registre de 40 de biti pentru extinderea preciziei. Aceste procesoare includ unitati de prelucrare in virgula mobila (de exemplu, multiplicator, ALU, deplasator), facilitati pentru managementul rapid al memoriei cu controler DMA incorporat, un cache intern pentru instructiuni de 64 cuvinte si un spatiu de adrese de 16 Mcuvinte. Procesorul are un fisier de registre de uz general, un cache pentru program, doua unitati aritmetice dedicate pentru registrele auxiliare precum si o memorie interna cu acces dublu. Viteza de executie este optimizata prin implementarea hardware a unor operatii frecvent utilizate, cum sunt operatiile repetitive cu blocuri de date, adresarea circulara, multiplicarea. Sistemul de magistrale interne permite executarea in paralel a operatiilor de extragere a codurilor, a accesarii datelor (pentru citiri/scrieri) si a transferurilor DMA. Procesorul foloseste adrese de 24 de biti pentru accesarea cuvintelor de cod si de date de 32 de biti.

Pentru functionarea in sisteme multiprocesor, cu memorie globala partajata, C3x foloseste cinci instructiuni si doua fanioane I/O externe, care pot fi configurati prin software ca intrari sau iesiri pentru executarea operatiei de interblocare. Desi procesorul este folosit mai ales ca procesor pentru operatii in virgula mobila, operatiile in virgula fixa sunt utile pentru anumite aplicatii, cum sunt prelucrarile de imagini. Procesoarele C3x executa operatii in virgula fixa, in virgula mobila si operatii logice folosind instructiuni cu doi sau cu trei operanzi. De asemenea C3x poate executa in paralel multiplicati si operatii cu ALU cu numere intregi reprezentate in virgula fixa sau cu numere reale reprezentate in virgula mobila intr-un singur ciclu. Procesoarele familiei pot executa mai multe tipuri de bucle (buclare hardware pentru instructiuni sau pentru blocuri de program, buclare intirziata pentru multiprocesare, buclare standard pentru golirea pipeline-ului). De asemenea pot fi executate conversii din virgula fixa in virgula mobila. Procesoarele familiei pot executa pina la 150 milioane de instructiuni in virgula mobila pe secunda (150 Mflops). C3x foloseste trei formate de date: intregi cu semn, intregi fara semn si numere in virgula mobila. Pentru numerele in virgula mobila este disponibil si un format in precizie extinsa. Numerele intregi pot fi reprezentate cu 16 biti (formatul scurt) sau cu 32 de biti (formatul lung). Pentru reprezentarea in virgula mobila sunt folosite trei formate de date: formatul scurt (16 biti), formatul standard (32 de biti) si formatul extins (40 de biti). Formatele de reprezentare nu respecta standardul IEEE 754. Pentru anumite aplicatii de timp real datele de intrare sunt esantioane de semnal furnizate de convertoare A/D. Procesoarele C3x convertesc datele intregi intr-un format cu virgula mobila, le prelucreaza, iar la sfirsit convertesc rezultatul in format intreg si le transefera la CDA. TMS320C4x Generatia C4x contine primele procesoare DSP proiectate pentru prelucrari paralele. Procesoarele C4x sunt compabibile la nivel de cod cu C3x. Procesoarele familiei includ sase porturi de comunicatie, un controler DMA cu sase canale, doua unitati independente de 32 de biti pentru interfatarea memoriei. Dupa cum s-a mentionat pot fi conectate direct pina la sase procesoare C4x pentru prelucrari paralele.

TMS320C67x Cel mai recent procesor in virgula mobila din familia TMS320 este TMS320C67x. C67x are la baza arhitectura VLIW prezentata anterior. Setul de instructiuni al procesorului C67x este un superset al setului de instructiuni al procesoarelor C62x, fiind adaugate instructiuni pentru operatii in virgula mobila. Procesorul este capabil sa execute pina la 1350 Mflops la un tact de 225MHz. C67x este optimizat pentru executarea eficienta a programelor scrise in limbajul C. Procesoarele C67x sunt destinate aplicatiilor care cer precizie ridicata de calcul, gama dinamica mare si viteza mare de calcul (radar, sonar, grafica 3D, statii de baza wireless, linii de abonat digitale, imagistica medicala, s.a.) Arhitectura C67x accepta date reprezentate in virgula mobila pe 32 de biti sau pe 64 biti. Fiecare din cele doua cai de date contin cite patru unitati de executie, cite un fisire de registre de uz general si cai de transfer de date intre registre si memorie. Arhitectura C67x este prezentata in Fig. 2 (5.6).

Fig. 2 Arhitectura procesoarelor C67x

Procesoarele C67x au doua cai de date in virgula mobila, o unitate pentru controlul programului, un controller DMA, memorie interna precum si interfete pentru extensia memoriei pentru programe si date. Cele doua cai de date accepta operanzi de 32/64 biti in virgula mobila si contin cite patru unitati de executie fiecare (.L, .S, .M si .D), un fisier de registre precum si cai de transer a datelor intre memorie si registre. Procesoarele C67x pot executa pina la opt instructiuni intr-un ciclu, incluzind doua operatii de multiplicare in precizie simpla sau o multiplicare in precizie dubla. Fata de procesoarele C62x arhitectuta C67x a fost modificata pentru a permite incarcarea operanzilor cu precizie dubla pe 64 biti. Procesoarele contin doua fisiere de cite 16 registre de uz general de 32 biti (A si B). Grupuri de cite doua registre adiacente pot stoca si operanzi pe 64 biti pentru operatii realizate cu precizie dubla. Operatiile realizate in precizie dubla necesita mai mult timp decit cele executate in precizie simpla. Memoria interna are o arhitectura Harvard modificata ccare asigura spatii separate pentru coduri si date. Cele doua cai de date sunt conectate la memoria de date prin magistrale de adrese (32 biti) si de date (64 biti) separate. Memoria pentru programe este accesata printr-o magistrala de adrese de 32 biti si una pentru date de 256 biti. O varianta mai performanta din familia C67x (C6713) ofera posibilitatea de a configura memoria interna ca memorie cache de nivel 1 (L1), iar memoria externa ca memorie cache de nivel 2 (L2), atit pentru coduri cit si pentru date. Procesoarele C67x poseda un sistem de periferice similar cu cel existent la procesoarele C62x/64x. C67x accepta toate instructiunile procesoarelor C62x plus un numar de instructiuni noi incluzind: multiplicari de numere intregi pe 32 de biti, incarcari de date de 64 biti, instructiuni pentru operatii in virgula mobila, etc. C67x realizeaza o folosire intensa a memoriei deoarece arhitectura VLIW produce pachete de pina la opt instructiuni de 32 de biti.

Você também pode gostar

- Procesoare Digitale de Semnal Si Sisteme PDSDocumento14 páginasProcesoare Digitale de Semnal Si Sisteme PDSRadu DanAinda não há avaliações

- Proiectarea Cu Microprocesoare c01Documento36 páginasProiectarea Cu Microprocesoare c01M LAinda não há avaliações

- PMP c01Documento30 páginasPMP c01Raluca RaluAinda não há avaliações

- Procesoarele Numerice de SemnalDocumento26 páginasProcesoarele Numerice de SemnalAlexandru TipaAinda não há avaliações

- Caracteristici RISC, UltraSPARC II Si MagistraleDocumento9 páginasCaracteristici RISC, UltraSPARC II Si MagistraleRoccoSuasitoAinda não há avaliações

- Ac ExamDocumento92 páginasAc ExamNegru TatianaAinda não há avaliações

- Carte SMPDocumento213 páginasCarte SMPAdrian FilipAinda não há avaliações

- Arhitectura MicroprocesoarelorDocumento78 páginasArhitectura MicroprocesoarelorDaniel Anton0% (1)

- Alin Tema 2 SMPDocumento5 páginasAlin Tema 2 SMPdragos_petrisorAinda não há avaliações

- Atestarea 1 AC RezolvatDocumento10 páginasAtestarea 1 AC RezolvatIon DamaschinAinda não há avaliações

- Componentele Unui Calculator Si Rolul LorDocumento63 páginasComponentele Unui Calculator Si Rolul LorVasile BerceaAinda não há avaliações

- Componentele Unui Calculator Si Rolul LorDocumento63 páginasComponentele Unui Calculator Si Rolul LorDorian MikeAinda não há avaliações

- Referat Arhitectura MicroprocesoarelorDocumento5 páginasReferat Arhitectura MicroprocesoarelorrobertexeAinda não há avaliações

- Arhitectura Calculatoaarelor C - 9Documento10 páginasArhitectura Calculatoaarelor C - 9Popa DaniAinda não há avaliações

- Atestarea AcDocumento11 páginasAtestarea AcCristina FloreaAinda não há avaliações

- Curs SAIPDocumento114 páginasCurs SAIPLaura ElenaAinda não há avaliações

- 01 Sisteme de CalculDocumento38 páginas01 Sisteme de CalculMike MikkelsenAinda não há avaliações

- Sistem de TelemasuraDocumento33 páginasSistem de TelemasuraRampajasdAinda não há avaliações

- Capitolul IiiDocumento6 páginasCapitolul IiiMoisii PetruAinda não há avaliações

- Sisteme Cu MicroprocesoareDocumento4 páginasSisteme Cu MicroprocesoareDiana NichiforAinda não há avaliações

- Curs10 11Documento18 páginasCurs10 11Cezara CocuAinda não há avaliações

- 5 6 Procesoare Si DSPDocumento14 páginas5 6 Procesoare Si DSPRambo333Ainda não há avaliações

- MicrocontrolereDocumento22 páginasMicrocontrolereAlexandru-Iulian IfrimAinda não há avaliações

- PMDDocumento34 páginasPMDPasan PetruAinda não há avaliações

- A SAD Achizitii Si PrelucrareDocumento180 páginasA SAD Achizitii Si PrelucrarerazvanjuvAinda não há avaliações

- Cursuri Depanare Hard-SoftDocumento15 páginasCursuri Depanare Hard-SoftflanjaAinda não há avaliações

- Mcu 01Documento92 páginasMcu 01Alex BadeaAinda não há avaliações

- Materiale Examen I Curs CSO I Ver.9Documento96 páginasMateriale Examen I Curs CSO I Ver.9Adrian NaeAinda não há avaliações

- Curs3 RamonaDocumento24 páginasCurs3 RamonaMatei FloreaAinda não há avaliações

- SMPDocumento222 páginasSMPPetreCaracaleanuAinda não há avaliações

- AC Sesiunea 1Documento8 páginasAC Sesiunea 1Valeria CodreanAinda não há avaliações

- Curs CNDocumento284 páginasCurs CNTatiana PurcareataAinda não há avaliações

- Proiectarea Microsistemelor DigitaleDocumento34 páginasProiectarea Microsistemelor DigitaleIulia Casapu100% (1)

- 2-Sisteme de Achizitie A DatelorDocumento5 páginas2-Sisteme de Achizitie A Datelorcioranu_ionAinda não há avaliações

- Arhitectura Calculatoarelor - Proc-IntelDocumento12 páginasArhitectura Calculatoarelor - Proc-Intelioana0simionAinda não há avaliações

- Considerații Teoretice - Automate ProgramabileDocumento35 páginasConsiderații Teoretice - Automate ProgramabileViorica MereoaraAinda não há avaliações

- Magistrale de SistemDocumento6 páginasMagistrale de SistemBruma NikuAinda não há avaliações

- Sisteme de CalculDocumento41 páginasSisteme de CalculAndreeaAinda não há avaliações

- Sisteme Cu Microprocesoare Unitatea de Invatare 5Documento12 páginasSisteme Cu Microprocesoare Unitatea de Invatare 5samycatalinAinda não há avaliações

- Referat - Retele de CalcDocumento9 páginasReferat - Retele de CalcVirginiaMihaelaAinda não há avaliações

- Atestare 2Documento20 páginasAtestare 2Elena ChicuAinda não há avaliações

- Examen PMP2Documento23 páginasExamen PMP2Tatar DanielAinda não há avaliações

- Documentatie CSC MazuruDocumento23 páginasDocumentatie CSC MazuruAlexandru AstefanoaieAinda não há avaliações

- Curs SM 4Documento27 páginasCurs SM 4Lavro IonutAinda não há avaliações

- Microcontrolerele AVR Pe 8 BitiDocumento19 páginasMicrocontrolerele AVR Pe 8 BitiolgaAinda não há avaliações

- Proiectarea Unei Retele de CalculatoareDocumento23 páginasProiectarea Unei Retele de CalculatoareCristian EnacheAinda não há avaliações

- 02 Evolutia Arhitecturilor Sist MicroprocesorDocumento11 páginas02 Evolutia Arhitecturilor Sist MicroprocesorCM MaryAinda não há avaliações

- Sisteme Digitale Pentru Prelucrarea Semnalelor in TelecomunicatiiDocumento2 páginasSisteme Digitale Pentru Prelucrarea Semnalelor in TelecomunicatiiMunteanu Tudor TudorAinda não há avaliações

- Laborator3 MIPSDocumento12 páginasLaborator3 MIPSMitzy MtzAinda não há avaliações

- Arhitectura Sistemelor de CalculDocumento41 páginasArhitectura Sistemelor de CalculVlad MuresanAinda não há avaliações

- Prelucrarea Datelor ExperimentaleDocumento16 páginasPrelucrarea Datelor ExperimentaleMihăiță PetreaAinda não há avaliações

- Proiectarea Unei Retele de Calculatoare PDFDocumento23 páginasProiectarea Unei Retele de Calculatoare PDFPaun MihaiAinda não há avaliações

- Structura Interna de Baza A Procesoarelor Intel PDFDocumento14 páginasStructura Interna de Baza A Procesoarelor Intel PDFБухонина ТатьянаAinda não há avaliações

- Recenzie La Emile Durkheim - Regulile Metodei SociologiceDocumento7 páginasRecenzie La Emile Durkheim - Regulile Metodei SociologiceLavinia Benedic100% (1)

- SEP - TMS320C10 - Cap13Documento21 páginasSEP - TMS320C10 - Cap13Mops LightAinda não há avaliações

- ASC 4 Nivelul Fizic SublDocumento51 páginasASC 4 Nivelul Fizic SublMops LightAinda não há avaliações

- ASC 2 Tipuri de Arhitecturi SUBLINIATDocumento47 páginasASC 2 Tipuri de Arhitecturi SUBLINIATMops LightAinda não há avaliações