Escolar Documentos

Profissional Documentos

Cultura Documentos

Electronica Digital Apuntes Unidad 4 Flip Flops

Enviado por

Juan Carlos CamposTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Electronica Digital Apuntes Unidad 4 Flip Flops

Enviado por

Juan Carlos CamposDireitos autorais:

Formatos disponíveis

Circuitos Digitales

Contenido

Unidad IV Lgica Secuencial

4.1 Flip-flops y dispositivos relacionados 4.2 Contadores 4.3 Registros de desplazamiento

Realizacin de prcticas

Nombre 15. Contador sncrono 16. Contador asncrono 17. Sistema de transmisin de datos paralelo-serieparalelo 18. Diseo de una mquina secuencial 19.Registros 20. Deteccin de falla de un sistema de transmisin de datos Tipo Simulacin Simulacin Fecha de realizacin/ entrega 21/Nov 21/Nov 17 Nov 24/Nov 24/Nov No

Introduccin

Entrada (s)

Lgica combinacional

Salida (s)

Laboratorio Simulacin Simulacin Simulacin

Elementos de memoria

Circuito secuencial

Introduccin

Flip-flops y dispositivos relacionados

Sncronos (flip-flop, biestables)

Perodo de reloj Flanco de bajada

Dependen de una seal de reloj (flanco de subida o bajada) Asncronos (latch)

Flanco de subida

Ancho de reloj

Seal de reloj

Dependen de una seal de control (nivel alto o bajo)

Maribel Gmez Franco

Circuitos Digitales

Flip-flops (biestables)

Latch SR con entradas activas en nivel alto

Tienen dos estados estables:

S Q

S 0 0 0

R 0 0 1 0 1

Q 0 1 X X X

Qn 0 1 0 1

Qn 1 0 1 0

SET (la salida se pone a uno lgico) activar, establecer

R

1 1

Indeterminado

RESET (la salida se pone a cero lgico) desactivar, restablecer, borrar

a) Smbolo lgico

b) Tabla de verdad

Latch SR disparado por compuerta

Latch D disparado por compuerta

C

S Q C Q R

S X X 0 0 0 1 1

R X X 0 0 1 0 1

Q 0 1 0 1 X X X

Qn 0 1 0 1 0 1 NA a) Smbolo lgico b) Circuito lgico c) Tabla de verdad

D C Q 0 1 1 X 0 1 1 X X 1 0 1 Q C 0

4,0/3,0

0 0 1 1 1 1 1

D X

Q 0

Qn 0

a) Smbolo lgico

b) Tabla de verdad

Latch D cudruple

Latch D cudruple

Entradas C 1 1 0 D 0 1 X

Salidas Observaciones Qn 0 1 Q Qn 1 0 Q Reset Set Sin cambio

0.000ms

0.500ms

1.000ms

1.500ms

2.000ms

2.500ms

3.000ms

3.500ms

4.000ms

4.500ms

5.000ms 5.000 V

D E Q

0.000 V

5.000 V

0.000 V

5.000 V

a) Circuito integrado

c) Tabla de funcin

0.000 V

Maribel Gmez Franco

Circuitos Digitales

Flip-flop SR

Diagrama de estados del flip-flop SR

R Q Clk Q S

clk R Q

Tabla de excitacin

Q Qn 0 1 0 1 S 0 1 0 X R X 0 1 0 S=0 R=X Q=0 S=1, R=0

Tabla caracterstica

S 0 0 1 1 R 0 1 0 1 Qn Q 0 1 NA

Ecuacin caracterstica

Q 0

Tabla de excitacin

Qn 0 1 0 1 S 0 1 0 X R X 0 1 0

0 0 1 1

Q=1 S=0, R=1 S=X R=0

Qn=S+RQ SR=0

0 1 1

Flip-flop JK

Diagrama de estados del flip-flop JK

K

Clk

Tabla de excitacin

Q 0 0 Qn 0 1 0 1 J 0 1 X X K X X 1 0 J=X, K=1 J=X K=0 J=0 K=X Q=0 J=1, K=X

clk K Q

Q=1

Tabla caracterstica

J 0 0 1 1 K 0 1 0 1 Qn Q 0 1 Q

Ecuacin caracterstica

Q 0

Tabla de excitacin

Qn 0 1 0 1 J 0 1 X X K X X 1 0

1 1

Qn=JQ+KQ

0 1 1

Diagrama de tiempos del flip-flop JK

Flip-flop D

D Q

Clk

Q clk Q

J K Clk

D Qn 0 1

Tabla caracterstica

Ecuacin caracterstica

Tabla de excitacin

Q 0 Qn 0 1 0 1 D 0 1 0 1

0 1

Qn=D

0 1 1

Maribel Gmez Franco

Circuitos Digitales

Diagrama de estados del flip-flop D

Diagrama de tiempos del flip-flop D 7474

Tabla de excitacin

Q 0 0 1 1 Qn 0 1 0 1 D 0 1 0 1 D=0 Q=0 Q=1 D=1 D=0

D Clk Q

D=1

Flip-flop T (Toggle)

Flip-flop T

T Clk

Q clk Q

Tabla de excitacin

Q 0

Qn 0 1 0 1

T 0 1 1 0 T=0 Q=0

T=1

Tabla caracterstica

Ecuacin caracterstica

Tabla de excitacin

Q Qn 0 1 0 1 T 0 1 1 0

0 1 1

Q=1 T=1 T=0

T 0 1

Qn Q Q

Qn=TQ+TQ

0 0 1 1

Disparo de los flip-flops

Disparo de los flip-flops

1 1 S Clk 0 R Q Q 0 t0

1 0 S Clk 1 R Q Q 0 t0

a) S=1, R=0 Estado SET en el flanco positivo de reloj

b) S=0, R=1 Estado RESET en el flanco positivo de reloj

Maribel Gmez Franco

Circuitos Digitales

Disparo de los flip-flops

Un mtodo de disparo por flanco

S Clk

Q=Q0 Sin cambio

Detector de transiciones de impulsos

S

Q

Q R

c) S=0, R=0 Estado permanece sin cambio en el flanco positivo de reloj

Compuertas de gobierno

Latch

Un mtodo de disparo por flanco

Flip-flops con entradas asncronas

CLR D

Q D

PRE Q C Q CLR

C Q

PRE

Dispositivos especficos

Dispositivos especficos

S D Q CP QN R

1S 1Q 1D >C1 1R 1Q 2S 2Q 2D >C2 2R 2Q

S J Q CP K QN R

1S 1J >C1 1K 1R 2S 2J >C2 2K 2R

1Q

1Q 2Q

2Q

Maribel Gmez Franco

Circuitos Digitales

Flip-flop JK 74LS76

Clk

Flip-flop 7476 con entradas asncronas

Clk

S R

PRE CLR

Caractersticas de operacin de los flip-flops

Retardo de propagacin tplh

Punto del 50% en el flanco de disparo Clk

PRE

Punto del 50 %

Q tPLH

Punto del 50% en la transicin de Q de nivel bajo a nivel alto

Q tPLH

Punto del 50% en la transicin de Q de nivel bajo a nivel alto

Retardo de propagacin

Retardo de propagacin tphl

Retardo de propagacin tphl

Punto del 50% en el flanco de disparo

Punto del 50% en el flanco de disparo Clk Q Punto del 50% en la transicin de Q de nivel alto a nivel bajo CLR Q

Punto del 50% en la transicin de Q de nivel alto a nivel bajo

tPHL

tPHL

Maribel Gmez Franco

Circuitos Digitales

Tiempo de establecimiento ts (tset up)

Tiempo de establecimiento ts (tset up)

Punto del 50%

Es el intervalo mnimo en que los niveles lgicos deben mantenerse constantes en las entradas (J-K, S-R, D o T) antes de que llegue el flanco de disparo del impulso de reloj.

clk Punto del 50%

tS

Tiempo de sostenimiento th (thold)

Tiempo de sostenimiento th (thold)

Es el intervalo mnimo en que los niveles lgicos deben permanecer constantes en las entradas despus de que haya pasado el flanco de disparo del impulso de reloj, de modo que dichos niveles sincronicen correctamente el flip-flop.

Punto del 50% D

Clk

th

Flip-flops Maestro-esclavo

Aplicacin de los flip-flops

Entrada de datos en paralelo

D3

Q

D2

D1

D0

J clk K

S Maestro

Entradas J 0 K 0 1 0 1 clk

Salidas Qn Q 0 1 Q Qn Q 1 0 Q

Observaciones Sin cambio RESET SET Cambio CLK CLR

D3 Clk

Q3

D2 Clk

Q2

D1 Clk

Q1

D0

Q0

Esclavo Q

0 1 1

Clk

Q3

Q2

Q1

Q0

Salida de datos en paralelo

Almacenamiento de datos en paralelo

Maribel Gmez Franco

Circuitos Digitales

Aplicacin de los flip-flops Divisor de frecuencia

Aplicacin de los flip-flops Contador

QB QA 1 J clk > Clk K Flip-flop B

0 1 2 3 5 6

1 J clk > Clk K Flip-flop B QB

1

1 J > Clk K Flip-flop A QA

J > Clk K Flip-flop A

7 8 9 10

Clk

Clk 0 0 1 0 1 0 1 2 1 1 3 0 0 0 1 0 1 0 1 2 1 1 3 0 0 0 1 0 1 0 1 2

QB

QB

QA

QA 0

Contador asncrono MOD_4

Contador asncrono MOD_4

QA 1 QB

QA 1

QB

clk

FFA S

FFB S J Q CP K QN R

FFA S J Q CP K QN R

FFB S J Q CP K QN R

J Q CP K QN R

clk

clk 0

1 1

2 0

3 1

4 0

QA QA

QB

Contadores de dcadas asncrono

Contador binario 7493

5V +V

Clk B

+V

+V J Q CP K QN R J Q CP K QN R

+V J Q CP K QN R

+V J Q CP K QN R

Clk A

J Q CP K QN R J Q CP K QN R J Q CP K QN R J Q CP K QN R

RO1 RO2 Q0 Q1 Q2 Q3

Maribel Gmez Franco

Circuitos Digitales

Contador binario 7493

Mquinas secuenciales

clk Entradas Lneas de excitacin Y0 Y1 . Yk Q0 Q1 . Qx Salidas

74LS93 MR1 Q3 MR2 Q2 CP0 Q1 CP1 Q0

I0 I1 . Im

Lgica combinacional

Memoria (Flip-flops)

O0 O1 . On

Lneas de variables de estado

Tipos de circuitos secuenciales

0/0 Entrada/Salida C=1/Y=0

Tipos de circuitos secuenciales

0 Entrada 1 0 01/0 1

0/0 01

00

00/0 Estado/salida 1

1/0 1/1

11 0/0 1/0

10 0/0

11/1 0 1

10/0 0

Mealy

Moore

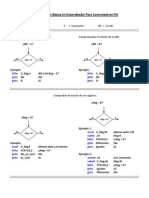

Procedimiento de diseo de un circuito secuencial

Generar el diagrama de estados Generar las tablas de estado siguiente y de salida Minimizar estados Codificar entradas, estados, salidas Seleccionar elementos de memoria Obtener las ecuaciones de excitacin Optimizar la implantacin lgica Obtener el circuito lgico y diagramas de tiempos Simular el circuito lgico Verificar funcionalidad y temporizacin

Diseo de un contador ascendente MOD_8

a) Generar el diagrama de estados

000

001

010

011

111

110

101

100

Maribel Gmez Franco

54

Maribel Gmez Franco

Circuitos Digitales

b) Obtener la tabla de estado siguiente

c) Seleccin del flip-flop, Tabla de excitacin JK

Q 0 0 1 1 Qn 0 1 0 1 J 0 1 X X K X X 1 0

Estado presente QA 0 0 0 0 1 1 1 1 QB 0 0 1 1 0 0 1 1 QC 0 1 0 1 0 1 0 1

Estado siguiente QA(n) 0 0 0 1 1 1 1 0 QB(n) 0 1 1 0 0 1 1 0 QC(n) 1 0 1 0 1 0 1 0

Maribel Gmez Franco

55

Maribel Gmez Franco

56

d) Obtener tabla de estado siguiente:

d) Obtener tabla de estado siguiente:

Estado presente QA 0 0 0 0 1 1 1 1 QB 0 0 1 1 0 0 1 1 QC 0 1 0 1 0 1 0 1

Estado siguiente QA(n) 0 0 0 1 1 1 1 0 QB(n) QC(n) 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 JA KA

Estado presente QA 0 0 0 0 1 1 1 1 QB 0 0 1 1 0 0 1 1 QC 0 1 0 1 0 1 0 1

Estado siguiente QA(n) 0 0 0 1 1 1 1 0 QB(n) QC(n) 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 JA 0 0 0 1 X X X X KA X X X X 0 0 0 1

Maribel Gmez Franco

57

Maribel Gmez Franco

58

d) Obtener tabla de estado siguiente:

d) Obtener tabla de estado siguiente:

Estado presente QA 0 0 0 0 1 1 1 1 QB 0 0 1 1 0 0 1 1 QC 0 1 0 1 0 1 0 1

Estado siguiente QA(n) 0 0 0 1 1 1 1 0 QB(n) QC(n) 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 JB KB

Estado presente QA 0 0 0 0 1 1 1 1 QB 0 0 1 1 0 0 1 1 QC 0 1 0 1 0 1 0 1

Estado siguiente QA(n) 0 0 0 1 1 1 1 0 QB(n) QC(n) 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 JB 0 1 X X 0 1 X X KB X X 0 1 X X 0 1

Maribel Gmez Franco

59

Maribel Gmez Franco

60

Maribel Gmez Franco

10

Circuitos Digitales

d) Obtener tabla de estado siguiente:

d) Obtener tabla de estado siguiente:

Estado presente QA 0 0 0 0 1 1 1 1 QB 0 0 1 1 0 0 1 1 QC 0 1 0 1 0 1 0 1

Estado siguiente QA(n) 0 0 0 1 1 1 1 0 QB(n) QC(n) 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 JC Kc

Estado presente QA 0 0 0 0 1 1 1 1 QB 0 0 1 1 0 0 1 1 QC 0 1 0 1 0 1 0 1

Estado siguiente QA(n) 0 0 0 1 1 1 1 0 QB(n) QC(n) 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 JC 1 X 1 X 1 X 1 X Kc X 1 X 1 X 1 X 1

Maribel Gmez Franco

61

Maribel Gmez Franco

62

d) Obtener tabla de estado siguiente:

d) Obtencin de las ecuaciones de excitacin

Estado presente QA 0 0 0 0 1 1 1 1 QB 0 0 1 1 0 0 1 1 QC 0 1 0 1 0 1 0 1

Estado siguiente QA(n) 0 0 0 1 1 1 1 0 QB(n) QC(n) 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 JA 0 0 0 1 X X X X KA X X X X 0 0 0 1 JB 0 1 X X 0 1 X X KB X X 0 1 X X 0 1 JC 1 X 1 X 1 X 1 X Kc X 1 X 1 X 1 X 1

Estado presente QA 0 0 0 0 1 1 1 1 QB 0 0 1 1 0 0 1 1 QC 0 1 0 1 0 1 0 1 JA 0 0 0 1 X X X X KA X X X X 0 0 0 1

QBQC QA 0 1

00

01

11 1

10

JA=QBQC

QB QC QA 0 1 00 X 01 X 11 X 1 10 X

Maribel Gmez Franco

63

Maribel Gmez Franco

KA=QBQC

64

d) Obtencin de las ecuaciones de excitacin

d) Obtencin de las ecuaciones de excitacin:

Estado presente QA 0 0 0 0 1 1 1 1 QB 0 0 1 1 0 0 1 1 QC 0 1 0 1 0 1 0 1

JB 0 1 X X 0 1 X X

KB X X 0 1 X X 0 1

QB QC QA 0 1

00

01 1 1

11 X X

10 X X

Estado presente QA 0 0 0 0 1 QB 0 0 1 1 0 0 1 1 QC 0 1 0 1 0 1 0 1

JC 1 X 1 X 1 X 1 X

Kc X 1 X 1 X 1 X 1

QB QC QA 0 1

00 1 1

01 X X

11 X X

10 1 1

JB=QC

QB QC QA 0 1

JC=1

QB QC QA 0 1 00 X X 01 1 1 11 1 1 10 X X

00 X X

01 X X

11 1 1

10

1 1 1

KC=1

Maribel Gmez Franco

KB=QC

65

Maribel Gmez Franco

66

Maribel Gmez Franco

11

Circuitos Digitales

e) Diseo del contador

Ejercicio

+V FFA

J Q CP K QN R

FFB

J Q CP K QN R

FFC

J Q CP K QN R

Disee un contador MOD_4, tipo Mealy. Si D=1 cuenta descendente, y Y=1 cuando llegue a la cuenta mnima 002; cuando D=0 cuenta ascendente, y Y=1 al alcanzar la cuenta mxima 112.

RST

Maribel Gmez Franco

67

Maribel Gmez Franco

68

a) Generar el diagrama de estados

b) Generar la tabla de estado siguiente y salida

0/0

0/0

00 1/0 0/1 1/1 1/0 1/0

01

D

01

Estado presente QA QB 0 1 0 1 0 1 0 1

Estado siguiente QA(n) 0 1 1 0 1 0 0 1 QB(n) 1 0 1 0 1 0 1 0

Salida

00 1/0

0

1/0 0/0

0 0 1 1 0 0 1 1

0 0 0 1 1 0 0 0

0/0

0/1

1/1 1/0 11

0 0

10 0/0

0 1

11 0/0

10

1 1 1

Maribel Gmez Franco

69

Maribel Gmez Franco

70

d) Obtencin de las ecuaciones de excitacin:

d) Obtencin de las ecuaciones de excitacin:

Q AQ B D

00

01 1

11 X X

10 X X

D 0 0 0 0 1 1 1 1

Estado presente QA 0 0 1 1 0 0 1 1 QB 0 1 0 1 0 1 0 1

JA 0 1 X X 1 0 X X

KA X X 0 1 X X 1 0

0 1 1

D 0 0 0 0

Estado presente QA 0 0 1 1 0 0 1 1 QB 0 1 0 1 0 1 0 1

JB 1 X 1 X 1 X 1 X

KB X 1 X 1 X 1 X 1

JB=KB=1

Q AQ B D 0 1

00 X X

01 X X

11 1

10

1 1 1

JA=KA=DQB+DQB =DQB

Maribel Gmez Franco 71 Maribel Gmez Franco 72

Maribel Gmez Franco

12

Circuitos Digitales

d) Obtencin de las ecuaciones de excitacin:

Contadores

QAQB D 0

D 0 0 0 0 1 1 1 1

Estado presente QA 0 0 1 1 0 0 1 1 QB 0 1 0 1 0 1 0 1

00

01

11

10

Y 0 0 0 1 1 0 0 0

Contador 74163

Entrada de datos

1 1

D3

D2

D1

D0

Y=DQAQB+DQAQB

CLR LOAD ENP ENT > CLK Q3 Q2 Q1

RCO TC=15 Q0

Salida de datos

Maribel Gmez Franco

73

Contadores

Contadores

Contador 74160

Entrada de datos

Contador ascendente/descendente 74190

Entrada de datos

D3 D2 D1 D0 CLR LOAD ENP ENT > CLK RCO TC=09 Q3 Q2 Q1 Q0 CTEN D/U LOAD > CLK

D3 D2 D1 D0 RCO MAX/MIN Q3 Q2 Q1 Q0

Salida de datos Salida de datos

Contadores en cascada

Contadores en cascada

Contador mdulo 32

Contador mdulo 100

J0 clk >C K0 Q0

J1 >C K1 Q1

J2 >C K2 Q2

J3 >C K3 Q3

J4 >C K4 Q4

Q4

Contador 1

CTEN CTR DIV 10 TC Q3 Q2 Q1 Q0

Contador 2 fin/10

CTEN > CLK Q3 Q2 Q1 Q0 CTR DIV 10 TC

clk

> CLK

fin/100

fin

Mdulo 4

Mdulo 8

Mdulo global= 4 8 = 32

Maribel Gmez Franco

13

Circuitos Digitales

Contadores en cascada

Decodificador de contadores

Contador mdulo 1000

10 kHz

Decodificacin del estado cinco

+V

1 CTR DIV 10 CTEN TC > CLK

100 kHz

1 kHz

clk

Q2

Q1

Q0

1 MHz

CTR DIV 10 CTEN TC > CLK

CTR DIV 10 CTEN TC > CLK

J Q CP K QN R

J Q CP K QN R

J Q CP K QN R

Salida =1 con el 5 decodificado

Contadores

Registros de desplazamiento

Aplicacin: control de estacionamiento

Sensor de entrada asc Interface CTR DIV 100 Sensor de salida desc Bajada/Subida Activacin de barrera Valor de fin de cuenta Enc./Apag. Indicador de completo

Entrada Salida Salida

Entrada

a) Entrada serie/ salida serie con desplazamiento a la derecha

b) Entrada serie/ salida serie con desplazamiento a la izquierda

c) Entrada paralelo/salida serie

Registros de desplazamiento

Registros de desplazamiento

Entrada

Entrada

Salida Salida

c) Entrada paralelo/salida serie

Entrada

d) Entrada serie /salida paralelo f) Rotacin a la izquierda g) Rotacin a la derecha

Salida

e) Entrada paralelo/salida paralelo

Maribel Gmez Franco

14

Circuitos Digitales

Registros de desplazamiento

Registros de desplazamiento

Registro de desplazamiento con entrada serie/salida serie

Registro de desplazamiento con entrada serie/salida paralelo

FFA FFB S Q D Q D CP QN R FFC S Q D CP QN R FFD S Q CP QN R

FFA

FFB S D Q D

FFC S Q

FFD S D Q CP QN R

Entrada de datos

Entrada de datos

S D CP QN R

S D Q CP QN R

Salida de datos

CLK QA QB QC QD

CP QN R

CP QN R

Entrada de datos SRG 8 CLK

Q7 Q7

Entrada de datos CLK

SRG 4

QA QB QC QD

Registros de desplazamiento

Registros de desplazamiento con carga paralelo

Registro de desplazamiento con entrada paralelo /salida serie

D0 Shift/Loa d D1 D2 D3

D0 D1 D2 D3

Registro de desplazamiento con carga paralelo

Shift/Load

SRG 4

CLK

Salida de datos

G4

G1

G5

G2

G6

G3

74LS165

Salida de datos serie

FF0 FF1 S Q D Q D CP QN R FF2 S Q D CP QN R FF3 S Q CP QN R

clk

S D CP QN R

6 D7 5 D6 4 D5 3 D4 14 D3 13 D2 12 D1 11 D0

DS 10 PL 1 CE 15 CP 2 Q7N 7 Q7 9

Registros de desplazamiento

Registro de desplazamiento con entrada paralelo /salida paralelo

D0 D1 D2 D3

Registros de desplazamiento

Registro de desplazamiento bidireccional de cuatro bits

D0 D1 D2 D3

Entrada de datos paralelo DD

FFC D S Q FFD D S Q Q0 Q1 Q2 Q3 Q0 Q1 Q2 Q3

FF0 FF1 Q S D Q D CP QN R FF2 S Q D CP QN R FF3 S Q CP QN R

DA

FFA D S Q

DB

FFB D S Q

DC

J K Shift/Load CLR CLK

CLR SRG 4

Right/Left Entrada de datos serie

G1

G5

G2

G6

G3

G7

G4

G8

S0 S1 SR SER SL SER CLK

SRG 4

CP QN R

CP QN R

CP QN R

CP QN R

CLK

S D CP QN R

QA

QB

QC

QD Q0 CLK

Q3

Salida de datos paralelo

Maribel Gmez Franco

15

Você também pode gostar

- Contador 0-39 FlipFlop DDocumento7 páginasContador 0-39 FlipFlop DAtocha Kú GüemezAinda não há avaliações

- 150 Circuitos EletronicosDocumento50 páginas150 Circuitos EletronicosLucelio Santos100% (6)

- Tutorial Caesar II TraducidoDocumento36 páginasTutorial Caesar II Traducidopablopasqualini18100% (2)

- Emulsiones Asfálticas (Definiciones)Documento17 páginasEmulsiones Asfálticas (Definiciones)Willian GonzalezAinda não há avaliações

- Manual Practico de Seguridad y Salud en La ConstrucciónDocumento366 páginasManual Practico de Seguridad y Salud en La ConstrucciónpelionekenobiAinda não há avaliações

- Circuito SecuencialDocumento86 páginasCircuito SecuencialHbr LpzAinda não há avaliações

- Flip Flops Tablas de Verdad, Caracteristicas y Señal de SincroniaDocumento17 páginasFlip Flops Tablas de Verdad, Caracteristicas y Señal de SincroniaChvd OzAinda não há avaliações

- Contadores Con Flip FlopsDocumento25 páginasContadores Con Flip FlopsCerezo YuriAinda não há avaliações

- Problema - Banda TransportadoraDocumento12 páginasProblema - Banda Transportadorabill00619Ainda não há avaliações

- 04 - Ffs y RegistrosDocumento54 páginas04 - Ffs y Registrospruebapruebaprueba03Ainda não há avaliações

- Lab10 Dispos Mendoza Rosales C15 4 CDocumento11 páginasLab10 Dispos Mendoza Rosales C15 4 CJairo Hans Cardenas MauricioAinda não há avaliações

- Contador Flip-Flop Tipo JKDocumento5 páginasContador Flip-Flop Tipo JKOvanio MolinaAinda não há avaliações

- LAB 08 - Registros de DesplazamientoDocumento6 páginasLAB 08 - Registros de Desplazamientogremorysmith123Ainda não há avaliações

- Prac 10 LBDLDocumento14 páginasPrac 10 LBDLIsthar D AvilaAinda não há avaliações

- Sistemas Digitales Problemas 1Documento25 páginasSistemas Digitales Problemas 1Ce ChavezAinda não há avaliações

- Diseño de Contadores UTFSMDocumento16 páginasDiseño de Contadores UTFSMMarco AlvarezAinda não há avaliações

- Diseño de SecuenciaDocumento9 páginasDiseño de SecuenciaCarlos Alberto Goyeneche AlfonsoAinda não há avaliações

- Final 1Documento20 páginasFinal 1Hans A-LeonAinda não há avaliações

- Informe Previo 2 - Circuitos Latch y Flip-FlopDocumento15 páginasInforme Previo 2 - Circuitos Latch y Flip-FlopLeo J Rojas RomeroAinda não há avaliações

- Contadores Asincrono1Documento3 páginasContadores Asincrono1Cesar Luis PoaquizaAinda não há avaliações

- Circuitos ContadoresDocumento26 páginasCircuitos ContadoresJoséM.PintoCarpioAinda não há avaliações

- FLIP FlopDocumento12 páginasFLIP Flopfishkdo100% (1)

- Cap1 Biestables - Villarreal (2 Diapositivas)Documento34 páginasCap1 Biestables - Villarreal (2 Diapositivas)KrOeGUeRAinda não há avaliações

- Diseño de ContadoresDocumento5 páginasDiseño de ContadoresOvanio MolinaAinda não há avaliações

- U01 - Logica SecuencialDocumento50 páginasU01 - Logica SecuencialYohanny Garcia SalazarAinda não há avaliações

- Cap1 Biestables - Villarreal (3 Diapositivas)Documento23 páginasCap1 Biestables - Villarreal (3 Diapositivas)Andrea Miluska Valer VilchezAinda não há avaliações

- MARCO TEORICO CONTADOR ASINCRONO Imprimir y BorrarDocumento11 páginasMARCO TEORICO CONTADOR ASINCRONO Imprimir y BorrarMartin CarbajalAinda não há avaliações

- Sistemas Digitales - 2° TareaDocumento27 páginasSistemas Digitales - 2° TareaCarlos Andrés67% (3)

- Informe Final 5Documento16 páginasInforme Final 5Julio David Vilca PizarroAinda não há avaliações

- Electrónica Digital: Diseño de Contador Con Flip-Flop Tipo JK y D Haciendo Del Uso de Mapa de KarnaughDocumento44 páginasElectrónica Digital: Diseño de Contador Con Flip-Flop Tipo JK y D Haciendo Del Uso de Mapa de Karnaughsantiago pablo albertoAinda não há avaliações

- Marco TeoricoDocumento20 páginasMarco TeoricoCarlos A. Pineda ChavarriaAinda não há avaliações

- Latch Flip FlopDocumento7 páginasLatch Flip FlopPipe CastilloAinda não há avaliações

- Ej Res 5Documento6 páginasEj Res 5Alfredo Freddy Guillermo Iglesias ZambranoAinda não há avaliações

- Entregable2 Plantilla 2022Documento9 páginasEntregable2 Plantilla 2022Eduardo GonzalezAinda não há avaliações

- Contador de 0-7Documento3 páginasContador de 0-7Jeison Orobio67% (3)

- AP Divisor de Frecuencia y Máquinas de EstadoDocumento8 páginasAP Divisor de Frecuencia y Máquinas de EstadoRonny AuccapiñaAinda não há avaliações

- Motor A Pasos ReporteDocumento13 páginasMotor A Pasos ReporteEmmanuel Migueles Perdomo100% (1)

- Previo Labo 1 Digitales 2Documento11 páginasPrevio Labo 1 Digitales 2Erick VillanuevaAinda não há avaliações

- Fundamentos de Lógica DigitalDocumento86 páginasFundamentos de Lógica DigitalTeago Pujar YevikoAinda não há avaliações

- Flip Flops D, J-K, y T.Documento14 páginasFlip Flops D, J-K, y T.AnaKarenHsAinda não há avaliações

- Sumativa N 3 Laborarrotio de Logica Digital Herms Chavez U.260621Documento18 páginasSumativa N 3 Laborarrotio de Logica Digital Herms Chavez U.260621Glenda Ureña de ChavezAinda não há avaliações

- Informe Previo (1 Laboratorio)Documento8 páginasInforme Previo (1 Laboratorio)Pedro CangalayaAinda não há avaliações

- Trabajo Colaborativo 2Documento12 páginasTrabajo Colaborativo 2Otto Ruefli100% (1)

- FlipflopsDocumento32 páginasFlipflopsCarlosRuizAinda não há avaliações

- Diseño de Contadores SincronosDocumento12 páginasDiseño de Contadores Sincronosorlando_heredia7934Ainda não há avaliações

- Semaforo WordDocumento4 páginasSemaforo WordAlexander Huaman JaimesAinda não há avaliações

- LAB 3 - CD2 - Registros y Transferencia Datos - 2018-1Documento4 páginasLAB 3 - CD2 - Registros y Transferencia Datos - 2018-1Raul Ñiquen LiñanAinda não há avaliações

- Pract 7Documento2 páginasPract 7xmnt2002Ainda não há avaliações

- Lab Flip FlopsDocumento3 páginasLab Flip FlopsmtrujillosAinda não há avaliações

- Tare ADocumento11 páginasTare AVictor DiazAinda não há avaliações

- Contador SincronoDocumento12 páginasContador SincronoJose Luis Tubon Condemaita100% (1)

- Resolución Del Examen ParcialDocumento9 páginasResolución Del Examen ParcialAlvaro Franco Tafur GutierrezAinda não há avaliações

- Cuatro Tipos de FlipFlopDocumento8 páginasCuatro Tipos de FlipFlopjuvelinAinda não há avaliações

- LAB 3 - Registros y Transferencia Datos - 2019-1Documento4 páginasLAB 3 - Registros y Transferencia Datos - 2019-1Aldair Bravo Yarleque100% (1)

- Sistemas Digitales Trabajo 4Documento34 páginasSistemas Digitales Trabajo 4福嶋満雄Ainda não há avaliações

- Capitulo Vi - Analisis y Sintesis de Circuitos Secuenciales SincronosDocumento72 páginasCapitulo Vi - Analisis y Sintesis de Circuitos Secuenciales Sincronosalex100% (1)

- Contador Asincrono AscendeneDocumento13 páginasContador Asincrono AscendeneAndiie RiveraAinda não há avaliações

- Contadores DigitalesDocumento9 páginasContadores DigitalesVega Sifuentes Edgar LuisAinda não há avaliações

- 1Documento15 páginas1Benjamin AlonsoAinda não há avaliações

- Control neuronal y difuso para sistemas fotovoltaicosNo EverandControl neuronal y difuso para sistemas fotovoltaicosAinda não há avaliações

- Derivas de complejidad: Aplicaciones y medicionesNo EverandDerivas de complejidad: Aplicaciones y medicionesAinda não há avaliações

- Introducción Al Psoc5Lp: Teoría y aplicaciones prácticaNo EverandIntroducción Al Psoc5Lp: Teoría y aplicaciones prácticaAinda não há avaliações

- 100 circuitos de shields para arduino (español)No Everand100 circuitos de shields para arduino (español)Nota: 3.5 de 5 estrelas3.5/5 (3)

- Revistaing Uniandes Edu coDpdfDrev5art1 PDFDocumento5 páginasRevistaing Uniandes Edu coDpdfDrev5art1 PDFRaúl Romero ÁvilaAinda não há avaliações

- Programación Básica en Ensamblador para Controladores PICDocumento2 páginasProgramación Básica en Ensamblador para Controladores PICJuan Carlos CamposAinda não há avaliações

- Construir GuitarraDocumento14 páginasConstruir GuitarraLopez Lopez Martin JhonyAinda não há avaliações

- Formulario de Precálculo (Matemáticas-KALASHNIKOV)Documento21 páginasFormulario de Precálculo (Matemáticas-KALASHNIKOV)Andrés Alfonso Hdez100% (1)

- Nomenclatura de Las Conexiones de Devanados en Transformadores TrifásicosDocumento5 páginasNomenclatura de Las Conexiones de Devanados en Transformadores Trifásicosbieito1968Ainda não há avaliações

- Tunel Proceso Constructivo Sin RocaDocumento5 páginasTunel Proceso Constructivo Sin RocaJuan CarlosAinda não há avaliações

- 20122sicq000188 2Documento22 páginas20122sicq000188 2edgar yadhir perez hernandezAinda não há avaliações

- Guia Ico PS2Documento8 páginasGuia Ico PS2luisortegarama_1Ainda não há avaliações

- Trabajo de Cualitativa Aniones Uno PDFDocumento12 páginasTrabajo de Cualitativa Aniones Uno PDFdanielAinda não há avaliações

- Basicos Haccp y Programas de Prerrequisitos PDFDocumento22 páginasBasicos Haccp y Programas de Prerrequisitos PDFRosie ReateguiAinda não há avaliações

- Respuesta A Solicitud Aclaracion Oferta ECONOMICADocumento10 páginasRespuesta A Solicitud Aclaracion Oferta ECONOMICAjuanjose92Ainda não há avaliações

- Las Placas Tectónicas Son Planchas Rígidas de Roca Sólida Que Conforman La Superficie de La TierraDocumento3 páginasLas Placas Tectónicas Son Planchas Rígidas de Roca Sólida Que Conforman La Superficie de La TierraMatias AravenaAinda não há avaliações

- Ecuaciones Diferenciales de Segundo Orden SISTEMA RESORTE-MASADocumento23 páginasEcuaciones Diferenciales de Segundo Orden SISTEMA RESORTE-MASAOliver58100% (2)

- Tubos Fluorecentes Ilumax PDFDocumento2 páginasTubos Fluorecentes Ilumax PDFJuan David Cardona SepulvedaAinda não há avaliações

- Taller 3. Gases Ideales PDFDocumento2 páginasTaller 3. Gases Ideales PDFGARCIA PEREZ ANDRES FELIPEAinda não há avaliações

- Clasificacion de LamparasDocumento7 páginasClasificacion de LamparasAldo MelchorAinda não há avaliações

- Proyecto de Semana 2 Curso 1Documento6 páginasProyecto de Semana 2 Curso 1fsp443140Ainda não há avaliações

- Importancia de Los Costos en La Toma deDocumento4 páginasImportancia de Los Costos en La Toma deCeledonio Hernandez SanchezAinda não há avaliações

- El Grado de Afectación Al Suelo Por La Actividad MineraDocumento13 páginasEl Grado de Afectación Al Suelo Por La Actividad MineraDaniel Mateo AyalaAinda não há avaliações

- Componentes de Un Sistema de ComputoDocumento2 páginasComponentes de Un Sistema de ComputoRudy BatenAinda não há avaliações

- Plan Remediacion LBDocumento38 páginasPlan Remediacion LBMarisabel MaidanaAinda não há avaliações

- Nom 091 SCTDocumento40 páginasNom 091 SCTrubiodegoAinda não há avaliações

- Unidad 2: Herramientas para La Solución de Problemas de GestiónDocumento84 páginasUnidad 2: Herramientas para La Solución de Problemas de GestiónMoises Rubio Silva100% (2)

- Memoria de CálculoDocumento17 páginasMemoria de Cálculosanty19870% (1)

- Clasificacion de Aceites AutomotricesDocumento8 páginasClasificacion de Aceites AutomotricesCharlie LtbAinda não há avaliações

- Esquemas Electricos InterruptoresDocumento6 páginasEsquemas Electricos InterruptoresavazquezseAinda não há avaliações

- Clasificación de Equipo Pesado MóvilDocumento36 páginasClasificación de Equipo Pesado MóvilCarlos Alfredo Laura100% (2)

- Plan de Negocios - LlanteriaDocumento2 páginasPlan de Negocios - LlanteriaPablo GuerraAinda não há avaliações

- Unidad 1. Respiración: Tema 1: Gases en El Aire Y en El Agua. Sistemas Respiratorios. Tipos de Sistemas RespiratoriosDocumento10 páginasUnidad 1. Respiración: Tema 1: Gases en El Aire Y en El Agua. Sistemas Respiratorios. Tipos de Sistemas RespiratoriosClara Muñoz PartidaAinda não há avaliações

- Procesos de Fabricación Reporte de PracticaDocumento11 páginasProcesos de Fabricación Reporte de Practicaomar gaimAinda não há avaliações

- ¿Tubería PVC Expuesta o en Cielos Falsos¿Documento12 páginas¿Tubería PVC Expuesta o en Cielos Falsos¿David MorenoAinda não há avaliações