Escolar Documentos

Profissional Documentos

Cultura Documentos

Design & Characterization of High Speed Power Efficient Cmos Comparator

Enviado por

IAEME PublicationDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Design & Characterization of High Speed Power Efficient Cmos Comparator

Enviado por

IAEME PublicationDireitos autorais:

Formatos disponíveis

COMMUNICATION ENGINEERING & TECHNOLOGY (IJECET)

ISSN 0976 6464(Print) ISSN 0976 6472(Online) Volume 4, Issue 3, May June, 2013, pp. 24-32 IAEME: www.iaeme.com/ijecet.asp Journal Impact Factor (2013): 5.8896 (Calculated by GISI) www.jifactor.com

International Journal of Electronics and Communication Engineering & Technology (IJECET), INTERNATIONAL JOURNAL OF ELECTRONICS AND ISSN 0976 6464(Print), ISSN 0976 6472(Online) Volume 4, Issue 3, May June (2013), IAEME

IJECET

IAEME

DESIGN & CHARACTERIZATION OF HIGH SPEED POWER EFFICIENT CMOS COMPARATOR

Priyesh P. Gandhi1, Dhanisha N. Kapadia2, N. M. Devashrayee3

2

(EC Dept., Institute of Technology, Nirma University, Ahmedabad, India) (EC Dept., L. C. Institute of Technology, Bhandu, Gujarat Technological University Ahmedabad, India) 3 (EC Dept., Institute of Technology, Nirma University, Ahmedabad, India)

ABSTRACT In this paper authors have design the High Speed Power Efficient CMOS Voltage Comparator which can be realized in A/D Converters. The simulation is carried out in 130nm and 90nm technologies. The supply voltage for this comparator is 1v and 0.9v for 130nm and 90nm respectively. The Characterization of comparator is done in terms of offset, ICMR, propagation delay, power dissipation in both the technologies and the result has been compared for both the technologies. The simulation results shows that the speed of 1.92GHz and 2.44GHz with the power dissipation of 9.19W and 7.45W was achieved in 130nm and 90nm technologies respectively. Index Terms: Buffer stage, Current Sensing Comparator, Latch Comparator. I. INTRODUCTION A Comparator is a circuit which compares the two analog signal and depending on the comparison gives the output either logic 1 or logic 0. The comparators are widely used in ADC. In fact, comparator is also called as 1 bit ADC. In conventional design, in order to reduce the input offset voltage preamplifiers were added before the comparator, but ultimately this increases the power consumption. Therefore, a latched comparator is a good alternative for low power consumption and high-speed operation. There are three types of comparator which can provide high speed, such as multistage open loop comparator, the dynamic latch comparator, and the preamplifier-latch comparator. The multistage open loop

24

International Journal of Electronics and Communication Engineering & Technology (IJECET), ISSN 0976 6464(Print), ISSN 0976 6472(Online) Volume 4, Issue 3, May June (2013), IAEME

comparator can meet high-speed and high-precision, but cannot provide the speed more than 1Gbps, so the dynamic latch comparator is widely utilized to satisfy the need for high-speed. The paper is being divided into six sections. In section 2, current sensing comparator topology and the buffer stage have been discussed. In section 3, authors have discussed about proposed architecture of comparator. In section 4, simulation results are presented. Section 5 includes the comparison of the simulation results in both the technologies. Finally in section 6, conclusion has been discussed. II. DIFFERENTIAL CURRENT SENSING COMPARATOR AND BUFFER STAGE A. Differential Current Sensing Comparator

Fig. 1. Differential current sensing comparator[3] Figure-1 shows the schematic of the differential current sensing comparator. Whenever the Clk signal goes low, circuit enters in regenerative mode. Transistor M12 is on and M7 is off. Both nMOS M5 and M6 will start conducting when values of both the outputs Out+ and Out- increases above threshold voltage of both transistors, which will connect the outputs with comparing circuit at the input side. Unless and until final state is reached both the outputs have to drive common mode currents, hence it consumes more power. When the CLK signal goes high, the circuit enters in reset mode. The comparing circuit used at the input side consisting of transistors M1, M2, M3 and M4 are used to transfer the difference of the input voltage into differential currents. A pass transistor M7 is used to connect both the outputs together. B. Buffer Stage The circuit diagram of output buffer circuit used in the comparator is shown in Figure-2[4]. The output buffer stage is also called post amplifier. This circuit is self biasing differential amplifier which has differential inputs as Vout+ & Vout- and does not have any slew rate limitations. It is also useful in giving the output in proper shape.

25

International Journal of Electronics and Communication Engineering & Technology (IJECET), ISSN 0976 6464(Print), ISSN 0976 6472(Online) Volume 4, Issue 3, May June (2013), IAEME

Fig.2 The Output Buffer Circuit[4] III. PROPOSED CMOS VOLTAGE COMPARATOR The circuit diagram of the proposed high speed CMOS voltage comparator is as shown in Figure-3. Whenever the Clk signal goes high, the circuit enters in regenerative mode. Transistor M11 and M7 are off and M14 is on. When values of both the outputs Out+ and Out- increases above threshold voltage of nMOS M5 and M6, both will start conducting which will connect the outputs with comparing circuit at the input side. The comparing circuit used at the input side consisting of transistors M1, M2, M3 and M4 are used to transfer the difference of the input voltage into differential currents. During reset interval, a pass transistor M11 is used to connect both the outputs together. Whenever the Clk signal goes low, transistor M7 and M8 are on. The two nodes which are connected with the drains of M7 and M8 will get reset to Vdd. These internal nodes are reset to Vdd during the phase when the comparator is not making a decision. This will ensure that all the internal nodes are reset before the comparator goes into decision mode. So the problem associated with previous code dependent biased decision which occurs due to the charge imbalance left from previous decision at one of the nodes of the comparator which affects next decision is thus removed. The two outputs Out+ and Out- of the comparator are being converted into single output with the output buffer circuit so that various analysis can be carried out. Table-I given below shows different widths of the transistor to be used according to the chosen technology. The length for the transistor is 0.13um and 0.1um respectively for 130nm and 90nm technology.

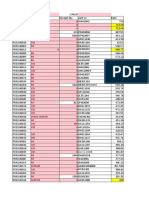

TABLE-1. CMOS TRANSISTOR WIDTHS FOR DIFFERENT TECHNOLOGIES Technology 130nm 90nm Wp(um) Wn(um) 0.15 0.12 0.15 0.12

26

International Journal of Electronics and Communication Engineering & Technology (IJECET), ISSN 0976 6464(Print), ISSN 0976 6472(Online) Volume 4, Issue 3, May June (2013), IAEME

Fig.3 Proposed Design of Comparator IV. SIMULATION RESULTS OF PROPOSED COMPARATOR The simulated results are obtained for two different technologies 130nm and 90nm. In Table-II, different voltage values are given for supply voltage VDD and VSS, reference voltage Vref+ and Vref-, input voltage Vin+ and Vin- and Clkb TABLE-II DIFFERENT VOLTAGE VALUES FOR DIFFERENT TECHNOLOGIES Voltage Terminals VDD VSS Clkb Vin+ VinVref+ VrefTechnology 130nm 90nm 1v 0.9v -1v -0.9v -1v -0.9v 1v 0.9v -1v -0.9v 0.43v 0.34v -0.43v -0.34v

When sine wave is applied to the comparator as an input, the output will be the square wave as shown in Figure-5 and Figure-9.

27

International Journal of Electronics and Communication Engineering & Technology (IJECET), ISSN 0976 6464(Print), ISSN 0976 6472(Online) Volume 4, Issue 3, May June (2013), IAEME

A. Simulated waveforms in 130nm technology

Fig. 5 Sine Wave as an Input

Fig. 6 Transient Response

28

International Journal of Electronics and Communication Engineering & Technology (IJECET), ISSN 0976 6464(Print), ISSN 0976 6472(Online) Volume 4, Issue 3, May June (2013), IAEME

Fig. 7 Input Common Mode Range

Fig 8 Output Offset voltage

29

International Journal of Electronics and Communication Engineering & Technology (IJECET), ISSN 0976 6464(Print), ISSN 0976 6472(Online) Volume 4, Issue 3, May June (2013), IAEME

B. Simulated waveforms in 90nm technology

Fig. 9 Sine Wave as an Input

Fig. 10 Transient Response

30

International Journal of Electronics and Communication Engineering & Technology (IJECET), ISSN 0976 6464(Print), ISSN 0976 6472(Online) Volume 4, Issue 3, May June (2013), IAEME

Fig. 11 Input Common Mode Range

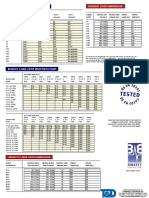

Fig.12 Output Offset Voltage V. COMPARISON OF DIFFERENT CHARACTERISTICS IN 130NM AND 90NM TECHNOLOGIES In this paper, simulated results are presented for the comparator for two different technologies, 130nm and 90nm. The summary of the comparison for the comparator in both the technologies is given in the Table III.

31

International Journal of Electronics and Communication Engineering & Technology (IJECET), ISSN 0976 6464(Print), ISSN 0976 6472(Online) Volume 4, Issue 3, May June (2013), IAEME

TABLE III SIMULATED RESULTS OF CURRENT SENSING COMPARATOR WITH BUFFER CIRCUIT FOR DIFFERENT TECHNOLOGIES Parameters Propagation Delay(ns) Speed(GHz) ICMR(V) Offset Power Dissipation(uW) VI. CONCLUSION Speed of the comparator which is implemented in 90nm is more than speed of comparator in 130nm. The input common mode range is almost remaining same for both the technologies. With the reduction in technology, the offset voltage is getting increased due to increase in the non-idealities of the transistors and the power dissipation is also reduced with the reduction in the technology. Proposed Comparator has high speed which can be realized in A/D Converters. REFERENCES [1] P. Uthaichana and E. Leelarasmee, "Low Power CMOS Dynamic Latch Comparators," IEEE, pp. 605-608, 2003. [2] Z. Huang and P. Zhong, "An Adaptive Analog-to-Digital Converter Based on Low-Power Dynamic Latch Comparator," IEEE conference, p. 6pp, 2005. [3] Christopher J. Lindsley A Nano-Power Wake-Up Circuit for RF Energy Harvesting Wireless Sensor Networks , M.S. thesis, Dept. Electrical & computer. Eng., Oregon State University 2008. [4] Priyesh P. Gandhi Design & Simulation of Low Power High Speed CMOS Comparator in Deep Sub-micron Technology, M.Tech thesis, Dept. of electronics & communication Eng. Nirma University, 2010. [5] Philip E. Allen and Douglas R. Hallberg. CMOS Analog Circuit Design. Oxford University Press, Inc USA-2002,pp.259-397, 2002 [6] R. Jacob Baker Harry W. Li David E. Boyce. CMOS Circuit Design, Layout and Simulation. IEEE Press Series on Microelectronics Systems, 2005. [7] Dhanisha N. Kapadia and Priyesh P. Gandhi, Design and Simulation of High Speed CMOS Differential Current Sensing Comparator in 0.35 m and 0.25m 1 Technologies, International journal of Electronics and Communication Engineering &Technology (IJECET), Volume 3, Issue 3, 2012, pp. 147 - 152, ISSN Print: 0976- 6464, ISSN Online: 0976 6472. [8] Rajinder Tiwari and R K Singh, An Optimized High Speed Dual Mode CMOS Differential Amplifier for Analog VLSI applications, International Journal of Electrical Engineering & Technology (IJEET), Volume 3, Issue 1, 2012, pp. 180 - 187, ISSN Print : 0976-6545, ISSN Online: 0976-6553. Technology 130nm 90nm 0.46 0.34 2.17 2.94 -0.2 to 0.61 -0.2 to 0.5 69mV 0.16 21 10.22

32

Você também pode gostar

- Impact of Emotional Intelligence On Human Resource Management Practices Among The Remote Working It EmployeesDocumento10 páginasImpact of Emotional Intelligence On Human Resource Management Practices Among The Remote Working It EmployeesIAEME PublicationAinda não há avaliações

- A Study On The Reasons For Transgender To Become EntrepreneursDocumento7 páginasA Study On The Reasons For Transgender To Become EntrepreneursIAEME PublicationAinda não há avaliações

- Broad Unexposed Skills of Transgender EntrepreneursDocumento8 páginasBroad Unexposed Skills of Transgender EntrepreneursIAEME PublicationAinda não há avaliações

- Analyse The User Predilection On Gpay and Phonepe For Digital TransactionsDocumento7 páginasAnalyse The User Predilection On Gpay and Phonepe For Digital TransactionsIAEME PublicationAinda não há avaliações

- Modeling and Analysis of Surface Roughness and White Later Thickness in Wire-Electric Discharge Turning Process Through Response Surface MethodologyDocumento14 páginasModeling and Analysis of Surface Roughness and White Later Thickness in Wire-Electric Discharge Turning Process Through Response Surface MethodologyIAEME PublicationAinda não há avaliações

- Determinants Affecting The User's Intention To Use Mobile Banking ApplicationsDocumento8 páginasDeterminants Affecting The User's Intention To Use Mobile Banking ApplicationsIAEME PublicationAinda não há avaliações

- Attrition in The It Industry During Covid-19 Pandemic: Linking Emotional Intelligence and Talent Management ProcessesDocumento15 páginasAttrition in The It Industry During Covid-19 Pandemic: Linking Emotional Intelligence and Talent Management ProcessesIAEME PublicationAinda não há avaliações

- Gandhi On Non-Violent PoliceDocumento8 páginasGandhi On Non-Violent PoliceIAEME PublicationAinda não há avaliações

- Voice Based Atm For Visually Impaired Using ArduinoDocumento7 páginasVoice Based Atm For Visually Impaired Using ArduinoIAEME PublicationAinda não há avaliações

- Influence of Talent Management Practices On Organizational Performance A Study With Reference To It Sector in ChennaiDocumento16 páginasInfluence of Talent Management Practices On Organizational Performance A Study With Reference To It Sector in ChennaiIAEME PublicationAinda não há avaliações

- A Study On The Impact of Organizational Culture On The Effectiveness of Performance Management Systems in Healthcare Organizations at ThanjavurDocumento7 páginasA Study On The Impact of Organizational Culture On The Effectiveness of Performance Management Systems in Healthcare Organizations at ThanjavurIAEME PublicationAinda não há avaliações

- Financial Literacy On Investment Performance: The Mediating Effect of Big-Five Personality Traits ModelDocumento9 páginasFinancial Literacy On Investment Performance: The Mediating Effect of Big-Five Personality Traits ModelIAEME PublicationAinda não há avaliações

- Visualising Aging Parents & Their Close Carers Life Journey in Aging EconomyDocumento4 páginasVisualising Aging Parents & Their Close Carers Life Journey in Aging EconomyIAEME PublicationAinda não há avaliações

- A Study of Various Types of Loans of Selected Public and Private Sector Banks With Reference To Npa in State HaryanaDocumento9 páginasA Study of Various Types of Loans of Selected Public and Private Sector Banks With Reference To Npa in State HaryanaIAEME PublicationAinda não há avaliações

- A Proficient Minimum-Routine Reliable Recovery Line Accumulation Scheme For Non-Deterministic Mobile Distributed FrameworksDocumento10 páginasA Proficient Minimum-Routine Reliable Recovery Line Accumulation Scheme For Non-Deterministic Mobile Distributed FrameworksIAEME PublicationAinda não há avaliações

- Role of Social Entrepreneurship in Rural Development of India - Problems and ChallengesDocumento18 páginasRole of Social Entrepreneurship in Rural Development of India - Problems and ChallengesIAEME PublicationAinda não há avaliações

- A Study On Talent Management and Its Impact On Employee Retention in Selected It Organizations in ChennaiDocumento16 páginasA Study On Talent Management and Its Impact On Employee Retention in Selected It Organizations in ChennaiIAEME PublicationAinda não há avaliações

- Application of Frugal Approach For Productivity Improvement - A Case Study of Mahindra and Mahindra LTDDocumento19 páginasApplication of Frugal Approach For Productivity Improvement - A Case Study of Mahindra and Mahindra LTDIAEME PublicationAinda não há avaliações

- Various Fuzzy Numbers and Their Various Ranking ApproachesDocumento10 páginasVarious Fuzzy Numbers and Their Various Ranking ApproachesIAEME PublicationAinda não há avaliações

- A Multiple - Channel Queuing Models On Fuzzy EnvironmentDocumento13 páginasA Multiple - Channel Queuing Models On Fuzzy EnvironmentIAEME PublicationAinda não há avaliações

- Dealing With Recurrent Terminates in Orchestrated Reliable Recovery Line Accumulation Algorithms For Faulttolerant Mobile Distributed SystemsDocumento8 páginasDealing With Recurrent Terminates in Orchestrated Reliable Recovery Line Accumulation Algorithms For Faulttolerant Mobile Distributed SystemsIAEME PublicationAinda não há avaliações

- Analysis of Fuzzy Inference System Based Interline Power Flow Controller For Power System With Wind Energy Conversion System During Faulted ConditionsDocumento13 páginasAnalysis of Fuzzy Inference System Based Interline Power Flow Controller For Power System With Wind Energy Conversion System During Faulted ConditionsIAEME PublicationAinda não há avaliações

- Knowledge Self-Efficacy and Research Collaboration Towards Knowledge Sharing: The Moderating Effect of Employee CommitmentDocumento8 páginasKnowledge Self-Efficacy and Research Collaboration Towards Knowledge Sharing: The Moderating Effect of Employee CommitmentIAEME PublicationAinda não há avaliações

- EXPERIMENTAL STUDY OF MECHANICAL AND TRIBOLOGICAL RELATION OF NYLON/BaSO4 POLYMER COMPOSITESDocumento9 páginasEXPERIMENTAL STUDY OF MECHANICAL AND TRIBOLOGICAL RELATION OF NYLON/BaSO4 POLYMER COMPOSITESIAEME PublicationAinda não há avaliações

- Optimal Reconfiguration of Power Distribution Radial Network Using Hybrid Meta-Heuristic AlgorithmsDocumento13 páginasOptimal Reconfiguration of Power Distribution Radial Network Using Hybrid Meta-Heuristic AlgorithmsIAEME PublicationAinda não há avaliações

- Quality of Work-Life On Employee Retention and Job Satisfaction: The Moderating Role of Job PerformanceDocumento7 páginasQuality of Work-Life On Employee Retention and Job Satisfaction: The Moderating Role of Job PerformanceIAEME PublicationAinda não há avaliações

- Moderating Effect of Job Satisfaction On Turnover Intention and Stress Burnout Among Employees in The Information Technology SectorDocumento7 páginasModerating Effect of Job Satisfaction On Turnover Intention and Stress Burnout Among Employees in The Information Technology SectorIAEME PublicationAinda não há avaliações

- Analysis On Machine Cell Recognition and Detaching From Neural SystemsDocumento9 páginasAnalysis On Machine Cell Recognition and Detaching From Neural SystemsIAEME PublicationAinda não há avaliações

- Prediction of Average Total Project Duration Using Artificial Neural Networks, Fuzzy Logic, and Regression ModelsDocumento13 páginasPrediction of Average Total Project Duration Using Artificial Neural Networks, Fuzzy Logic, and Regression ModelsIAEME PublicationAinda não há avaliações

- A Review of Particle Swarm Optimization (Pso) AlgorithmDocumento26 páginasA Review of Particle Swarm Optimization (Pso) AlgorithmIAEME PublicationAinda não há avaliações

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNo EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNota: 4 de 5 estrelas4/5 (5794)

- The Yellow House: A Memoir (2019 National Book Award Winner)No EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Nota: 4 de 5 estrelas4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNo EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNota: 4 de 5 estrelas4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNo EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNota: 4.5 de 5 estrelas4.5/5 (344)

- The Little Book of Hygge: Danish Secrets to Happy LivingNo EverandThe Little Book of Hygge: Danish Secrets to Happy LivingNota: 3.5 de 5 estrelas3.5/5 (399)

- The Emperor of All Maladies: A Biography of CancerNo EverandThe Emperor of All Maladies: A Biography of CancerNota: 4.5 de 5 estrelas4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNo EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNota: 4.5 de 5 estrelas4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItNo EverandNever Split the Difference: Negotiating As If Your Life Depended On ItNota: 4.5 de 5 estrelas4.5/5 (838)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNo EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNota: 3.5 de 5 estrelas3.5/5 (231)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNo EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNota: 4.5 de 5 estrelas4.5/5 (474)

- Team of Rivals: The Political Genius of Abraham LincolnNo EverandTeam of Rivals: The Political Genius of Abraham LincolnNota: 4.5 de 5 estrelas4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyNo EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyNota: 3.5 de 5 estrelas3.5/5 (2259)

- The Unwinding: An Inner History of the New AmericaNo EverandThe Unwinding: An Inner History of the New AmericaNota: 4 de 5 estrelas4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNo EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNota: 4 de 5 estrelas4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)No EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Nota: 4.5 de 5 estrelas4.5/5 (120)

- Remote Controlled Obstacle Detection Robot: Submitted by Mr.P.Ramesh Naidu 1165008Documento7 páginasRemote Controlled Obstacle Detection Robot: Submitted by Mr.P.Ramesh Naidu 1165008Pasam RameshAinda não há avaliações

- Very Low Dropout 3.0 Amp Regulator With Enable: Power Management Features DescriptionDocumento10 páginasVery Low Dropout 3.0 Amp Regulator With Enable: Power Management Features DescriptionmitusharmaAinda não há avaliações

- Basic Sentence PatternsDocumento21 páginasBasic Sentence PatternsSarah NasihahAinda não há avaliações

- System Protection Chapter 2Documento19 páginasSystem Protection Chapter 2Almiqdad AldeekAinda não há avaliações

- Design of Induction Heating Coils For Cylindrical Magnetic LoadsDocumento6 páginasDesign of Induction Heating Coils For Cylindrical Magnetic LoadsAlee LópezAinda não há avaliações

- Cairo Mini 3d-Printer Parts ListDocumento9 páginasCairo Mini 3d-Printer Parts ListAliAinda não há avaliações

- Difference Between BJT and FETDocumento2 páginasDifference Between BJT and FETkanwaljiaAinda não há avaliações

- E700 WiringDocumento3 páginasE700 WiringTrần HoàngAinda não há avaliações

- Ft-Oct 22 FinalDocumento79 páginasFt-Oct 22 FinalOmkar Balasaheb MetkariAinda não há avaliações

- Process Automation Factory Automation Terminal AutomationDocumento4 páginasProcess Automation Factory Automation Terminal AutomationRitaban R. BanerjeeAinda não há avaliações

- Matlab Simulink Model of Sinusoidal PWM For Three-Phase Voltage Source InverterDocumento3 páginasMatlab Simulink Model of Sinusoidal PWM For Three-Phase Voltage Source InverterEditor IJTSRDAinda não há avaliações

- LNK562 564Documento16 páginasLNK562 564oscar herediaAinda não há avaliações

- Manual Interfase ESAB DigipulseDocumento32 páginasManual Interfase ESAB DigipulseJohan Zraghoz100% (1)

- Datasheet lf356 PDFDocumento23 páginasDatasheet lf356 PDFAlberto Chica CardenasAinda não há avaliações

- Network AnalysisDocumento2 páginasNetwork AnalysisPandit SumitAinda não há avaliações

- Submittal For Al Barsha 363 Rev0 PDFDocumento54 páginasSubmittal For Al Barsha 363 Rev0 PDFGokulAinda não há avaliações

- Technical Note MD MODBUS Protocol Rev23eDocumento7 páginasTechnical Note MD MODBUS Protocol Rev23eMallampati RamakrishnaAinda não há avaliações

- Conventional Current Flow Vs Electron Current FlowDocumento8 páginasConventional Current Flow Vs Electron Current FlowNels OdrajafAinda não há avaliações

- Review of Reactive Power Compensation TechnologiesDocumento79 páginasReview of Reactive Power Compensation TechnologiesRadu BabauAinda não há avaliações

- Cat. Vickers - Válvulas KBCG3Documento12 páginasCat. Vickers - Válvulas KBCG3Elcio AzevedoAinda não há avaliações

- About This ProjectDocumento2 páginasAbout This ProjectMr. ThopeAinda não há avaliações

- VdivDocumento12 páginasVdivmehralsmenschAinda não há avaliações

- 컨베어속도조절 가변저항 - VR-RV24YN+20S (B103) PDFDocumento7 páginas컨베어속도조절 가변저항 - VR-RV24YN+20S (B103) PDF박상길Ainda não há avaliações

- Service Manual: Viewsonic Vt2230-1MDocumento90 páginasService Manual: Viewsonic Vt2230-1MDaniboy1994Ainda não há avaliações

- Birkett Cable Joints PDFDocumento2 páginasBirkett Cable Joints PDFtobyAinda não há avaliações

- Elmeasure Transducer TR Programming GuideDocumento2 páginasElmeasure Transducer TR Programming GuideVinay KrishnaAinda não há avaliações

- Circuit Theory Notes PDFDocumento147 páginasCircuit Theory Notes PDFSaNdeepAinda não há avaliações

- 7.5w Audio AmplifierDocumento1 página7.5w Audio AmplifierSowjanya DaliparthiAinda não há avaliações

- Electronics - and - Telecommunications - Noise, F R CONNOR PDFDocumento143 páginasElectronics - and - Telecommunications - Noise, F R CONNOR PDFAjay VarmaAinda não há avaliações

- Ets-05-Xx-A: Surface Sensing Electronic ThermostatDocumento4 páginasEts-05-Xx-A: Surface Sensing Electronic ThermostatRajkumar KhaseraoAinda não há avaliações