Escolar Documentos

Profissional Documentos

Cultura Documentos

825482C54

Enviado por

Anonymous lubWipsrWDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

825482C54

Enviado por

Anonymous lubWipsrWDireitos autorais:

Formatos disponíveis

8254/82C54: Introduction to Programmable<BR> Interval Timer

Page 1 of 4

8254/82C54: Introduction to Programmable Interval Timer

WHY IS THE DEVICE NEEDED?

It generates accurate time delays under software control. Instead of setting up timing loops in software, the programmer configures the interval timer to match system requirements and programs the counter for the desired delay or for the desired output. Some common timer/counter/output functions which microprocessors require are: real time clock, event counter, digital one-shot, programmable rate generator, square wave generator, binary rate multiplier, complex wave form generator, and complex motor control.

HOW DOES IT WORK?

BASIC OPERATION: 1. The user inputs a control word and then an initial count. The Control Word itself specifies which Counter is being programmed and which counting Mode is desired. 2. Counting is enabled via the GATE input. 3. Either at the end of a count or during the count, transitions occur on the Counter OUT pin. 4. These OUT pin transitions are used to do things in the system. 5. The types of OUT pin transitions depend on the Mode which was programmed.

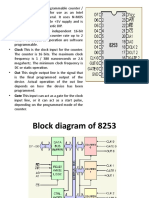

MAJOR DEVICE BLOCKS:

DATA BUS BUFFER: 1. 3-state, bi-directional, 8-bit buffer. 2. Interfaces the 8254 to the system bus. READ/WRITE LOGIC BLOCK: 1. the Read/Write Logic Block accepts inputs from the system bus and generates control signals for the other functional blocks of the 8254. 2. A1 and A0 select one of the three counters or the Control Word Register to be read from or written into. 3. A low on RD# tells the 8254 that the CPU is reading one of the counters. 4. A low on WR# tells the 8254 that the CPU is writing either a Control Word or an initial count. 5. Both RD# and WR# are qualified by CS#. CONTROL WORD REGISTER: 1. This register is selected by the Read/Write Logic when A1,A0=11. 2. If the CPU then does a write operation to the 8254, the data is stored in the Control Word Register and is interpreted as a Control Word used to define the operation of the counters. 3. The Control Word Register can only be written to. Status information is available with the Read-Back command. COUNTERS: 1. There are three Counters. Each is fully independent of the others. Each Counter may operate in a different Mode. 2. Each counter is a 16-bit synchronous down counter.

file://F:\Backup Old Hdds\DpFun\Utile\PROBL\DPNT\7203.HTM

6/1/2013

8254/82C54: Introduction to Programmable<BR> Interval Timer

Page 2 of 4

3. After power-up, the count value and output of all Counters are undefined. 4. Each counter must be programmed before it can be used. 5. Unused counters need not be programmed. 6. Counters are programmed by writing a Control Word and then an initial count. 7. GATE=1 enables counting, GATE=0 disables counting.

COUNTER DESCRIPTION:

COUNTING ELEMENT, OLm, OLl, OL: 1. The actual Counter is "CE" in figure 5. 2. OLm and OLl are two 8-bit latches. OL is "Output Latch" The subscripts m and l stand for "Most significant byte" and "Least significant byte". Both are normally referred to as one unit and called just OL. These latches "follow" the CE as it counts. 3. If a suitable Counter Latch Command is sent to the 8254, the latches capture the present count until read by the CPU. Once read, the latches return to "following" the CE. 4. One latch at a time is enabled by the counter's control logic to drive the internal bus. This is how the 16bit counter communicates over the 8-bit bus. 5. The CE itself cannot be read. If the user wants to read the count, it is the OL that is being read. CE, CRm, CRl, CR: 1. There are two 8-bit registers called CRm and CRl. These are the Count Register (Most significant byte and Least significant byte.) Both are normally just called the CR. 2. When a new count is written to the counter, the count is stored in the CR and later transferred to the CE. 3. The Control Logic allows one register at a time to be loaded from the internal bus. 4. Both bytes are transferred to the CE simultaneously. 5. CRm and CRl cleared when the Counter is programmed so that if the Counter has been programmed for one byte counts (either lsb or msb only) the other byte will be zero. 6. Note that the CE cannot be written into; whenever a count is written, it is written into the CR.

PROGRAMMING THE 8254:

1. Counters are programmed by writing a Control Word and then an initial count. 2. Control Words are written into the Control Word Register, which is selected when A0,A1=11. The Control Word itself specifies which Counter is being programmed. 3. Initial counts are written into the Counters, not the Control Word Register. The A0,A1 inputs are used to select the Counter to be written into. 4. The format of the initial count is determined by the Control Word used.

WRITE OPERATIONS:

There are two conventions for writing to the 8254: 1. For each Counter, the Control Word must be written before the initial count is written. 2. The initial count must follow the count format specified in the Control Word (lsb only, msb only, or lsb then msb). A new initial count may be written to a Counter at any time without affecting the Counter's programmed Mode in any way. However, the actual counting in the Counter will be affected as described in the various Mode definitions.

READ OPERATIONS:

The value of a Counter can be read by any one of the following three methods: 1. A simple READ operation: a. Select the Counter with the A1,A0 inputs. b. Inhibit the CLK of the selected counter by using either the GATE input or external logic. (The CLK must be inhibited or the count may be in the process of changing when it is read, giving an undefined result.)

file://F:\Backup Old Hdds\DpFun\Utile\PROBL\DPNT\7203.HTM

6/1/2013

8254/82C54: Introduction to Programmable<BR> Interval Timer

Page 3 of 4

c. Note that stopping the CLK stops the count. 2. Counter Latch Command (does not disturb the count in progress): a. It is written to the Control Word Register like a Control Word, but two bits (D5,D4) distinguish this command from a Control Word. b. The selected Counter's OL latches the count at the time the Counter Latch Command is received. c. The count is held in the latch until it is read by the CPU. d. The count is then unlatched automatically and the OL returns to "following" the CE. 3. Read-Back Command: a. This command allows the user to check the count value, programmed Mode, and current states of the OUT pin and Null Count flag of the selected counter(s). b. This command is similar to several Counter Latch Commands, one for each counter latched.

MODE DEFINITIONS:

CLK PULSE: a rising edge, then a falling edge, in that order, of a Counter's CLK input. Trigger: a rising edge of a Counters GATE input. Counter loading: the transfer of a count from the CR to the CE. MODE 0: INTERRUPT ON TERMINAL COUNT 1. Event counting. 2. After the Control Word is written, OUT is initially low and remains low. 3. When the counter reaches zero. OUT then goes high and remains high until a new count or a new Mode 0 Control Word is written into the Counter. MODE 1: HARDWARE RETRIGGERABLE ONE-SHOT 1. OUT will be initially high. OUT will go low on the CLK pulse following a trigger to begin the one-shot pulse, and remain low until the Counter reaches zero. 2. OUT will then go high and remain high until the CLK pulse after the next trigger. MODE 2: RATE GENERATOR 1. Functions like a divide-by-N counter and used to generate a Real Time Clock interrupt. 2. OUT will initially be high. 3. When the initial count has decremented to one, OUT goes low for one CLK pulse. 4. Out then goes high again, the Counter reloads the initial count and the process is repeated. 5. MODE 2 is periodic. The same sequence is repeated indefinitely. MODE 3: SQUARE WAVE MODE 1. Typically used for baud rate generation. 2. Out will initially be high. 3. When half the initial count is expired, OUT goes low for the remainder of the count. 4. MODE 3 is periodic. The same sequence is repeated indefinitely. MODE 4: SOFTWARE TRIGGERED STROBE 1. OUT will initially be high. 2. When the initial count expires, OUT will go low for one CLK pulse and then go high again. 3. The counting sequence is "triggered" by writing the initial count. 4. The Counter is loaded on the next CLK pulse following writing a Control Word and initial count. MODE 5: HARDWARE TRIGGERED STROBE (RETRIGGERABLE) 1. OUT will initially be high. 2. Counting is triggered by a rising edge of GATE. 3. When the initial count expires, OUT will go low for one CLK pulse and then go high again. 4. The difference between MODE 4 and MODE 5 is that in MODE 5 the count will not be loaded until the CLK pulse after a trigger.

file://F:\Backup Old Hdds\DpFun\Utile\PROBL\DPNT\7203.HTM

6/1/2013

8254/82C54: Introduction to Programmable<BR> Interval Timer

Page 4 of 4

OPERATION COMMON TO ALL MODES:

1. When a Control Word is written to a Counter, all Control Logic is immediately reset and OUT goes to the initial state. It does not take a CLK transition to do this. 2. The GATE input is always sampled on the rising edge of CLK 3. In some MODES the GATE input is level sensitive and some are rising-edge sensitive. In some MODES the GATE input is both edge and level sensitive. 4. New counts are loaded and Counters are decremented on the falling edge of CLK. 5. The largest possible initial count is zero. This is equivalent to 2^16 binary and 10^4 BCD. 6. The Counter does not stop when it reaches zero. In MODES 0, 1, 4, and 5 the Counter wraps around to the highest count (FFFFh or 9999bcd) and continues counting. In MODES 2 and 3 (which are periodic) the Counter reloads itself with the initial count and continues counting from there.

* Legal Information and Privacy Policy 2001 Intel Corporation

file://F:\Backup Old Hdds\DpFun\Utile\PROBL\DPNT\7203.HTM

6/1/2013

Você também pode gostar

- Direct Memory AccessDocumento6 páginasDirect Memory AccessPratik SandilyaAinda não há avaliações

- 6.timer 8254Documento15 páginas6.timer 8254Akram TahaAinda não há avaliações

- 82C54 Programmable Interval Timer: Microprocessors ApplicationsDocumento18 páginas82C54 Programmable Interval Timer: Microprocessors ApplicationsAliAinda não há avaliações

- The 8253Documento29 páginasThe 8253Soumya Ranjan PandaAinda não há avaliações

- By K. Vijay Kumar Assistant Professor Dept. of ECEDocumento31 páginasBy K. Vijay Kumar Assistant Professor Dept. of ECEsignjpcoeAinda não há avaliações

- 8254 Programmable Interval TimerDocumento4 páginas8254 Programmable Interval Timerapi-26100966100% (1)

- Unit III 8254Documento29 páginasUnit III 8254Sahil SinghAinda não há avaliações

- 8254 ModesDocumento39 páginas8254 ModesVamsi KrishnaAinda não há avaliações

- Programmable Interval Timer.Documento68 páginasProgrammable Interval Timer.BETHWEL KIPROTICH100% (1)

- 8253Documento17 páginas8253Parv SharmaAinda não há avaliações

- 8254 Micro ProcessorDocumento16 páginas8254 Micro Processornishukaushal100% (2)

- 8253 54-1Documento14 páginas8253 54-1crsarinAinda não há avaliações

- Segment 7: Rogrammable Nterval ImerDocumento36 páginasSegment 7: Rogrammable Nterval ImerDOUNIAAinda não há avaliações

- Programmable Interval Timer - 8254Documento35 páginasProgrammable Interval Timer - 8254Arnav BansalAinda não há avaliações

- Mod 4 Note 2Documento33 páginasMod 4 Note 2Arya ChandranAinda não há avaliações

- 8254 TimerDocumento9 páginas8254 TimerHarisankar R N R 21BRS1524Ainda não há avaliações

- MicroprocessorDocumento23 páginasMicroprocessorSahilPrabhakarAinda não há avaliações

- The 8253 Data Sheets Are List in The Following: Functional DescriptionDocumento13 páginasThe 8253 Data Sheets Are List in The Following: Functional Descriptionharijai26Ainda não há avaliações

- C8254 ADocumento6 páginasC8254 AHongryul ChunAinda não há avaliações

- CS305 M6 Ktunotes - inDocumento35 páginasCS305 M6 Ktunotes - inDipin Preet SinghAinda não há avaliações

- 8254 MICROPROCESSOR (Driste)Documento13 páginas8254 MICROPROCESSOR (Driste)CSE7 NDUBAinda não há avaliações

- Microprocessor Interfacing Microprocessor Interfacing & Application & ApplicationDocumento19 páginasMicroprocessor Interfacing Microprocessor Interfacing & Application & ApplicationMoses BrandNewAinda não há avaliações

- 8253Documento15 páginas8253Abdul RajakAinda não há avaliações

- 8254 Programmable Interval Timer (Andres Suarez-201210937)Documento21 páginas8254 Programmable Interval Timer (Andres Suarez-201210937)Andres SuarezAinda não há avaliações

- Mod 3 Timer DMAcontrDocumento55 páginasMod 3 Timer DMAcontrNicky SanthoshAinda não há avaliações

- Clock This Is The Clock Input For The CounterDocumento22 páginasClock This Is The Clock Input For The CounterSri NikethanAinda não há avaliações

- 8253 NotesDocumento8 páginas8253 NotesSushmita SharmaAinda não há avaliações

- 8254 - Programmable Interval TimerDocumento21 páginas8254 - Programmable Interval Timeray1975507Ainda não há avaliações

- Unit 4 - Microprocessor & Its Application - WWW - Rgpvnotes.inDocumento9 páginasUnit 4 - Microprocessor & Its Application - WWW - Rgpvnotes.inJayesh JoshiAinda não há avaliações

- 8253 NotesDocumento7 páginas8253 NotesSarthak DidwaniaAinda não há avaliações

- MP Module 4 8254Documento15 páginasMP Module 4 8254Lekshmi SasidharanAinda não há avaliações

- 8155 Is An Integrated RamDocumento22 páginas8155 Is An Integrated RamVipan SharmaAinda não há avaliações

- Interfacing Techniques: The 8254 Programmable Interval Timer (PIT)Documento11 páginasInterfacing Techniques: The 8254 Programmable Interval Timer (PIT)yaseen jobaAinda não há avaliações

- Programmable Timer 8254Documento20 páginasProgrammable Timer 8254Axe AxeAinda não há avaliações

- Practical 2 PicDocumento7 páginasPractical 2 PicPrerna Sanjivan MhatreAinda não há avaliações

- Adc0808 and 8253Documento35 páginasAdc0808 and 8253Avanish NiranjanAinda não há avaliações

- Adc0808 and 8253Documento35 páginasAdc0808 and 8253Avanish NiranjanAinda não há avaliações

- Module 4 Interfacing ChipsDocumento12 páginasModule 4 Interfacing ChipsaviralAinda não há avaliações

- Intel 8253/8254 - Programmable Interval TimerDocumento15 páginasIntel 8253/8254 - Programmable Interval TimerAjnamol N RAinda não há avaliações

- Setup and Use The AVR® TimersDocumento16 páginasSetup and Use The AVR® Timersmike_helplineAinda não há avaliações

- Programmable Interval Timer 8253 (PIT) : COE305 LabDocumento10 páginasProgrammable Interval Timer 8253 (PIT) : COE305 LabudayAinda não há avaliações

- PIT: Programmable Interval Timer: Introduction To 8253/8254Documento34 páginasPIT: Programmable Interval Timer: Introduction To 8253/8254Sayan GhoshAinda não há avaliações

- En - stm32f7 WDG Timers GptimDocumento61 páginasEn - stm32f7 WDG Timers GptimLODELBARRIO RDAinda não há avaliações

- 8253 - Timer: Features of 8253Documento5 páginas8253 - Timer: Features of 8253srikrishnathotaAinda não há avaliações

- En - stm32l4 WDG Timers GptimDocumento64 páginasEn - stm32l4 WDG Timers GptimGia LữAinda não há avaliações

- Programmable Interval Timer 8253: Architecture of 8253Documento13 páginasProgrammable Interval Timer 8253: Architecture of 8253Srikanth KodothAinda não há avaliações

- 8255 PpiDocumento22 páginas8255 PpiAswin AswinAinda não há avaliações

- En - STM32G4-WDG TIMERS-General Purpose Timer GPTIMDocumento91 páginasEn - STM32G4-WDG TIMERS-General Purpose Timer GPTIMnorbertscribdAinda não há avaliações

- Lab3 Rev eDocumento13 páginasLab3 Rev eSaad Sulaiman KhanAinda não há avaliações

- 8254 PDFDocumento14 páginas8254 PDFMehul Shah100% (1)

- 8254-Programmable Interval TimerDocumento21 páginas8254-Programmable Interval TimerSanthosh SandyAinda não há avaliações

- Lecture 12 8051 Timer Programing v2Documento22 páginasLecture 12 8051 Timer Programing v2Faisal Bin Abdur Rahman 1912038642Ainda não há avaliações

- 8254 AnniDocumento43 páginas8254 AnniCSE7 NDUBAinda não há avaliações

- Programmable Interval Timer: T.Shakeel, Lovely Professional UniversityDocumento25 páginasProgrammable Interval Timer: T.Shakeel, Lovely Professional UniversityFaiz RahmanAinda não há avaliações

- 8253 Programmable Interval Timer - Free 8085 Microprocessor Notes PDFDocumento4 páginas8253 Programmable Interval Timer - Free 8085 Microprocessor Notes PDFMary HelenAinda não há avaliações

- 8253 Programmable Interval Timer - Free 8085 Microprocessor NotesDocumento4 páginas8253 Programmable Interval Timer - Free 8085 Microprocessor NotesJohn PaulAinda não há avaliações

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Ainda não há avaliações

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationAinda não há avaliações

- Testul Din Anul 2014 - en - Şcoala de Agenţi de Poliţie Vasile Lascăr CâmpinaDocumento24 páginasTestul Din Anul 2014 - en - Şcoala de Agenţi de Poliţie Vasile Lascăr CâmpinaAnonymous lubWipsrWAinda não há avaliações

- Descriere Curs OxfordDocumento11 páginasDescriere Curs OxfordAnonymous lubWipsrWAinda não há avaliações

- Testul Din Anul 2014 - en - Şcoala de Agenţi de Poliţie Vasile Lascăr CâmpinaDocumento24 páginasTestul Din Anul 2014 - en - Şcoala de Agenţi de Poliţie Vasile Lascăr CâmpinaAnonymous lubWipsrWAinda não há avaliações

- Import Import Import Import Import Import ImportDocumento3 páginasImport Import Import Import Import Import ImportAnonymous lubWipsrWAinda não há avaliações

- Agile Project ManagementToc PDFDocumento1 páginaAgile Project ManagementToc PDFAnonymous lubWipsrW0% (2)

- Famous PlacesDocumento4 páginasFamous PlacesAnonymous lubWipsrWAinda não há avaliações

- Product Data Sheet: Relayaux - Fast Trip and Lockout Relay - 8 C/O - Pick-Up Time 10 Ms - 220 V DCDocumento3 páginasProduct Data Sheet: Relayaux - Fast Trip and Lockout Relay - 8 C/O - Pick-Up Time 10 Ms - 220 V DCKuenley TiNy OndeAinda não há avaliações

- Netbackup Cheat SheetDocumento7 páginasNetbackup Cheat SheetSai100Ainda não há avaliações

- Telephone Systems PDFDocumento13 páginasTelephone Systems PDFsorry2qaz67% (3)

- Wireless Data Encryption and Decryption Using RFDocumento4 páginasWireless Data Encryption and Decryption Using RFsanthosh100% (1)

- Updates To ANSI-EASA AR100 2015 0Documento3 páginasUpdates To ANSI-EASA AR100 2015 0VILLANUEVA_DANIEL2064Ainda não há avaliações

- HCPL-7800A: Isolation AmplifierDocumento9 páginasHCPL-7800A: Isolation AmplifierkarkonAinda não há avaliações

- Laboratory: Generation of Am SignalsDocumento25 páginasLaboratory: Generation of Am SignalsTun ShukorAinda não há avaliações

- 96722599-B68L-54 Quick Start - (V100R001 01, En, SI, L)Documento20 páginas96722599-B68L-54 Quick Start - (V100R001 01, En, SI, L)Marco Alejandro Flores BarrazaAinda não há avaliações

- U-WAS 2000 UserManualDocumento106 páginasU-WAS 2000 UserManualEstetAinda não há avaliações

- D N F ElementsDocumento21 páginasD N F ElementsJatinChadhaAinda não há avaliações

- 2.2.44. Total Organic Carbon in Water For Pharmaceutical UseDocumento2 páginas2.2.44. Total Organic Carbon in Water For Pharmaceutical UseMulayam Singh Yadav100% (1)

- 207.OTN 260SCX2 and 130SCX10 Cards V1 04 11feb16Documento24 páginas207.OTN 260SCX2 and 130SCX10 Cards V1 04 11feb16Ronald N Meza C100% (1)

- Service Manual Lh780Documento1.150 páginasService Manual Lh780Phạm Ngọc TàiAinda não há avaliações

- WTLZ - Foxtech Fh-10z English ManualDocumento7 páginasWTLZ - Foxtech Fh-10z English ManualSyed Omer AliAinda não há avaliações

- ABB ACS 800 PM KitsDocumento2 páginasABB ACS 800 PM Kitsvenkatesan0% (1)

- 74 HC 4316Documento12 páginas74 HC 4316jhonco02Ainda não há avaliações

- Partial Discharge HV and EHV Power Cable SystemsDocumento88 páginasPartial Discharge HV and EHV Power Cable Systemszarchiwin05100% (1)

- Isow7741 q1Documento59 páginasIsow7741 q1gwegawAinda não há avaliações

- Teco Ma7200 2 PDFDocumento209 páginasTeco Ma7200 2 PDFDung LeAinda não há avaliações

- Lenovo SL400Documento94 páginasLenovo SL400Abhilash VamanAinda não há avaliações

- Mplab IDE TutorialDocumento12 páginasMplab IDE Tutorialahsoopk100% (1)

- WSDA-USB Datasheet (8400-0074)Documento2 páginasWSDA-USB Datasheet (8400-0074)paulkohanAinda não há avaliações

- Nema SB 50-2008Documento32 páginasNema SB 50-2008Irwin CastroAinda não há avaliações

- Fingerprint-Authentication Using BiometricDocumento59 páginasFingerprint-Authentication Using BiometricDebashishParidaAinda não há avaliações

- Gear MotorDocumento45 páginasGear Motorb3ltaAinda não há avaliações

- WEG Guia de Instalacao pws5610 Quick Guide English PDFDocumento1 páginaWEG Guia de Instalacao pws5610 Quick Guide English PDFÁgó AttilaAinda não há avaliações

- ML4824 Power Factor Correction and PWM Controller Combo: General Description FeaturesDocumento16 páginasML4824 Power Factor Correction and PWM Controller Combo: General Description FeaturesTaras100% (1)

- Overhead Distribution System DesignDocumento5 páginasOverhead Distribution System DesignPhel FloresAinda não há avaliações

- Samsung Un24h4000af Un24h4000afxza Manual de UsuarioDocumento3 páginasSamsung Un24h4000af Un24h4000afxza Manual de UsuarioSaid Raúl Macías GonzálezAinda não há avaliações