Escolar Documentos

Profissional Documentos

Cultura Documentos

Arquitectura RISC

Enviado por

Pili MiliDescrição original:

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Arquitectura RISC

Enviado por

Pili MiliDireitos autorais:

Formatos disponíveis

1

Indic

Pagina 1.- Qu es Risc?......................................................................................

2.- Principios de diseo de las Computadores Risc

2

3

3.-Caracteristicas. 4.- Risc moderno.. 5.- Conjunto de Instrucciones 6.- Arquitectura 7.- Risc Vs Cisc 8.-Conclusiones . 9.-Recomendacin..

3 3 4 7 8 9 9

2 ARQUITECTURAS RISC

Reduced Instruction Set Computer - Computadora con Conjunto de Instrucciones Reducido. Tipo de arquitecturas de computadoras que promueve conjuntos pequeos y simples de instrucciones que pueden tomar poco tiempo para ejecutarse. Los microprocesadores basados en esta arquitectura tienen instrucciones de tamaos fijos y presentados en un nmero reducido de formatos y en donde slo las instrucciones de carga y almacenamiento acceden a la memoria por datos. Tambin suelen tener muchos registros de propsito general. El objetivo de esta arquitectura es facilitar la segmentacin y el paralelismo en la ejecucin de instrucciones y reducir los accesos a memoria.

Intel no fabrica microprocesador completamente RISC para no perder la compatibilidad con los microprocesadores anteriores.

PRINCIPIOS DE DISEO DE LAS MAQUINAS RISC En el diseo de una mquina RISC se tienen cinco pasos: 1. 2. 3. 4. 5. Analizar las aplicaciones para encontrar las operaciones clave. Disear un bus de datos que sea ptimo para las operaciones clave. Disear instrucciones que realicen las operaciones clave utilizando el bus de datos. Agregar nuevas instrucciones slo si no hacen ms lenta a la mquina. Repetir este proceso para otros recursos.

E l diseador deber encontrar qu es lo que hacen en realidad los programas que se pretenden ejecutar. La parte principal de cualquier sistema es la que contiene los registros, el ALU y los 'buses' que los conectan. Se debe optimizar para el lenguaje o aplicacin en cuestin. El tiempo requerido, (denominado tiempo del ciclo del bus de datos) para extraer los operandos de sus registros, mover los datos a travs del ALU y almacenar el resultado de nuevo en un registro, deber hacerse en el tiempo mas corto posible.

Ventajas: 1. La CPU trabaja mas rpido al utilizar menos ciclos de reloj para cumplir sus funciones . 2. RISC ofrece soluciones donde se requiere una elevada capacidad de procesamiento y se presente una orientacin hacia los lenguajes de alto nivel..

3 3. Cada instruccin puede ser ejecutada en un solo ciclo de la CPU (mxima velocidad y eficiencia).

Caractersticas RISC

-Instrucciones de longitud fija -Limitada de carga y almacenamiento de memoria de acceso Instrucciones -Menos modos de direccionamiento -Instruccin de canalizacin -Cargas retrasadas y Sucursales -Optimizacin del compilador -Instruccin independiente y flujos de datos -Un gran nmero de registros -Cableado de la unidad de control - Decodificacin ms rpida. - Registros homogneos, permitiendo que cualquier registro sea utilizado en cualquier contexto - Modos de direccionamiento simple con reemplazados por secuencias de instrucciones aritmticas simples.

RISC Moderno:

-La lnea MIPS Technologies Inc: Que se encontraba en la mayora de las computadoras de Silicon Graphics -La serie IBM POWER: Utilizado principalmente por IBM en Servidores y superordenadores -La versin PowerPC de Motorola e IBM Utilizada en los ordenadores AmigaOne, Apple Macintosh como el iMac, eMac -El procesador SPARC y UltraSPARC de Sun Microsystems y Fujitsu Que se encuentra en sus ltimos modelos de servidores -Descatalogados: -El PA-RISC y el HP/PA de Hewlett-Packard -El DEC Alpha -El ARM Se encuentra en dispositivos PALM, Nintendo DS, Game Boy Advance y en mltiples PDAs, telfonos mviles, Smartphone y reproductores multimedia (como el iPod).

Conjunto de Instrucciones

Instrucciones de carga/almacenamiento:

OPERANDO LDSB LDSH LDUB LDUH LD LDD STB STH STD STDD DESCRIPCIN Cargar byte con signo Cargar media palabra con signo Cargar byte sin signo Cargar media palabra sin signo Cargar palabra Cargar doble palabra Almacenar byte Almacenar media palabra Almacenar palabra Almacenar doble palabra

Instrucciones Aritmticas

OPERANDO DESCRIPCIN ADD ADDCC ADDX ADDXCC SUB SUBCC Sumar Sumar, ajustar icc Sumar con acarreo Sumar con acarreo, ajustar icc Restar Restar, ajustar icc

SUBX SUBXCC MULSCC

Restar con adeudo Restar con adeudo, ajustar icc Paso de multiplicacin, ajustar icc

Instrucciones Booleanas

OPERANDO DESCRIPCIN AND ANDCC ANDN ANDNCC OR ORCC ORN ORNCC XOR XORCC XNOR XNORCC Y Y, ajustar icc No Y No Y, ajustar icc O O, ajustar icc No O No O, ajustar icc O Exclusiva O Exclusiva, ajustar icc No O Exclusiva No O Exclusiva, ajustar icc

Instrucciones de salto/bifurcacin

OPERANDO DESCRIPCIN BCC FBCC CBCC CALL JMPL Bifurcar si condicin Bifurcar si condicin de coma flotante Bifurcar si condicin del procesador Llamar a procedimiento Saltar y enlazar

6 TCC SAVE RESTORE RETT Interceptar si condicin Avanzar ventana de registros Mover ventanas hacia atrs Retornar de interceptacin

Instrucciones de desplazamiento

OPERANDO DESCRIPCIN SLL SRL SRA Desplazamiento lgico a la izquierda Desplazamiento lgico a la derecha Desplazamiento aritmtico a la derecha

Instrucciones diversas

OPERANDO DESCRIPCIN SETHI UNIMP RD WR IFLUSH Fijar los 22 bits altos Instruccin no implementada (Interceptacin) Leer un registro especial Escribir en un registro especial Vaciar la cach de instrucciones

Arquitectura RISC

Con el paso del tiempo se fue experimentando y se descubri que si se usaba una cierta cantidad de instruccin y se implementaban en la CPU se podra ahorrar tiempo a la hora de decodificar instrucciones complejos. Es Partiendo de ello que se llega a concebir la idea de RISC. Caractersticas de RISC Toma como base el esquema de moderno de Von Neuman. Existen tres grupos de instrucciones: Transferencia , operaciones y control de flujo. Cuentas con instrucciones bsicas con las cuales puede procesar instrucciones complejas Arquitectura del tipo load-store (cargar y almacenar). Cuenta con pipeline lo cual permite ejecutar varias instrucciones ala vez y as se disminuye los ciclos de maquina.

La CPU tenia una arquitectura minimalista con lo que se poda usar para incorporar funciones adicionales: Unidad para el procesamiento aritmtico de punto flotante Unidad de administracin de memoria Funciones de control de memoria cache. Implantacin de un conjunto de registros mltiples

Usa menos ciclos de reloj

8 Conserva en memoria los resultados de las operaciones y sus operandos reduciendo la ejecucin de nuevas operaciones Cada instruccin puede ser ejecutada en un solo ciclo del CPU

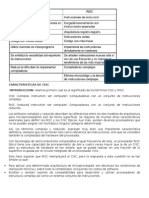

Los Microprocesadores RISC vs CISC Haciendo la presente investigacin acerca de los procesadores RISC, obligatoriamente tendremos que mencionar las diferencias evidentes que tienen los procesadores RISC de los procesadores CISC. Como ya se sabe los procesadores RISC aparecieron tiempo despus de los CISC. Con nuevas mejoras y beneficios que a continuacin mediante una tabla detallaremos: Le dice no a la microprogramacin(se usa autmatas) Sus modos de direccionamiento son limitados Tiene un conjunto limitado y simple de instrucciones La ejecucin de sus instrucciones es lenta El formato de instrucciones es fijo o simplemente son poqusimos. Cuenta con un gran banco de registros La microprogramacin es lo que lo caracteriza Gran cantidad de modos de direccionamiento. Sus instrucciones son complicadas y abundantes en cantidad. La ejecucin es rpida de las instrucciones El formato de las instrucciones es bastante variable El numero de registros es reducido

Grficamente podemos expresar esta comparacin:

RISC

Instrucciones de la maquina Ejecucion de la instruccin

CISC

Instrucciones de la maquina Conversin a microcdigo Microinstrucciones Ejecucion de microinstrucciones

Conclusiones : La arquitectura RISC represent la tendencia contraria a la arquitectura CISC. Aunque ambas apunten a la optimizacin cabe mencionar que la presente arquitectura RISC ofrece unas soluciones mas accesibles donde se requiere una alta capacidad de procesamiento. Las arquitecturas RISC facilitan que las instrucciones sean ejecutadas rpidamente. La forma de lograrlo es simplificando el tipo de instrucciones que ejecuta el procesador, es decir, las instrucciones breves y sencillas son capaces de ejecutarse mucho mas rpido que las instrucciones largas y complejas de un procesador CISC. Debido a la sencillez con la que se maneja la arquitectura de los procesadores RISC, los ciclos de diseo son ms cortos y no solo ofrecen una capacidad de procesamiento triplemente mejor a comparacin de los procesadores CISC, sino que los saltos de capacidad que se producen son mucho mayores. El usuario es el que elige a conveniencia cual procesador le favorece en funcin de la aplicacin que quiera realizar. Si bien hemos explicado anteriormente las ventajas de la arquitectura RISC, no quiere decir que sea el fin de las arquitecturas CISC puesto que tambin seguir perfeccionndose hasta encontrar nuevas rutas para el incremento de sus capacidades.

Se trata de microprocesadores con un conjunto de instrucciones muy reducidas en contraposicin a CISC Su arquitectura fsica nos permite incorporar diferentes componetes que no existan o existan en poca cantidad en la arquitectura Cisc

RECOMENDACIONES Debemos decidir por una determinada arquitectura de procesador de acuerdo a la aplicacin concreta que quiera realizar. No solo por la capacidad de procesamiento del microprocesador; se debe considerar tambin la capacidad real que puede alcanzar el sistema en su conjunto.

Você também pode gostar

- Problemas Ciclos TermodinámicosDocumento27 páginasProblemas Ciclos TermodinámicosCursos Facultad de Ingeniería93% (14)

- Programación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubeNo EverandProgramación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubeAinda não há avaliações

- Computadores para bases de datos. IFCT0310No EverandComputadores para bases de datos. IFCT0310Ainda não há avaliações

- Arquitectura CISC y RISCDocumento10 páginasArquitectura CISC y RISCWilliams Alexander Trias AscanioAinda não há avaliações

- Tecnologia RISC Y CISC TrabajoDocumento5 páginasTecnologia RISC Y CISC TrabajoEsteban Irusta ClaureAinda não há avaliações

- Ensayo Arquitectura Risc y CiscDocumento6 páginasEnsayo Arquitectura Risc y CiscJCARLOS_CUEVAS_Ainda não há avaliações

- Introduccion Risc y CiscDocumento7 páginasIntroduccion Risc y CiscAldo ReignAinda não há avaliações

- 05 - Arquitectura - CISC Vs RISCDocumento36 páginas05 - Arquitectura - CISC Vs RISCDamian ManzabaAinda não há avaliações

- Significado de Los Términos CISC y RISCDocumento8 páginasSignificado de Los Términos CISC y RISCRandy EstradaAinda não há avaliações

- Arquitectura CISCDocumento6 páginasArquitectura CISCNayeli MayoAinda não há avaliações

- MicroI TeoriaDocumento48 páginasMicroI Teoriaottoniel RosarioAinda não há avaliações

- Arquitectura RISC Vs CISCDocumento20 páginasArquitectura RISC Vs CISCEduardo SalazarAinda não há avaliações

- Informe de Arquitecturas RISC Y CISCDocumento13 páginasInforme de Arquitecturas RISC Y CISCJuan Carlos Romero Chalco0% (1)

- Tecnologia Risc y CiscDocumento5 páginasTecnologia Risc y CiscSonia CordovaAinda não há avaliações

- Arquitecturas RISC y CISCDocumento5 páginasArquitecturas RISC y CISCNadia JuarezAinda não há avaliações

- Miguel Jofre S2 Tarea MicrocontroldoresDocumento6 páginasMiguel Jofre S2 Tarea MicrocontroldoresMiguel JofreAinda não há avaliações

- Semana 5 PDFDocumento21 páginasSemana 5 PDFcesardasilvahijoAinda não há avaliações

- 1 Arquitectura RISC Vs CISCDocumento6 páginas1 Arquitectura RISC Vs CISCGerald AburtoAinda não há avaliações

- Sisc RiscDocumento15 páginasSisc RiscROHNNeAinda não há avaliações

- Rodrigo Soto Tarea2Documento6 páginasRodrigo Soto Tarea2rodrigoAinda não há avaliações

- Arquitectura RISC y CISCDocumento10 páginasArquitectura RISC y CISCUsiel RTAinda não há avaliações

- 1 - Modelos de Arquitecturas de CómputoDocumento8 páginas1 - Modelos de Arquitecturas de CómputoSorel TorresAinda não há avaliações

- Arquitectura RISC Vs CISCDocumento9 páginasArquitectura RISC Vs CISCRaul CrookersAinda não há avaliações

- Desventajas Cisc y RiscDocumento15 páginasDesventajas Cisc y RiscMilenka León ChavezAinda não há avaliações

- Taller #1 - Grupo ADocumento6 páginasTaller #1 - Grupo ABryan PxAinda não há avaliações

- Arquitectura RISC Vs CISCDocumento10 páginasArquitectura RISC Vs CISCMario SaicoAinda não há avaliações

- Cisk Vs RiskDocumento9 páginasCisk Vs RiskWilberth Antonio Tuz SegoviaAinda não há avaliações

- Risc y CiscDocumento6 páginasRisc y CiscCamila CuevaAinda não há avaliações

- Caracteristicas de CiscDocumento3 páginasCaracteristicas de CiscWilliam Fernando Garcia100% (1)

- Diferencia Entre Risc y CiscDocumento9 páginasDiferencia Entre Risc y CiscMaria Isabel Fajardo DelgadoAinda não há avaliações

- Arquitectura RISC Vs CISCDocumento25 páginasArquitectura RISC Vs CISCGiacinto DimambroAinda não há avaliações

- CPU Documento ExpoDocumento18 páginasCPU Documento ExpoSorel TorresAinda não há avaliações

- 2 Características de La Arquitectura de RISC y CISCDocumento6 páginas2 Características de La Arquitectura de RISC y CISCLuisVillafuerteAinda não há avaliações

- Investigación MicroprocesadoresDocumento4 páginasInvestigación MicroprocesadoresSergio Ruvalcaba LozanoAinda não há avaliações

- Diferencia CISC Vs RISCDocumento3 páginasDiferencia CISC Vs RISCrodri2507Ainda não há avaliações

- Actividad #5Documento9 páginasActividad #5Ashley IvánAinda não há avaliações

- Arquitectura RISC Vs CISCDocumento10 páginasArquitectura RISC Vs CISCVictor TomatsuAinda não há avaliações

- Risc CiscDocumento51 páginasRisc CiscYamid GambaAinda não há avaliações

- Arquitectura RISC Vs CISCDocumento9 páginasArquitectura RISC Vs CISCMinimo Peluchente JondulAinda não há avaliações

- RiseDocumento7 páginasRiseDalvi JoelAinda não há avaliações

- Risc, Cisc y DSPDocumento57 páginasRisc, Cisc y DSPCesar ChiioAinda não há avaliações

- Risc CiscDocumento13 páginasRisc CiscMary G RamirezAinda não há avaliações

- Introducción A Los Microprocesadores y MicrocontroladoresDocumento4 páginasIntroducción A Los Microprocesadores y MicrocontroladoresOmar AguilarAinda não há avaliações

- Arquitectura Cisc Vs RiscDocumento6 páginasArquitectura Cisc Vs RiscFernando ZapataAinda não há avaliações

- Módulo 3 - Lectura 4Documento18 páginasMódulo 3 - Lectura 4Mateo OteyAinda não há avaliações

- Trabajo Investigacion Micro2Documento14 páginasTrabajo Investigacion Micro2Joel Marcos CopaAinda não há avaliações

- Procesadores CISC y RISCDocumento4 páginasProcesadores CISC y RISCyeison arteagaAinda não há avaliações

- Organizacion y ArquitecturaDocumento24 páginasOrganizacion y ArquitecturaDamian ObrequeAinda não há avaliações

- Ensayo Arquitectura RISC Y CISCDocumento5 páginasEnsayo Arquitectura RISC Y CISCThe Boy SeriousAinda não há avaliações

- Cisc y RiscDocumento5 páginasCisc y RiscCriz dguezAinda não há avaliações

- Arquitectura RISC y Arquitectura CISCDocumento5 páginasArquitectura RISC y Arquitectura CISCSebas TAinda não há avaliações

- Arquitectura de MicroprocesadoresDocumento7 páginasArquitectura de MicroprocesadoresmayteAinda não há avaliações

- CPU o Procesador (Central Processing Unit)Documento27 páginasCPU o Procesador (Central Processing Unit)Alejandro Torres PérezAinda não há avaliações

- Arquitectura Cisc y RiscDocumento27 páginasArquitectura Cisc y RiscEucaris GarciaAinda não há avaliações

- Tipos de Arquitecturas y Evolucion Del CpuDocumento26 páginasTipos de Arquitecturas y Evolucion Del Cpuoso67% (3)

- Arquitecturas Risc y CiscDocumento22 páginasArquitecturas Risc y CiscAlex Alexyear MendozaAinda não há avaliações

- Arquitecturas Risc y CiscDocumento2 páginasArquitecturas Risc y Ciscmanuel_cruz_86Ainda não há avaliações

- Arquitectura MicroprocesadoresDocumento22 páginasArquitectura MicroprocesadoresRony William Pineda BolAinda não há avaliações

- Proyecto de CienciasDocumento21 páginasProyecto de CienciasAnghel CarreroAinda não há avaliações

- Compilador C CCS y Simulador Proteus para Microcontroladores PICNo EverandCompilador C CCS y Simulador Proteus para Microcontroladores PICNota: 2.5 de 5 estrelas2.5/5 (5)

- Reglas para Solucionar Problemas en ComputadorasDocumento2 páginasReglas para Solucionar Problemas en ComputadorasPili MiliAinda não há avaliações

- I - Funciones Lógicas, Si, Y, oDocumento5 páginasI - Funciones Lógicas, Si, Y, oPili MiliAinda não há avaliações

- N - Gestión de Listas RepasoDocumento2 páginasN - Gestión de Listas RepasoPili MiliAinda não há avaliações

- J - FUNCIONES LÓGICAS, RepasoDocumento3 páginasJ - FUNCIONES LÓGICAS, RepasoPili Mili0% (1)

- F MulticinesDocumento3 páginasF MulticinesPili MiliAinda não há avaliações

- ZZ - Excel Repaso 7Documento2 páginasZZ - Excel Repaso 7Pili MiliAinda não há avaliações

- Abis - Formato y SeriesDocumento2 páginasAbis - Formato y SeriesPili MiliAinda não há avaliações

- ZZ - Excel Repaso 6Documento2 páginasZZ - Excel Repaso 6Pili MiliAinda não há avaliações

- ZZ - Excel Repaso 2Documento3 páginasZZ - Excel Repaso 2Pili MiliAinda não há avaliações

- ZZ - Excel Repaso 1Documento3 páginasZZ - Excel Repaso 1Pili MiliAinda não há avaliações

- Circunferencia TrigonometricaDocumento1 páginaCircunferencia Trigonometricaxddd100% (1)

- ElectroneumaticaDocumento3 páginasElectroneumaticaIgnacioQuirozCasasAinda não há avaliações

- Plan Petrolera ITPEDocumento2 páginasPlan Petrolera ITPEDANIEL LARICO PACOAinda não há avaliações

- Trabajo Final de CursoDocumento2 páginasTrabajo Final de CursodanielAinda não há avaliações

- CCNA V6 M1 C7 - Asignación de Direcciones IPDocumento24 páginasCCNA V6 M1 C7 - Asignación de Direcciones IPJavi YaguanaAinda não há avaliações

- Antecedentes Historicos de Pavimentos en MexicoDocumento16 páginasAntecedentes Historicos de Pavimentos en MexicoJeronimoAinda não há avaliações

- Instalar PaquetesDocumento19 páginasInstalar PaquetesMiguel Ángel FernándezAinda não há avaliações

- Guia de Aprendizaje 3 Scada PDFDocumento4 páginasGuia de Aprendizaje 3 Scada PDFedison quinteroAinda não há avaliações

- Claves para Entender El Algoritmo de Instagram en 2021Documento35 páginasClaves para Entender El Algoritmo de Instagram en 2021Dhaniel MacadanAinda não há avaliações

- Modelo Tesis Correlacional-PregradoDocumento41 páginasModelo Tesis Correlacional-PregradoGabriel Romero33% (6)

- Curvas de SecadoDocumento6 páginasCurvas de SecadoDiana MoedanoAinda não há avaliações

- How To Think Like A Computer Scientist - 2 ESDocumento20 páginasHow To Think Like A Computer Scientist - 2 ESEduardo e isabellaAinda não há avaliações

- Detección de Grafeno en Vacunas Covid19 Por Espectroscopía Micro-RamanDocumento75 páginasDetección de Grafeno en Vacunas Covid19 Por Espectroscopía Micro-Ramanelisa blanesAinda não há avaliações

- Minsa Especificaciones Técnicas Del Equipo MedicoDocumento106 páginasMinsa Especificaciones Técnicas Del Equipo MedicoLinaAinda não há avaliações

- Enlace Químico Iónico y CovalenteDocumento51 páginasEnlace Químico Iónico y CovalenteDiego Giraldo BoteroAinda não há avaliações

- Movimientos de TherbligsDocumento7 páginasMovimientos de TherbligsAngel Rojas RamirezAinda não há avaliações

- Universo y MuestraDocumento37 páginasUniverso y MuestraMarla PeppersAinda não há avaliações

- Capítulo 19 - Chopra: Respuesta Sísmica de Edificios Elástico LinealesDocumento20 páginasCapítulo 19 - Chopra: Respuesta Sísmica de Edificios Elástico LinealesAdery Baltodano Monterrey100% (1)

- Diseño Hidrosanitario de Un Aula de ClasesDocumento16 páginasDiseño Hidrosanitario de Un Aula de ClasesBelfanL.NuñezAinda não há avaliações

- Problema1 7Documento23 páginasProblema1 7Cassandra BarriosAinda não há avaliações

- Conservacion de La Energia.Documento11 páginasConservacion de La Energia.Genny AlvarezAinda não há avaliações

- INEN Cantidad Productos Empacados Rec Tec INEN OIML R87 PDFDocumento20 páginasINEN Cantidad Productos Empacados Rec Tec INEN OIML R87 PDFMaría Del Mar AndradeAinda não há avaliações

- Laboratorio Quimica 4Documento10 páginasLaboratorio Quimica 4VICTOR HUGO LEONARDO MEDRANO ADCOAinda não há avaliações

- Actividad 2. Estructura de Los Organizadores CurricularesDocumento2 páginasActividad 2. Estructura de Los Organizadores Curricularesaraceligaliciacuamat86% (7)

- Semana 2 Mediciones FinalDocumento49 páginasSemana 2 Mediciones FinalGustavo CastroAinda não há avaliações

- EXAMEN MICROECONOMÍA. SoluciónDocumento2 páginasEXAMEN MICROECONOMÍA. SoluciónLidia EscAinda não há avaliações

- Actividad 2Documento13 páginasActividad 2Jorge Daniel Andrade HermosilloAinda não há avaliações

- Facultad de Ingeniería Civil Caminos "Actividad Tc-S3": DocenteDocumento5 páginasFacultad de Ingeniería Civil Caminos "Actividad Tc-S3": DocenteMoises Garcia DurandAinda não há avaliações

- Determinacion Del Contenido de Carbonatos en ArcillasDocumento10 páginasDeterminacion Del Contenido de Carbonatos en ArcillasMonica Perez DurandAinda não há avaliações