Escolar Documentos

Profissional Documentos

Cultura Documentos

WP 359

Enviado por

Chemanthi RojaTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

WP 359

Enviado por

Chemanthi RojaDireitos autorais:

Formatos disponíveis

White Paper: Spartan-6 and Virtex-6 FPGAs

WP359 (v1.0) December 8, 2009

Accelerating System Designs Requiring High-Bandwidth Connectivity with Targeted Reference Designs

By: Navneet Rao

FPGAs that provide multi-gigabit serial transceivers to implement high-speed serial protocols have become the platform of choice for a large and growing number of applications today. The flexibility to accommodate different protocols, line rates, and emerging standards has made the multi-gigabit serial transceiver the perfect companion to the flexible reprogrammable logic in FPGAs. However, this flexibility comes at a cost. Designing systems that incorporate high-speed serial I/O is difficult enough. Designing systems that work with multiple protocols and different line rates is even more challenging.

To provide a simpler, more accessible solution, Xilinx has created fully-functional, fully-validated, and fully-supported connectivity targeted reference designs introduced in two new kitsthe Virtex-6 FPGA Connectivity Kit (DK-V6-CONN-G) and the Spartan-6 FPGA Connectivity Kit (DK-S6-CONN-G)that engineers can use to jump-start their connectivity-based designs.

Copyright 2009 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. PCI, PCIe, and PCI Express are trademarks of PCI-SIG and used under license. All other trademarks are the property of their respective owners.

WP359 (v1.0) December 8, 2009

www.xilinx.com

Connectivity Targeted Reference Designs

Connectivity Targeted Reference Designs

To address changing customer requirements and use models, Xilinx surveyed its customers in 2008 to determine what they needed most to complete high-speed serial designs. The results established a number of criteria for the next generation in Xilinx connectivity kits. The most substantial of these was the requirement for a connectivity-based reference design that works with design software, includes all necessary firmware and IP, and can be used as a starting point in a design. The connectivity-based reference design also needs to provide a fully operational system and be tested to a quality standard to enable production-level designs. To meet these requirements, Xilinx defined the connectivity targeted reference design. It was fairly straightforward to determine what needed to go into the connectivity targeted reference designs. PCI Express technology is the most commonly required high-speed serial protocol for both Virtex-6 and Spartan-6 FPGAs. XAUI is the second most desired interface for applications using Virtex-6 FPGAsGigabit Ethernet is the second most desired for Spartan-6 FPGAs. However, the survey also revealed a consensus that to be truly useful, the connectivity targeted reference designs must also include: Source code for easy evaluation and modification of the reference design Implementation scripts A comprehensive, well-documented design flow Support and verification of all reference designs and design flows across the entire tool suite (ISE software) roadmap for the lifetime of the connectivity kit The ability to measure actual transceiver and protocol performance without modifying the design Any software required to run the reference design (i.e., an application programming interface (API) for performance analysis) Documentation that takes the user from the initial bring-up and evaluation stages through design modification

Another important factor in the connectivity targeted reference design is the need for a direct memory access (DMA) controller. Because all PCI Express devices are memory-mapped, data movement occurs as an exchange between the local onboard memory and the system/host memory. To facilitate this exchange, the connectivity kit must provide an interface to DDR2/DDR3 SDRAM while maintaining support for older (slower) memory devices. To efficiently utilize the available memory space at multi-gigabit serial transceiver speeds, the DMA controller must provide sufficient data transfer sizes and throughput. To fulfill this requirement, Xilinx worked with Northwest Logic to include a full license for a production Packet DMA engine (with no timeout or reduced functionality) in the Spartan-6 FPGA connectivity kit. This IP, which customers can use in their end systems, significantly simplifies and accelerates design development of all PCI Express applications for the Spartan-6 LXT family. It provides all the necessary PCI Express design elements: the integrated Endpoint block for PCI Express technology, the Northwest Logic Packet DMA engine, and a DDR3 SDRAM controller. The targeted reference design for the Virtex-6 FPGA connectivity kit integrates a production hardware-timeout version of a high-performance (>10 Gb/s) Packet DMA engine from Northwest Logic. This DMA engine enables designers to fully evaluate the performance of system designs implemented on the Virtex-6 FPGA.

www.xilinx.com

WP359 (v1.0) December 8, 2009

Spartan-6 FPGA Connectivity Targeted Reference Design

Spartan-6 FPGA Connectivity Targeted Reference Design

The Spartan-6 FPGA connectivity targeted reference design is a fully operational bridge between the Gigabit Ethernet IP and the integrated Endpoint block for PCI Express, providing an efficient platform for evaluating the key integrated components in a Spartan-6 FPGA:

X-Ref Target - Figure 1

GTP transceivers Integrated Endpoint block for PCI Express Memory controller block supporting DDR/DDR2/DDR3 SDRAMs and LPDDR (Figure 1).

Control Plane Bridge User Data System to Card DMA to TEMAC Bridge 32-bit Streaming Interface Card to System TEMAC to DMA Bridge User Status LocalLink PLBv46 Slave PLBv46 Master

Target Interface

PLBv46 1000BASE-X

PCS PMA GTP RJ45 SFP

x1 Endpoint Block for PCI Express v1.1

32-bit Transaction Interface

Packet DMA (32-bit)

Wrapper for PCI Express

XPS-LL TEMAC

Marvell PHY GMII

GTP Transceivers

x1 Link for PCI Express

DMA Register Interface

User Space Registers

System to Card

MIG Wrapper

Integrated Blocks

Card to System

32-bit Streaming Interface

Virtual FIFO Layer

MIG User Interface

Memory Controller Block

Xilinx IP

Third Party IP

FPGA Logic

On SP605

wp359_01_113009

Figure 1:

High-Level Diagram of the Spartan-6 FPGA Connectivity Targeted Reference Design

The connectivity targeted reference design also integrates a number of additional IP cores, including the Bus Mastering Packet DMA engine from Northwest Logic (optimized for the Spartan-6 FPGA) and the Xilinx Platform Studio LocalLink Tri-Mode Ethernet MAC (XPS-LL-TEMAC). The DMA engine works in conjunction with the integrated Endpoint block for PCI Express to offload processor data transfer overhead and enables high-speed data movement between the system memory and the FPGA. This design utilizes one integrated Endpoint block for PCI Express technology that is compliant with the PCI Express Base Specification Revision 1.1. The Endpoint block is used to interface to the host system while the Gigabit Ethernet connection is used to implement a network interface card. The system supports either the Gigabit Media

WP359 (v1.0) December 8, 2009 www.xilinx.com 3

SDRAM

Virtex-6 FPGA Connectivity Targeted Reference Design

Independent Interface (GMII) mode using an external Ethernet PHY (typically used to connect to copper networks) or the 1000BASE-X mode using Xilinx GTP transceivers (typically used to connect to optical fibre Ethernet networks). The system design shows how to connect to an external network and run networking applications like Telnet, FTP, etc. The Spartan-6 FPGA connectivity targeted reference design uses the PCI Express standard to exchange data between the local DDR3 memory and system memory. This data exchange is significantly accelerated by a Packet DMA Design maintaining efficient utilization of the available bandwidth. Each Spartan-6 FPGA connectivity kit comes preconfigured with the targeted reference design loaded and verified on a Xilinx SP605 development board (populated with the Spartan-6 LX45T FPGA). The kit also includes the complete ISE Design Suite: Embedded Edition, device driver files, design source files, and board design files. All the necessary software and files are loaded on a USB memory stick along with printed versions of the Hardware Setup Guide and the Getting Started Guide. This enables customers to bring their systems up quickly, begin evaluation, and start extending the design to build their application.

Virtex-6 FPGA Connectivity Targeted Reference Design

The Virtex-6 FPGA connectivity targeted reference design showcases the capabilities of Virtex-6 FPGAs and various IP cores developed for the Virtex-6 family. Figure 2 provides a block-level overview of the connectivity targeted reference design architecture.

X-Ref Target - Figure 2

@250 MHz 64 S2C x4 Gen2/x8 Gen1 Endpoint for v2.0 PCI Express S2C_Data S2C_Ctrl C2S_Ctrl C2S Wrapper for PCI Express 64-bit TRN @ 250 MHz C2S_Data 64

Packet Control +CRC

@250 MHz 64 WR_Data Control Control RD_Data 64 64 Multi-Port Virtual FIFO

@156.25 MHz 64 RD_Data Control Control WR_Data 64 64 RD_Data Control Control WR_Data 64 @250 MHz XAUI RX XAUI TX

@156.25 MHz 64 Data Control XAUI 64 Control Data 64 GTX DDR3

GTX Transceiver

x4/x8 Link for PCI Express

Packet Control +CRC

DMA

64 S2C S2C_Data S2C_Ctrl C2S_Ctrl C2S C2S_Data 64 @250 MHz Control Control WR_Data Control Control RD_Data 64 @250 MHz

Raw Data Loopback

Register Interface TRN Performance Monitor Integrated Blocks Xilinx IP

User Space Registers

256 @200 MHz 256

Native Interface of DDR3 Memory Controller

@400 MHz

Third Party IP

FPGA Logic

WP359_02_120109

Figure 2:

High-Level Diagram of the Virtex-6 FPGA Connectivity Targeted Reference Design

www.xilinx.com

WP359 (v1.0) December 8, 2009

Connectivity Targeted Reference Design Deliverables

The Virtex-6 FPGA connectivity targeted reference design employs FPGA logic that interfaces with the dedicated blocks and wrappers to deliver up to 10 Gb/s performance end-to-end. The IP cores implemented in the connectivity targeted reference design include: Virtex-6 FPGA integrated block for PCI Express (configured as a x4 Gen2 or x8 Gen1 Endpoint) Packet DMA from Northwest Logic Multi-port virtual FIFO memory interface controller generated with the Virtex-6 FPGA Memory Interface Generator (MIG) tool LogiCORE IP XAUI core that supports up to 10 Gb/s throughput

Like its Spartan-6 FPGA counterpart, each Virtex-6 FPGA connectivity kit comes preconfigured with the targeted reference design loaded and verified on a Xilinx ML605 development board (populated with the Virtex-6 LX240T FPGA). To enable high-speed serial bandwidth evaluation and measurement, the kit includes the performance monitor interface to the connectivity targeted reference design. The kit also includes the complete ISE Design Suite: Embedded Edition, device driver files, design source files, and board design files. All the necessary software and files are loaded on a USB memory stick along with printed versions of the Hardware Setup Guide and the Getting Started Guide.

Connectivity Targeted Reference Design Deliverables

The connectivity targeted reference design is a design framework that provides key elements to simplify and accelerate system design development. These include: Design source and IP files:

Top-level system integration RTL source files Xilinx CORE Generator technology for dedicated blocks and LogiCORE IP Third-party IP core deliverables and license management Testbench and bus functional models (BFMs) for faster simulation Regression scripts for random and directed tests FPGA/board constraint files Complete steps and parameters for design synthesis MAP, place and route, and timing closure analysis Automated scripts to generate the FPGA programming files Device driver source files Scripts to build and attach the software driver to the hardware board Performance & status monitor application and GUI Connectivity targeted reference design user guide

Simulation environment:

Implementation environment:

Software deliverables:

Documentation:

WP359 (v1.0) December 8, 2009

www.xilinx.com

Access to the Connectivity Targeted Reference Design

Access to the Connectivity Targeted Reference Design

Designers can gain access to a connectivity targeted reference design in two ways: Purchase a connectivity kit: Connectivity kits provide the complete targeted reference design framework. A simple, easy-to-follow hardware setup guide enables the customer to bring up the demonstration of the connectivity targeted reference design. The customer can then evaluate the system performance of this connectivity targeted reference design through a performance monitor application. All of the deliverables described in Connectivity Targeted Reference Design Deliverables, page 5 can be accessed by registering on www.xilinx.com and downloading the elements. With these tools, the customer can modify and configure specific system parameters, tune the connectivity targeted reference design to their application requirements, and measure the system performance. The customer can then include the modifications and apply them to their specific design implementations. Download the connectivity targeted reference design from the Xilinx website: Customers that already have access to the base Virtex-6 and Spartan-6 FPGA evaluation kits and boards can also gain access to the connectivity targeted reference design deliverables by downloading the complete design from www.xilinx.com. They do not have to purchase the connectivity kit to get started. The IP included in the web download is a hardware evaluation version that is time-limited. Customers that do not have access to the software, IP, and/or hardware elements included in the connectivity kits have to buy them separately to understand and experience the complete hardware bring-up demonstration and flow. However, the included deliverable still enables the customer to go through the simulation and implementation steps and download the time-limited design/bitstream and evaluate system parameters. This enables the customer to quickly ascertain the system performance but precludes them from testing the system parameters through an overnight test run.

Using and Modifying the Connectivity Targeted Reference Design

The connectivity targeted reference design is a building-block architecture design. Design reuse is highly encouraged so that customers can advance their design development stages quickly, as described here: System Architecture: The connectivity targeted reference design delivers clocking and reset topologies for high-performance, multi-clock, domain system designs. Architects can borrow this concept and topology for their FPGA-based system design implementations. The I/O blocks of the connectivity targeted reference design can be easily be replaced, modified, or both, by utilizing a different interface. For example, the Virtex-6 FPGA PCIe-10GDMA-DDR3-XAUI connectivity targeted reference design can be scaled up to include the RXAUI interface. Designers can make this change by replacing the XAUI IP instantiation in the connectivity targeted reference design with the RXAUI interface of LogiCORE IP. Simulation and Verification: The simulation flow provided with the connectivity targeted reference design includes all the deliverables needed to integrate the tests in the users environment. This provides the user a working demonstration of an industry-standard simulator like ModelSim. The user can then add more directed and random tests, as needed, and tune the environment for their own

www.xilinx.com

WP359 (v1.0) December 8, 2009

Use Models

design verification strategies. Design Implementation: To automate FPGA design and development flow, implementation scripts are provided that support the Xilinx design flow and provide a quick parse-through of possible settings and parameter optimizations. This accelerates closure on design goalsarea, design speed, or both. Software Development: Along with hardware design development strategies, software source files and scripts are also included in the connectivity targeted reference design. These device driver source files enable a software architect to understand the intricacies of mapping and using the underlying hardware infrastructure in the software application. Driver build and insert steps are automated to establish a hardware-to-software connection. A performance & status monitor application and GUI further simplifies the users ability to configure the available high-speed serial and memory interfaces and to validate system parameter settings.

Use Models

The connectivity targeted reference designs have building-block architectures that can be modified or scaled up and tuned to meet multiple application requirements. For example, Xilinx supports these user flows for the Virtex-6 FPGA connectivity targeted reference design: As Is or Subset: These are used primarily as a high-bandwidth bridge between PCI Express and XAUI protocol interfaces. Modify by Substitution: This is used to modify or replace the media/network interface to support higher line rates (e.g., users can replace the XAUI interface of the Virtex-6 FPGA connectivity targeted reference design with another interface such as the 6.25 Gb/s RXAUI or the 6.5 Gb/s Aurora interfaces). Scalable Platform: This is used to add custom processing blocks such as coprocessing and in-line acceleration. Evaluate/Measure: This is used for performance evaluation of the PCI Express technology, DDR3, or XAUI interfaces.

The examples in Spartan-6 FPGA Use Model and Virtex-6 FPGA Use Model illustrate the application of these use models in the Virtex-6 and Spartan-6 families, respectively.

Spartan-6 FPGA Use Model

The design example shown in Figure 3 is an Ethernet Command and Control card for an industrial Ethernet system. The architecture for this carrier card includes a Spartan-6 FPGA that supports multiple Ethernet protocols: Tri-mode Ethernet MAC (RJ-45), Gigabit Ethernet (SFP), Sercos III, and Power Over Ethernet (PoE). The Command and Control card interfaces to a PC system to control the data and arbitration across these different Ethernet protocols. Because the PCI Express technology link is oversubscribed, to ensure efficient maintenance and packet throughput, the context of current data must be stored until control is established for both the interface throttle and the data switch that services all of the Ethernet interfaces. An external DDR3 memory controller ensures a smooth transition from one Ethernet interface to another.

WP359 (v1.0) December 8, 2009

www.xilinx.com

Use Models

X-Ref Target - Figure 3

Add-in Card for Ethernet Command and Control

RJ-45 (Standard Ethernet) SFP Cage (Gigabit Ethernet) Data

Power Over Ethernet (PoE) MAC

Sercos III Ethernet IP Interface

Gigabit Ethernet (SFP) Interface

16-bit DDR3 @ 800 Mb/s

S2C_Ctrl C2S_Ctrl

S2C_Ctrl C2S_Ctrl

S2C_Ctrl C2S_Ctrl

RJ-45 (Sercos III)

Spartan-6 FPGA Connectivity Targeted Reference Design

Data

Data

Data

Data

Data

S2C RJ-45 (PoE)

C2S

S2C

C2S

S2C

C2S

Additional DMA Channels

Spartan-6 LXT FPGA

x1 Gen1 PCI Express

WP359_03_120309

Figure 3:

Spartan-6 FPGA Connectivity Targeted Reference Design Use Model

By adopting the Spartan-6 FPGA connectivity targeted reference design, the user can greatly simplify design development. Access to additional Ethernet interfaces requires only a simple building-block architectural change to the provided DMA design (adding extra channels). This enables the design team to focus their efforts on software development and building differentiation into their solution.

Virtex-6 FPGA Use Model

The design example shown in Figure 4 is a network security carrier card for an Advanced Telecom Compute Architecture (ATCA) chassis. The architecture for this carrier card includes a Virtex-6 FPGA, which provides the line interfaces (SFP, XFP, etc.), and connects to a XAUI backplane. The FPGA design also includes a XAUI interface using PCI Express.

www.xilinx.com

WP359 (v1.0) December 8, 2009

DDR3 Memory Array

Summary

X-Ref Target - Figure 4

Network Security Carrier Card

Multi-Core CPU Chipset

(e.g., Intel, Freescale)

x4 Gen2/x8 Gen1 PCI Express

Virtex-6 LXT FPGA

Multi-CPU Buffer Splitting Function

Channel Merging Engine

Line Interface

Optical Framer & Mapper Optical Framer & Mapper Optical Framer & Mapper Optical Framer & Mapper

MAC & Packet Classification MAC & Packet Classification MAC & Packet Classification MAC & Packet Classification

Additional VFIFO Ports

Intrusion Detection Algorithm

(Packet Coloring/ Hash Key Generation)

64-bit DDR3 @ 800 Mb/s

DDR3 Memory Array

XAUI Interface

Virtex-6 FPGA Connectivity Targeted Reference Design

WP359_04_120309

Figure 4:

Virtex-6 FPGA Connectivity Targeted Reference Design Use Model

Connection to a multi-CPU chipset is enabled by the PCI Express compliant Virtex-6 FPGA. The included DMA engine efficiently transports data to and from the chipset. To ensure error-free operation for highly reliable security systems, the system must store current information until the interface throttle establishes control. A high-bandwith data pipe to an external DDR3 memory controller ensures this reliability is maintained. Thus, the Virtex-6 FPGA connectivity targeted reference design can significantly accelerate the design development phase, allowing the design team to focus on key areas for differentiationnetwork security blocks, such as intrusion-detection algorithms or packet-classification engines.

Summary

Xilinx connectivity design platforms address the mounting market challenges facing designers needing high-speed serial I/O by delivering optimized reference designs. These reference designs are precisely targeted to accelerate application development and serve as a reliable foundation to jump-start customer designs. To learn more about these kits, visit http://www.xilinx.com/technology/connectivity.htm

WP359 (v1.0) December 8, 2009

www.xilinx.com

Backplane Interface

Optical Framer & Mapper

MAC & Packet Classification

Revision History

Revision History

The following table shows the revision history for this document:

Date 12/08/09 Version 1.0 Description of Revisions Initial Xilinx release.

Notice of Disclaimer

The information disclosed to you hereunder (the Information) is provided AS-IS with no warranty of any kind, express or implied. Xilinx does not assume any liability arising from your use of the Information. You are responsible for obtaining any rights you may require for your use of this Information. Xilinx reserves the right to make changes, at any time, to the Information without notice and at its sole discretion. Xilinx assumes no obligation to correct any errors contained in the Information or to advise you of any corrections or updates. Xilinx expressly disclaims any liability in connection with technical support or assistance that may be provided to you in connection with the Information. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE INFORMATION, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NONINFRINGEMENT OF THIRD-PARTY RIGHTS.

10

www.xilinx.com

WP359 (v1.0) December 8, 2009

Você também pode gostar

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNo EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNota: 4 de 5 estrelas4/5 (5794)

- Ml605 Product BriefDocumento2 páginasMl605 Product BriefChemanthi RojaAinda não há avaliações

- Manju QC - InternalDocumento4 páginasManju QC - InternalChemanthi RojaAinda não há avaliações

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNo EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNota: 4 de 5 estrelas4/5 (895)

- Time and Distance Prepared by M (1) - Giri, Assoc. Prof in Cse, Sitams, ChittoorDocumento30 páginasTime and Distance Prepared by M (1) - Giri, Assoc. Prof in Cse, Sitams, ChittoorChemanthi RojaAinda não há avaliações

- Question Bank For Reasoning-1Documento7 páginasQuestion Bank For Reasoning-1Chemanthi RojaAinda não há avaliações

- The Yellow House: A Memoir (2019 National Book Award Winner)No EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Nota: 4 de 5 estrelas4/5 (98)

- Puzzle TestDocumento33 páginasPuzzle TestChemanthi RojaAinda não há avaliações

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNo EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNota: 4.5 de 5 estrelas4.5/5 (344)

- WP 363Documento14 páginasWP 363Chemanthi RojaAinda não há avaliações

- The Little Book of Hygge: Danish Secrets to Happy LivingNo EverandThe Little Book of Hygge: Danish Secrets to Happy LivingNota: 3.5 de 5 estrelas3.5/5 (399)

- OpDocumento1 páginaOpChemanthi RojaAinda não há avaliações

- Kochi Metro Rail LTD Managers 22062013Documento7 páginasKochi Metro Rail LTD Managers 22062013Chemanthi RojaAinda não há avaliações

- The Emperor of All Maladies: A Biography of CancerNo EverandThe Emperor of All Maladies: A Biography of CancerNota: 4.5 de 5 estrelas4.5/5 (271)

- Application Form APSPEWCDocumento3 páginasApplication Form APSPEWCChemanthi RojaAinda não há avaliações

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNo EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNota: 4.5 de 5 estrelas4.5/5 (266)

- Bangalore MetroDocumento3 páginasBangalore MetroAlly AkramAinda não há avaliações

- Never Split the Difference: Negotiating As If Your Life Depended On ItNo EverandNever Split the Difference: Negotiating As If Your Life Depended On ItNota: 4.5 de 5 estrelas4.5/5 (838)

- National BrainDocumento2 páginasNational BrainAsim JavedAinda não há avaliações

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNo EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNota: 3.5 de 5 estrelas3.5/5 (231)

- Bank Manager CV TemplateDocumento5 páginasBank Manager CV TemplateChemanthi RojaAinda não há avaliações

- Application Form APSPEWCDocumento3 páginasApplication Form APSPEWCChemanthi RojaAinda não há avaliações

- Instructions For Filling Up The Applicaion For MP 5Documento5 páginasInstructions For Filling Up The Applicaion For MP 5Chemanthi RojaAinda não há avaliações

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNo EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNota: 4.5 de 5 estrelas4.5/5 (474)

- UPSC: Engineering Services Examination 2013Documento7 páginasUPSC: Engineering Services Examination 2013TrcStaffAinda não há avaliações

- Team of Rivals: The Political Genius of Abraham LincolnNo EverandTeam of Rivals: The Political Genius of Abraham LincolnNota: 4.5 de 5 estrelas4.5/5 (234)

- CAT2006 Test Bookletwith KeysDocumento19 páginasCAT2006 Test Bookletwith Keysnitin27mayAinda não há avaliações

- The Unwinding: An Inner History of the New AmericaNo EverandThe Unwinding: An Inner History of the New AmericaNota: 4 de 5 estrelas4/5 (45)

- Project DescriptionDocumento6 páginasProject DescriptionShrinivas SaptalakarAinda não há avaliações

- BEL Recruiting Armed Forces Personnel With DiplomaDocumento2 páginasBEL Recruiting Armed Forces Personnel With DiplomaCareerNotifications.comAinda não há avaliações

- Menu - 635124993669327280 - Advertisement For DST 2013 Project-DJDocumento1 páginaMenu - 635124993669327280 - Advertisement For DST 2013 Project-DJChemanthi RojaAinda não há avaliações

- AP Set Notification 2013 PDF FormatDocumento1 páginaAP Set Notification 2013 PDF Formatvinay0717Ainda não há avaliações

- PlanAhead Tutorial Design Analysis and Floorplanning For PerformanceDocumento65 páginasPlanAhead Tutorial Design Analysis and Floorplanning For PerformanceChemanthi RojaAinda não há avaliações

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyNo EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyNota: 3.5 de 5 estrelas3.5/5 (2259)

- Bank Manager CV TemplateDocumento5 páginasBank Manager CV TemplateChemanthi RojaAinda não há avaliações

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNo EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNota: 4 de 5 estrelas4/5 (1090)

- AP Set Information Broucher2013Documento11 páginasAP Set Information Broucher2013Chemanthi RojaAinda não há avaliações

- D 0007 Paper I MasterDocumento24 páginasD 0007 Paper I MasterashusalluAinda não há avaliações

- System and Network EngineerDocumento1 páginaSystem and Network EngineerChemanthi RojaAinda não há avaliações

- GATE SyllabusDocumento2 páginasGATE SyllabusVenkatesh KaulgudAinda não há avaliações

- Apset Electronic Science Paper IIDocumento10 páginasApset Electronic Science Paper IIChemanthi RojaAinda não há avaliações

- Cabinet SecrateriateDocumento3 páginasCabinet SecrateriateChemanthi RojaAinda não há avaliações

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)No EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Nota: 4.5 de 5 estrelas4.5/5 (121)

- Recruitment - AO 2013Documento7 páginasRecruitment - AO 2013sunilaec1234Ainda não há avaliações

- 2003-20 Communication Plan AttachmentDocumento6 páginas2003-20 Communication Plan Attachmentapi-3731879Ainda não há avaliações

- Viscoelastic Modeling of Flexible Pavement With Abaqus PDFDocumento143 páginasViscoelastic Modeling of Flexible Pavement With Abaqus PDFcabrel TokamAinda não há avaliações

- Pacom S72724+PDR32-RMT-HYB+ManualDocumento130 páginasPacom S72724+PDR32-RMT-HYB+ManualDavidChisholmAinda não há avaliações

- Tally Erp 9.0 Material Control Centre in Tally Erp 9.0Documento27 páginasTally Erp 9.0 Material Control Centre in Tally Erp 9.0Raghavendra yadav KMAinda não há avaliações

- 2015f - CPCS 202 - Quiz 2 - SolutionDocumento3 páginas2015f - CPCS 202 - Quiz 2 - SolutionOsama MaherAinda não há avaliações

- Cap Screws: Sae J429 Grade IdentificationDocumento6 páginasCap Screws: Sae J429 Grade IdentificationHomer SilvaAinda não há avaliações

- Butterworth Filter Design With A Low Pass ButterworthDocumento8 páginasButterworth Filter Design With A Low Pass ButterworthashishkkrAinda não há avaliações

- 3 3 3 Reverse Engineering Worksheet 1Documento4 páginas3 3 3 Reverse Engineering Worksheet 1api-275555576Ainda não há avaliações

- UNIT - 1 (Data Structure Using C/C++) .: Definition of AlgorithmDocumento2 páginasUNIT - 1 (Data Structure Using C/C++) .: Definition of AlgorithmArjun BhargavaAinda não há avaliações

- MeshMolder HelpDocumento2 páginasMeshMolder HelpKarlay SouzaAinda não há avaliações

- Ganesh Balasubramanian (Eds.) - Advances in Nanomaterials - Fundamentals, Properties and Applications-Springer International Publishing (2018)Documento181 páginasGanesh Balasubramanian (Eds.) - Advances in Nanomaterials - Fundamentals, Properties and Applications-Springer International Publishing (2018)Jesus Moreno Castillo100% (1)

- H Beam Load Bearing CalculationDocumento31 páginasH Beam Load Bearing CalculationMuhammad Attiq Ur RahmanAinda não há avaliações

- GU Pipette Quick Check ENDocumento20 páginasGU Pipette Quick Check ENCeren Alim DavutluoğluAinda não há avaliações

- DC Rectifier - OrionDocumento12 páginasDC Rectifier - OrionLimbagaAinda não há avaliações

- Aerodynamics of Paper AirplanesDocumento16 páginasAerodynamics of Paper AirplanesBrindleSmith111Ainda não há avaliações

- Vineeth - Curriculum VitaDocumento8 páginasVineeth - Curriculum VitaVineeth NBAinda não há avaliações

- Centrifugation (Separation Processes)Documento25 páginasCentrifugation (Separation Processes)Allyana Marie Tiemsim100% (2)

- Sony Cdx-G3100ue G3100uv G3150up G3150uv Ver.1.1 PDFDocumento38 páginasSony Cdx-G3100ue G3100uv G3150up G3150uv Ver.1.1 PDFLisandroPeñateAinda não há avaliações

- Buffer Cache AdvisoryDocumento8 páginasBuffer Cache Advisorysteve_fordAinda não há avaliações

- 1233 Pid 03Documento11 páginas1233 Pid 03Reza AranAinda não há avaliações

- Chemical BondingDocumento27 páginasChemical BondingSachin Kumar50% (2)

- LY IR9000 BGA Rework Station User GuideDocumento4 páginasLY IR9000 BGA Rework Station User GuidemariabaccaroAinda não há avaliações

- CI 1580A ENG User ManualDocumento50 páginasCI 1580A ENG User ManualArdy KristianAinda não há avaliações

- Activity9 PDFDocumento5 páginasActivity9 PDFSmitAinda não há avaliações

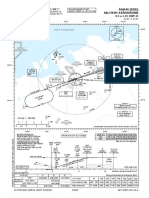

- I/G/O I/G/O A/M/I: Instrument Approach Chart - IcaoDocumento1 páginaI/G/O I/G/O A/M/I: Instrument Approach Chart - IcaoMIkołaj MorzeAinda não há avaliações

- Andreki, P. (2016) - Exploring Critical Success Factors of Construction Projects.Documento12 páginasAndreki, P. (2016) - Exploring Critical Success Factors of Construction Projects.beast mickeyAinda não há avaliações

- Material Turbina A GásDocumento47 páginasMaterial Turbina A GásGetúlio RibeiroAinda não há avaliações

- Aircraft Construction, Repair & Modification Mock Board Exam 10Documento5 páginasAircraft Construction, Repair & Modification Mock Board Exam 10July TadeAinda não há avaliações

- Ricoh Shotmaster ZoomDocumento17 páginasRicoh Shotmaster Zoommanana mappleAinda não há avaliações

- Build Your First Mobile Flex Application: Lab ExercisesDocumento37 páginasBuild Your First Mobile Flex Application: Lab ExercisesSrdjan MarjanovicAinda não há avaliações

- Unlock Any Roku Device: Watch Shows, TV, & Download AppsNo EverandUnlock Any Roku Device: Watch Shows, TV, & Download AppsAinda não há avaliações

- Chip War: The Quest to Dominate the World's Most Critical TechnologyNo EverandChip War: The Quest to Dominate the World's Most Critical TechnologyNota: 4.5 de 5 estrelas4.5/5 (227)

- CompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)No EverandCompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)Nota: 5 de 5 estrelas5/5 (1)

- Chip War: The Fight for the World's Most Critical TechnologyNo EverandChip War: The Fight for the World's Most Critical TechnologyNota: 4.5 de 5 estrelas4.5/5 (82)

- iPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XNo EverandiPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XNota: 3 de 5 estrelas3/5 (2)