Escolar Documentos

Profissional Documentos

Cultura Documentos

Prácticas de Electrónica Cadiz

Enviado por

Jorge Santiago MontielTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Prácticas de Electrónica Cadiz

Enviado por

Jorge Santiago MontielDireitos autorais:

Formatos disponíveis

PRCTICAS DE LABORATORIO [E.D.

]

Prctica N1 Introduccin y funciones lgicas

En esta prctica hemos observado el comportamiento de diferentes puertas lgicas y un integrado tanto en el entrenador como en el simulador Electronics Workbench. Esta prctica abarca dos puntos: el primero trata el aspecto elemental de las puertas lgicas y sus tablas de verdad y el segundo introduce la observacin del integrado 7400.

Funciones lgicas bsicas

A continuacin se muestran siete esquemas correspondientes al comportamiento de las puertas lgicas: NOT, OR, AND, NOR, NAND, AND (3 in) y XOR. Junto a los mismos se indica una tabla de verdad. La correspondencia es obvia. a) NOT A 1 0 F 0 1 d) NOR A B F 0 0 1 0 1 0 1 0 0 1 1 0

b) OR A B F 0 0 0 0 1 1 1 0 1 1 1 1

e) NAND A B F 0 0 1 0 1 1 1 0 1 1 1 0

c) AND A B F 0 0 0 0 1 0 1 0 0 1 1 1

g) XOR A B F 0 0 0 0 1 1 1 0 1 1 1 0

PRCTICAS DE LABORATORIO [E.D.]

f) AND (3-in) A B CF 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1

Circuito integrado 7400

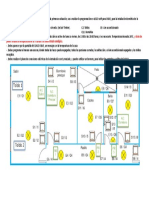

Una vez visto el funcionamiento de las anteriores puertas lgicas nos centramos en un integrado. El 7400. Consiste en siete pares de patas. Dos de ellas por alimentacin y masa. Las doce restantes son entradas y salidas de cuatro puertas NAND tal y como se muestra en el dibujo a continuacin.

El montaje para comprobar el funcionamiento de una de las puertas NAND del 7400 podra ser:

PRCTICAS DE LABORATORIO [E.D.]

Prctica N2 Caractersticas y parmetros de los Circuitos Integrados

En la prctica no.2 se ha puesto atencin en un aspecto fsico de la electrnica y finalmente concluye con el diseo de un circuito lgico. El aspecto inicial estudia el umbral lgico (correspondencia entre tensin y seal de valor 1 o 0) y el tiempo de propagacin segn las puertas lgicas, integrados, disposicin general, etc. Comenzamos por el.

Determinacin de los umbrales de los niveles lgicos

La gua de prcticas facilita datos. El nivel bajo lgico (0) est comprendido entre 0 y 0,8 volts. Es posible que esto se deba a los diodos Zener. Sin perder el objetivo de este apartado, hallamos los valores umbrales segn la figura 4 que nos facilita el guin de prcticas.

[IDEAL] V1Hmx V1Hmn V0Lmx V0Lmn Determinacin del tiempo de propagacin

Umbrales 5 2'548 2'498 0

En este apartado medimos el tiempo de propagacin de un inversor. Nos ayudamos del osciloscopio virtual:

PRCTICAS DE LABORATORIO [E.D.]

Rellenamos la tabla correspondiente:

Inversor TOSC= t2- t1 TP=tOSC/6

Repetimos el apartado usando esta vez el integrado 7404 para ver diferencias.

Tiempo (ns) 53'5 8'91

Volviendo a mirar el osciloscopio vemos que el tiempo de propagacin en el integrado ha disminuido aproximadamente 10 ns. Esto nos ofrece la ventaja de una mayor rapidez de transmisin, aunque el conexionado se complica algo. Tabla de tiempos:

CI 7404 TOSC= t2- t1 TP=tOSC/6 Diseo de un circuito lgico

Tiempo (ns) 39'8 6'63

Para finalizar la prctica se pide disear un circuito lgico con tres entradas (P, Q y R) de forma que la salida S se encuentre en estado 1 cuando P sea 0 o si Q = R = 1. Tras rellenar la tabla de verdad nos queda: Por inspeccin se observa que la solucin es la suma (OR) de una funcin NOT 'P' y de una funcin AND 'Q'-'R'. P Q R S Para quedar seguros aplicamos el lgebra de Boole: 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1

S =P Q R P Q R PQ R PQ R P Q R S =P Q R R P Q R R P Q R S =P Q PQ P Q R S =P Q Q PQ R =P P Q R S =P Q R (izq.) S =P Q R =P Q R Ley de Morgan S =P Q R =P Q R (der.)

Solo con NAND: (para usar el 7400)

PRCTICAS DE LABORATORIO [E.D.]

Prctica N3 Funciones combinacionales

Con lo visto anteriormente nos centramos, como dice el ttulo, en las funciones combinacionales. Diseo de funciones y generacin de las mismas mediante un nuevo bloque: el decodificador.

Diseo de funciones lgicas

Se realizan el diseo de algunas funciones lgicas a continuacin: a)

F1 = A B A B C F1 = A B A C B C

00 1 1 01 11 1 1 10 1 1

c)

F3 = w w x y z F3 = w x y z

00 1

Tras simplificar queda

Tras simplificar queda Rellenamos la tabla de Karnaugh: A \ BC 00 10 11 10 La funcin es en s un menor principal: m4 Representacin de la funcin con puertas NOR: 01 11 10

Rellenamos la tabla de Karnaugh: A \ BC 0 1

Esto nos da informacin suficiente para plantear los menores principales:

F1 = A B C A B C A B C A B C A B C A B C F1 =B C (Dos grupos de 4)

Simplifacin de la funcin ayudndonos con el diagrama de Karnaugh: Representacin de la funcin con puertas NOR:

b)

F2 = A A B CB C F2 = A B C B C

00 1 1 01 11 1 1 10 1 1

d)

Tras simplificar queda

F4 =w x y z w F4 = w x x y z

00 01 11 10

Tras simplificar queda

Rellenamos la tabla de Karnaugh: A \ BC 0 1

Rellenamos la tabla de Karnaugh: A \ BC 00 10 11 10 1 1 1 1 1

Los menores principales son exactamente los mismos que en el caso anterior (a), la simplifacin es la misma y la representacin tambin.

El diagrama nos da los siguientes menores:

F4 = w x y z w x y z w x y z w x y z w x y z

Representacin de la funcin con puertas NAND:

PRCTICAS DE LABORATORIO [E.D.]

Decodificadores de 7 segmentos

Usamos el decodificador del entrenador lgico de tipo BCD a 7 segmentos para rellenar la siguiente tabla de verdad: D 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 C 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 A 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 a 1 0 1 1 0 1 0 1 1 1 0 0 0 1 0 0 b 1 1 1 1 1 0 0 1 1 1 0 0 1 0 0 0 c 1 1 0 1 1 1 1 1 1 1 0 1 0 0 0 0 d 1 0 1 1 0 1 1 0 1 0 1 1 0 1 1 0 e 1 0 1 0 0 0 1 0 1 0 1 0 0 0 1 0 f 1 0 0 0 1 1 1 0 1 1 0 0 1 1 1 0 g 0 0 1 1 1 1 1 0 1 1 1 1 1 1 1 0

Entendiendo por 1 cuando el segmento del display se enciende y 0 cuando est apagado.

Decodificador BCD-Decimal: 7442

En este apartado observamos mediante el montaje del decodificador 7442 tal y como se muestra en la figura 9 (pg. 12) del guin de prcticas, cmo funciona. Algo importante a comentar es la importancia de conectarlo correctamente a un generador de palabras o a la entrada de seal. No obstante, la salida se ven con valor contrario al esperado y esto es debido a que las salidas del decodificador estn previamente conectadas a un inversor lgico.

PRCTICAS DE LABORATORIO [E.D.]

Generador de funciones mediante decodificador

Se pretende en este ltimo punto sacarle partido al decodificador visto (7442) y usarlo como generador de funciones. Por ejemplo:

F1 = A B C A B C A B C A B C que equivale a los cuatro menores principales iniciales. Tengo que llegar a F1 =m0m1 m2 m3 con F7442 =m0 m1 m2 m3

a) Dos posibles soluciones: a.1) Negar previamente las 4 primeras salidas del 7442 y posteriormente a.2) Usar las leyes de Morgan para llegar a la funcin con tan solo una puerta conectar las salidas negadas a las entradas de una puerta lgica OR de 4 lgica (en nuestro caso NAND para eliminar sumas): entradas: F =m m m m F =m m m m

1 0 1 2 3 1 0 1 2 3

b)

F2 = A B C A C usamos Karnaugh para saber su expresin en trminos de menores principales.

00 1 1 01 1 1 11 1 10 1 1 0 1

A \ BC

Tenemos los 7 primeros menores principales.

F2 =m0m1 m2 m3m4m5m6

Al igual que en el caso anterior, tenemos dos maneras de generar la funcin F2 usando el decodificador 7442. b.1) Negar previamente las 7 primeras salidas del decodificador y b.2) Podemos ver F2 como la suma de 7 trminos o la negacin de slo uno (el posteriormente conectarlas a las entradas de una puerta lgica OR de 7 octavo) F =m As pues aprovechamos las salidas del decodificador, 2 7 entradas: que estn negadas, y de paso nos ahorramos puertas lgicas. Basta con conectar la salida novena (no. 7) al punto que evale la funcin.

PRCTICAS DE LABORATORIO [E.D.]

Prctica N4 Multiplexores y Demultiplexores

Esta prctica introduce el uso de multiplexor como dispositivo para generar cualquier tipo de funcin. En el primer apartado comprobamos ya sea con el simulador EWB o con el entrenador lgico el funcionamiento de uno de los dos multiplexores 4x1 que nos encontramos en un integrado 74153. Tras comprobar la tabla de verdad

MUX como generador de funciones

a)

F1 = A B C (entindase como 2 sumas exclusivas encadenadas)

A B C F1 Vista la tabla de verdad de las dos sumas exclusivas encadenadas, procedemos a rellenar la tabla para tres 0 0 0 0 variables (A, B, C) facilitada en el guin de prcticas: 0 0 1 1 E0 E1 E2 E3 0 0 1 1 1 1 1 1 0 0 1 1 0 1 0 1 0 1 1 0 1 0 0 1 A\BC 0 1 00 0 1 01 1 0 10 1 0 11 0 1

Una vez hecho esto podemos realizar la funcin con el multiplexor.

b)

F2 = A B C D A B C D A B C DA B C DA B CD A B CD A B CD

En este caso nos viene dada la tabla de la verdad como suma de menores principales: rellenamos la tabla segn 4 variables y siguiendo el orden como siempre: E0 A\BCD 0 1 000 0 1 E1 001 1 0 E2 010 1 0 E3 011 0 1 0 E4 100 0 1 E5 101 1 0 E6 110 0 0 0 E7 111 1 1 1

F2 =m0m2 m5m7m9m12m15 as pues

Usamos dos integrados 74153

PRCTICAS DE LABORATORIO [E.D.]

c)

F3= A B C D A B C D A B C E A B C E completamos: F3= A B C D E E A B CD E E A B C DD E A B C DD E F3= A B CDE A B CD E A B C DE A B C DE A B C DE A B CD E

E0 0 1 1 0 E1 1 0 E2 1 0 E3 0 0 0 E4 0 0 0 E5 0 0 0 E6 0 0 0 E7 0 0 0 E8 0 0 0 E9 0 0 0 E10 0 0 0 E11 0 0 0 E12 0 1 E13 0 1 E14 0 1 E15 0 0 0

Procedemos a rellenar la tabla

A\BCDE 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1

Ntese en azulado que la seal en los dos mux centrales es 0. Para ahorrar se usan solo dos multiplexores como en el anterior caso.

PRCTICAS DE LABORATORIO [E.D.]

Prctica N5 Comparadores, Detectores de Paridad y Circuitos Aritmticos

Llegados a la ltima prctica, tratamos de obtener un punto de vista ms prctico comenzando con la comprobacin del funcionamiento de integrados para comparar magnitudes, siguiendo con aplicaciones para la correcta transmisin de datos y finalizando con el diseo y utilizacin de puertas lgicas para obtener funciones aritmticas alcanzando finalmente el concepto de ALU (unidad aritmtico-lgica)

Generadores y detectores de paridad

Los generadores de paridad par son construidos con puertas XOR mientras que los de paridad impar estn hechos con XNOR. Su funcionamiento se basa en contar si hay un nmero par o impar de 1's. Se genera un bit de paridad par, cuando el nmero de 1's contados es impar y se genera un bit de paridad impar cuando el nmero de 1's contados es par. Tabla de verdad: B1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 B2 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 B3 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 B4 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 B5 (par) 0 1 1 0 1 0 0 1 1 0 0 1 0 1 1 0 B6 (impar) 1 0 0 1 0 1 1 0 0 1 1 0 1 0 0 1

Basta con colocar una puerta XOR o XNOR extra para crear el detector de paridad que salta con estado 1 si hay error o 0 si la transmisin es buena o los errores se han eliminado entre s.

10

PRCTICAS DE LABORATORIO [E.D.]

Circuitos aritmticos bsicos

En este apartado se pide la tabla de verdad y funcin de un semisumador y de un sumador completo. - Semisumador A 0 0 1 1 B 0 1 0 1 S 0 1 1 0 AC 0 0 0 1

- Sumador completo A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 AP 0 1 0 1 0 1 0 1 S 0 1 1 0 1 1 0 0 AF 0 0 0 1 0 0 1 1

11

PRCTICAS DE LABORATORIO [E.D.]

Unidad aritmtico-lgica (ALU)

Tocamos fondo en la prctica con el diseo de una unidad aritmtico-lgica que suma, resta y opera lgicamente dos datos de 1 bit. A 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 O1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 O2 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 R 0 0 0 1 1 1 1 1 1 1 1 1 0 0 0 0 C 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0

Diagrama de Karnaugh y resolucin de funcin R AB\O1O0 00 01 11 10 1 1 1 1 1 00 01 1 1 1 1 11 10

Diagrama de Karnaugh y resolucin de funcin C AB\O1O0 00 01 11 10 1 1 00 01 11 10

R = A B A B A O1 O0 R = A B A O1 O0 *

*entindase el crculo como suma exclusiva.

C= A B O1 O 0 A B O 1 O 0 C=B O 1 A O0 *

12

Você também pode gostar

- Problemas resueltos de Hidráulica de CanalesNo EverandProblemas resueltos de Hidráulica de CanalesNota: 4.5 de 5 estrelas4.5/5 (7)

- P3EQ4Documento16 páginasP3EQ4Fernando CamposAinda não há avaliações

- Practica 2Documento6 páginasPractica 2Vin Doyle BravoAinda não há avaliações

- Compuertas Lógicas y Tabla de VerdadDocumento17 páginasCompuertas Lógicas y Tabla de VerdadAc Bob BeatAinda não há avaliações

- Laboratorio - Informe - 7 Flip Flops RS JK D TDocumento2 páginasLaboratorio - Informe - 7 Flip Flops RS JK D TBryan RodriguezAinda não há avaliações

- IDL2020 Pca2Documento7 páginasIDL2020 Pca2Electro MotiveAinda não há avaliações

- Laboratorio 4 I 2023 601Documento6 páginasLaboratorio 4 I 2023 601JOELAinda não há avaliações

- Práctico 3 - Sisttemas Digitales 2022Documento6 páginasPráctico 3 - Sisttemas Digitales 2022EduardoAinda não há avaliações

- Control Con Compuertas Logicas PDFDocumento27 páginasControl Con Compuertas Logicas PDFAlison ReedAinda não há avaliações

- Informe Final 2 Sistemas DigitalesDocumento18 páginasInforme Final 2 Sistemas DigitalesIrvin CormánAinda não há avaliações

- U2 CombinacionalesCompletoDocumento20 páginasU2 CombinacionalesCompletoRey HolguinAinda não há avaliações

- 4 KarnaughDocumento15 páginas4 KarnaughRoberto CantoAinda não há avaliações

- Sumador Binario de 4 BitsDocumento10 páginasSumador Binario de 4 BitsBere Ramírez AguileraAinda não há avaliações

- P4 Alvarado Aviles Escobar Moran MendezDocumento20 páginasP4 Alvarado Aviles Escobar Moran MendezSamuel MoralesAinda não há avaliações

- Informe 5 Electronica DigitalDocumento18 páginasInforme 5 Electronica DigitalPedrito TzaquimbioAinda não há avaliações

- Lab 07 Sist Digit. Jhon LaureanoDocumento24 páginasLab 07 Sist Digit. Jhon LaureanoJhon LaureanoAinda não há avaliações

- Sistemas Digitales I 2 LaboratorioDocumento15 páginasSistemas Digitales I 2 LaboratorioMiguel Obispo ChaguaAinda não há avaliações

- Informe de Mapas de KarnaughDocumento11 páginasInforme de Mapas de KarnaughBhily Quipo100% (1)

- Qdoc - Tips Sistemas-Digitales PDFDocumento35 páginasQdoc - Tips Sistemas-Digitales PDFLuisa FernandaAinda não há avaliações

- Laboratorio 1 Lógicos AND OR NOTDocumento12 páginasLaboratorio 1 Lógicos AND OR NOTdeoli1990Ainda não há avaliações

- Laboratorio - Informe - 5 Sumador y Restador CompletosDocumento3 páginasLaboratorio - Informe - 5 Sumador y Restador CompletosBryan RodriguezAinda não há avaliações

- Display de 7 Elementos ProtoboardDocumento12 páginasDisplay de 7 Elementos ProtoboardAndree Zuñiga GuevaraAinda não há avaliações

- Sumador y MultiplexorDocumento6 páginasSumador y MultiplexorCesar ContrerasAinda não há avaliações

- Practica - 5 Compuertas LogicasDocumento6 páginasPractica - 5 Compuertas LogicasEmiliano lara zeaAinda não há avaliações

- Aplicacion de Los Sistemas Digitales Combinacionales (Parte 1)Documento35 páginasAplicacion de Los Sistemas Digitales Combinacionales (Parte 1)egyyoAinda não há avaliações

- Circuitos Digitales 1Documento12 páginasCircuitos Digitales 1Circulo Es NivelAinda não há avaliações

- Laboratorio de Circuitos Digitales 4Documento7 páginasLaboratorio de Circuitos Digitales 4Csar PariapazaAinda não há avaliações

- Preinforme de La Practica 3 Diseño de Sumador-Restador de 8 BitsDocumento8 páginasPreinforme de La Practica 3 Diseño de Sumador-Restador de 8 BitsGabrielCordobaAinda não há avaliações

- Practica 2Documento12 páginasPractica 2sergio cerinoAinda não há avaliações

- Laboratorio 02 - Depaz Nuñez, RaulDocumento20 páginasLaboratorio 02 - Depaz Nuñez, RaulRaul Depaz NuñezAinda não há avaliações

- Practi Arqui AvDocumento129 páginasPracti Arqui AvJErdradexAinda não há avaliações

- Practica - Odificadores y DecodificadoresDocumento12 páginasPractica - Odificadores y DecodificadoresYosel VilchezAinda não há avaliações

- COMPUERTAS LÓGICAS Y ÁLGEBRA BOOLEANA (Capitulo 3)Documento7 páginasCOMPUERTAS LÓGICAS Y ÁLGEBRA BOOLEANA (Capitulo 3)Manuel Alonso Correa AtocheAinda não há avaliações

- DECODIFICADORDocumento16 páginasDECODIFICADORDANIEL ANDRES RAMIREZ SEGURAAinda não há avaliações

- Sistema Digital Con Memoria EpromDocumento17 páginasSistema Digital Con Memoria EpromIvan Dario Jaramillo TorresAinda não há avaliações

- Informe Previo N°2Documento10 páginasInforme Previo N°2Jorge HuamanAinda não há avaliações

- Flash de 3 BitsDocumento5 páginasFlash de 3 Bitsj_adolfoAinda não há avaliações

- 04 Programacion de SPLDs Con WinCUPLDocumento29 páginas04 Programacion de SPLDs Con WinCUPLasandovAinda não há avaliações

- Taller 2Documento10 páginasTaller 2Raul Andres Mejia DiazAinda não há avaliações

- Previo de Sumadores y RestadoresDocumento9 páginasPrevio de Sumadores y RestadoresCarlosAndresSolisChavezAinda não há avaliações

- Decodificador BCD A 7 Segmentos 2009Documento6 páginasDecodificador BCD A 7 Segmentos 2009Rosario Trejo CerinoAinda não há avaliações

- Practica 2 Electrónica Equipo 14Documento23 páginasPractica 2 Electrónica Equipo 14Ximena J LanderosAinda não há avaliações

- Lab #1 Compuertas LogicasDocumento6 páginasLab #1 Compuertas LogicasManolo Camilo Ortega CondegaAinda não há avaliações

- 06-Metodos Minimizacion KarnaughDocumento10 páginas06-Metodos Minimizacion KarnaughRomero100% (1)

- Circuitos CombinacionalesDocumento25 páginasCircuitos Combinacionaleschinguito100% (3)

- 3 Controladores Logicos FESTO - Logica BooleanaDocumento14 páginas3 Controladores Logicos FESTO - Logica Booleanacarlos.otiniano9811Ainda não há avaliações

- Circuitos Logica SecuencialDocumento4 páginasCircuitos Logica SecuencialCarlos MartinezAinda não há avaliações

- Ieee Algebra BooleanaDocumento6 páginasIeee Algebra BooleanaNilsa Yohanna Niño HernandezAinda não há avaliações

- Practica ALUDocumento6 páginasPractica ALUJuan Carlos Villagran OrdonezAinda não há avaliações

- Practicas PLDDocumento20 páginasPracticas PLDJesus GarciaAinda não há avaliações

- Compuertas Lógicas BásicasDocumento9 páginasCompuertas Lógicas BásicasTazann24Ainda não há avaliações

- Sistemas Logicos - 1 - Guia de PracticosDocumento22 páginasSistemas Logicos - 1 - Guia de PracticosFranklin ElPatronAinda não há avaliações

- Manual de Prácticas de Electrónica Básica - Christian EspinosaDocumento13 páginasManual de Prácticas de Electrónica Básica - Christian EspinosaelkmaleonAinda não há avaliações

- TP2 Simplificación-2024Documento5 páginasTP2 Simplificación-2024Magali GutierrezAinda não há avaliações

- Practica UftDocumento5 páginasPractica UftArturo Gonzalez SegueriAinda não há avaliações

- Introducción Al Psoc5Lp: Teoría y aplicaciones prácticaNo EverandIntroducción Al Psoc5Lp: Teoría y aplicaciones prácticaAinda não há avaliações

- Métodos Matriciales para ingenieros con MATLABNo EverandMétodos Matriciales para ingenieros con MATLABNota: 5 de 5 estrelas5/5 (1)

- Aprender Arduino, prototipado y programación avanzada con 100 ejerciciosNo EverandAprender Arduino, prototipado y programación avanzada con 100 ejerciciosNota: 5 de 5 estrelas5/5 (5)

- P1 Punto Luz SimpleDocumento4 páginasP1 Punto Luz SimpleJorge Santiago MontielAinda não há avaliações

- Practica #1 IsfvDocumento3 páginasPractica #1 IsfvJorge Santiago MontielAinda não há avaliações

- P3 Dos Lamparas en ParaleloDocumento4 páginasP3 Dos Lamparas en ParaleloJorge Santiago MontielAinda não há avaliações

- P4 Tablero para Instalaciones de InteriorDocumento3 páginasP4 Tablero para Instalaciones de InteriorJorge Santiago MontielAinda não há avaliações

- P2 Dos Lamparas en ParaleloDocumento5 páginasP2 Dos Lamparas en ParaleloJorge Santiago MontielAinda não há avaliações

- P5 Lineas de Tomas de CorrienteDocumento5 páginasP5 Lineas de Tomas de CorrienteJorge Santiago MontielAinda não há avaliações

- Normativa Sobre Motores Asíncronos ACDocumento8 páginasNormativa Sobre Motores Asíncronos ACJorge Santiago MontielAinda não há avaliações

- FRANCÉS 6 Semana Del 27 Al 30 de AbrilDocumento1 páginaFRANCÉS 6 Semana Del 27 Al 30 de AbrilJorge Santiago MontielAinda não há avaliações

- Plantilla Prácticas IEBASICASDocumento3 páginasPlantilla Prácticas IEBASICASJorge Santiago MontielAinda não há avaliações

- Soluciones Semana Del 20 Al 24Documento5 páginasSoluciones Semana Del 20 Al 24Jorge Santiago Montiel100% (1)

- Actividades Musicales 6ºDocumento2 páginasActividades Musicales 6ºJorge Santiago MontielAinda não há avaliações

- Informacion VIVIDocumento112 páginasInformacion VIVISteawardAinda não há avaliações

- Lengua Semana 20-24Documento1 páginaLengua Semana 20-24Jorge Santiago MontielAinda não há avaliações

- Soluciones U-10 Semana 20 A 24 de Abril (Págs. 164 A 167)Documento2 páginasSoluciones U-10 Semana 20 A 24 de Abril (Págs. 164 A 167)Jorge Santiago MontielAinda não há avaliações

- Tablas y Datos para ProteccionesDocumento11 páginasTablas y Datos para ProteccionesJorge Santiago MontielAinda não há avaliações

- Formulario Máquinas EléctricasDocumento6 páginasFormulario Máquinas EléctricasJorge Santiago MontielAinda não há avaliações

- Normativa Sobre Motores Asíncronos ACDocumento8 páginasNormativa Sobre Motores Asíncronos ACJorge Santiago MontielAinda não há avaliações

- Hoja de Trabajo MCD y MCMDocumento2 páginasHoja de Trabajo MCD y MCMEdgarGonzalez100% (1)

- Proyecto Vivienda y SupermercadoDocumento1 páginaProyecto Vivienda y SupermercadoJorge Santiago MontielAinda não há avaliações

- Cálculo de SeccionesDocumento1 páginaCálculo de SeccionesJorge Santiago MontielAinda não há avaliações

- Protección Contra Contactos IndirectosDocumento3 páginasProtección Contra Contactos IndirectosJorge Santiago MontielAinda não há avaliações

- 46Documento35 páginas46RobAinda não há avaliações

- Faq TecnicasDocumento23 páginasFaq TecnicasSteawardAinda não há avaliações

- Formulario Máquinas EléctricasDocumento6 páginasFormulario Máquinas EléctricasJorge Santiago MontielAinda não há avaliações

- Tablas y Datos para ProteccionesDocumento11 páginasTablas y Datos para ProteccionesJorge Santiago MontielAinda não há avaliações

- Práctica 9 VIVIENDADocumento2 páginasPráctica 9 VIVIENDAJorge Santiago MontielAinda não há avaliações

- Practica Final Persiana AutomaticaDocumento3 páginasPractica Final Persiana AutomaticaJorge Santiago MontielAinda não há avaliações

- ACTIVIDAD Tres Ultimas Programaciones OBA5Documento4 páginasACTIVIDAD Tres Ultimas Programaciones OBA5Jorge Santiago MontielAinda não há avaliações

- Práctica 9 VIVIENDADocumento1 páginaPráctica 9 VIVIENDAJorge Santiago Montiel100% (1)

- Problemas Tipos de Datos y CodificaciónDocumento3 páginasProblemas Tipos de Datos y CodificaciónJorge Santiago MontielAinda não há avaliações

- P5 Amplificadores Con Retroalimentación NegativaDocumento4 páginasP5 Amplificadores Con Retroalimentación NegativaJose Latouchet Jr.Ainda não há avaliações

- Conversor Analogo A DigitalDocumento89 páginasConversor Analogo A DigitalJuan Pablo PerezAinda não há avaliações

- Familias Lógicas de Circuitos IntegradosDocumento2 páginasFamilias Lógicas de Circuitos IntegradosAnton GarciaAinda não há avaliações

- S08.s1 - Ejercicios de Teorema de Norton y Thevenin - Máxima PotenciaDocumento18 páginasS08.s1 - Ejercicios de Teorema de Norton y Thevenin - Máxima PotenciaJhamir MartellAinda não há avaliações

- Informe de Laboratorio #5 - Análisis de MallasDocumento12 páginasInforme de Laboratorio #5 - Análisis de MallasMaria Camila Marin SanchezAinda não há avaliações

- PLL 1Documento12 páginasPLL 1alder anthony anahueAinda não há avaliações

- Teoria Operacional2 Industrial 23Documento60 páginasTeoria Operacional2 Industrial 23Benja Cardozo TbbAinda não há avaliações

- Puertas LogicasDocumento5 páginasPuertas LogicasManuel MarraAinda não há avaliações

- Tecnología TTLDocumento6 páginasTecnología TTLMarioAinda não há avaliações

- 3 - Algebra de BooleDocumento44 páginas3 - Algebra de BooleBrandon DamianAinda não há avaliações

- Informe Final Practica 4Documento15 páginasInforme Final Practica 4Adrian ValdiviaAinda não há avaliações

- Circuito RLCDocumento4 páginasCircuito RLCXimme YagamiiAinda não há avaliações

- Tarea 1Documento11 páginasTarea 1Fernando MendozaAinda não há avaliações

- Familias de Circuitos IntegradosDocumento3 páginasFamilias de Circuitos IntegradosAndres Mauricio Ruiz MolanoAinda não há avaliações

- Laboratorio 4 Amplificadores BásicosDocumento9 páginasLaboratorio 4 Amplificadores BásicosAndres SanchezAinda não há avaliações

- Nivel 1 - Leccion 1 - Actividad 1Documento2 páginasNivel 1 - Leccion 1 - Actividad 1jorge luis campagne nevarezAinda não há avaliações

- Parcial 1 Circuitos II 2021-1Documento31 páginasParcial 1 Circuitos II 2021-1Yeison Stiven Jiménez Mejía100% (1)

- Tema 7Documento10 páginasTema 7PALOP23Ainda não há avaliações

- PLLDocumento5 páginasPLLArsenio VillanuevaAinda não há avaliações

- Fase 3 Carlos UnadDocumento8 páginasFase 3 Carlos UnadEiden PereaAinda não há avaliações

- Tecnología TTLDocumento8 páginasTecnología TTLapi-3760181100% (8)

- S2 Familias LógicasDocumento18 páginasS2 Familias Lógicasantony bustamanteAinda não há avaliações

- Informe Práctica 8Documento3 páginasInforme Práctica 8Santiago Vergara HernandezAinda não há avaliações

- Deber Teoremas PDFDocumento5 páginasDeber Teoremas PDFDiego Alexander Enriquez0% (1)

- Resumen Del Capítulo 13Documento4 páginasResumen Del Capítulo 13Maylor Fernández MendezAinda não há avaliações

- Diferencia Entre Un Rectificador Normal y Un Rectificador de Precisión Con OP-AMPDocumento2 páginasDiferencia Entre Un Rectificador Normal y Un Rectificador de Precisión Con OP-AMPJonathan RiofrioAinda não há avaliações

- S1 Simplificación de Funciones LógicasDocumento12 páginasS1 Simplificación de Funciones LógicasFlexXcat MiguelAinda não há avaliações

- Marco TeóricoDocumento4 páginasMarco TeóricoEscob4rt099Ainda não há avaliações

- LAB 12 - MultivibradoresDocumento13 páginasLAB 12 - MultivibradoresDiego ClavijoAinda não há avaliações

- Emitter Coupled LogicDocumento3 páginasEmitter Coupled LogicoscarAinda não há avaliações