Escolar Documentos

Profissional Documentos

Cultura Documentos

7 A H-Bridge for DC-Motor Applications

Enviado por

João JoséDescrição original:

Título original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

7 A H-Bridge for DC-Motor Applications

Enviado por

João JoséDireitos autorais:

Formatos disponíveis

7 A H-Bridge for DC-Motor Applications

TLE 6209 R

Data Sheet

1 1.1

Overview Features

Delivers up to 6 A continuous and 7 A peak current Optimized for DC motor management applications Very low RDS ON of typ. 150 m @ 25 C per switch Operates at supply voltages of up to 40V P-DSO-20-12 Overvoltage Protection against transients up to 45 V Outputs fully short circuit protected Standard SPI-Interface, daisy chain capability Adjustable chopper current regulation of up to 7 A Temperature monitor with prewarning, warning and shutdown Over- and Undervoltage-Lockout Open load detection Detailed load failure diagnosis by SPI Minimized power dissipation due to active free-wheeling Low EMI due to voltage slope regulation Very low current consumption (typ. 20 A @ 25 C) in stand-by (Inhibit) mode Enhanced power P-DSO-Package Ordering Code Q67007-A9488 Package P-DSO-20-12

Type TLE 6209 R Functional Description

The TLE 6209 R is an integrated power H-Bridge with D-MOS output stages for driving bidirectional loads such as DC-Motors. The design is based on Infineons Smart Power Technology SPT which allows bipolar, CMOS and power D-MOS devices on the same monolithic circuit. Operation modes forward (cw), reverse (ccw) and brake are invoked by two control pins PWM and DIR. Protection and a reliable diagnosis of overcurrent, openload, short-circuit to ground, to the supply voltage or across the load are integrated. Detailed diagnostic information is given via the 8 bit SPI status word. An integrated chopper current limitation limits the current e.g. to reduce power dissipation during mechanical block of a DC

Data Sheet, Version 3.0

2001-10-15

TLE 6209 R

motor. Several device parameters can be set by the SPI control word. A three-level temperature monitoring with prewarning, warning and shutdown is included for controlled operation under critical power loss conditions. The full protection and diagnosis capability make the device suitable especially for safety relevant applications, e.g. in automotive ECUs. 1.2 Pin Configuration (top view)

TLE 6209R

1

GND OUT 1 OUT 1 VS SCLK SDI SDO CSN INH GND

GND OUT 2 OUT 2 VS DRV VCC PWM DIR DIS GND

20

19

18

17

16

15

14

13

12

10

11

Metal slug, connected to GND

Pin Definitions and Functions

VS

DRV SDI SCLK OUT PWM DIS

Power Supply Voltage Input for Charge pump buffer capacitor Serial Data Input Serial Clock Input Power Output PWM Input Disable Input

VCC

GND SDO CSN DIR INH

5 V Logic Supply Ground Serial Data Output Chip-Select-Not Input Direction Input Inhibit

Data Sheet, Version 3.0

2001-10-15

TLE 6209 R

1.2.1 1, 10, 11, 20 2,3 4,17

Pin Definitions and Functions GND OUT1 Ground; internally connected to cooling tab (heat slug); to reduce thermal resistance place cooling areas and thermal vias on PCB. Output 1; output of D-MOS half bridge 1; external connection between pin 2 and pin 3 is necessary. Power supply; needs a blocking capacitor as close as possible to GND; 47 F electrolytic in parallel to 220 nF ceramic is recommended; external connection between pin 4 and pin 17 is necessary. Serial clock input; clocks the shiftregister; SCLK has an internal active pull down and requires CMOS logic levels Serial data input; receives serial data from the control device; serial data transmitted to SDI is an 8 bit control word with the Least Significant Bit (LSB) being transferred first; the input has an active pull down and requires CMOS logic levels; SDI will accept data on the falling edge of SCLK-signal; see Table 1 for input data protocol. Serial-Data-Output; this tri-state output transfers diagnosis data to the control device; the output will remain tri-stated unless the device is selected by a low on Chip-Select-Not (CSN); SDO state changes on the rising edge of SCLK; see Table 4 for diagnosis protocol. Chip-Select-Not input; CSN is an active low input; serial communication is enabled by pulling the CSN terminal low; CSN input should only be transitioned when SCLK is low; CSN has an internal active pull up and requires CMOS logic levels. Inhibit input; has an internal pull down; device is switched in standby condition by pulling the INH terminal low. Disable input; has an internal pull up; the output stages are switched in tristate condition by pulling the DIS terminal high. Direction input; has an internal pull down; TTL/CMOS compatible input. PWM input; has an internal pull down; TTL/CMOS compatible input. Logic supply voltage; needs a blocking capacitor as close as possible to GND; 10 F electrolytic in parallel to 220 nF ceramic is recommended.

Pin No. Symbol Function

VS

5 6

SCLK SDI

SDO

CSN

9 12 13 14 15

INH DIS DIR PWM

VCC

Data Sheet, Version 3.0

2001-10-15

TLE 6209 R

1.2.1 16 18,19

Pin Definitions and Functions (contd) DRV OUT2 Drive; Input for external charge pump capacitor CDRV Output 2; output of D-MOS half bridge 2; external connection between pin 2 and pin 3 is necessary.

Pin No. Symbol Function

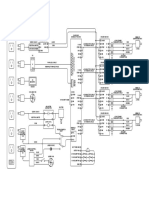

1.3

Functional Block Diagram

VCC 15 Bias

DRV 16 Charge Pump

VS 4,17

INH DIS CSN SDI SCLK SDO PWM DIR

9 12 8 6 5 7 14 13

Inhibit

FaultDetect Driver 8 Bit Logic and Latch & GateControl 18,19 OUT 2 2,3

S P I

OUT 1

Direct Input UV OV TSD 1,10,11,20 GND 1

Figure 1

Block Diagram

Data Sheet, Version 3.0

2001-10-15

TLE 6209 R

2 2.1

Circuit Description Serial Peripheral Interface (SPI)

The SPI is used for bidirectional communication with a control unit. The 8-bit programming word or control word (see Table 1) is read in via the SDI serial data input, and this is synchronized with the serial clock input SCLK. The status word appears synchronously at the SDO serial data output (see Table 4). The transmission cycle begins when the chip is selected with the chip-select-not (CSN) input (H to L). When the CSN input changes from L to H, the word which has been read into the shift register becomes the control word. The SDO output switches then to tristate status, thereby releasing the SDO bus circuit for other uses. The SPI allows to parallel multiple SPI devices by using multiple CSN lines. Due to the full duplex shift register, the TLE 6209 R can also be used in daisy-chain configuration. The settings made by the SPI control word become active at the end of the SPI transmission and remain valid until a different control word is transmitted or a power on reset occurs. At each SPI transmission, the diagnosis bits as currently valid in the error logic are transmitted. The behavior of the diagnosis bits is described in Section 2.5. Table 1 Bit 7 6 5 4 3 2 1 0 Status Register Reset: H = reset OVLO: H = on, L = off not used MSB of 2bit chopper-OFF-time LSB of 2bit chopper-OFF-time PWM Operation mode: H = Fast decay, L = Slow decay MSB of 2 bit chopper current limit LSB of 2 bit chopper current limit Input Data Protocol

Data Sheet, Version 3.0

2001-10-15

TLE 6209 R

Table 2 Bit 1 0 0 1 1

Programmable Chopper Current Limit IL_xx Bit 0 0 1 0 1 Current limit

IL_00 IL_01 IL_10 IL_11

Note: For actual values, see page 16 Table 3 Bit 4 0 0 1 1 Programmable Chopper OFF-time tOFF_xx Bit 3 0 1 0 1 Chopper-OFF-time

tOFF_00 tOFF_01 tOFF_10 tOFF_11

Note: For actual values, see page 16

Table 4 Bit 7 6 5 4 3 2 1 0

Diagnosis Data Protocol H = Error/L = no error Power supply fail not used, always H Short to VS or across the load Short to GND Open load MSB of Temperature Monitoring LSB of Temperature Monitoring Error-Flag

Table 5 Bit 2 0 0

Temperature Monitoring Bit 1 0 1 Chip Temperature Below Prewarning Temperature Prewarning

Data Sheet, Version 3.0

2001-10-15

TLE 6209 R

Table 5 Bit 2 1 1 2.2 2.2.1

Temperature Monitoring Bit 1 0 1 Supply Logic Supply Voltage, Power-On-Reset Chip Temperature Temperature Warning Overtemperature Shutdown

The logic is supplied with 5 V by the VCC pin, separated from the power stage supply VS. The advantage of this system is that information stored in the logic remains intact even in the event of failures in the supply voltage VS. The power supply failure information can be read out via the SPI. If VCC falls below typically 4.5 V, the logic is shut down, all internally stored data is deleted and the Output Stages are switched to tristate. The IC is restarted on rising VCC with a hysteresis of typically 80 mV After this restart at increasing VCC, or if the device is activated after having been set into inhibit mode (INH L to H), the IC is initialized by Power-On-Reset (POR). After POR, all SPI control bits are set to L. This setting remains valid until first SPI communication. Also the error bits are reset by POR. 2.2.2 Power Supply Voltage

The power stages are connected to the supply voltage VS. This voltage is monitored by over voltage (OV) and under voltage (UV) comparators as described in Section 2.5.6. The power supply voltage needs a blocking capacitor to GND. 2.3 2.3.1 Direct Inputs Inhibit (sleep mode)

The INH input can be used to cut off the complete IC. By pulling the INH input to low, the power stages are switched to tristate, and the current consumption is reduced to just a few A at both the VS and the VCC input. It also leads to the loss of any data stored. The TLE 6209 R is reinitialized with POR if INH is put to high again. The pin has an internal pull-down. 2.3.2 Disable

The DIS input can be used to disable the output stages. By pulling the DIS input to high the power stages are switched to tristate, regardless of the signals at the DIR and PWM inputs. The DIS input can be used as an emergency disable without resetting the SPI data stored in the IC. It has an internal pull-up.

Data Sheet, Version 3.0

2001-10-15

TLE 6209 R

2.3.3

Direction and PWM

The power stages are controlled by the direct inputs DIR and PWM as given in Table 6 and further illustrated in Figure 2. The DIR input gives the direction of output current, while the PWM input controls whether the current is increased or reduced. The SPI control bit 2 sets the decay mode, i.e. determines what happens if PWM = L. In pulsewidth modulated applications, this control scheme allows to supply the PWM-signal always through the same port, using less controller resources. Table 6 DIR 0 0 1 1 0 0 1 1 Functional Truth Table PWM 1 0 1 0 1 0 1 0 1 (fast decay) MODE (Bit 2) 0 (slow decay) OUT1 H H L H H L L H OUT2 L H H H L H H L Comments Motor turns clockwise Freewheel with slow decay Motor turns counterclockwise Freewheel with slow decay Motor turns clockwise Fast decay Motor turns counterclockwise Fast decay

Slow Decay PWM = H PWM = L

Fast Decay PWM = H PWM = L

Figure 2

DIR/PWM Control with Slow- and Fast Decay

Data Sheet, Version 3.0

2001-10-15

TLE 6209 R

2.4

Power Stages

The output stages consist of a DMOS H-bridge built by two highside switches and two lowside switches. Integrated circuits protect the outputs against overcurrent and overtemperature if there is a short-circuit to ground or to the supply voltage or across the load. Positive and negative voltage spikes, which occur when switching inductive loads, are limited by integrated freewheeling diodes. 2.4.1 Charge Pump

To realize the fast switching times, the charge pump, which generates the voltage necessary to switch on the n-channel D-MOS high-side switches, must be highly efficient. It requires an external capacitor CDRV which is connected to VS and the charge pump buffer input, DRV. It should be placed as close to the pins as possible. 2.4.2 Chopper Current Limitation

To limit the output current, a chopper current limitation is integrated as shown in Figure 3. The current is measured by sense cells integrated in the low-side switches. As soon the current limit IL is reached, the low-side switch is switched off for a fixed time tOFF. IL and tOFF can be set by the SPI control bits 0,1, 3 and 4.

current limit IL IOUT

off-time tOFF time

Figure 3 2.4.3

Chopper current limitation Active Freewheeling

When drivng inductive loads with PWM operation, the dissipated power can be significantly reduced by activating the transistor located parallel to the internal freewheeling diode. This is realized in the TLE 6209 R. When switching an output from L to H, the high-side switch is turned on after a certain dead-time to avoid cross currents flowing through the half bridge.

Data Sheet, Version 3.0

2001-10-15

TLE 6209 R

2.5 2.5.1

Protection and Diagnosis Short of Output to Ground

The high-side switches are protected against a short of the output to ground by an over current shutdown. If a high-side switch is turned on and the current rises above the highside shutdown threshold ISDH for longer than the shutdown delay time tdOC, all output transistors are turned off and bit 4 the SPI diagnosis word is set. During the delay time, the current is limited to ISC (typically 20 A). The output stages stay off and the error bit set until a status register reset (bit 7 of SPI control word) is received or a power-on reset is performed. 2.5.2 Short of Output to VS

Due to the chopper current regulation, the low-side switches are protected against a short to the supply voltage. To detect the short, the first time the current limit is reached, the off-command for the low-side switch is blanked out for 10 s. If the current rises above the low-side shutdown threshold ISDL during this time, all output transistors are turned off and bit 5 in the SPI diagnosis word is set. The value of the shutdown threshold depends on the current limit that is set via the SPI. The shutdown threshold is 1 A higher than the current limit. The output stages stay off and the error bit set until a status register reset (bit 7 of SPI control word) is received or a power-on reset is performed. 2.5.3 Short Across the Load

The short circuit protection circuits of the high- and low-side switches work independently of each other. In most cases, a short across the load will be detected as a short to VS because of the longer filter time in the high-side switches tdOC and the higher shutdown threshold ISDH. 2.5.4 Open Load

If the current through the low side transistor is lower than the reference current IdOL in ON-state (PWM = H), a timer is started. After a filter time tdOC an open load failure will be recognized and the status bit 3 is set. If the current exceeds the reference current IdOL the open load timer is reset. If the H-bridge is switched to OFF-state (PWM = L) the timer is stopped but not reset. The timer continues if the H-bridge is switched to ON-state again. There is no reset of the open load timer if the direction is changed using the DIR input in open load condition. The open load error bit is latched and can be reset by the status register reset bit 7 of the SPI control word or a POR. 2.5.5 Temperature Monitoring

Temperature sensors are integrated in the power stages. The temperature monitoring circuit compares the measured temperature to the prewarning, warning and shutdown

Data Sheet, Version 3.0

10

2001-10-15

TLE 6209 R

thresholds. As soon as a threshold is reached, the according status bits are set in the SPI diagnosis word (c.f. Table 5). If the overtemperature shutdown threshold is reached, the output stages are turned off. The temperature monitoring messages and the over temperature shutdown are latched and can be reset by the status register reset bit 7 of the SPI control word or a POR. 2.5.6 Power Supply Fail

The power supply Voltage is monitored for over- and under voltage lockout: Under Voltage Lockout If the supply voltage VS drops below the switch off voltage VUV OFF, all output transistors are switched off and the power supply fail bit (bit 7 of the SPI diagnosis word) is set. If VS rises again and reaches the switch on voltage VUV ON, the power stages are restarted. The error bit, however, is latched and has to be reset by the status register reset bit 7 of the SPI control word. Over Voltage Lockout If the supply voltage VS rises above the switch off voltage VOV OFF, all output transistors are switched off and the power supply fail bit (bit 7 of the SPI diagnosis word) is set. If VS falls again and reaches the switch on voltage VOV ON, the power stages are restarted. The error bit, however, is latched and has to be reset by the status register reset bit 7 of the SPI control word. The OVLO is only active if control bit 6 is H. If the bit is low, the OVLO is deactivated. 2.5.7 Error Flag

Bit 0 of the SPI diagnosis word is an OR of the status bits 1 to 7. It can be read out without full SPI communication as described in Figure 8.

Data Sheet, Version 3.0

11

2001-10-15

TLE 6209 R

3 3.1 Parameter

Characteristics Absolute Maximum Ratings Symbol Limit Values min. max. Unit Remarks

Voltages Supply voltage Supply voltage Logic supply voltage Logic input voltages (SDI, SCLK, CSN, INH, DIS, PWM, DIR) Logic output voltage (SDO) Output voltage (OUT1, OUT2) Charge pump buffer voltage (DRV) Currents Output current (cont.) Output current (peak)

VS VS VCC VI

0.3 1 0.3 0.3

40 45 5.5 5.5

V V V V

t < 0.5 s; IS > 2 A 0 V < VS < 40 V 0 V < VS < 40 V 0 V < VCC < 5.5 V

0 V < VS < 40 V 0 V < VCC < 5.5 V 0 V < VS < 40 V 0 V < VS < 40 V

VO VOUT VDRV

0.3

5.5

0.3 V VS + 1,5V

VS

0.3 V

VS +

15 V

IOUT IOUT

A A

internally limited, see page 16 and page 17.

Temperatures Junction temperature Storage temperature

Tj Tstg

40 50

150 150

C C

Note: Maximum ratings are absolute ratings; exceeding any one of these values may cause irreversible damage to the integrated circuit.

Data Sheet, Version 3.0

12

2001-10-15

TLE 6209 R

3.2 Parameter

Operating Range Symbol Limit Values min. max. V V/s V After VS rising above VUV ON Outputs in tristate Outputs in tristate Unit Remarks

Supply voltage Supply voltage slew rate Logic supply voltage Supply voltage increasing Supply voltage decreasing Logic input voltage (SDI, SCLK, CSN, INH) SPI clock frequency Junction temperature Thermal Resistances Junction pin Junction ambient

VS

dVS /dt

VUV OFF 40

10 4.75 0.3 0.3 0.3 40 10 5.50

VCC VS VS VI fCLK Tj

VUV ON V VUV OFF V VCC V

2 150 MHz

RthjC RthjA

1.5 50

K/W K/W

measured to pin 1, 10, 11, 20

Data Sheet, Version 3.0

13

2001-10-15

TLE 6209 R

3.3

Electrical Characteristics

8 V < VS < 40 V; 4.75 V < VCC < 5.25 V; INH = High; all outputs open; 40 C < Tj < 150 C; unless otherwise specified Parameter Symbol Limit Values min. Current Consumption Quiescent current Quiescent current typ. max. Unit Test Conditions

IS IS

10

50 30

A A

INH = Low; VS = 13.2 V INH = Low; VS = 13.2 V; Tj = 25 C INH = Low

Logic-Supply current Logic-Supply current Supply current

ICC ICC IS

2.0 2.8

20 4.0 5.0

A

mA mA

Over- and Under-Voltage Lockout UV-Switch-ON voltage UV-Switch-OFF voltage UV-ON/OFF-Hysteresis OV-Switch-OFF voltage OV-Switch-ON voltage OV-ON/OFF-Hysteresis

VUV ON VUV OFF VUV HY VOV OFF VOV ON VOV HY

4.4 0.2 34 28

5.4 4.9 0.5 37 32 5.0

5.7 5.2 40 36

V V V V V V

VS increasing VS decreasing VUV ON VUV OFF VS increasing VS decreasing VOV OFF VOV ON

Data Sheet, Version 3.0

14

2001-10-15

TLE 6209 R

3.3

Electrical Characteristics (contd)

8 V < VS < 40 V; 4.75 V < VCC < 5.25 V; INH = High; all outputs open; 40 C < Tj < 150 C; unless otherwise specified Parameter Symbol Limit Values min. Outputs OUT1-2 Static Drain-Source-On Resistance Source (High-Side) IOUT = 3 A typ. max. Unit Test Conditions

RDS ON H

140

170

5.2 V < VS < 40 V Tj = 25 C; CDRV = 33 nF 5.2 V < VS < 40 V CDRV = 33 nF 5.2 V < VS < 40 V Tj = 25 C; CDRV = 33 nF 5.2 V < VS < 40 V CDRV = 33 nF

Sink (Low-Side) IOUT = 3 A

280 160

m m

RDS ON L

130

270

Clamp Diodes Forward Voltage Upper Lower

VFU VFL

1.0 1.0

1.5 1.5

V V

IF = 3 A IF = 3 A

Data Sheet, Version 3.0

15

2001-10-15

TLE 6209 R

3.3

Electrical Characteristics (contd)

8 V < VS < 40 V; 4.75 V < VCC < 5.25 V; INH = High; all outputs open; 40 C < Tj < 150 C; unless otherwise specified Parameter Symbol Limit Values min. Open Circuit/Underload Detection Detection current Delay time Current Limits Current limit Current limit Current limit Current limit typ. max. Unit Test Conditions

IOCD tdOC

30 2

130 8

mA ms

IL_00 IL_01 IL_10 IL_11

3.4 4.25 5.1 5.95

4 5 6 7

4.6 5.75 6.9 8.05

A A A A

Bit 0 = L; Bit 1 = L; Bit 0 = H; Bit 1 = L; Bit 0 = L; Bit 1 = H; Bit 0 = H; Bit 1 = H;

Low-Side Switch Overcurrent Shutdown Threshold

ISDL

0.5

1.0

1.5

ISDL = ISDL - IL

Note: low-side shutdown threshold is guaranteed by design Switch-OFF Time during Current Limitation (Chopper OFF-Time) OFF-time OFF-time OFF-time OFF-time

tOFF_00 tOFF_01 tOFF_10 tOFF_11

16 32 48 64

24 43 62 80

28 51 74 96

s s s s

Bit 3 = L; Bit 4 = L; Bit 3 = H; Bit 4 = L; Bit 3 = L; Bit 4 = H; Bit 3 = H; Bit 4 = H;

Data Sheet, Version 3.0

16

2001-10-15

TLE 6209 R

3.3

Electrical Characteristics (contd)

8 V < VS < 40 V; 4.75 V < VCC < 5.25 V; INH = High; all outputs open; 40 C < Tj < 150 C; unless otherwise specified Parameter Symbol Limit Values min. High-Side Switch Overcurrent High-side shutdown threshold Shutdown delay time Short circuit current typ. max. Unit Test Conditions

ISDH tdSD ISC

8 15

12 25

18 40 25

during tdSD

s

A

Note: For short circuit current definition, see Figure 5. Short circuit current is guaranteed by design Leakage Current / Output Current in Tristate Source-Output-Stage Sink-Output-Stage

IQLH IQLL

120 50 0.5

A

mA

VOUT = 0 V VOUT = VS

Output Delay Times (device not in stand-by for t > 1 ms) High-side ON High-side OFF Low-side ON Low-side OFF

td ON H td OFF H td ON L td OFF L

4 0.6 2 2.5

10 1 3.5 4

s s s s

VS = 13.2 V,

Resistive load of 12

Output Switching Times (device not in stand-by for t > 1 ms) High-side switch rise time High-side switch fall time Low-side switch rise time Low-side switch fall time

tRISE H tFALL H tRISE L tFALL L

2 2

1.8 0.2 6.5 4.3

3.5 0.8 11 6.5

s s s s

VS = 13.2 V,

Resistive load of 12

Note: For switching time definitions, see Figure 6.

Data Sheet, Version 3.0

17

2001-10-15

TLE 6209 R

3.3

Electrical Characteristics (contd)

8 V < VS < 40 V; 4.75 V < VCC < 5.25 V; INH = High; all outputs open; 40 C < Tj < 150 C; unless otherwise specified Parameter Symbol Limit Values min. Inhibit Input typ. max. Unit Test Conditions

VIINHH L-input voltage threshold VIINHL Hysteresis of input voltage VIINHHY IIINHL Pull down current (low) Pull down current (high) IIINHH

H-input voltage threshold Disable Input

0.2 50 10

300 25

0.7 500 50 80

VCC VCC

mV

A A

VIINH = 0.2 VCC VIINH = 0.7 VCC

VIDISH VIDISL L-input voltage threshold Hysteresis of input voltage VIDISHY IIDISH Pull up current (high) Pull up current (low) IIDISL

H-input voltage threshold Direction/PWM Input

0.2 50 50 50

300 25

0.7 500 10

VCC VCC

mV

A A

VIDIS = 0.7 VCC VIDIS = 0.2 VCC

VIH VIL L-input voltage threshold Hysteresis of input voltage VIHY II Pull down current (low) Pull down current (high) II

H-input voltage threshold

0.2 50 10

300 25

0.7 500 50 50

VCC VCC

mV

A A

VI= 0.2 VCC VI= 0.7 VCC

Data Sheet, Version 3.0

18

2001-10-15

TLE 6209 R

3.3

Electrical Characteristics (contd)

8 V < VS < 40 V; 4.75 V < VCC < 5.25 V; INH = High; all outputs open; 40 C < Tj < 150 C; unless otherwise specified Parameter Symbol Limit Values min. SPI-Interface Delay Time from Stand-by to Data In/Power on Reset Setup time typ. max. Unit Test Conditions

tset

100

Logic Inputs SDI, SCLK and CSN H-input voltage threshold

VIH VIL L-input voltage threshold Hysteresis of input voltage VIHY Pull up current at pin CSN IICSNH

(high) Pull up current at pin CSN (low)

0.2 50 50 50 10

300 25 25 10

0.7 500 10 50 50 15

VCC VCC

mV

A A A A

pF

VCSN = 0.7 VCC VCSN = 0.2 VCC VSDI (VSCLK) = 0.2 VCC VSDI (VSCLK) = 0.7 VCC 0 V < VCC < 5.25 V

IICSNL

Pull down current at pin SDI IISDIL and SCLK (low) (IISCLKL)

Pull down current at pin SDI IISDIH and SCLK (high) (IISCLKH) Input capacitance at pin CSN, SDI or SCLK

CI

Note: Input capacitances are guaranteed by design.

Data Sheet, Version 3.0

19

2001-10-15

TLE 6209 R

3.3

Electrical Characteristics (contd)

8 V < VS < 40 V; 4.75 V < VCC < 5.25 V; INH = High; all outputs open; 40 C < Tj < 150 C; unless otherwise specified Parameter Symbol Limit Values min. Logic Output SDO H-output voltage level L-output voltage level Tri-state leakage current Tri-state input capacitance typ. max. Unit Test Conditions

VSDOH VSDOL ISDOLK CSDO

VCC

1.0 10

VCC

0.85 0.25 10

0.4 10 15

V V

ISDOH = 1 mA ISDOL = 1.6 mA VCSN = VCC 0 V < VSDO < VCC VCSN = VCC 0 V < VCC < 5.25 V

A

pF

Note: Input capacitances are guaranteed by design.

Data Sheet, Version 3.0

20

2001-10-15

TLE 6209 R

3.3

Electrical Characteristics (contd)

8 V < VS < 40 V; 4.75 V < VCC < 5.25 V; INH = High; all outputs open; 40 C < Tj < 150 C; unless otherwise specified Parameter Symbol Limit Values min. Serial Data Input Timing Serial Clock period Serial Clock high time Serial Clock low time Serial Clock low before CSN low CSN setup time SCLK setup time Clock low after CSN high SDI setup time SDI hold time Input signal rise time at pin SDI, SCLK and CSN typ. max. Unit Test Conditions

tPSCLK tSCLKH tSCLKL tbef tlead tlag tbeh tSDISU tSDIHO trSIN

500 250 250 250 250 250 250 125 125

100 100

ns ns ns ns ns ns ns ns ns ns ns

tfSIN Input signal fall time at pin SDI, SCLK and CSN

Serial Data Output Timing SDO rise time SDO fall time SDO enable time SDO disable time SDO valid time

trSDO tfSDO tENSDO tDISSDO tVASDO

25 25 50

50 50 125 125 125

ns ns ns ns ns

CL = 100 pF CL = 100 pF

low impedance high impedance

VDO < 0.2 VCC; VDO > 0.7 VCC; CL = 100 pF

Data Sheet, Version 3.0

21

2001-10-15

TLE 6209 R

3.3

Electrical Characteristics (contd)

8 V < VS < 40 V; 4.75 V < VCC < 5.25 V; INH = High; all outputs open; 40 C < Tj < 150 C; unless otherwise specified Parameter Symbol Limit Values min. typ. max. Unit Test Conditions

Thermal Prewarning, Warning and Shutdown Thermal prewarning junction temperature Temperature prewarning hysteresis Thermal warning junction temperature Temperature prewarning hysteresis

TjPW

T

120 140 160 1.07 1.06

140 20 160 20 180 20 1.14 1.13

160 180 200

C

K

TjW

T

C

K

Thermal shutdown junction TjSD temperature Temperature shutdown hysteresis Ratio of W to PW temperature Ratio of SD to W temperature

C

K

TjW / TjPW TjSD / TjW

Note: Temperature thresholds are guaranteed by design.

Data Sheet, Version 3.0

22

2001-10-15

TLE 6209 R

Diagrams

V 13.2V 9V 9V

VOUT

0

tOFF_xx

IOUT

Figure 4

Switch-OFF time during current limitation (chopper OFF-time)

Vs

V

Vs

5V PWM 0

OUT

tdSD IOUT ISDH

GND

ISC

Figure 5

Short circuit of high-side switch to GND

Data Sheet, Version 3.0

23

2001-10-15

TLE 6209 R

V 5 PW M Input 0 50% 50%

t RISE

100% 90%

t F ALL

90%

V O UT

10% 10%

t d1

D IR = L / H => V O UT = V O UT 1/2 R esistive load to V s => t RISE = t R ISE L , t FALL = t FALL L t d1 = t d O F F L , t d2 = t d O N L

t d2

Resistive load to G N D => t RISE = t R ISE H , t F ALL = t F ALL H t d1 = t d O N H , t d2 = t d O F F H

Figure 6

Output Delay and Switching Time Definitions

CSN High to Low & rising edge of SCLK: SDO is enabled. Status information is transfered to Output Shift Register

CSN time CSN Low to High: Data from Shift-Register is transfered to Output Driver Logic

SCLK

actual Data SDI 0 1 2 3 4 5 6 7

new Data 0 +

SDI: Data will be accepted on the falling edge of CLK-Signal previous Status SDO _ 0 1 _ _ 2 _ 3 _ 4 _ 5 _ 6 _ 7 actual Status 0

SDO: State will change on the rising edge of CLK-Signal

old Data

actual Data

Figure 7

Standard Data Transfer Timing

Data Sheet, Version 3.0

24

2001-10-15

TLE 6209 R

CSN High to Low & SCLK stays Low: Status information of Data Bit 0 ( Error Flag ) is transfered to SDO CSN time

SCLK

SDI SDI: Data is not accepted

SDO

tristate

0 _

tristate SDO: Status information of Data Bit 0 ( Error-Flag ) will stay as long as CSN is low

Figure 8

Timing for Error Detection Only

0.7 VCC

CSN

0.2 VCC tSCLKH 0.7 VCC

SCLK

0.2 VCC tlead tbef tSDISU tSDIHO 0.7 VCC tSCLKL tlag tbeh

SDI

Dont care

Valid

Dont care

Valid

Dont care

0.2 VCC

Figure 9

SPI-Input Timing

Data Sheet, Version 3.0

25

2001-10-15

TLE 6209 R

trSIN

tfSIN 0.7 VCC

SCLK

trSDO

50 % 0.2 VCC

0.7 VCC

SDO

( low to high )

0.2 VCC tVASDO tfSDO 0.7 VCC

SDO

( high to low )

0.2 VCC

Figure 10

DO Valid Data Delay Time and Valid Time

tfSIN trSIN 0.7 VCC

CSN

50 % 0.2 VCC tENSDO tDISSDO 10 k Pullup to VCC

SDO

50 %

tENSDO

tDISSDO 10 k Pulldown 50 % to GND

SDO

Figure 11

SDO Enable and Disable Time

Data Sheet, Version 3.0

26

2001-10-15

TLE 6209 R

Application

Watchdog Reset Q

TLE 4278G

D CD 10nF

Vbat

Z39 GND

100F

100nF

CQ 22F

CDRV WD R VCC VCC 15 DRV 16 33nF VS 4,17

Bias

Charge Pump

INH MicroController for EMS/ETC Function DIS CSN SDI SCLK SDO

9 12 8 6 5 7

Inhibit

FaultDetect

2,3 S P I 8 Bit Logic and Latch Driver & Gate-Control 18,19

OUT 1

OUT 2

PWM DIR

14 13 Direct Input UV 1

GND

OV Micro-Controller for Evaluation Process Monitoring

TSD

GND

GND

Figure 12

Application Circuit

Data Sheet, Version 3.0

27

2001-10-15

TLE 6209 R

Package Outlines P-DSO-20-12 (Plastic Dual Small Outline Package)

3.5 max.

1.3

0.25 +0.0

-0.027

1.2 -0.3

0 +0.15 3.25 0.1

11 0.15 1) 2.8

15.74 0.1 1.27 0.4

+0.13

0.1 0.25

M

6.3 14.2 0.3

A 20x

Heatsink 0.95 0.15 0.25

M

20

11

Index Marking

1 1 x 45

10

A 1) Does not include plastic or metal protrusion of 0.15 max. per side

15.9 0.15 1)

GPS05791

Sorts of Packing Package outlines for tubes, trays etc. are contained in our Data Book Package Information. SMD = Surface Mounted Device Data Sheet, Version 3.0 28

Dimensions in mm 2001-10-15

5 3

B

This datasheet has been download from: www.datasheetcatalog.com Datasheets for electronics components.

Você também pode gostar

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Ainda não há avaliações

- Circuito Integrado Tle6368Documento58 páginasCircuito Integrado Tle6368Angy GiraldoAinda não há avaliações

- Agis User Manula M210 P13Documento28 páginasAgis User Manula M210 P13Ante MandićAinda não há avaliações

- Ficha Tecnica Terminales Tipo Codo 200A 15KV ElastimoldDocumento4 páginasFicha Tecnica Terminales Tipo Codo 200A 15KV ElastimoldCarlos Alirio Vera AAinda não há avaliações

- Winstar 98 Motor 3.8LTSDocumento5 páginasWinstar 98 Motor 3.8LTSRogelio Arenas100% (1)

- 2006 Toyota Rav4 70Documento415 páginas2006 Toyota Rav4 70Pușcă MartinAinda não há avaliações

- ssc9503 10 12Documento2 páginasssc9503 10 12tecnologo456Ainda não há avaliações

- 2011 Dodge Avenger Express 2011 Dodge Avenger Express: Theory of OperationDocumento171 páginas2011 Dodge Avenger Express 2011 Dodge Avenger Express: Theory of Operationjosecuellar69Ainda não há avaliações

- Taiko-Tb2 Rev070717 PDFDocumento1 páginaTaiko-Tb2 Rev070717 PDFdelioymanuelAinda não há avaliações

- Diagrama de Coneccion de Motores para CNCDocumento1 páginaDiagrama de Coneccion de Motores para CNCFreddy CajasAinda não há avaliações

- NacelleDocumento7 páginasNacellecarlitos232067% (3)

- Manual Tester Inova - 3340aDocumento76 páginasManual Tester Inova - 3340aCristopher Wlach ChacónAinda não há avaliações

- Laserline Alarm Mod 996Documento12 páginasLaserline Alarm Mod 996John Ha100% (1)

- Escape 2002 PDFDocumento4 páginasEscape 2002 PDFLuis GongoraAinda não há avaliações

- Comprehensive Component Monitor Diagnosis OverviewDocumento18 páginasComprehensive Component Monitor Diagnosis OverviewmongongoAinda não há avaliações

- MOSFET PA - PDF PDFDocumento16 páginasMOSFET PA - PDF PDFDoDuyBacAinda não há avaliações

- Avh-P5000dvd Installation Manual en FR de NL It EsDocumento98 páginasAvh-P5000dvd Installation Manual en FR de NL It EsJose Augusto Lobina RoncaglioloAinda não há avaliações

- Sony+XM 504Z+Car+Power+AmplifDocumento18 páginasSony+XM 504Z+Car+Power+AmplifB.r. ArturoAinda não há avaliações

- BCM Jeep Grand Cherokee WK 2014-1 PDFDocumento1 páginaBCM Jeep Grand Cherokee WK 2014-1 PDFJorge Antonio Guillen100% (1)

- USM Data Communication & Networks Test 1 SummaryDocumento2 páginasUSM Data Communication & Networks Test 1 SummaryAdron LimAinda não há avaliações

- Asd Relay Terminal IdentificationDocumento3 páginasAsd Relay Terminal IdentificationgtranAinda não há avaliações

- Codigos de Falla Caravan 1996 PDFDocumento4 páginasCodigos de Falla Caravan 1996 PDFTizzie ContrerasAinda não há avaliações

- Read Write Srs Mcu Can EngDocumento13 páginasRead Write Srs Mcu Can EngdongvacAinda não há avaliações

- P&D RussiaVersionDocumento32 páginasP&D RussiaVersionMilind PatilAinda não há avaliações

- Spirit 92 2.5L PDFDocumento1 páginaSpirit 92 2.5L PDFAgustinAinda não há avaliações

- 1998 Ford WindstarDocumento371 páginas1998 Ford WindstarJosé100% (1)

- 2GR-FE Engine CKP Sensor CodesDocumento7 páginas2GR-FE Engine CKP Sensor CodesYdelkadiasmela Dominguezmorel100% (1)

- Compal ZPT10 LA-B151P Rev 1.0 2014-01-14Documento48 páginasCompal ZPT10 LA-B151P Rev 1.0 2014-01-14uga_uga100% (1)

- Ec Harness ConectorDocumento15 páginasEc Harness ConectorHawkar SuleimanAinda não há avaliações

- Electric OsDocumento429 páginasElectric OsAleejandro VaargasAinda não há avaliações

- Lp133wh1 Tpd1 LGDocumento32 páginasLp133wh1 Tpd1 LGjohnel ruszkiAinda não há avaliações

- Diagrama de Arranque HondaDocumento1 páginaDiagrama de Arranque HondaJose NuñezAinda não há avaliações

- Nitro BMWX 647-2 Channel 3000wDocumento1 páginaNitro BMWX 647-2 Channel 3000wfornicadorsAinda não há avaliações

- Inter-Integrated Circuit & IR MLX90614 IN CCSDocumento17 páginasInter-Integrated Circuit & IR MLX90614 IN CCSem330Ainda não há avaliações

- Dodge Caliber Rele Bomba de GasolinaDocumento19 páginasDodge Caliber Rele Bomba de GasolinaJhonny TorralbaAinda não há avaliações

- Electrical Equipment: Engine Compartment Connection UnitDocumento106 páginasElectrical Equipment: Engine Compartment Connection UnitAlejandro ArangurenAinda não há avaliações

- Control del alternador diagram mc33888afDocumento2 páginasControl del alternador diagram mc33888afOliver lealAinda não há avaliações

- Hitachi Sh7055 Mec38-480 NissanDocumento8 páginasHitachi Sh7055 Mec38-480 NissanWilfredo QuispeAinda não há avaliações

- Wiring Diagram: E1 - Engine Control UnitDocumento3 páginasWiring Diagram: E1 - Engine Control UnitJez Pulis100% (1)

- APSM 1200 ManualDocumento15 páginasAPSM 1200 ManualHumberto Linares ChumaceroAinda não há avaliações

- MC 10162044 0001Documento5 páginasMC 10162044 0001Daniel rodriguez alayoAinda não há avaliações

- MAP HeliomarDocumento1 páginaMAP HeliomarUbiratan LoureiroAinda não há avaliações

- Ect (Sensor de Temperatura Del Refrigerante Chevrolet Tracker 2002Documento1 páginaEct (Sensor de Temperatura Del Refrigerante Chevrolet Tracker 2002gerber damianAinda não há avaliações

- V-Car Service Training Manual: Engine Performance Instructor GuideDocumento52 páginasV-Car Service Training Manual: Engine Performance Instructor GuideAlex PilcoAinda não há avaliações

- Datasheet On NGD8201AGDocumento9 páginasDatasheet On NGD8201AGAlexandre KaczanukAinda não há avaliações

- MANUAL TV LG 49UJ620T-DA - 1602 - 0102 - WebOS3.5Documento67 páginasMANUAL TV LG 49UJ620T-DA - 1602 - 0102 - WebOS3.5Olga Jeannette Riveros LealAinda não há avaliações

- Diagrama Conectores Interfaces NEXIQDocumento1 páginaDiagrama Conectores Interfaces NEXIQFrancisco VidalAinda não há avaliações

- Canbus and Mpu VersionsDocumento8 páginasCanbus and Mpu VersionsKarim Ahmed KhodjaAinda não há avaliações

- Sentra-2008 InglesDocumento18 páginasSentra-2008 InglesLuis HilachoqueAinda não há avaliações

- LCD Led Power Rsag7.820.2194Documento1 páginaLCD Led Power Rsag7.820.2194Mad_Max_HJAinda não há avaliações

- LIN Transceiver: Automotive and IndustrialDocumento19 páginasLIN Transceiver: Automotive and IndustrialRayan88Ainda não há avaliações

- CD 00003131Documento24 páginasCD 000031314131etasAinda não há avaliações

- 7 A H-Bridge For DC-Motor Applications TLE 6209 R: 1 1.1 FeaturesDocumento29 páginas7 A H-Bridge For DC-Motor Applications TLE 6209 R: 1 1.1 Featureswtn2013Ainda não há avaliações

- Infineon TLE6209R DS v03 02 enDocumento30 páginasInfineon TLE6209R DS v03 02 enRoger SegoAinda não há avaliações

- Tle6220gp DatasheetDocumento18 páginasTle6220gp Datasheetmaelo99999Ainda não há avaliações

- Dual Full-Bridge Driver: DescriptionDocumento13 páginasDual Full-Bridge Driver: DescriptionBaher Bassem MorkosAinda não há avaliações

- Multi-Voltage Processor Power Supply TLE 6361 G: Data SheetDocumento57 páginasMulti-Voltage Processor Power Supply TLE 6361 G: Data SheetСергецAinda não há avaliações

- MC 33186Documento21 páginasMC 33186Olga PlohotnichenkoAinda não há avaliações

- DRV 8834Documento30 páginasDRV 8834Anonymous 10cG5eRp8100% (1)

- LCD221SD Service ManualDocumento41 páginasLCD221SD Service Manual1cvbnmAinda não há avaliações

- Sort Set-In-Order Shine Standardize Sustain: What Is 5-S?Documento44 páginasSort Set-In-Order Shine Standardize Sustain: What Is 5-S?Angel David ChavezAinda não há avaliações

- Me5np PDFDocumento3 páginasMe5np PDFJoão JoséAinda não há avaliações

- Adjustable Speed Drives TutorialDocumento13 páginasAdjustable Speed Drives Tutorialapi-3765150100% (2)

- Asrwer dfsdfsdfsdqwqwqwqwqw2qwqw Qeqqweqweqwekjkj66777 222wewe111333222sdfasdf) Erwerwgwerg Erwerwerw Dsfa Dfa D 3rerweweDocumento1 páginaAsrwer dfsdfsdfsdqwqwqwqwqw2qwqw Qeqqweqweqwekjkj66777 222wewe111333222sdfasdf) Erwerwgwerg Erwerwerw Dsfa Dfa D 3rerweweJoão JoséAinda não há avaliações

- Info Stanford02 FpgasDocumento18 páginasInfo Stanford02 FpgasJoão JoséAinda não há avaliações

- Asrwer dfsdfsdfsdqwqwqwqwqw2qwqw Qeqqweqweqwekjkj 222111222sdfasdf) Erwerwgwerg Erwerwerw Dsfa Dfa D 3rerweweDocumento1 páginaAsrwer dfsdfsdfsdqwqwqwqwqw2qwqw Qeqqweqweqwekjkj 222111222sdfasdf) Erwerwgwerg Erwerwerw Dsfa Dfa D 3rerweweJoão JoséAinda não há avaliações

- Oriental Motor Motor Sizing CalculationsDocumento10 páginasOriental Motor Motor Sizing CalculationsKha VeenAinda não há avaliações

- Alimentaçãogeral4-01092016 Model PDFDocumento1 páginaAlimentaçãogeral4-01092016 Model PDFJoão JoséAinda não há avaliações

- White Paper FPGA vs. DSP Design Reliability and Maintenance: May 2007, Ver. 1.1 1Documento4 páginasWhite Paper FPGA vs. DSP Design Reliability and Maintenance: May 2007, Ver. 1.1 1Mahdi HallakAinda não há avaliações

- Copper Wire Install StandardDocumento70 páginasCopper Wire Install Standardcharlesc5746100% (1)

- Asrwer dfsdfsdfsdqwqwqwqwqw2qwqw Qeqqweqweqwekjkj66777 222111333222sdfasdf) Erwerwgwerg Erwerwerw Dsfa Dfa D 3rerweweDocumento1 páginaAsrwer dfsdfsdfsdqwqwqwqwqw2qwqw Qeqqweqweqwekjkj66777 222111333222sdfasdf) Erwerwgwerg Erwerwerw Dsfa Dfa D 3rerweweJoão JoséAinda não há avaliações

- Asrwer dfsdfsdfsdqwqwqwqwqw2qwqw Qeqqweqweqwekjkj66 222111333222sdfasdf) Erwerwgwerg Erwerwerw Dsfa Dfa D 3rerweweDocumento1 páginaAsrwer dfsdfsdfsdqwqwqwqwqw2qwqw Qeqqweqweqwekjkj66 222111333222sdfasdf) Erwerwgwerg Erwerwerw Dsfa Dfa D 3rerweweJoão JoséAinda não há avaliações

- Asrwer dfsdfsdfsdqwqwqwqwqw2qwqw Qeqqweqweqwekjkj 222222sdfasdf) Erwerwgwerg Erwerwerw Dsfa Dfa D 3rerweweDocumento1 páginaAsrwer dfsdfsdfsdqwqwqwqwqw2qwqw Qeqqweqweqwekjkj 222222sdfasdf) Erwerwgwerg Erwerwerw Dsfa Dfa D 3rerweweJoão JoséAinda não há avaliações

- Asrwer dfsdfsdfsdqwqwqwqwqw2qwqw Qeqqweqweqwekjkj 222111333222sdfasdf) Erwerwgwerg Erwerwerw Dsfa Dfa D 3rerweweDocumento1 páginaAsrwer dfsdfsdfsdqwqwqwqwqw2qwqw Qeqqweqweqwekjkj 222111333222sdfasdf) Erwerwgwerg Erwerwerw Dsfa Dfa D 3rerweweJoão JoséAinda não há avaliações

- Asrwer DFSDFSDFSDQWQWQWQWQWQWQW Qeqqweqweqwe Sdfasdf) Erwerwgwerg Erwerwerw Dsfa Dfa D 3rerweweDocumento1 páginaAsrwer DFSDFSDFSDQWQWQWQWQWQWQW Qeqqweqweqwe Sdfasdf) Erwerwgwerg Erwerwerw Dsfa Dfa D 3rerweweJoão JoséAinda não há avaliações

- Asrwer DFSDFSDFSDQWQWQWQWQWQWQW Qeqqweqweqwe Sdfasdf) Erwerwgwerg Erwerwerw Dsfa Dfa D 3rerweweDocumento1 páginaAsrwer DFSDFSDFSDQWQWQWQWQWQWQW Qeqqweqweqwe Sdfasdf) Erwerwgwerg Erwerwerw Dsfa Dfa D 3rerweweJoão JoséAinda não há avaliações

- Asrwer DFSDFSDFSDQWQWQWQWQWQWQW Qeqqweqweqwe Sdfasdf) Erwerwerw Dsfa Dfa D 3rerweweDocumento1 páginaAsrwer DFSDFSDFSDQWQWQWQWQWQWQW Qeqqweqweqwe Sdfasdf) Erwerwerw Dsfa Dfa D 3rerweweJoão JoséAinda não há avaliações

- Asrwer dfsdfsdfsdqwqwqwqwqw2qwqw Qeqqweqweqwe Sdfasdf) Erwerwgwerg Erwerwerw Dsfa Dfa D 3rerweweDocumento1 páginaAsrwer dfsdfsdfsdqwqwqwqwqw2qwqw Qeqqweqweqwe Sdfasdf) Erwerwgwerg Erwerwerw Dsfa Dfa D 3rerweweJoão JoséAinda não há avaliações

- As DFSDFSDFSDQWQWQWQWQWQWQW Qeqqweqweqwe Sdfasdf) Erwerwerw Dsfa Dfa D 3rerweweDocumento1 páginaAs DFSDFSDFSDQWQWQWQWQWQWQW Qeqqweqweqwe Sdfasdf) Erwerwerw Dsfa Dfa D 3rerweweJoão JoséAinda não há avaliações

- As DFSDFSDFSDQWQWQWQWQWQWQW Qeqqweqweqwe Sdfasdf) Erwerwerw 3rerweweDocumento1 páginaAs DFSDFSDFSDQWQWQWQWQWQWQW Qeqqweqweqwe Sdfasdf) Erwerwerw 3rerweweJoão JoséAinda não há avaliações

- As DFSDFSDFSDDocumento1 páginaAs DFSDFSDFSDJoão JoséAinda não há avaliações

- As DFSDFSDFSDQWQWQWQWQWQWQW Qeqqweqweqwe SdfasdfDocumento1 páginaAs DFSDFSDFSDQWQWQWQWQWQWQW Qeqqweqweqwe SdfasdfJoão JoséAinda não há avaliações

- 25LC160Documento21 páginas25LC160João JoséAinda não há avaliações

- As DFSDFSDFSD Qeqqweqweqwe SdfasdfDocumento1 páginaAs DFSDFSDFSD Qeqqweqweqwe SdfasdfJoão JoséAinda não há avaliações

- 1Documento1 página1João JoséAinda não há avaliações

- Automotive MCUs and MPUs 8 16 e 32 Bits Devices FreescaleDocumento2 páginasAutomotive MCUs and MPUs 8 16 e 32 Bits Devices FreescaleJoão JoséAinda não há avaliações

- 12Documento1 página12João JoséAinda não há avaliações

- InfineonDocumento89 páginasInfineonJoão JoséAinda não há avaliações

- Artistic Real PDFDocumento1 páginaArtistic Real PDFJoão JoséAinda não há avaliações

- Freescale Diversos Componentes para Eletronica Embarcada AutomotivaDocumento36 páginasFreescale Diversos Componentes para Eletronica Embarcada AutomotivaJoão JoséAinda não há avaliações

- Onsemi ATX PSU DesignDocumento37 páginasOnsemi ATX PSU Designusuariojuan100% (1)

- SDLC - Agile ModelDocumento3 páginasSDLC - Agile ModelMuhammad AkramAinda não há avaliações

- Word Formation - ExercisesDocumento4 páginasWord Formation - ExercisesAna CiocanAinda não há avaliações

- Acute Care Handbook For Physical Therapists 5Th Edition Full ChapterDocumento41 páginasAcute Care Handbook For Physical Therapists 5Th Edition Full Chaptergloria.goodwin463100% (20)

- ARCH1350 Solutions 6705Documento16 páginasARCH1350 Solutions 6705Glecy AdrianoAinda não há avaliações

- PHILIPPINE INCOME TAX REVIEWERDocumento99 páginasPHILIPPINE INCOME TAX REVIEWERquedan_socotAinda não há avaliações

- Scientech 2502ADocumento2 páginasScientech 2502Aashutosh kumarAinda não há avaliações

- (Cambridge Series in Statistical and Probabilistic Mathematics) Gerhard Tutz, Ludwig-Maximilians-Universität Munchen - Regression For Categorical Data-Cambridge University Press (2012)Documento574 páginas(Cambridge Series in Statistical and Probabilistic Mathematics) Gerhard Tutz, Ludwig-Maximilians-Universität Munchen - Regression For Categorical Data-Cambridge University Press (2012)shu100% (2)

- VDA ChinaDocumento72 páginasVDA Chinatuananh1010Ainda não há avaliações

- Readingdev 7Documento2 páginasReadingdev 7api-190328610Ainda não há avaliações

- Apostles CreedDocumento141 páginasApostles Creedjerome mecca0% (2)

- Al-Rimawi Et Al-2019-Clinical Oral Implants ResearchDocumento7 páginasAl-Rimawi Et Al-2019-Clinical Oral Implants ResearchSohaib ShujaatAinda não há avaliações

- Chapter 11, 12 Curve Tracing and EnvelopeDocumento37 páginasChapter 11, 12 Curve Tracing and EnvelopeNitish PokhrelAinda não há avaliações

- People vs. Abad SantosDocumento2 páginasPeople vs. Abad SantosTrixie PeraltaAinda não há avaliações

- People vs. LorenzoDocumento8 páginasPeople vs. LorenzoMRose SerranoAinda não há avaliações

- Primer To Using Stampplot® Pro Standard User LicensedDocumento21 páginasPrimer To Using Stampplot® Pro Standard User LicensedSandy Rachman AdrianAinda não há avaliações

- The Research TeamDocumento4 páginasThe Research Teamapi-272078177Ainda não há avaliações

- Sustainability of A Beach Resort A Case Study-1Documento6 páginasSustainability of A Beach Resort A Case Study-1abhinavsathishkumarAinda não há avaliações

- Table Topics Contest Toastmaster ScriptDocumento4 páginasTable Topics Contest Toastmaster ScriptchloephuahAinda não há avaliações

- Adina CFD FsiDocumento481 páginasAdina CFD FsiDaniel GasparinAinda não há avaliações

- BCOM 302 BookDocumento179 páginasBCOM 302 BookHitanshi AgarwalAinda não há avaliações

- The Human Element is Critical in Personal SellingDocumento18 páginasThe Human Element is Critical in Personal SellingArsalan AhmedAinda não há avaliações

- ASSIGNMENTDocumento5 páginasASSIGNMENTPanchdev KumarAinda não há avaliações

- Interpleader Actions in The Ugandan Civil ProcedureDocumento6 páginasInterpleader Actions in The Ugandan Civil ProcedureLevis M AtukwatseAinda não há avaliações

- Andy Landers - Freeze Zone OffenseDocumento6 páginasAndy Landers - Freeze Zone OffenseWinston Brown100% (1)

- DRF1301 1000V 15A 30MHz MOSFET Push-Pull Hybrid DriverDocumento4 páginasDRF1301 1000V 15A 30MHz MOSFET Push-Pull Hybrid DriverAddy JayaAinda não há avaliações

- Conic SectionDocumento58 páginasConic SectionNailah Sakinah100% (1)

- We Don't Eat Our: ClassmatesDocumento35 páginasWe Don't Eat Our: ClassmatesChelle Denise Gumban Huyaban85% (20)

- HCF and LCMDocumento3 páginasHCF and LCMtamilanbaAinda não há avaliações

- Sexual Self PDFDocumento23 páginasSexual Self PDFEden Faith Aggalao100% (1)