Escolar Documentos

Profissional Documentos

Cultura Documentos

01 - Apéndice A

Enviado por

Luis TavisTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

01 - Apéndice A

Enviado por

Luis TavisDireitos autorais:

Formatos disponíveis

APNDICE

Gua rpida del PIC12F508

INTRODUCCIN

Cuando se est desarrollando un diseo tanto del hardware como del software conviene tener a mano las principales caractersticas del microcontrolador que se emplea. La gua rpida proporciona un resumen de la informacin ms importante del dispositivo y facilita, entre otras cosas, el nmero que corresponde a una patita, el bit especfico de un registro, los sealizadores a los que afecta una instruccin, etc. A continuacin, se presentan las caractersticas relevantes del PIC12F508.

CARACTERSTICAS GENERALES

En la tabla de la Figura A.1 se muestran las caractersticas representativas de PIC12F508.

PIC12F508 Memoria Reloj Perifricos Prestaciones De programa tipo FLASH De datos tipo RAM Frecuencia mx de funcionamiento Temporizador Despertar de sleep por cambio en una patita Patitas E/S Patita de entrada Resistencias pull-up internas Programacin serie en circuito Repertorio de instrucciones Tamao de los datos Encapsulados Coste Volumen Consumo 512 12 25 8 4 MHz TMR0 de 8 bits S 5 1 S S 33 de 12 bits 8 bits PDIP, SOIC y MSOP (8 patitas) Muy bajo (<0,5 ) Muy bajo (<mosca) Muy bajo (<350 A/2 V/4 MHz)

Ventajas

Figura A.1. Tabla que recoge las caractersticas fundamentales del PIC12F508.

MICROCONTROLADORES PIC. DISEO PRCTICO DE APLICACIONES

Otras caractersticas complementarias son las siguientes:

Oscilador interno de precisin de 4 MHz. Proteccin del cdigo del programa ante lecturas. Todas las instrucciones se ejecutan en un ciclo de instruccin (4 Tosc) menos las de salto, que duran el doble. Pila de dos niveles. Grabacin de la memoria FLASHen serie (ICSP) con recursos para la depuracin en circuito (ICD). Perro Guardin con oscilador RC integrado. Temporizador de 8 bits.

DIAGRAMA DE CONEXIONES

El diagrama de conexionado de las patitas del PIC12F508, que coincide con el del PIC12F509, se muestra en la Figura A.2. La tabla de la Figura A.3 muestra la misin de cada una de las patitas del PIC12F508/509.

Figura A.2. Diagrama de conexiones del PIC12F508 y del PIC12F509.

GUA RPIDA DEL PIC12 F508 Nombre GP0/ICSPDAT Funcin GPO Entrada TTL Salida CMOS Descripcin

Lnea de E/S bidireccional. Puede programarse con resistencia pull-up interna y salida del modo sleep por cambio de estado. Lnea de datos serie en la programacin de la memoria FLASH mediante ICSP. Lnea de E/S bidireccional. Puede programarse con resistencia pull-up interna y salida del modo sleep por cambio de estado. Lnea de reloj en la programacin ICSP. Lnea de E/S bidireccional. Puede programarse con resistencia pull-up interna y salida del modo sleep por cambio de estado. Entrada de reset. Cuando se configura como MCLR#, genera reset por nivel 0 y siempre dispone de resistencia pull-up. La tensin en esta patita no debe ser superior a VDD durante el funcionamiento normal del dispositivo, de lo contrario entra en el modo de programacin. Entrada de tensin VPP en el modo de grabacin (12,8 V).

ICSPDAT GP1/ICSPCLK GP1

ST TTL

CMOS CMOS

ICSPCLK GP3/MCLR#/VPP GP3

ST TTL

CMOS

MCLR#

ST

VPP GP4/OSC2 GP4 OSC2 GP5/OSC1/CLKIN GP5 OSC1 CLKIN VDD GND VDD GND

HV TTL CMOS XTAL TTL XTAL ST P P CMOS

Lnea de E/S bidireccional. Conexin de salida con el cristal o resonador en los modos de oscilador XT y LP. Lnea de E/S bidireccional. Conexin de entrada con el cristal del oscilador. Entrada de reloj externo de trabajo Entrada del positivo de alimentacin. Entrada de la tierra de alimentacin.

Figura A.3. Descripcin de las funciones de las patitas del PIC12F508/509.

MICROCONTROLADORES PIC. DISEO PRCTICO DE APLICACIONES

ARQUITECTURA INTERNA

En la Figura A.4 se ofrece el esquema de la arquitectura interna del PIC12F508.

Figura A.4. Arquitectura interna del PIC12F508.

MEMORIA DE PROGRAMA

El PIC12F508 tiene implementado en FLASH una memoria de programa de 512 palabras de 12 bits cada una. El direccionamiento de la instruccin en curso corre a cargo del PC, que est asociado a una Pila con dos niveles (Fig. A.5). Conviene recordar que cuando se produce un reset en el PIC12F508, se ejecuta la instruccin de la ltima posicin (01FF h) de la memoria que viene grabada de fbrica con un valor XX (movlw 0xXX), que hay que cargar en el registro de calibracin (OSCCAL) para asegurar la frecuencia de funcionamiento del oscilador interno de 4 MHz.

GUA RPIDA DEL PIC12 F508

Figura A.5. Estructura de la memoria de programa del PIC12F508. Los modelos PIC12F509 y PIC16F505 tienen el doble de capacidad.

MEMORIA DE DATOS

Es de tipo RAM y ocupa treinta y dos posiciones o registros de 8 bits de longitud cada uno, desde la direccin 00 h a la 1F h. Los siete primeros registros son los especficos (SFR) y los veinticinco restantes los de propsito general (GPR) (Fig. A.6.

Figura A.6. Estructura de la memoria de datos RAM del PIC12F508.

MICROCONTROLADORES PIC. DISEO PRCTICO DE APLICACIONES

REGISTROS ESPECFICOS DE CONTROL STATUS: Registro de Estado

Contiene los bits sealizadores que informan aspectos del estado del procesador cuando se ejecuta una instruccin (Fig. A.7).

Figura A.7. Estructura interna del Registro de Estado (STATUS).

GPWUF: Es un bit de STATUS que cuando vale 1 indica que se ha producido un reset por cambio de estado en una patita de entrada. PA0: Bit que selecciona una pgina de 512 posiciones de la memoria de programa. PD#: Se activa y se pone a 0 cuando el procesador entra en modo de bajo consumo tras ejecutar una instruccin SEP. TO#: Se activa y se pone a 0 cuando se desborda el WDT y se produce reset. Z: Se pone a 1 cuando el resultado de la instrucin ejecutada es 0. DC: Acarreo/llevada en el cuarto bit del resultado. C: Acarreo/llevada en el octavo bit del resultado.

OSCCAL: Registro de calibracin del oscilador interno

En este registro hay que cargar el valor XX, que viene grabado de fbrica, en la ltima posicin de la memoria de programa (movlw 0xXX) que se ejecuta en el reset.

Figura A.8. Estructura del registro de calibracin en el que se guarda el valor XX, que viene grabado de fbrica, en la ltima posicin de la memoria de programa.

Los 6 bits de menos peso de este registro se corresponden con el valor que tienen las lneas de E/S GP5-GP0, respectivamente.

Figura A.9. En el PIC12F508, el registro GPIO o PORTB contiene 6 bits vlidos que se relacionan con las seis lneas de E/S.

GUA RPIDA DEL PIC12 F508

OPTION: Registro del control de TMR0

El TMR0 es un contador ascendente de 8 bits que evoluciona con los impulsos de reloj que recibe y que se desborda al pasar del valor 1111 1111 al 0000 0000. Contiene un predivisor de frecuencia o preescaler que lo comparte con el WDT (Fig. A.10).

Figura A.10. Estructura interna del TMR0.

Figura A.11. Distribucin de los bits del registro OPTION.

PS2, PS1, PS0: Eligen el rango de divisin de los impulsos de reloj del predivisor. PSA: Asigna el predivisor de frecuencia al TMR0 (0) o al WDT (1). T0SE: Selecciona el flanco en que se produce el contaje: 1, descendente. y 0, ascendente. T0CS: Si vale 0, los impulsos proceden del oscilador interno (Fosc/4), y si vale 1, se introducen desde el exterior por la patita GP2/T0CKI. GPPU#: Si vale 0, el procesador despierta del modo de reposo cuando cambia de estado una de las lneas de entrada GP0, GP1 o GP3. GPWU#: Cuando vale 1, las lneas GP0, GP1 y GP3, si son entrada, disponen de una resistencia pull-up.

PALABRA DE CONFIGURACIN

Es una posicin de la memoria de programa que slo es accesible al grabar el microcontrolador (Fig. A.12).

Figura A.12. Distribucin de los 5 bits vlidos de la palabra de configuracin.

MICROCONTROLADORES PIC. DISEO PRCTICO DE APLICACIONES

MCLRE: Control de la funcin de la patita GP3/MCLR#. Si vale 1, acta como MCLR#, y si vale 0, como GP3. CP#: Proteccin de cdigo. Cuando vale 0, hay proteccin del cdigo ante lectura. WDTE: Si vale 1 el WDT funciona, y si vale 0, no. FOSC<1:0>: Seleccin del tipo de oscilador. 11: EXTRC (externo); 10: INTRC (interno) 01: XT, y 00: LP.

REPERTORIO DE INSTRUCCIONES

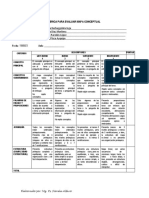

En la Figura A.13 se presentan los nemnicos y las principales caractersticas de las treinta y tres instrucciones de los PIC de la gama bsica, entre los que se encuentra el PIC12F508.

INSTRUCCIONES ORIENTADAS AL MANEJO DE BYTES Nemnico operandos ADDWF ANDWF CLRF CLRW COMF DECF DECFSZ INCF INCFSZ IORWF MOVF NOP RLF RRF SUBWF SWAPF Descripcin Ciclos 1 1 1 1 1 1 1o2 1 1o2 1 1 1 1 1 1 1 1 Formato 12 bits MSb LSb 0001 11df ffff 0001 01df ffff 0000 011f ffff 0000 0100 0000 0010 01df ffff 0000 11df ffff 0010 11df ffff 0010 10df ffff 0011 11df ffff 0001 00df ffff 0010 00df ffff 0000 001f ffff 0000 0000 0000 0011 01df ffff 0011 00df ffff 0000 10df ffff 0011 10df ffff Bits afectados Notas STATUS C, DC, Z Z Z Z Z Z Ninguno Z Ninguno Z Z Ninguno Ninguno C C C, DC, Z Ninguno 2, 4 2, 4 1, 2, 4 2, 4 2, 4 2, 4 2, 4 2, 4 2, 4 2, 4 1, 4 1, 2, 4 2, 4 4

f,d Suma W y f f,d Operacin lgica AND de W y f f Establece f a ceros Establece W a ceros

f,d Complementa f f,d Decrementa f f,d Decrementa f y salta si cero f,d Incrementa f f,d Incrementa f y salta si cero f,d Operacin lgica OR de Wyf f,d Mueve f a d Mueve W a f No operar

MOVFW f

f,d Rotar a izquierda a travs del acarreo f,d Rotar a derecha a travs del acarreo f,d Resta W de f f,d Intercambia f y d

GUA RPIDA DEL PIC12 F508

XORWF

f,d Operacin lgica OR exclusiva de W y f

0001 10df ffff

2,4

INSTRUCCIONES ORIENTADAS A MANEJO DE BITS Nemnico operandos BCF BSF BTFSC BTFSS Descripcin Ciclos 1 1 1o2 1o2 Formato 12 bits MSb LSb 0100 bbbf ffff 0101 bbbf ffff 0110 bbbf ffff 0111 bbbf ffff Bits afectados Notas STATUS Ninguno Ninguno Ninguno Ninguno 2, 4 2, 4

f,b Borrar el bit b de f f,b Establece a 1 el bit b de f f,b Brinca si el bit b de f es cero f,b Brinca si el bit b de f es uno k k k k k k f k AND entre W y el literal k Llamada a subrutina Refrescar Perro Guardin Salto incondicional Operacin lgica OR con el literal k Mueve el literal a W Carga el registro OPTION Retorno subrutina, devuelve k en W Entra en modo sleep Carga el registro TRIS OR exclusiva con W y el literal k

INSTRUCCIONES DE CONTROL Y DE MANEJO DE LITERALES ANDLW CALL GOTO IORLW MOVLW RETLW SLEEP TRIS XORLW 1 2 1 2 1 1 1 2 1 1 1 1110 kkkk kkkk 1001 kkkk kkkk 0000 0000 0100 101k kkkk kkkk 1101 kkkk kkkk 1100 kkkk kkkk 0000 0000 0010 1000 kkkk kkkk 0000 0000 0011 0000 0000 0fff 1111 kkkk kkkk Z Ninguno TO#, PD# Ninguno Z Ninguno Ninguno Ninguno TO#,PD# Ninguno Z 3 1

CLRWDT

OPTION

Notas: 1. El noveno bit del contador de programa es puesto a 0 por cualquier instruccin que modifique el valor del PC excepto la instruccin GOTO. 2. Cuando un registro de E/S se modifica a si mismo (por ejemplo, MOVF PORTB,1), el valor usado es que est presente en los propios pines. Por ejemplo, si el registro de datos tiene puesto a 1 un pin configurado como entrada y es cambiado a nivel bajo por un dispositivo externo, el dato ser escrito con un 0. 3. La instruccin TRIS f, donde f es igual a 6, provoca que el contenido del registro W sea escrito en los registros tri-estados de la puerta B (PORTB). Un 1 pone el pin en un estado de alta impedancia y deshabilita los buffers de salida. 4. Si esta instruccin es ejecutada en el registro TMR0 (y donde sea aplicable, d=1), el preescaler ser puesto a 0.

Figura A.13. Principales caractersticas de las treinta y tres instrucciones del PIC12F508 de la g gama bsica.

Você também pode gostar

- Manual Principal AnalisisDocumento305 páginasManual Principal AnalisismlandronAinda não há avaliações

- Ejemplos PIC Basic ProDocumento372 páginasEjemplos PIC Basic PropatxarinAinda não há avaliações

- Compilador C Ccs Y Simulador Proteus para Microcontroladores Pic PDFDocumento270 páginasCompilador C Ccs Y Simulador Proteus para Microcontroladores Pic PDFherreraherrerarubenAinda não há avaliações

- 01 - Apéndice ADocumento10 páginas01 - Apéndice ALuis TavisAinda não há avaliações

- DsPIC Diseño Practico de AplicacionesDocumento428 páginasDsPIC Diseño Practico de AplicacionesLópez Esperanza JhonnyAinda não há avaliações

- SEM270 BDocumento84 páginasSEM270 BLuis TavisAinda não há avaliações

- 03 Apéndice CDocumento18 páginas03 Apéndice CLuis TavisAinda não há avaliações

- FDM TDM 2Documento27 páginasFDM TDM 2Luis TavisAinda não há avaliações

- A Portes 2008Documento101 páginasA Portes 2008alirpeAinda não há avaliações

- Ingles Sin Barreras AUDIOS para El Foro de Jesy2474Documento1 páginaIngles Sin Barreras AUDIOS para El Foro de Jesy2474Luis TavisAinda não há avaliações

- Definiciones y Tecnologías de CelularesDocumento50 páginasDefiniciones y Tecnologías de CelularesVictor Antonio Guzman SandovalAinda não há avaliações

- CDMADocumento7 páginasCDMALuis TavisAinda não há avaliações

- 04 - Apéndice DDocumento18 páginas04 - Apéndice DLuis TavisAinda não há avaliações

- Piense en Francés, Hable en Francés (Libro 2)Documento244 páginasPiense en Francés, Hable en Francés (Libro 2)pilar.retondo100% (8)

- Experiment o 21Documento5 páginasExperiment o 21Luis TavisAinda não há avaliações

- Cap 1 Medi Osc.Documento18 páginasCap 1 Medi Osc.Luis TavisAinda não há avaliações

- Ingles Sin Barreras AUDIOS para El Foro de Jesy2474Documento1 páginaIngles Sin Barreras AUDIOS para El Foro de Jesy2474Luis TavisAinda não há avaliações

- Uso Del NipleDocumento9 páginasUso Del NipleLuis Tavis100% (1)

- Pasatiempo - Avanzado (Con Respuestas)Documento78 páginasPasatiempo - Avanzado (Con Respuestas)Luis TavisAinda não há avaliações

- Auto Escaner OBDIIDocumento48 páginasAuto Escaner OBDIIMauricio RjAinda não há avaliações

- Pasatiempo - Intermedio (Con Respuestas)Documento78 páginasPasatiempo - Intermedio (Con Respuestas)Luis TavisAinda não há avaliações

- 06 - Apéndice FDocumento70 páginas06 - Apéndice FLuis TavisAinda não há avaliações

- Manual de Aplicación de Compresores Embraco Refrigeracion BUENODocumento78 páginasManual de Aplicación de Compresores Embraco Refrigeracion BUENOmjhonny86% (73)

- SEM270 BDocumento84 páginasSEM270 BLuis TavisAinda não há avaliações

- Mundo de La Electronic A 1Documento16 páginasMundo de La Electronic A 1api-3733793100% (1)

- SEM270 BDocumento84 páginasSEM270 BLuis TavisAinda não há avaliações

- LG RP 29fc40p MC 021bDocumento38 páginasLG RP 29fc40p MC 021bchikiyjenny100% (2)

- Curso Reparacion ImpresorasDocumento6 páginasCurso Reparacion ImpresorasGABRIEL FERNANDO100% (1)

- Ampli Tda 7294 StereoDocumento6 páginasAmpli Tda 7294 StereoCm ElectronicaAinda não há avaliações

- LAB 11 ZavaletaDocumento8 páginasLAB 11 ZavaletaRoberto Carlos Zavaleta CrispinAinda não há avaliações

- Diagramas de Flujo de SeñalesDocumento35 páginasDiagramas de Flujo de Señaleschumenez00Ainda não há avaliações

- Practica N 5Documento5 páginasPractica N 5Jesus Lopez GoytiaAinda não há avaliações

- Seminario KinesiologiaDocumento10 páginasSeminario KinesiologiaCarmen Infante100% (1)

- Ses-Mart-Tut-La Importancia de La Autonomía para La Toma DecisionesDocumento5 páginasSes-Mart-Tut-La Importancia de La Autonomía para La Toma DecisionesOscar ZapataAinda não há avaliações

- La Gallinita CiegaDocumento2 páginasLa Gallinita Ciegadsgdfghf100% (2)

- Catalogo Enfermeria 2nivel ISSSTEDocumento13 páginasCatalogo Enfermeria 2nivel ISSSTEkapap lotar00100% (1)

- Ficha de Ingreso PediatriaDocumento7 páginasFicha de Ingreso PediatriaMacarena Castillo RiverosAinda não há avaliações

- ANEXO 4.2. Ejemplos de Verbos Irregulares y Sus ConstituyentesDocumento6 páginasANEXO 4.2. Ejemplos de Verbos Irregulares y Sus ConstituyentesCristina ScaleseAinda não há avaliações

- Plano de Acometida, Alimentador y TableroDocumento1 páginaPlano de Acometida, Alimentador y TableroJulio Candela Espinoza100% (1)

- Energías Renovables en México y El MundoDocumento11 páginasEnergías Renovables en México y El MundoMario Eduardo Muñoz MéridaAinda não há avaliações

- Mod 3 Proceso Gerencial de Informacion y Toma de Decisiones PDFDocumento18 páginasMod 3 Proceso Gerencial de Informacion y Toma de Decisiones PDFRicardo InquillaAinda não há avaliações

- Ejercicios Propuestos Cap 3Documento5 páginasEjercicios Propuestos Cap 3JUAN CARLOS BAUTISTA CATOTAAinda não há avaliações

- Excell Caso 2Documento6 páginasExcell Caso 2Daniela CalderónAinda não há avaliações

- Proyecto de AcueductosDocumento49 páginasProyecto de Acueductosdanigonza1059Ainda não há avaliações

- Dengue en PediatriaDocumento21 páginasDengue en Pediatriajoan diazAinda não há avaliações

- Caso Rosewood Hotels Lurie NicolasDocumento5 páginasCaso Rosewood Hotels Lurie NicolasMaria Segura IbañezAinda não há avaliações

- Fdsfdsfsdfsddfsdfsfds Fdsfds FD SFD SD FD sf32 f32f32f 32f 323 2f 32Documento57 páginasFdsfdsfsdfsddfsdfsfds Fdsfds FD SFD SD FD sf32 f32f32f 32f 323 2f 32Bryan GaribayAinda não há avaliações

- Arco en C Radius XP Range - Intermedical en EspañolDocumento5 páginasArco en C Radius XP Range - Intermedical en EspañolDPTO TECNICO OFICINAAinda não há avaliações

- Informeevalua PEI 2022Documento23 páginasInformeevalua PEI 2022Raysa Santa CruzAinda não há avaliações

- Presentacion FinalDocumento41 páginasPresentacion FinalConstanzaRivasAinda não há avaliações

- Especialidad de Letreros y Carteles Universidad Del ConquistadorDocumento3 páginasEspecialidad de Letreros y Carteles Universidad Del ConquistadorArud PoloAinda não há avaliações

- Clase 12 - Taller de GradoDocumento63 páginasClase 12 - Taller de GradochinchulinAinda não há avaliações

- SEMANA 1 - Mapa ConceptualDocumento2 páginasSEMANA 1 - Mapa ConceptualConnie :pAinda não há avaliações

- Herramientas de Inteligencia Comercial PDFDocumento40 páginasHerramientas de Inteligencia Comercial PDFnayshaAinda não há avaliações

- 3 La Estructura en Las Organizaciones EducativasDocumento3 páginas3 La Estructura en Las Organizaciones Educativasfatima REYESAinda não há avaliações

- Tweeen Clean 2205Documento4 páginasTweeen Clean 2205Arslan HussainAinda não há avaliações

- HD-3527 EndurecedorDocumento10 páginasHD-3527 EndurecedorArely AyalaAinda não há avaliações

- WD Rapido ES ARG (43033868) - ROW41066DWHCR-12Documento32 páginasWD Rapido ES ARG (43033868) - ROW41066DWHCR-12lscorveraposeAinda não há avaliações

- Gestion s13Documento3 páginasGestion s13Echeverre LuisAinda não há avaliações