Escolar Documentos

Profissional Documentos

Cultura Documentos

16 Bit Accumulator Using NAND and Logical Effort Method

Enviado por

Jaydip FadaduTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

16 Bit Accumulator Using NAND and Logical Effort Method

Enviado por

Jaydip FadaduDireitos autorais:

Formatos disponíveis

Assignment 5 EE671(VLSI Design) Timing Analysis By Fadadu Jaydip Ramnikbhai Roll No.

133070045 (1) Flip-flop characterization

For flip-flop characterisation following type of data pulse is applied.

For set-up of 92 ps and hold time of 10 ps flip-flop is able to flip output from 1 to 0 as shown in below figure.

Set-up time = 92 ps Hold = 10 ps

However delay of flip-flop is more and flip-flop takes almost 500ps to reach steady state value. This is not acceptable so I kept increasing set up time till there was not significant improvement in delay. All cases are shown below

Set-up = 93 ps Hold=10 ps

Set-up = 94 ps Hold=10 ps

Set-up = 95 ps Hold=10 ps

Set-up = 96 ps Hold=10 ps As observed above as I increase set-up time further more delay is not improving significantly. So we can finalize set-up as 95-96 ps. Now if I decrease hold time we observe following scenario.

Set-up = 96 ps Hold =10 ps

Set-up = 96 ps Hold = 9 ps

Set-up = 96 ps Hold=8 ps Thus if I decrease hold time make less than 8 ps delay is increasing. So we can finalize hold time as 9-10 ps. Same procedure was applied for positive pulse and set-up and hold time were found to be 52 ps and 9 ps

Set-up = 52 ps Hold=9 ps Taking worst case set-up time of flip-flop is 96 ps and hold time is 9 ps.

(2)

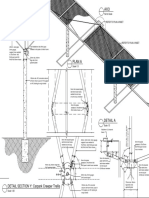

Block diagram of carry look ahead adder

Fig. 1 Block diagram of carry look ahead adder Here objective here is to construct adder such that (1) (2) (3) (4) (5) (6) Input capacitance is less than 10fF Output capacitance that accumulator needs to drive is 20fF Output should be settled within 1ns of rising edge Circuit should be realized using 2 input NAND gates only Flipflop used should have input capacitance of 15 Multiplexer is tri-state mux.

Now logic inside each block is as shown below.

(1) Single bit p and g signal

Fig 2. Single bit propagate and generate

(2) Group generate

GG= G3 + P3G2 + P3.P2.G1. + P3.P2.P1.G0

Fig 3 Group generate using 2 input nand gate only

(3) Group Propogate

PG = P3.P2.P1.P0

Fig 4 group propogate

(4) Carry look ahead block C1 = G0 + P0.C0 C2 = G1 + P1C1 = G1 + P1G0 + P1P0C0 C3 = G2 + P2G1 + P2P1G0 + P2P1P0C0 Equation to generate is similar to that of GG. So circuit is same for both. To make delay equal of all pathes (to minimize hazards in circuit) C1 and C2 are also realised with same circuit topology by making input of 4 input NAND gate zero.

(3)

Critical path in circuit

Fig. 5 critical path Critical path is shown in fig. 5.

The circuit of critical path is shown below.

Fig 6. critical path As mentioned by sir in class all NAND gates are kept of same size. So all inverters are working with electrical effort of 1. Logical effort is also 1. So all inverters are adding fixed delay of (1+p) There are total 19 stages in critical path. Flip-flop is presenting capacitance of 15 , that is 3.64 fF. Now input capacitance is to be kept less than 10fF. Lets design for 1fF. So H=3.64 Total branching in ciruit, B=2*3*6*3*3*2*2=1296 G=( )

So F=GBH=1.67469e+6

So stage effort

Taking this stage effort input capacitance of all stage is shown in fig 7

Fig 7. Sizing in critical path Here maximum size of nand gate is 8.8 . So size of nand size is 4.4 Nearest integer to 4.4 is 4 . So size of nand gate is kept Input capacitance of inverter at maximum is 8 So size of inverter is 8/3 = 2.66 Nearest integer is 3 . So size of inverter is kept 3 in NGSPICE.

(6) Simulation in NGSPICE

Clock to Q delay is maximum of 650 ps for critical path as shown below.

Fig 8 clock and output 15 showing maximum delay

Minimum clock for which circuit works correctly is around 1.3 ns. Along critical path maximum delay is arround 1.1 ns so minimum clock period for which circuit works correctly is 1.1ns + set up time. So arround 1.2ns.

Fig 9 maximum delay in critical path

Accumulator gives correct output for different input as shown below. Different combinations of input A (1) For A=0x0010

Fig 10 out(0-7) and clock for A= 0x0010

Fig 11 out(8-15) and clock for A= 0x0010

(2) A=0x0100

Fig 12 out(0-7) and clock for A=0x0100

Fig 13 out(8-15) and clock for A=0x0100

(3) A=0x1000

Fig 14 out(0-7) and clock for A=0x1000

Fig 15 out(8-15) and clock A=0x1000

(4) A=0x000f

Fig 16 out(0-7) and clock for A=0x000f

Fig 17 out(8-15) and clock for A=0x000f

(9) FLOOR PLAN

Fig 18 floor plan of accumulator

(10) Realization of circuit in magic

This circuit is realized in magic layout tool as shown below. However this is only partially realized. All important blocks are realized and complete circuit can be made by just repeating these blocks. Block 1: single bit p and g

Fig 19 single bit p and g in magic

Block 2: Group propogate

Fig 20 group propogate

Block 3: Group generate (can be used to generate carry C3, C2 and C1 also)

Fig 21 group generate

Partially realized layout of accumulator is as shown below. Output is shown only for 4 bits. By repeating the same blocks 16 bits can be realized.

Fig 22 Accumulator in magic layout tool

Você também pode gostar

- Why File A Ucc1Documento10 páginasWhy File A Ucc1kbarn389100% (4)

- Industrial Machine and ControlsDocumento31 páginasIndustrial Machine and ControlsCarol Soi100% (4)

- Mixing and Agitation 93851 - 10 ADocumento19 páginasMixing and Agitation 93851 - 10 Aakarcz6731Ainda não há avaliações

- IBPS Clerk Pre QUANT Memory Based 2019 QuestionsDocumento8 páginasIBPS Clerk Pre QUANT Memory Based 2019 Questionsk vinayAinda não há avaliações

- Laplace TransformDocumento158 páginasLaplace Transformpranayreddy12Ainda não há avaliações

- RoaLogic RV12 RISCV DatasheetDocumento73 páginasRoaLogic RV12 RISCV DatasheetJoão VictorAinda não há avaliações

- Report RISC 16bitDocumento82 páginasReport RISC 16bitMd. Jubayer Al-MahmodAinda não há avaliações

- Risc VDocumento5 páginasRisc VOlhaAinda não há avaliações

- The Design of A Custom 32-Bit RISC CPU and Port To GCC Compiler BDocumento179 páginasThe Design of A Custom 32-Bit RISC CPU and Port To GCC Compiler B吕治宽Ainda não há avaliações

- Laplace Fourier RelationshipDocumento17 páginasLaplace Fourier Relationshipnakasob100% (8)

- Design of A RISC Microcontroller Core in 48 HoursDocumento11 páginasDesign of A RISC Microcontroller Core in 48 HoursPulkit TrivediAinda não há avaliações

- Bushcraft Knife AnatomyDocumento2 páginasBushcraft Knife AnatomyCristian BotozisAinda não há avaliações

- Ultra-Low Power VLSI CircuitDocumento27 páginasUltra-Low Power VLSI CircuitRockstar_rohithAinda não há avaliações

- Pic10 Risc DesignDocumento169 páginasPic10 Risc DesignDai Thang TranAinda não há avaliações

- Mos IvDocumento47 páginasMos IvRaga LasyaAinda não há avaliações

- A Junk Project - An Income Generating ProjectDocumento2 páginasA Junk Project - An Income Generating ProjectHercules Verdeflor ValenzuelaAinda não há avaliações

- Electro Mechanical RelayDocumento30 páginasElectro Mechanical RelayJaydip Fadadu100% (1)

- ETIN25 - Analogue IC Design Laboratory Manual - Lab 2: Jonas Lindstrand Martin Liliebladh Markus Törmänen September 2011Documento14 páginasETIN25 - Analogue IC Design Laboratory Manual - Lab 2: Jonas Lindstrand Martin Liliebladh Markus Törmänen September 2011Western777Ainda não há avaliações

- Lab 5 Music Player and Audio Amp Fall 2014Documento8 páginasLab 5 Music Player and Audio Amp Fall 2014SteveAinda não há avaliações

- DelayDocumento31 páginasDelayvarun186Ainda não há avaliações

- 29.ECE301 - Logical Effort and Transistor Sizing - IIDocumento22 páginas29.ECE301 - Logical Effort and Transistor Sizing - IINambisan04Ainda não há avaliações

- 33 7 LM V1 S1 Delay ModelingDocumento39 páginas33 7 LM V1 S1 Delay ModelingPriyanka AshishAinda não há avaliações

- Elmore Delay in RC Networks: September 16, 2010Documento3 páginasElmore Delay in RC Networks: September 16, 2010Siddharth SabharwalAinda não há avaliações

- ESDynamic Logic CircuitsDocumento61 páginasESDynamic Logic CircuitsMandovi BorthakurAinda não há avaliações

- Dynamic Logic Circuits: A. MarzukiDocumento25 páginasDynamic Logic Circuits: A. Marzukisreekanthreddy peramAinda não há avaliações

- Electrical Network Analysis Lab Course Lab Course: Prepared By: Husan AliDocumento34 páginasElectrical Network Analysis Lab Course Lab Course: Prepared By: Husan AliengrhusanAinda não há avaliações

- VLSI Lab CompendiumDocumento52 páginasVLSI Lab CompendiumSaad Ali Khan SherwaniAinda não há avaliações

- HSPICE TutorialDocumento7 páginasHSPICE TutorialSreyas MohanAinda não há avaliações

- Mosfet 1Documento33 páginasMosfet 1Palash SwarnakarAinda não há avaliações

- AdcDocumento69 páginasAdc123kailashAinda não há avaliações

- CMOS Digital Integrated Circuits: Lec 5 SPICE Modeling of MOSFETDocumento16 páginasCMOS Digital Integrated Circuits: Lec 5 SPICE Modeling of MOSFETNIET14Ainda não há avaliações

- Format of HSPICE NetlistDocumento2 páginasFormat of HSPICE NetlistJinesh PatelAinda não há avaliações

- CAD For VLSI Design - II: V. Kamakoti and Shankar BalachandranDocumento18 páginasCAD For VLSI Design - II: V. Kamakoti and Shankar BalachandranAjaya HsAinda não há avaliações

- Principles of Semiconductor Devices-L5Documento21 páginasPrinciples of Semiconductor Devices-L5LIAKMANAinda não há avaliações

- 07.5.Z-Transform ExamplesDocumento25 páginas07.5.Z-Transform ExamplesNoel KeakedaAinda não há avaliações

- VLSI & Embedded Systems Lab ManualDocumento137 páginasVLSI & Embedded Systems Lab Manualganga avinash reddyAinda não há avaliações

- Lec3 Single Stage PDFDocumento24 páginasLec3 Single Stage PDFRavinder KumarAinda não há avaliações

- Vlsi - CalculatorDocumento14 páginasVlsi - CalculatorKarthik RamasamyAinda não há avaliações

- TriennaleDocumento129 páginasTriennaleJesus UrrestiAinda não há avaliações

- Resistance CapacitanceDocumento24 páginasResistance Capacitancemayurp90100% (1)

- 10 Metal-Semiconductor JunctionsDocumento56 páginas10 Metal-Semiconductor JunctionsKamalesh DebnathAinda não há avaliações

- SPICE ParametersDocumento4 páginasSPICE ParametersKaran KeherAinda não há avaliações

- Logical Effort Dinesh SharmaDocumento60 páginasLogical Effort Dinesh SharmaShyamRamamoorthyAinda não há avaliações

- Embedded Systems GPIO-1-1Documento57 páginasEmbedded Systems GPIO-1-1C SriharshaAinda não há avaliações

- Laplace TransformDocumento10 páginasLaplace Transformariana_kardiamouAinda não há avaliações

- ZhengchenDocumento139 páginasZhengchenAnh PhanAinda não há avaliações

- Aulas15 16Documento16 páginasAulas15 16Pramod Reddy RAinda não há avaliações

- Clocked CmosDocumento24 páginasClocked CmosAnil KumarAinda não há avaliações

- Foundry Technologies 180-Nm Cmos, RF Cmos and Sige Bicmos: High-Performance Devices For A Wide Range of ApplicationsDocumento4 páginasFoundry Technologies 180-Nm Cmos, RF Cmos and Sige Bicmos: High-Performance Devices For A Wide Range of Applicationssandeep_sggsAinda não há avaliações

- Flash ADC MidsemDocumento9 páginasFlash ADC MidsemBikashKumarMoharanaAinda não há avaliações

- Elec Eng 2ei5 Microelectronic Devices and Circuits I Winter 2011 Final Exam - April 25, 2011Documento4 páginasElec Eng 2ei5 Microelectronic Devices and Circuits I Winter 2011 Final Exam - April 25, 2011Filip ZubacAinda não há avaliações

- VLSI UNIT 1 Part - III PDFDocumento35 páginasVLSI UNIT 1 Part - III PDFKARTHIKAYEN AAinda não há avaliações

- Metal-Semiconductor Junctions PDFDocumento22 páginasMetal-Semiconductor Junctions PDFTuncay YeşilkaynakAinda não há avaliações

- Sill HSpice Tutorial FinalDocumento106 páginasSill HSpice Tutorial FinalSharan Kumar GoudAinda não há avaliações

- CCS TivaWareDocumento26 páginasCCS TivaWareJoginder YadavAinda não há avaliações

- Lecture 8 - Circuits Design Issues and Layout FormationDocumento18 páginasLecture 8 - Circuits Design Issues and Layout FormationevildoctorbluetoothAinda não há avaliações

- Hspice ExampleDocumento3 páginasHspice ExamplesriIITAinda não há avaliações

- TM4C123G LaunchPad Workshop WorkbookDocumento336 páginasTM4C123G LaunchPad Workshop WorkbookCésar TapiaAinda não há avaliações

- Feedback OscillatorDocumento9 páginasFeedback OscillatorNageswara Rao ChallaAinda não há avaliações

- 2023 Vlsi HW3Documento2 páginas2023 Vlsi HW3q3366325Ainda não há avaliações

- ADS Oscillator DesignDocumento23 páginasADS Oscillator Designnavvaba100% (1)

- RF Amp TutorialDocumento17 páginasRF Amp TutorialMihailAinda não há avaliações

- Lab 10Documento34 páginasLab 10menchieAinda não há avaliações

- Soln Quiz 2Documento4 páginasSoln Quiz 2Akul Kumar SinghAinda não há avaliações

- MOSIS Counter Report Spring 2008Documento60 páginasMOSIS Counter Report Spring 2008atom_2334Ainda não há avaliações

- Tutorial 1 15Documento13 páginasTutorial 1 15Charan Kanwal SinghAinda não há avaliações

- Digital Electronics Tutorial Sheet-1Documento13 páginasDigital Electronics Tutorial Sheet-1shraddhabansalAinda não há avaliações

- 3 To 8 Decoder in NGSPICEDocumento14 páginas3 To 8 Decoder in NGSPICEJaydip FadaduAinda não há avaliações

- OPen Collector and Tri State GateDocumento19 páginasOPen Collector and Tri State GateJaydip FadaduAinda não há avaliações

- Abrasive Machining and Finishing: Manufacturing ProcessesDocumento73 páginasAbrasive Machining and Finishing: Manufacturing ProcessesJaydip FadaduAinda não há avaliações

- 2a Unani Medicine in India - An OverviewDocumento123 páginas2a Unani Medicine in India - An OverviewGautam NatrajanAinda não há avaliações

- DxDiag Copy MSIDocumento45 páginasDxDiag Copy MSITạ Anh TuấnAinda não há avaliações

- TrellisDocumento1 páginaTrellisCayenne LightenAinda não há avaliações

- Acampamento 2010Documento47 páginasAcampamento 2010Salete MendezAinda não há avaliações

- Specification Sheet: Case I Case Ii Operating ConditionsDocumento1 páginaSpecification Sheet: Case I Case Ii Operating ConditionsKailas NimbalkarAinda não há avaliações

- Vernacular ArchitectureDocumento4 páginasVernacular ArchitectureSakthiPriya NacchinarkiniyanAinda não há avaliações

- Monitor Stryker 26 PLGDocumento28 páginasMonitor Stryker 26 PLGBrandon MendozaAinda não há avaliações

- CV ChristianDocumento2 páginasCV ChristianAlya ForeferAinda não há avaliações

- BIOBASE Vortex Mixer MX-S - MX-F User ManualDocumento10 páginasBIOBASE Vortex Mixer MX-S - MX-F User Manualsoporte03Ainda não há avaliações

- Oracle SOA Suite 11g:buildDocumento372 páginasOracle SOA Suite 11g:buildMohsen Tavakkoli100% (1)

- Will Smith BiographyDocumento11 páginasWill Smith Biographyjhonatan100% (1)

- Blake 2013Documento337 páginasBlake 2013Tushar AmetaAinda não há avaliações

- Kidney Stone Diet 508Documento8 páginasKidney Stone Diet 508aprilAinda não há avaliações

- Properties of LiquidsDocumento26 páginasProperties of LiquidsRhodora Carias LabaneroAinda não há avaliações

- Oral ComDocumento2 páginasOral ComChristian OwlzAinda não há avaliações

- Baxter - Heraeus Megafuge 1,2 - User ManualDocumento13 páginasBaxter - Heraeus Megafuge 1,2 - User ManualMarcos ZanelliAinda não há avaliações

- AstmDocumento5 páginasAstmyanurarzaqaAinda não há avaliações

- Intervensi Terapi Pada Sepsis PDFDocumento28 páginasIntervensi Terapi Pada Sepsis PDFifan zulfantriAinda não há avaliações

- 3rd Page 5Documento1 página3rd Page 5api-282737728Ainda não há avaliações

- Particle BoardDocumento1 páginaParticle BoardNamrata RamahAinda não há avaliações

- Nutrition Great Foods For Getting Vitamins A To K in Your DietDocumento1 páginaNutrition Great Foods For Getting Vitamins A To K in Your DietDhruv DuaAinda não há avaliações

- International Patient Referral - Part 2 - Revised - 29-04-2010 - 2Documento2 páginasInternational Patient Referral - Part 2 - Revised - 29-04-2010 - 2Fatah AssadAinda não há avaliações

- Rare Malignant Glomus Tumor of The Esophagus With PulmonaryDocumento6 páginasRare Malignant Glomus Tumor of The Esophagus With PulmonaryRobrigo RexAinda não há avaliações

- War at Sea Clarifications Aug 10Documento4 páginasWar at Sea Clarifications Aug 10jdageeAinda não há avaliações