Escolar Documentos

Profissional Documentos

Cultura Documentos

Analog multiplier circuit using opamps

Enviado por

xongassilvaDescrição original:

Título original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Analog multiplier circuit using opamps

Enviado por

xongassilvaDireitos autorais:

Formatos disponíveis

Indian Journal of Pure & Applied Physics

Vol. 48, January 2010, pp. 67-70

Analog multiplier using operational amplifiers

Vanchai Riewruja & Apinai Rerkratn

Faculty of Engineering, King Mongkuts Institute of Technology Ladkrabang, Ladkrabang, Bangkok 10520 Thailand

E-mail: kvanchai@kmitl.ac.th

Received 10 August 2009; revised 10 September 2009; accepted 20 November 2009

Simple circuit technique for implementing four-quadrant analog multiplier has been presented. The proposed circuit

requires only operational amplifier (opamp) as the active element. The realization method is based on the quarter-square

technique where a square is provided from the inherent quadratic behaviour of class-AB output stage of opamp.

Experimental results showing the circuit performance are described. The wore-case linearity error and total harmonic

distortion for maximum operating range are about 0.23 and 1.02%, respectively.

Keywords: Analog multiplier, Opamp, Quarter-square technique, Squaring circuit, Class AB configuration

1 Introduction

Analog multiplier is an important circuit building

block in the field of analog signal processing. Its

applications can be found in communication,

measurement and instrumentation systems. In the

past, analog multiplier based on a variable

transconductance technique is proposed

1

. Many

commercial analog multipliers using this technique

are available in the form of integrated circuit

fabricated in bipolar technology. Alternately, one of

the successful techniques to realize an analog

multiplier is based on the use of quarter-square

technique

2,3

. The squaring of sum and difference

schemes used in this technique are the necessary

operation. The squaring schemes of current input

signal can be performed using translinear principle

4-6

.

However, these schemes realized for the specific

purpose are unavailable in the commercial integrated

circuit form. It is known that output stage of a

general-purpose opamp is a class-AB configuration.

The characteristic of a class-AB configuration can be

expressed by the translinear principle

7,8

and exploited

to realize a high performance squaring scheme

9-11

.

The square operation achieved by this mention is

suited for the realization of analog multiplier using

quarter-square technique. The use of an opamp in the

realization of analog multiplier will provide the

structure of high performance at low cost and simple

construction. In this paper, four-quadrant analog

multiplier is described. The proposed circuit requires

only opamp as the active elements. Experimental

results that verify the circuit performance will be

given.

2 Circuit Description

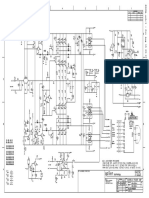

The proposed analog multiplier is shown in Fig. 1.

The circuit operation can be expressed as follow.

Assumming that opamps A

1

and A

2

are well matched

such as I

B1

= I

B2

= I

B

and I

S1

= I

S2

= I

S

, where I

B

and I

S

denote the quiescent current and class-AB bias current

of opamp, respectively. Opamps A

1

and A

2

and

resistors R

3i

R

5i

form an unity gain summing

amplifier with supply current sensing. Resulting

voltage v

11

and v

12

are, respectively, sum and

difference of input voltage v

x

and v

y

. Resistors R

11

and

R

12

convert the signal voltages v

11

and v

12

into the

signal currents i

11

and i

12

. For the output currents i

11

and i

12

less than 2I

S

, the quadratic characteristic of

class-AB output stage of opamps A

1

and A

2

, which

exist in the supply currents I

1

and I

2

, are fulfilled

10,11

.

The supply currents I

1

and I

2

are sensed and converted

to voltages v

21

and v

22

by resistors R

21

and R

22

,

respectively. If resistors R

11

= R

12

= R

C

, R

21

= R

22

=

R

S

, R

3i

= R

41

= R

5i

= R

m

and R

42

= R

m

/2 are assigned,

then voltages v

21

and v

22

can be written as

11

:

( )

2

11 21 11 21

21 CC B S 21 2

S 11 11

8 2

v R v R

v v I I R

I R R

= + for

11

S

11

2

v

I

R

(1)

( )

2

12 22 12 22

22 CC B S 22 2

S 12 12

8 2

v R v R

v v I I R

I R R

= + for

12

S

12

2

v

I

R

(2)

Voltages v

21

and v

22

will transfer to four input

difference amplifier formed by opamp A

3

and resistors

R

1

R

6

, where R

3

= R

6

=

R

p

, R

1

= R

4

= R

f

and R

2

= R

5

=

R

q

. From routine circuit analysis, voltages v

11

and v

12

INDIAN J PURE & APPL PHYS, VOL 48, JANUARY 2010

68

are, respectively, sum and difference of input voltages

v

x

and v

y

. Therefore, the output voltage v

o

can be

stated as:

f S S f

o x y y 2

C q S C p

2

2 2

R R R R

v v v v

R R I R R

= +

(3)

To provide the multiplication operation, the

condition of R

f

/R

p

= R

S

/2R

C

is assigned. Hence the

output voltage can be expressed as:

f S

o x y m x y 2

C q S

2

R R

v v v k v v

R R I

= = (4)

where k

m

denotes the multiplication gain. From Eq.

(4), it can be seen that four-quadrant analog multiplier

can be simply realized using general purpose opamp

without specific device.

3 Circuit Performance

Deviation from ideal performance of the proposed

circuit is disturbed by the mismatches between

opamps A

1

and A

2

and the tolerance of resistors being

used. The device mismatches will influence the

multiplication gain error and second harmonic

distortion of the input signals v

x

and v

y

. The output

voltage v

o

included term of errors and can be

expressed as:

2 2 f

0 1 x y 2 x 3 y off

C q S

{(1 ) }

R

v v v v v v

R R I

= + + + + (5a)

q

1 S

f

6

4

R

R

= + (5b)

q

S

2

f

3

3

2

R

R

= + (5c)

q

S

3

f

3

4

2

R

R

= + (5d)

Fig. 1 Proposed analog multiplier

RIEWRUJA & RERKRATN: ANALOG MULTIPLIER USING OPERATIONAL AMPLIFIERS

69

( )( )

f S

off B1 B2 S

q

1 2

R R

v I I

R

= + + (5e)

where is the tolerance of resistors,

S

= (I

S1

I

S2

) is

the mismatch between class-AB bias currents of

opamps A

1

and A

2

,

1

to

3

and v

off

denote the error

factors and offset voltage, respectively. If R

f

/R

q

= 1,

= 110

3

,

S

= 1.310

6

, I

B1

= 0.537 mA,

I

B2

= 0.539 mA, then errors

1

to

3

are calculated as

1

= 210

4

,

2

= 1.310

6

,

3

= 110

3

and v

off

= 6.6

mV. The input operating range of the proposed circuit

can be considered from the accepted value of the

output current drawn from opamps A

1

and A

2

to fulfill

the condition in Eqs (1) and (2). The voltages v

21

and

v

22

included higher-order terms can be expressed as

11

:

2 4

11 11

21 CC B1 21 S1 21 2 2 4 4

S1 11 S1 11

1 ....

8 128

v v

v v I R I R

I R I R

= + +

11 21

11

2

v R

R

(6)

2 4

12 12

22 CC B2 22 S2 22 2 2 4 4

S2 12 S2 12

1 ....

8 128

v v

v v I R I R

I R I R

= + +

12 22

12

2

v R

R

(7)

From Eqs (6) and (7), if term v

1i

/R

1i

in backet is

chosen such as v

1i

/R

1i

< 1.26I

Si

, then Eqs (6) and (7)

can be approximated by truncated higher-order terms

as in Eqs (1) and (2). For v

11

= -(v

x

+ v

y

) and v

12

= (v

x

v

y

), the input operating range of the proposed

circuit, |v

x

| + |v

y

|, can be estimated to smallest value

between 1.26R

11

I

S1

and 1.26R

12

I

S2

.

4 Exprimental Details

The proposed circuit in Fig. 1 was constructed

using commercially available opamps UA741 and

0.1% tolerance resistors. The resistors used in the

circuit are chosen to be R

11

= R

12

= 5 k, R

21

= R

22

=

2 k, R

1

= R

2

= R

4

= R

5

= R

31

= R

32

= R

41

= R

51

= R

52

=

100 k, R

42

= 50k and R

3

= R

6

= 500 k. The

power supply voltages used were set to 9V. The

quiescent currents and the class-AB bias currents of

opamps A

1

and A

2

, respectively, were measured as

I

B1

= 0.537 mA, I

B2

= 0.539 mA, I

S1

= 144.8 A and

I

S2

= 146.1 A using the technique proposed earlier

12

.

Hence scale factor k

m

and input operating range can

be calculated as 0.275 and 0.91 V, respectively. The

measure of dc transfer characteristic is shown in

Fig. 2. Figure 3 shows the linearity error for input

voltage v

x

varied from 1V to 1V and v

y

= 0.5 V. For

input operating range, |v

x

| + |v

y

| = 0.9 V, the worse-

case linearity error of Fig. 3 is about 0.9 mV or

Fig. 2 dc transfer characteristic

INDIAN J PURE & APPL PHYS, VOL 48, JANUARY 2010

70

Fig. 3 Linearity error

Fig. 4 Total harmonic distortions

relative error of 0.23% for input voltage v

x

of 0.4V.

The output response of the proposed circuit can be

investigated from the total harmonic distortions

(THDs). The measure of THDs is determined by

applying a sinusoidal wave to v

x

and dc voltage varied

from 1V to 1V to v

y

. Figure 4 shows THDs versus

input voltage v

x

at 1, 10 and 50 kHz of peak amplitude

100 mV. Figure 5 shows the result of amplitude

modulation for 20 kHz sinusoidal wave of 0.4V peak

amplitude and 1 kHz triangular wave of 0.2 V peak

amplitude applied to v

x

and v

y

, respectively. It is

clearly seen that the proposed circuit provides an

adequate performance of analog multiplier.

5 Conclusions

Four-quadrant analog multiplier using opamps as

only active element has been described. The

realization method is based on opamp supply current

sensing to provide the squaring of sum and difference

of two input signals for quarter-square algebraic

identity. The proposed circuit provides a simple

construction, a good performance and low cost.

Experimental results show that the proposed circuit

exhibits basic feature of multiplier for analog signal

processing.

References

1 Gilbert B A, IEEE J Solid-State Circuits, SC-9 (1974) 364.

2 Kimura K, IEEE J Solid-State Circuits, 29 (1994) 46.

3 Pena-Finol J S & Connelly J A, IEEE J Solid-State Circuits,

SC-22 (1987) 1064.

4 Abuelmaatti M T & Abed S M, Int J Electron, 86 (1999) 35.

5 Bratt A H, King D & Lysejko M J, Electronics Lett, 27

(1991) 1852.

6 De La Cruz-Blas C A, Lopez-Martin A J & Carlosena Ar,

Electron Lett, 39 (2003) 434.

7 Gilbert B, Electron Lett, 11 (1975) 14.

8 Seevinck E & Wiegerink R J, IEEE J Solid-State Circuits, 26

(1991) 1098.

9 Surakampontorn W & Riewruja V, Int J Electron, 73 (1992)

627.

10 Surakampontorn W, IEEE Trans Inst & Meas, 37 (1988)

259.

11 Riewruja V & Kamsri T, IET Circuit Devices & Systems, 3

(2009) 57.

12 Toumazou C & Lidgey F J, IEE Proc Part G, 134 (1987) 7.

Fig. 5 Amplitude modulation of sinusoidal wave 20 kHz with

amplitude 0.4 V

p

and triangle wave 1 kHz with amplitude 0.2 V

p

(vertical scale, upper trace:100 mV/div; lower trace: 5 mV/div,

horizontal scale: 400 s/div)

Você também pode gostar

- Measure Small Currents Using a GalvanometerDocumento8 páginasMeasure Small Currents Using a GalvanometerAnkit ChauhanAinda não há avaliações

- Electrostatic Headphones - N. Pollock (Wireless World, Nov 1979)Documento5 páginasElectrostatic Headphones - N. Pollock (Wireless World, Nov 1979)jimmy67musicAinda não há avaliações

- Msi B75ma-E33Documento37 páginasMsi B75ma-E33A2139Ainda não há avaliações

- The Force On A Current Carrying Conductor in Magnetic FieldDocumento119 páginasThe Force On A Current Carrying Conductor in Magnetic FieldMuhammad AdibAinda não há avaliações

- TransformerDocumento116 páginasTransformerOsman TolhildanAinda não há avaliações

- Compactrio Ni Crio-9022: Operating Instructions and SpecificationsDocumento23 páginasCompactrio Ni Crio-9022: Operating Instructions and Specificationsashraf8588100% (1)

- CH18Documento79 páginasCH18deepakkr22781100% (1)

- Public PM2xxx PMC Register List v1001Documento26 páginasPublic PM2xxx PMC Register List v1001Le BinhAinda não há avaliações

- Layout Fasilitas Power House: SCALE 1:50Documento1 páginaLayout Fasilitas Power House: SCALE 1:50Ihsan RamadhanAinda não há avaliações

- Preface: Licensing AgreementDocumento58 páginasPreface: Licensing AgreementNarcis Patrascu100% (1)

- A. E. Fitzgerald, Dkk. 1981. Dasar-Dasar Elektro Teknik Jilid I PDFDocumento299 páginasA. E. Fitzgerald, Dkk. 1981. Dasar-Dasar Elektro Teknik Jilid I PDFAnton SriwidjajaAinda não há avaliações

- Optiplex 780 Arrowhead RA03Documento43 páginasOptiplex 780 Arrowhead RA03João Luis N. Do AmaralAinda não há avaliações

- 1500W Inverter Full Schematics and PCBDocumento7 páginas1500W Inverter Full Schematics and PCBFélix Takey KobataAinda não há avaliações

- Spice Model of DiodeDocumento20 páginasSpice Model of DiodeharizAinda não há avaliações

- 12V DC Amplifier Using TDA 2003Documento5 páginas12V DC Amplifier Using TDA 2003mahdad20% (1)

- Rangkaian Listrik ResonansiDocumento62 páginasRangkaian Listrik ResonansiMuazamFakhriSunyAinda não há avaliações

- Hall Effect Measurements PDFDocumento45 páginasHall Effect Measurements PDFjotageaAinda não há avaliações

- 4 Essential Features of Transformer On-Load Tap Changer OLTCDocumento5 páginas4 Essential Features of Transformer On-Load Tap Changer OLTCrobertoseniorAinda não há avaliações

- GRAFCET-A Powerful Tools For Specification of Logic ControllersDocumento16 páginasGRAFCET-A Powerful Tools For Specification of Logic ControllerstruongthanhdoAinda não há avaliações

- Power Topologies Quick Reference Guide PDFDocumento9 páginasPower Topologies Quick Reference Guide PDFbiosbgAinda não há avaliações

- 2 5 2 PDFDocumento2 páginas2 5 2 PDFJoshua Roberto Gruta100% (1)

- Calculations For Design Parameters of TransformerDocumento7 páginasCalculations For Design Parameters of TransformerMaximilian SylvesterAinda não há avaliações

- Variable DC Power SupplyDocumento27 páginasVariable DC Power SupplyAshok DamorAinda não há avaliações

- Kumpulan Skema TV by Mbah ElektroDocumento15 páginasKumpulan Skema TV by Mbah ElektroDabeng DabengAinda não há avaliações

- Double Tuned AmplifierDocumento1 páginaDouble Tuned AmplifierAnbarasan RamamoorthyAinda não há avaliações

- Product Summary:: PD194E-9S4Documento3 páginasProduct Summary:: PD194E-9S4wildpere50% (2)

- Gyrator Capacitor ModelingDocumento7 páginasGyrator Capacitor Modelingbenitogaldos19gmail.comAinda não há avaliações

- ASGN Ethernet Loopback DesignDocumento4 páginasASGN Ethernet Loopback DesignsenthilAinda não há avaliações

- Practical SCR Triac Projects - M.C. SharmaDocumento53 páginasPractical SCR Triac Projects - M.C. Sharmaenrique_ortizAinda não há avaliações

- Power Electronics Devices LectureDocumento78 páginasPower Electronics Devices LectureM Waqar ZahidAinda não há avaliações

- 6260A.sch-1 - Fri Aug 15 09:37:09 2003 Power Amp Parts ListDocumento32 páginas6260A.sch-1 - Fri Aug 15 09:37:09 2003 Power Amp Parts ListCarlos Humberto Vergara PeñaAinda não há avaliações

- MSDS Oil Transformer Sun OhmDocumento8 páginasMSDS Oil Transformer Sun OhmYulius IndhraAinda não há avaliações

- Diodes Thyristors TransistorsDocumento19 páginasDiodes Thyristors TransistorsJayloyd LaraAinda não há avaliações

- Chap 11Documento18 páginasChap 11ashinkumarjerAinda não há avaliações

- Schneider Electric ATV12H075M2 DatasheetDocumento8 páginasSchneider Electric ATV12H075M2 DatasheetrochimunAinda não há avaliações

- Anlisa Dioda ZnerDocumento14 páginasAnlisa Dioda ZnerAlrashid ArsyadAinda não há avaliações

- LAB 2 Magnetic Circuits Using Matlab PDFDocumento6 páginasLAB 2 Magnetic Circuits Using Matlab PDFyasirAinda não há avaliações

- Hambley SolutionsDocumento72 páginasHambley SolutionsVaibhav Monga0% (1)

- Teorema SuperposisiDocumento6 páginasTeorema SuperposisiHizkia Glorius SomaAinda não há avaliações

- Lesson 7 Insulated Gate Bipolar Transistor (IGBT)Documento23 páginasLesson 7 Insulated Gate Bipolar Transistor (IGBT)Chacko MathewAinda não há avaliações

- Design and Construction of 1KW Power InverterDocumento14 páginasDesign and Construction of 1KW Power InverterJoemarAlcantaraBuenoAinda não há avaliações

- CMOS Amplifiers - Problems PDFDocumento20 páginasCMOS Amplifiers - Problems PDFAnurag AnandAinda não há avaliações

- AC to DC Conversion TechniquesDocumento40 páginasAC to DC Conversion Techniquesrahmanrestu33% (3)

- Experiment # 1: P-N Junction Diode: TheoryDocumento9 páginasExperiment # 1: P-N Junction Diode: Theorypoonginithi040% (1)

- RC Snubber Design CalculationsDocumento2 páginasRC Snubber Design CalculationsDavid NeiferdAinda não há avaliações

- Learn to Design a High-Frequency Power Transformer Using Forward TopologyDocumento3 páginasLearn to Design a High-Frequency Power Transformer Using Forward TopologyNiranjan kumarAinda não há avaliações

- 1a-Sensor Resistif-1 PDFDocumento45 páginas1a-Sensor Resistif-1 PDFSat SatrioAinda não há avaliações

- Engineering Circuit Analysis Practice ProblemsDocumento2 páginasEngineering Circuit Analysis Practice ProblemsbrnlmdzAinda não há avaliações

- How To Make Any Windows App PortableDocumento3 páginasHow To Make Any Windows App PortableAmit BhavikattiAinda não há avaliações

- Xelil Muellim Design - BookDocumento161 páginasXelil Muellim Design - BookDyan FayeAinda não há avaliações

- Power Electronics Lab Manual With Orcad Pspice 10.5Documento36 páginasPower Electronics Lab Manual With Orcad Pspice 10.5Muhammad Ahtisham Asif100% (2)

- Improved Dynamic Model of Fast-Settling Linear-in-dB Automatic Gain Control CircuitDocumento4 páginasImproved Dynamic Model of Fast-Settling Linear-in-dB Automatic Gain Control Circuitapi-19755952Ainda não há avaliações

- Complex Number Expressions in Polar FormDocumento9 páginasComplex Number Expressions in Polar Formpiali89Ainda não há avaliações

- PEC Tutorial 3Documento3 páginasPEC Tutorial 3harsh chaudharyAinda não há avaliações

- Frequency Shift Keying: ObjectivesDocumento3 páginasFrequency Shift Keying: ObjectivesSyam SundarAinda não há avaliações

- Multiplier PDFDocumento4 páginasMultiplier PDFHimanshu SaxenaAinda não há avaliações

- Lectures 6 & 7 - Uncontrolled (Diode) Rectifier Circuits: Single-Phase Center-Tapped RectifierDocumento21 páginasLectures 6 & 7 - Uncontrolled (Diode) Rectifier Circuits: Single-Phase Center-Tapped RectifierTommy ManAinda não há avaliações

- DISTANCE PROTECTION OF DOUBLE–CIRCUIT TRANSMISSION LINESDocumento5 páginasDISTANCE PROTECTION OF DOUBLE–CIRCUIT TRANSMISSION LINEStandin tshewangAinda não há avaliações

- 3-Lesson Notes Lec 30 Short Medium Line ModelDocumento7 páginas3-Lesson Notes Lec 30 Short Medium Line ModelAsadAliAwanAinda não há avaliações

- DA AnalysisDocumento5 páginasDA AnalysisraineymjAinda não há avaliações

- Voltage-Current Characteristic of Incandescent Lightbulbs: Measurement and AnalysisDocumento14 páginasVoltage-Current Characteristic of Incandescent Lightbulbs: Measurement and AnalysisxongassilvaAinda não há avaliações

- Acs712 30a Range Current SensorDocumento3 páginasAcs712 30a Range Current SensorxongassilvaAinda não há avaliações

- Transimpedance Amplifier With Mic PDFDocumento23 páginasTransimpedance Amplifier With Mic PDFChanderKishoreJoshiAinda não há avaliações

- Understanding Microphone Sensitivity: by Jerad LewisDocumento3 páginasUnderstanding Microphone Sensitivity: by Jerad LewisxongassilvaAinda não há avaliações

- Dark Room Enlightenment - Lesser, Greater, and Greatest Kan & Li PDFDocumento43 páginasDark Room Enlightenment - Lesser, Greater, and Greatest Kan & Li PDFAlexandra Ioana Niculescu100% (1)

- Circles in Circles: Creating A Mathematical Model of Surface Water WavesDocumento15 páginasCircles in Circles: Creating A Mathematical Model of Surface Water WavesxongassilvaAinda não há avaliações

- Chap4 Waves BasicsDocumento33 páginasChap4 Waves BasicsVinay GuptaAinda não há avaliações

- RippleDocumento8 páginasRipplevindiskAinda não há avaliações

- Applications Manual For Computing Amplifiers - Philbrick 1966Documento121 páginasApplications Manual For Computing Amplifiers - Philbrick 1966wagnalang1639Ainda não há avaliações

- Chap 4 PDFDocumento40 páginasChap 4 PDFxongassilvaAinda não há avaliações

- Greatest Kan Li - Gathering The Cosmic Energy PDFDocumento47 páginasGreatest Kan Li - Gathering The Cosmic Energy PDFAlexandra Ioana NiculescuAinda não há avaliações

- Simple Chi Kung Warm Up Exercises - Mantak Chia PDFDocumento41 páginasSimple Chi Kung Warm Up Exercises - Mantak Chia PDFIrving BarreraAinda não há avaliações

- P2133500 PDFDocumento12 páginasP2133500 PDFxongassilvaAinda não há avaliações

- RippleDocumento8 páginasRipplevindiskAinda não há avaliações

- 1 - Tan Tien Chi Kung Mantak ChiaDocumento177 páginas1 - Tan Tien Chi Kung Mantak ChiaAnonymous KxjjlhMA95% (19)

- Fusion of Eight Psychic Channels - Opening and Sealing Psychic Channels PDFDocumento48 páginasFusion of Eight Psychic Channels - Opening and Sealing Psychic Channels PDFAlexandra Ioana Niculescu100% (2)

- KiCad TutorialDocumento18 páginasKiCad TutorialprageAinda não há avaliações

- Synthesis and Optimization of Digital Circuits PDFDocumento587 páginasSynthesis and Optimization of Digital Circuits PDFxongassilvaAinda não há avaliações

- KiCad Tutorial PDFDocumento36 páginasKiCad Tutorial PDFbanpioAinda não há avaliações

- Electronic Instrument Handbook Third EditionDocumento1.217 páginasElectronic Instrument Handbook Third Editionhashemowida100% (39)

- White-Light Diffraction With A CD: The Circular Slit. Basic Set-Up For The Experiment With The Reflective CDDocumento2 páginasWhite-Light Diffraction With A CD: The Circular Slit. Basic Set-Up For The Experiment With The Reflective CDxongassilvaAinda não há avaliações

- The CD Lens For Optical EngineeringDocumento6 páginasThe CD Lens For Optical EngineeringxongassilvaAinda não há avaliações

- A Four-Quadrant Analog Multiplier Under A Single Power SupplyDocumento6 páginasA Four-Quadrant Analog Multiplier Under A Single Power SupplyxongassilvaAinda não há avaliações

- Absolute-Value Circuit Using JunctionDocumento4 páginasAbsolute-Value Circuit Using JunctionxongassilvaAinda não há avaliações

- Engineering Silence: Active Noise Cancellation: Michael Benoit Christopher Camastra Melissa KennyDocumento12 páginasEngineering Silence: Active Noise Cancellation: Michael Benoit Christopher Camastra Melissa KennyxongassilvaAinda não há avaliações

- Nonlinear Op-Amp Circuits and Logarithmic AmplifiersDocumento31 páginasNonlinear Op-Amp Circuits and Logarithmic AmplifiersBeth ValerdiAinda não há avaliações

- MPY634Documento9 páginasMPY634api-3825669Ainda não há avaliações

- Linear Integrated CircuitsDocumento4 páginasLinear Integrated CircuitsJohn360% (1)

- Critikon Dinamap Compact - Service Manual 2Documento78 páginasCritikon Dinamap Compact - Service Manual 2Ayaovi JorlauAinda não há avaliações

- Multiplier PDFDocumento4 páginasMultiplier PDFHimanshu SaxenaAinda não há avaliações

- Cmos Four Quadrant Analog MultiplierDocumento15 páginasCmos Four Quadrant Analog MultiplierAnurag AroraAinda não há avaliações

- ICL8013 Four Quadrant Analog MultiplierDocumento8 páginasICL8013 Four Quadrant Analog MultiplierJuan Gil RocaAinda não há avaliações

- Rohini 90538804456Documento8 páginasRohini 90538804456KhanAinda não há avaliações

- Paper-4 Voltage Controlled, Low-Pass and High-Pass Filter Using Analog MultiplierDocumento8 páginasPaper-4 Voltage Controlled, Low-Pass and High-Pass Filter Using Analog MultiplierRachel WheelerAinda não há avaliações

- Copy of SE-Cat-REV-6Documento1.574 páginasCopy of SE-Cat-REV-6api-3809838Ainda não há avaliações

- UNIT-4 Lecture-1: Log, - Anti Log Amplifiers, Analog Multipliers and Their ApplicationsDocumento13 páginasUNIT-4 Lecture-1: Log, - Anti Log Amplifiers, Analog Multipliers and Their ApplicationschiranjibaviAinda não há avaliações

- ColocviuDocumento6 páginasColocviuAndra BordeaAinda não há avaliações

- Analog System Lab Pro ManualDocumento104 páginasAnalog System Lab Pro ManualPankaj BongaleAinda não há avaliações

- Comparison of Current Modes in CMOS Analog MultipliersDocumento4 páginasComparison of Current Modes in CMOS Analog MultipliersseventhsensegroupAinda não há avaliações

- Questions On Operational AmplifierDocumento4 páginasQuestions On Operational AmplifierSubhashree DashAinda não há avaliações

- Electromechanical Relay GuideDocumento19 páginasElectromechanical Relay GuideRajesh Naik Dharavath100% (1)

- IEEE - CMOS Transconductance Amplifiers, Architectures and Active Filters TutorialDocumento10 páginasIEEE - CMOS Transconductance Amplifiers, Architectures and Active Filters Tutorialdragos_bondAinda não há avaliações

- A High-Voltage Sic-Based Boost PFC For Led ApplicationsDocumento10 páginasA High-Voltage Sic-Based Boost PFC For Led Applicationsjhon jairo gomez solanoAinda não há avaliações

- Data Acquisition Systems (DAS) in GeneralDocumento3 páginasData Acquisition Systems (DAS) in GeneralArjun SinghAinda não há avaliações

- Dr. Yuri Panarin's Notes on Log and AntiLog AmplifiersDocumento24 páginasDr. Yuri Panarin's Notes on Log and AntiLog AmplifiersCostel CojocaruAinda não há avaliações

- Four Quadrant Multiplier CmosDocumento11 páginasFour Quadrant Multiplier CmosRodrigo SantosAinda não há avaliações

- Analog multiplier circuit using opampsDocumento4 páginasAnalog multiplier circuit using opampsxongassilvaAinda não há avaliações

- ANALOG MULTIPLIERS: KEY COMPONENTS AND APPLICATIONSDocumento17 páginasANALOG MULTIPLIERS: KEY COMPONENTS AND APPLICATIONSMarykutty CyriacAinda não há avaliações

- AD633 Analog MultiplierDocumento16 páginasAD633 Analog MultiplierCostel CostescuAinda não há avaliações

- Multipliers ApplicationsDocumento16 páginasMultipliers ApplicationsVictorSAinda não há avaliações

- Multiplier & Divider Questions and Answers - SanfoundryDocumento5 páginasMultiplier & Divider Questions and Answers - SanfoundryHarith Nawfel100% (1)

- Ch8 Op Amp Nonlinear Circuits & FiltersDocumento31 páginasCh8 Op Amp Nonlinear Circuits & FiltersPahala SamosirAinda não há avaliações

- LIC Unit 3Documento25 páginasLIC Unit 3mekalajesiAinda não há avaliações

- Analog MultiplierDocumento9 páginasAnalog MultiplierPravin Sanap0% (1)

- 00002686Documento3 páginas00002686GautamSikka100% (1)