Escolar Documentos

Profissional Documentos

Cultura Documentos

H. Liu, D. K. Mohata, A. Nidhi, V. Saripalli, V. Narayanan and S. Datta

Enviado por

Mas MoDescrição original:

Título original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

H. Liu, D. K. Mohata, A. Nidhi, V. Saripalli, V. Narayanan and S. Datta

Enviado por

Mas MoDireitos autorais:

Formatos disponíveis

Exploration of Vertical MOSFET and Tunnel FET Device Architecture for Sub 10nm Node Applications

H. Liu, D. K. Mohata, A. Nidhi, V. Saripalli, V. Narayanan and S. Datta

The Pennsylvania State University, PA 16802, E-mail: hxl249@psu.edu, Phone: (814) 753 0026, Fax: (814) 865 7065

Introduction: With growing challenges in maintaining physical gate-length (L

g

) scaling and device performance

tradeoff, extending the technology roadmap with lateral devices to sub-10 nm technology node with 37nm contacted

gate-pitch (L

pitch

) is becoming increasingly difficult.

[1]

At or beyond this point, vertical device architecture can bring

in new perspectives with regards to increasing device density and improving performance

[2]

, simultaneously.

Because vertical devices use side-gates which can be contacted outside the active region (Fig. 1), the contacted gate

area can be reduced, resulting in ~40% density gain over lateral devices. However, vertical configuration brings

additional gate-dielectric overlap for the gate, requires bottom source (or drain) extensions and metal plugs for the

contacts, all of which increase the device parasitic elements. In this abstract, a double-gate vertical device

architecture has been evaluated using TCAD simulations. Besides showing the area advantage, parasitics included

energy efficiency and switching performance of vertical n-channel MOSFET and n-type Hetero-junction Tunnel

FET (N-HTFET) are systematically compared for low operating power (LOP) logic applications. L

pitch

of 37nm is

used to target sub-10nm technology node, while L

g

of 16nm is used to maintain short channel effects.

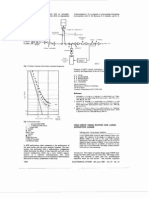

Vertical FET Physical Layout: The cascaded inverter layouts using planar CMOS, FinFETs and vertical FETs are

shown in Fig. 1. The vertical FETs have source terminals connected at the bottom and eventually to the surface with

metal plugs. The source region is recessed down to reduce the gate-to-source capacitance. FinFET inverters exhibit

similar area as planar CMOS (10FW), while the vertical FETs show ~40% area reduction (Table I).

Vertical FET Parasitics: For the evaluation of the parasitic components, the base structure of shared bottom-source

is used as shown in Fig. 2(a). The device spacing (L

pitch

) is 37nm. The total gate fringe capacitance C

g,fringe

comprises

of side-gate to plug, side-gate to drain extension and side-gate to source extension capacitance due to fringe field

through the low-k dielectric spacer. The total overlap capacitance, C

ov

includes gate to source/drain overlap of 1 nm.

The lateral gate-oxide extension (L

ox,ext

) induced C

ox,ext

becomes part of C

g,fringe

because of the recess and low-k

filling. Vertical HTFET and Si NMOS I

DS

-V

GS

characteristics are compared in Fig. 2(b). Minimum sub-threshold

slope of 30mV is achieved in HTFET. With off-state current I

OFF

<5nA/m (LOP target) at V

GS

=0V, on-state current

I

ON

of 403A/m and 397A/um at V

DD

=0.5V are obtained in vertical Si NMOS and III-V HTFET, respectively.

Fig. 3 provides the parasitic extraction methods with small-signal simulation using vertical Si NMOS as an example.

C

g,fringe

of 0.15fF/m is extracted from

ILD

variation. C

ov

of 0.213fF/m is obtained from C

g,total

-C

g,fringe

extrapolation

at L

g,eff

=0nm. C

ox,ext

of 0.047fF/m is extracted from L

ox,ext

variation on the 1

st

order estimation. The extension series

resistance (R

SD,ext

) of 35-m is extracted from Z parameter analysis.

[3]

R

S,plug

is below 0.5-m for plug height of

28nm with tungsten. Similar evaluations are performed for both Si NMOS and III-V HTFET at V

DD

=0.3V and 0.5V.

Vertical FET Energy-Performance: As shown in Fig. 4, C

g,total

of III-V HTFET is dominated by C

gd

at high V

GS

,

mainly due to the enhanced Miller capacitance.

[4]

When V

GS

increases from 0 to V

DD

, HTFETs offers smaller C

g,total

compared to Si NMOS (Fig. 5) due to (i) the lower density of states electron mass of III-V and (ii) the required

lower drain doping to prevent ambipolar conduction, which also results in C

ov

reduction, however with a penalty of

increased R

D,ext

. Fig. 6 shows the parasitic capacitance components comparison between HTFET and Si NMOS at

different V

DD

. C

g,fringe

is similar for both Si NMOS and III-V HTFET. Despite lower I

ON

, the low C

g,total

in HTFET

offers advantage in energy and delay reduction. Table III shows the device performance comparison. At V

DD

=0.5V,

intrinsic delay (

intrinsic

= C

g,total

V

DD

/I

ON

) of 0.438ps for III-V HTFET and 0.714ps for Si NMOS can be obtained.

Energy-delay figure of merit is then evaluated for FO1 (fan-out=1) inverter assuming symmetric PMOS

performance with Miller effect considered (Fig.7). Si NMOS can achieve 1ps delay at V

DD

>0.6V, while HTFET has

superior energy efficiency below 0.6V. Fig. 8 shows the cut-off frequency (F

T

) versus DC power relationship,

considering the parasitics. III-V HTFET presents further advantages for low-power analog applications. Since the

contact resistance (R

co

) dominates the series resistance beyond 32nm technology node

[1]

, the analysis of R

co

effect is

important (Fig. 9). Considering R

co

of 100 (resistivity of 10

-8

-cm

2

) for 10.01m

2

contact, HTFET and Si

NMOS show ~26% and ~40% I

ON

degradation at V

DD

=0.5V, respectively. R

co

requires further improvement to

maintain the performance.

Conclusions: A vertical device architecture having ~40% density improvement over planar for sub-10nm

technology node has been evaluated for Si NMOS and III-V HTFET with L

g

=16nm. For LOP applications including

the effect of parasitic elements, the HTFET presents superior energy efficiency and desired low-power analog

performance for V

DD

<0.6V, while MOSFET is superior for V

DD

>0.6V. To further improve MOSFET performance,

I

ON

needs to be improved with higher injection velocity materials (e.g. III-V). For delay reduction, the parasitic

capacitances (C

ov

and C

g,fringe

) and contact resistance need to be further engineered for both MOSFETs and TFETs.

[1] L. Wei et al., IEEE Trans. Elec. Dev., vol. 56, no. 2, 2009. [2] D. K. Mohata et al., IEEE IEDM Tech. Dig., 2011.

[3] R. Torres-Torres et al., IEEE Electronics Lett., vol. 39, no. 20, 2003. [4] S. Mookerjea et al., IEEE Trans. Elec. Dev., vol. 56, no. 9, 2009.

Fig. 1 Planar CMOS (a), FinFET (b) and vertical-FET (c) cascaded inverter layout

example with illustrated gate-pitch and cascaded vertical NMOS and HTFETs cross-

session. F is the minimum feature. The vertical FETs have reduced layout area.

Fig. 2 (a) Simulated structure showing parasitic

components. Lpitch=37nm for 10nm technology.

(b) I

DS

-V

GS

at different V

DS

of vertical Si NMOS and

HTFET. I

ON

=23A/m, 403A/m, 743A/m for

Si NMOS at V

DD

=0.3V, 0.5V, 0.61V. I

ON

=130

A/m, 398A/m for HTFET at V

DD

=0.3V, 0.5V.

Fig. 3 Vertical NMOS

Parasitic Extraction: (a)

C

g,fringe

extracted from

ILD

variation. (b) C

ox,ext

extracted by varying

L

ox,ext

. (c) C

ov

extracted

from L

g

extrapolation.

(d) R

SD,ext

extracted from

Z parameter to avoid

short-channel length

extrapolation uncertainty.

Fig. 4 C-V plots of HTFETs at

V

DS

= 0.3V, 0.5V. At low V

GS

,

C

gg

is dominant by C

gs

. As V

GS

increases, C

gd

dominates as on-

state enhanced C

miller

.

Fig. 5 Normalized capacitance

comparison of vertical NMOS

and HTFET at V

DD

=0.5V.

Lower C

g

in HTFET comes

from lower drain doping.

Fig. 8 F

T

-DC power of

vertical HTFET and Si

NMOS of L

g

=16nm.

HTFET shows superior high

frequency performance at

low DC power.

Fig. 6 C

g,total

and parasitic capaci-

tance comparison of vertical

HTFET and Si NMOS. HTFET

presents lower C

g,total

and reduced

C

ov

compared to Si NMOS.

(a) (b) (c) (d)

,

=

,

,

=

,

,

|

,

=0

Fig. 7 Switching energy-delay for

FO1 inverter using effective

current (I

EFF

) evaluation. Cross-

over happens at V

DD

=0.6V for

NMOS. HTFET shows lower

power advantage below 0.6V.

Table II Parameters in Simulation Setup

L

pitch

37nm L

N+

5nm

L

g

16nm t

B

7nm

L

ox,ext

7nm EOT 0.7

L

ov

1nm t

G

5nm

L

res

5nm

ILD

/

0

2.3

L

s,ext

11nm

gate

5.64 /

L

plug

28nm t

plug

8nm

Si NMOS S/D Doping 1e20 cm

-3

N-HTFET Source Doping (GaSb) 2e17 cm

-3

N-HTFET Drain Doping (InAs) 5e19 cm

-3

For N-HTFET: Eg,GaSb=0.804eV,

Eg, InAs=0.44eV, Ec=0.796eV

Table I Normalized Area of Laterial/Vertical FETs

Planar

CMOS

FinFET

Vertical

FET

Cascaded

Inverter

100% 100% ~ 60%

(a)

(b)

= (

)/2

= 2(

,

+

)

|(

= 0.5

|(

= 0.5

)

Fig. 9 Contact resistance (R

co

)

effect on vertical HTFET and Si

NMOS. HTFET shows lower

current degradation (26%) with

large R

co

than NMOS (40%) due

to high tunneling resistance.

Table III Performance Comparison

Vertical

HTFET

Vertical

NMOS

V

DD

(V) 0.5 0.5

Cg,total

(fF/m)

0.367 0.595

Cg,fringe

(fF/m)

0.148 0.153

I

OFF

(nA/m)

5 5

I

ON

(A/m)

398 403

R

SD,ext

(-m)

52 35

intrinsic

(ps)

0.438 0.714

,

= (

12

)|

1/

2

=0

,

= (

22

12

)|

1/

2

=0

(b) FinFETs (c) Vertical FETs (a) Planar CMOS

Você também pode gostar

- Mosfet To TfetDocumento4 páginasMosfet To TfetmuktikantaAinda não há avaliações

- Performance Study For Quad Gate Vertically Stacked Junctionless NanosheetDocumento6 páginasPerformance Study For Quad Gate Vertically Stacked Junctionless NanosheetTarun SinghalAinda não há avaliações

- A 5.8-Ghz High Efficient, Low Power, Low Phase Noise Cmos Vco For Ieee 802.11ADocumento4 páginasA 5.8-Ghz High Efficient, Low Power, Low Phase Noise Cmos Vco For Ieee 802.11ARitika SinghAinda não há avaliações

- Scaling Challenges and Device Requirements for Sub-50 nm Planar CMOS TransistorsDocumento2 páginasScaling Challenges and Device Requirements for Sub-50 nm Planar CMOS TransistorsSwati MattaAinda não há avaliações

- Low-Loss Millimeter-Wave Phase Shifters Based On Mechanical ReconfigurationDocumento6 páginasLow-Loss Millimeter-Wave Phase Shifters Based On Mechanical ReconfigurationArun KumarAinda não há avaliações

- Drain Current Modeling of Tunnel FET Using Simpson's RuleDocumento9 páginasDrain Current Modeling of Tunnel FET Using Simpson's RuleFebhe Maulita May PramastaAinda não há avaliações

- Design and Simulation of A Two Stage OPAMPDocumento4 páginasDesign and Simulation of A Two Stage OPAMPAbd TashAinda não há avaliações

- Design of Directional Coupler in Bulk-CMOS Switch TechnologyDocumento4 páginasDesign of Directional Coupler in Bulk-CMOS Switch TechnologyBogdan TancAinda não há avaliações

- D 119Documento35 páginasD 119Mohammad Ayatullah MaktoomAinda não há avaliações

- A 900Mhz RF Energy Harvesting Module: Taris Thierry, Vigneras Valérie Fadel LudivineDocumento4 páginasA 900Mhz RF Energy Harvesting Module: Taris Thierry, Vigneras Valérie Fadel Ludivinekavirasu1990Ainda não há avaliações

- The Impact of Fringing Field On The Device Performance of A P-Channel Tunnel Field-Effect Transistor With A High-Gate DielectricDocumento6 páginasThe Impact of Fringing Field On The Device Performance of A P-Channel Tunnel Field-Effect Transistor With A High-Gate DielectricdabalejoAinda não há avaliações

- Channel Doping Impact On Finfets For 22Nm and BeyondDocumento2 páginasChannel Doping Impact On Finfets For 22Nm and Beyondnithint60Ainda não há avaliações

- Ref 26 Fully Coupled 3-D Device Simulation of Negative Capacitance FinFETs For Sub 10 NM IntegrationDocumento4 páginasRef 26 Fully Coupled 3-D Device Simulation of Negative Capacitance FinFETs For Sub 10 NM IntegrationM. Ashikuzzaman KowshikAinda não há avaliações

- Hollow Rectangular WaveguideDocumento6 páginasHollow Rectangular Waveguidemoluewli100% (1)

- Analog Circuits in 28 NM and 14 NM Finfet: Lukas Dörrer, Franz Kuttner, Francesco Conzatti, and Patrick TortaDocumento15 páginasAnalog Circuits in 28 NM and 14 NM Finfet: Lukas Dörrer, Franz Kuttner, Francesco Conzatti, and Patrick TortaRodrigo SantosAinda não há avaliações

- Design of Broadband Lumped Element BalunsDocumento4 páginasDesign of Broadband Lumped Element BalunsA. Villa100% (1)

- A Two Op-A Mps Third-Order Modulator With Complex Conjugate NTF ZerosDocumento4 páginasA Two Op-A Mps Third-Order Modulator With Complex Conjugate NTF ZerosPham Viet ThanhAinda não há avaliações

- 3rd PaperDocumento9 páginas3rd Paperaruna kumariAinda não há avaliações

- A Compact Analytical Model For The Drain Current of Gate-All-Around Nanowire Tunnel FET Accurate From Sub-Threshold To ON-StateDocumento5 páginasA Compact Analytical Model For The Drain Current of Gate-All-Around Nanowire Tunnel FET Accurate From Sub-Threshold To ON-StateKadava R N Karthik 20PHD7152 (SENSE)Ainda não há avaliações

- Filter Design For Grid Connected InvertersDocumento7 páginasFilter Design For Grid Connected InvertersAirton FloresAinda não há avaliações

- A Low On-Resistance Triple RESURF SOI LDMOS With Planar and Trench Gate IntegrationDocumento5 páginasA Low On-Resistance Triple RESURF SOI LDMOS With Planar and Trench Gate IntegrationwoshisimoxAinda não há avaliações

- 1.5GHz Negative Impedance Converter PaperDocumento3 páginas1.5GHz Negative Impedance Converter PaperNestor Alberto EscalaAinda não há avaliações

- Simultaneous Noise and Impedance MatchingDocumento4 páginasSimultaneous Noise and Impedance MatchingDurbha RaviAinda não há avaliações

- Series Fed MSA AntennaDocumento3 páginasSeries Fed MSA Antennaanirban pahariAinda não há avaliações

- Pid00050 2 CmosDocumento8 páginasPid00050 2 CmosSaurabh ChakravartyAinda não há avaliações

- Compact Analytical Drain Current Model of Gate-All-Around Nanowire Tunneling FETDocumento5 páginasCompact Analytical Drain Current Model of Gate-All-Around Nanowire Tunneling FETKadava R N Karthik 20PHD7152 (SENSE)Ainda não há avaliações

- Abstract:: RatioDocumento18 páginasAbstract:: RatioNaveen ChaubeyAinda não há avaliações

- Stacked Nanosheet Gate-All-Around Transistor Scaling Beyond FinFETDocumento2 páginasStacked Nanosheet Gate-All-Around Transistor Scaling Beyond FinFETGary Ryan DonovanAinda não há avaliações

- MDLX Atc App Note Pi 026Documento0 páginaMDLX Atc App Note Pi 026david_benavidez_3Ainda não há avaliações

- Equivalent Circuit Model of Slotted Ground StructuresDocumento3 páginasEquivalent Circuit Model of Slotted Ground StructureshmalrizzoAinda não há avaliações

- Wangkheirakpam2021 Article LinearityPerformanceAndIntermoDocumento9 páginasWangkheirakpam2021 Article LinearityPerformanceAndIntermosharmasamriti27Ainda não há avaliações

- Agilent Eesof Eda: Overview On Designing A Low-Noise Vco On Fr4Documento6 páginasAgilent Eesof Eda: Overview On Designing A Low-Noise Vco On Fr4bayman66Ainda não há avaliações

- Application: Design For ProcessDocumento4 páginasApplication: Design For ProcessjaberyemeniAinda não há avaliações

- RFQ INJECTOR FOR THE SPES PROJECT RADIOACTIVE ION BEAMDocumento3 páginasRFQ INJECTOR FOR THE SPES PROJECT RADIOACTIVE ION BEAMcomunian1Ainda não há avaliações

- VFT Study For EHV-GIS Substation: Amit Kumar and Mahesh K. MishraDocumento6 páginasVFT Study For EHV-GIS Substation: Amit Kumar and Mahesh K. Mishraarunw110Ainda não há avaliações

- Conclusion:: To DiagnosticsDocumento3 páginasConclusion:: To DiagnosticsDhaval PatelAinda não há avaliações

- Gate Tunneling Current and Quantum Effects in Deep Scaled MosfetsDocumento5 páginasGate Tunneling Current and Quantum Effects in Deep Scaled Mosfetsashishj1083Ainda não há avaliações

- IEEE - CMOS Transconductance Amplifiers, Architectures and Active Filters TutorialDocumento10 páginasIEEE - CMOS Transconductance Amplifiers, Architectures and Active Filters Tutorialdragos_bondAinda não há avaliações

- Broadband Low Noise Amplifier with Built-in LinearizerDocumento8 páginasBroadband Low Noise Amplifier with Built-in LinearizerRAJAMOHANAinda não há avaliações

- Dual Material Gate Technique For Enhanced Transconductance and Breakdown Voltage of Trench Power MOSFETsDocumento17 páginasDual Material Gate Technique For Enhanced Transconductance and Breakdown Voltage of Trench Power MOSFETsMamidala Jagadesh KumarAinda não há avaliações

- Baliga Figure of MeritDocumento3 páginasBaliga Figure of MeritKyle BotheAinda não há avaliações

- "Tunnel Field Effect Transistors (TFET) ": Prepared By:-Group 10Documento24 páginas"Tunnel Field Effect Transistors (TFET) ": Prepared By:-Group 10Rajesh Sharma50% (2)

- Doping and Doping Less III-V Tunnel Field Effect Transistors (TFET) : Investigation On Reasons For ON Current ImprovementDocumento4 páginasDoping and Doping Less III-V Tunnel Field Effect Transistors (TFET) : Investigation On Reasons For ON Current ImprovementNiranjan ReddyAinda não há avaliações

- TFETDocumento4 páginasTFETSurya KalagaAinda não há avaliações

- SSE 2010-SOI Versus Bulk-Silicon Nanoscale FinFETsDocumento4 páginasSSE 2010-SOI Versus Bulk-Silicon Nanoscale FinFETsWenqi ZhangAinda não há avaliações

- Baccarelli Et Al. - 2007 - Harmonic-Tuned Patch Active Integrated Antenna ForDocumento4 páginasBaccarelli Et Al. - 2007 - Harmonic-Tuned Patch Active Integrated Antenna Forsagar378Ainda não há avaliações

- Review of Modern Field Effect Transistor Technologie1Documento8 páginasReview of Modern Field Effect Transistor Technologie1G ManAinda não há avaliações

- Enhancing Frequency Performance of Underlap Tunnel Field-Effect Transistor For Analog/RF ApplicationsDocumento7 páginasEnhancing Frequency Performance of Underlap Tunnel Field-Effect Transistor For Analog/RF Applicationsutkarsh chaudharyAinda não há avaliações

- A Practical Approach To A Compct Wide-Band SMT Directional CouplerDocumento3 páginasA Practical Approach To A Compct Wide-Band SMT Directional Coupleragmnm1962Ainda não há avaliações

- High Power VHF Frequency-Hopping FiltersDocumento10 páginasHigh Power VHF Frequency-Hopping FiltersA. VillaAinda não há avaliações

- Implementation of Second Order Switched Capacitors Filters With Feedback SignalDocumento3 páginasImplementation of Second Order Switched Capacitors Filters With Feedback SignalInternational Journal of Application or Innovation in Engineering & ManagementAinda não há avaliações

- Write Up1Documento10 páginasWrite Up1Ishita AggarwalAinda não há avaliações

- Performance Very Low Frequency Filters: Design Considerations For HighDocumento4 páginasPerformance Very Low Frequency Filters: Design Considerations For Highmvmuthukumar88Ainda não há avaliações

- Two-Stage Op-Amp and Integrator Realisation Through Gaasp/Algasb Nanowire Cp-TfetDocumento6 páginasTwo-Stage Op-Amp and Integrator Realisation Through Gaasp/Algasb Nanowire Cp-TfetRakesh KumarAinda não há avaliações

- Microelectronic CircuitDocumento696 páginasMicroelectronic CircuitImtiaz AhmedAinda não há avaliações

- A High-Performance 40-85 GHZ Mmic SPDT Switch Using Fet-Integrated Transmission Line StructureDocumento3 páginasA High-Performance 40-85 GHZ Mmic SPDT Switch Using Fet-Integrated Transmission Line StructureBisuAinda não há avaliações

- Full Adder Design With GDI Cell and Independent Double Gate TransistorDocumento5 páginasFull Adder Design With GDI Cell and Independent Double Gate TransistorMadhu Sudhan DAinda não há avaliações

- Performance Evaluation of Finfet-Based Fpga Cluster Under Threshold Voltage VariationDocumento4 páginasPerformance Evaluation of Finfet-Based Fpga Cluster Under Threshold Voltage VariationKunal SinghAinda não há avaliações

- Operational Transconductance Amplifier For Low Frequency ApplicationDocumento3 páginasOperational Transconductance Amplifier For Low Frequency Applicationkok6100% (1)

- Organic Light-Emitting Transistors: Towards the Next Generation Display TechnologyNo EverandOrganic Light-Emitting Transistors: Towards the Next Generation Display TechnologyAinda não há avaliações

- Fabrication of Flexible and Vertical Silicon Nanowire ElectronicsDocumento5 páginasFabrication of Flexible and Vertical Silicon Nanowire ElectronicsMas MoAinda não há avaliações

- Nanoelectronics and at Imec: More-than-MooreDocumento52 páginasNanoelectronics and at Imec: More-than-MooreMas MoAinda não há avaliações

- H. Liu, D. K. Mohata, A. Nidhi, V. Saripalli, V. Narayanan and S. DattaDocumento2 páginasH. Liu, D. K. Mohata, A. Nidhi, V. Saripalli, V. Narayanan and S. DattaMas MoAinda não há avaliações

- Silicon-Nanowire Mosfets Cmos Compatible Gate-All-Around VerticalDocumento4 páginasSilicon-Nanowire Mosfets Cmos Compatible Gate-All-Around VerticalMas MoAinda não há avaliações

- Boosting The On-Current of Silicon Nanowire Tunnel-Fets: KCL - Ll.EuvenDocumento2 páginasBoosting The On-Current of Silicon Nanowire Tunnel-Fets: KCL - Ll.EuvenMas MoAinda não há avaliações

- Fabrication of Nanowire MOSFETS Using SOI SubstratesDocumento14 páginasFabrication of Nanowire MOSFETS Using SOI SubstratesMas MoAinda não há avaliações

- Vertical Silicon-Nanowire Formation and Gate-All-Around MOSFETDocumento4 páginasVertical Silicon-Nanowire Formation and Gate-All-Around MOSFETMas MoAinda não há avaliações

- Silicon Vertically Integrated Nanowire Field Effect TransistorsDocumento5 páginasSilicon Vertically Integrated Nanowire Field Effect TransistorsMas MoAinda não há avaliações

- 05746327Documento3 páginas05746327Mas MoAinda não há avaliações

- 11 Edl Zhou Sidewall TFETsDocumento3 páginas11 Edl Zhou Sidewall TFETsMas MoAinda não há avaliações

- Vertical Silicon Nanowire CMOS InverterDocumento4 páginasVertical Silicon Nanowire CMOS InverterMas MoAinda não há avaliações

- 00333812Documento7 páginas00333812Mas MoAinda não há avaliações

- 11 Edl Zhou Sidewall TFETsDocumento3 páginas11 Edl Zhou Sidewall TFETsMas MoAinda não há avaliações

- 04381446Documento12 páginas04381446Mas MoAinda não há avaliações

- MicrowaveDocumento22 páginasMicrowaveMas MoAinda não há avaliações

- Logic Gates With A Single Graphene Transistor: Roman Sordan Floriano Traversi Valeria RussoDocumento4 páginasLogic Gates With A Single Graphene Transistor: Roman Sordan Floriano Traversi Valeria RussoMas MoAinda não há avaliações

- Fan 7317Documento23 páginasFan 7317Graciela Judith Dacto ChAinda não há avaliações

- Dual-Frequency Modified C/V Technique: 150 125 100 7 5 1 50 25 / I 15MW/600nmDocumento2 páginasDual-Frequency Modified C/V Technique: 150 125 100 7 5 1 50 25 / I 15MW/600nmkurabyqldAinda não há avaliações

- Design and Implementation of 1 GHZ Current Starved Voltage Controlled Oscillator (Vco) For PLL Using 90Nm Cmos TechnologyDocumento6 páginasDesign and Implementation of 1 GHZ Current Starved Voltage Controlled Oscillator (Vco) For PLL Using 90Nm Cmos Technologyanon_701088587Ainda não há avaliações

- CCM Vs DCMDocumento27 páginasCCM Vs DCMErnesto Gonzalez UrdanetaAinda não há avaliações

- A3959 DatasheetDocumento12 páginasA3959 DatasheetOctavio ParedesAinda não há avaliações

- ElectronicsDocumento96 páginasElectronicsAnjan SenguptaAinda não há avaliações

- Research Admissions Syllabus July 2020Documento35 páginasResearch Admissions Syllabus July 2020AnbumaniAinda não há avaliações

- DatasheetDocumento13 páginasDatasheetkishore kumarAinda não há avaliações

- Ec1461 Vlsi DesignDocumento17 páginasEc1461 Vlsi DesignArunkumarAinda não há avaliações

- TK8P65W Datasheet en 20140917Documento10 páginasTK8P65W Datasheet en 20140917Leudin Russo PedrozaAinda não há avaliações

- KA1M0565R/KA1H0565R: Fairchild Power Switch (FPS)Documento10 páginasKA1M0565R/KA1H0565R: Fairchild Power Switch (FPS)Guilherme Ribeiro BarbosaAinda não há avaliações

- LTC 7001Documento18 páginasLTC 7001anaseng92_960680896Ainda não há avaliações

- Vlsi HW 3Documento2 páginasVlsi HW 3Tâm LưuAinda não há avaliações

- Mp2a5038 FujiDocumento24 páginasMp2a5038 FujiSafarudinAnugrahAinda não há avaliações

- Using An Arduino To Measure Frequency Response and Current Voltage Device Characteristics in Electronics LabsDocumento14 páginasUsing An Arduino To Measure Frequency Response and Current Voltage Device Characteristics in Electronics LabsJAWWAD SADIQ AYONAinda não há avaliações

- HT7 L4815 V 100Documento9 páginasHT7 L4815 V 100Enéas BaroneAinda não há avaliações

- (Ebook - Electronics) - Analog and Mixed Signal Vlsi CircuitDocumento418 páginas(Ebook - Electronics) - Analog and Mixed Signal Vlsi CircuitPuja GuptaAinda não há avaliações

- FDMC 8884Documento7 páginasFDMC 8884Kholit LitAinda não há avaliações

- STB45NF06 PDFDocumento6 páginasSTB45NF06 PDFjose luisAinda não há avaliações

- Principles of Semiconductor DevicesDocumento515 páginasPrinciples of Semiconductor Devicestrungkiendt9100% (1)

- 11N80Documento4 páginas11N80Anil BpsAinda não há avaliações

- Design and Implementation of A Discrete-Time Proportional Integral (PI) Controller For The Temperature Control of A Heating PadDocumento11 páginasDesign and Implementation of A Discrete-Time Proportional Integral (PI) Controller For The Temperature Control of A Heating PadYe AnAinda não há avaliações

- 13 Circuit Descriptions: 13-1 Overall Block Structure Power TreeDocumento8 páginas13 Circuit Descriptions: 13-1 Overall Block Structure Power TreeJoseni FigueiredoAinda não há avaliações

- 6th Sem SyllabusDocumento13 páginas6th Sem SyllabusAbhishek GuptaAinda não há avaliações

- str-x6768n Ds en PDFDocumento9 páginasstr-x6768n Ds en PDFCarlAinda não há avaliações

- Digital Logic Structures and Transistor BasicsDocumento49 páginasDigital Logic Structures and Transistor BasicsNirmal GuptaAinda não há avaliações

- IRFP450 Mosfet 500V 14ADocumento8 páginasIRFP450 Mosfet 500V 14AJunim CarvalhoAinda não há avaliações

- Application Notes UC3710TDocumento16 páginasApplication Notes UC3710TSHAHID_71Ainda não há avaliações

- Comparative Analysis of Low Power 10T and 14T FullDocumento6 páginasComparative Analysis of Low Power 10T and 14T Fullkhaja mohiddienAinda não há avaliações