Escolar Documentos

Profissional Documentos

Cultura Documentos

Verilog/Digital FAQS by Verilog Course Team Email:Info@Verilogcourseteam - Com WWW - Vlsi

Enviado por

verilogcourseteamDescrição original:

Título original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Verilog/Digital FAQS by Verilog Course Team Email:Info@Verilogcourseteam - Com WWW - Vlsi

Enviado por

verilogcourseteamDireitos autorais:

Formatos disponíveis

Verilog/Digital FAQS

By

Verilog Course Team

Email:info@verilogcourseteam.com

www.vlsifaqs.blogspot.com

www.verilogcourseteam.com

Verilog Course Team www.verilogcourseteam.com

DISCLAIMER

Verilog Course Team does not warrant or assume any legal liability or responsibility for the

accuracy, completeness, or usefulness of any information, apparatus, product, or process

disclosed. No warranty of any kind, implied, expressed or statutory, including to fitness for

a particular purpose and freedom from computer virus, is given with respect to the

contents of this document or its hyperlinks to other Internet resources. Reference in this

document to any specific commercial products, processes, or services, or the use of any

trade, firm or corporation name is for the information, and does not constitute

endorsement, recommendation, or favoring.

Verilog Course Team www.verilogcourseteam.com

About Verilog Course Team

Verilog Course Team is a Electronic Design Services (EDS) for VLSI / EMBEDDED and

MATLAB, delivering a wide variety of end-to-end services , including design ,

development, & testing for customers around the world .With proven expertise across multiple

domains such as Consumer Electronics Market ,Infotainment, Office Automation, Mobility and

Equipment Controls. Verilog Course Team is managed by Engineers / Professionals

possessing significant industrial experience across various application domains and

engineering horizontals . Our engineers have expertise across a wide range of

technologies, to the engineering efforts of our clients. Leveraging standards

based components and investments in dedicated test lab infrastructure; we offer innovative,

flexible and cost-effective Services and solutions.

Our Mission

Our mission is to provide cost effective, technology independent, good quality reusable

Intellectual Property cores with quality and cost factor are our important constraints so as

to satisfy our customers ultimately. We develop and continuously evaluate systems so as to

pursue quality in all our deliverables. At our team, we are completely dedicated to customer’s

requirements. Our products are designed and devoted to empower their competitive edge and

help them succeed.

Verilog Course Team www.verilogcourseteam.com

1.Design a circuit(positive edge ) that detect the sequence when input changes

from 0 to 1,the output should go high for only one clock pulse.

clk

rst

in

out

2. Design a circuit to detect when the 2‐16 bits inputs are same.

3. Assume b = 3 and c = 5, after the first @ (posedge clk) what is the value of a?

4. After the first @ (posedge clk), does this do a swap?

Verilog Course Team www.verilogcourseteam.com

5. Consider the following code:

`define FALSE 0

`define TRUE 1

initial

begin

a = `FALSE;

a <= `TRUE;

if (a == `TRUE)

$display ("True");

else

$display ("False");

end

What will print out? True or False?

6. Design AND, OR gate using 2:1 mux.

7. Draw the circuit to avoid the Set‐up and Hold‐time violation.

8. Consider the following code:

always@(posedge clk)

if(rst==0)

out<=1’b0;

else

out<=data_in;

a. Draw the synthesis view for the above code.

b. Modify the code for Asynchronous Reset.

c. Draw the timing diagram for synchronous and asynchronous reset.

9. How to test the functionality (test cases) of a FIFO.

10. What is the advantage of using Gray code instead of Binary code while

designing FIFO.

11. What are the parameters to be considered before starting the design work.

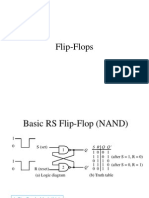

12. Design EX‐OR gate using 4 NAND gates.

13. Design EX‐NOR gate using 4 NOR gates.

Verilog Course Team www.verilogcourseteam.com

14. What will be the synthesis structure?

Verilog Course Team www.verilogcourseteam.com

Dream IT, We make U to Deliver

15. Consider the following code,

always@(posedge clk)

begin

a=b;

b=c;

c=a;

end

What logic does the code implies.

Verilog Course Team www.verilogcourseteam.com

Você também pode gostar

- Ring Oscillator IssueDocumento2 páginasRing Oscillator IssueAnonymous Mw7ZFF3A3Ainda não há avaliações

- Fpga Programming Using Verilog HDL LanguageDocumento89 páginasFpga Programming Using Verilog HDL LanguageSidhartha Sankar Rout0% (1)

- RTL2GDSFLOWDocumento23 páginasRTL2GDSFLOWAbhishek Gupta0% (1)

- EE434 ASIC Digital Systems Lab Guide: Automatic Layout GenerationDocumento47 páginasEE434 ASIC Digital Systems Lab Guide: Automatic Layout Generationijalab1Ainda não há avaliações

- Nvme Pcie SSD M.2 ManualDocumento56 páginasNvme Pcie SSD M.2 ManualDummy BearAinda não há avaliações

- VHDL PDFDocumento112 páginasVHDL PDFvivek patelAinda não há avaliações

- Introduction To VHDLDocumento88 páginasIntroduction To VHDLpusd_90Ainda não há avaliações

- Verilog VII Synthesis of Combinational LogicDocumento18 páginasVerilog VII Synthesis of Combinational Logicvortex2910_899547857Ainda não há avaliações

- STA AssignmentsDocumento3 páginasSTA AssignmentsTejas DharaniAinda não há avaliações

- 1.FPGA Design Flow Processes PropertiesDocumento5 páginas1.FPGA Design Flow Processes Propertiesmachnik1486624Ainda não há avaliações

- VHDL Coding Tips and TricksDocumento209 páginasVHDL Coding Tips and TricksvinutaAinda não há avaliações

- Sram Part1Documento36 páginasSram Part1api-285860375Ainda não há avaliações

- Verilog Operators Part-IDocumento5 páginasVerilog Operators Part-IsenthilAinda não há avaliações

- Verification TutorialDocumento14 páginasVerification TutorialAdemar Gregoruti JuniorAinda não há avaliações

- Data Transfer Between Asynchronous Clock DomainsDocumento10 páginasData Transfer Between Asynchronous Clock DomainsShiva ShankarAinda não há avaliações

- System Verilog TrainingDocumento2 páginasSystem Verilog TrainingVlsi GuruAinda não há avaliações

- Product OverviewDocumento9 páginasProduct OverviewUsha KrishnaAinda não há avaliações

- Digital Morse Code Decoder Design Lab 1Documento4 páginasDigital Morse Code Decoder Design Lab 1sharmanator99Ainda não há avaliações

- Basic flip-flops and memory devicesDocumento25 páginasBasic flip-flops and memory devicesNagul MeeraAinda não há avaliações

- EE520 ASIC Design PDFDocumento44 páginasEE520 ASIC Design PDFthiendoan_bkAinda não há avaliações

- Floating Point DSPs by BhaskarDocumento44 páginasFloating Point DSPs by BhaskarSai Anirudh SanagaramAinda não há avaliações

- Cadence Virtuoso Spectre - Virtuoso - MmsimDocumento12 páginasCadence Virtuoso Spectre - Virtuoso - MmsimParker333Ainda não há avaliações

- Io MultiplexingDocumento19 páginasIo Multiplexingsubramanyam62Ainda não há avaliações

- Ex 02Documento14 páginasEx 02elumalaianithaAinda não há avaliações

- Multi Mode Constraints Analysis Using SpyGlassDocumento11 páginasMulti Mode Constraints Analysis Using SpyGlasssunilbrAinda não há avaliações

- Zynq 7020Documento4 páginasZynq 7020NGUYỄN HOÀNG LINHAinda não há avaliações

- IEEE Floating Point Multiplier VerilogDocumento19 páginasIEEE Floating Point Multiplier VerilogSakthi Velan0% (1)

- Using Parameterised ClassesDocumento14 páginasUsing Parameterised ClassespriyajeejoAinda não há avaliações

- Digital VLSI Design Lecture 3: Logic Synthesis: Semester A, 2018-19 Lecturer: Dr. Adam TemanDocumento47 páginasDigital VLSI Design Lecture 3: Logic Synthesis: Semester A, 2018-19 Lecturer: Dr. Adam TemansrajeceAinda não há avaliações

- XCELIUM BASIC Vs ADVANCED PROFILERDocumento9 páginasXCELIUM BASIC Vs ADVANCED PROFILERPriya JeejoAinda não há avaliações

- GDSII For The Rest of Us-27nov2016Documento17 páginasGDSII For The Rest of Us-27nov2016aanbalanAinda não há avaliações

- Low Power Vlsi Design: Assignment-1 G Abhishek Kumar Reddy, M Manoj VarmaDocumento17 páginasLow Power Vlsi Design: Assignment-1 G Abhishek Kumar Reddy, M Manoj VarmamanojAinda não há avaliações

- SystemVerilog Vs Verilog in RTL DesignDocumento4 páginasSystemVerilog Vs Verilog in RTL DesignVijay KumarAinda não há avaliações

- VerilogDocumento34 páginasVerilogromeoalvzAinda não há avaliações

- PrimeTime 2011 Webinar-Advanced OCVDocumento32 páginasPrimeTime 2011 Webinar-Advanced OCVSourabh Aditya SwarnkarAinda não há avaliações

- Building Better IP With RTL Architect NoC IP Physical Exploration by ArterisDocumento30 páginasBuilding Better IP With RTL Architect NoC IP Physical Exploration by Arterisyang huAinda não há avaliações

- VerilogDocumento226 páginasVerilogNadeem AkramAinda não há avaliações

- Digital Design Through Verilog-18 PDFDocumento31 páginasDigital Design Through Verilog-18 PDFAnanth G NAinda não há avaliações

- Interconnect Noise Optimization in Nanometer TechnologiesDocumento145 páginasInterconnect Noise Optimization in Nanometer TechnologiesSmile NagsAinda não há avaliações

- Case Study of Complex Full Chip Low Power Implementation in 16nm NodeDocumento32 páginasCase Study of Complex Full Chip Low Power Implementation in 16nm NodemanojkumarAinda não há avaliações

- Verilog Synthesis Guide for FPGA and ASIC DesignDocumento26 páginasVerilog Synthesis Guide for FPGA and ASIC Designksb9790Ainda não há avaliações

- Resume Arvind ShrivastavaDocumento2 páginasResume Arvind ShrivastavaArvind ShrivastavaAinda não há avaliações

- Real-Time System AssignmentDocumento4 páginasReal-Time System AssignmentTommy Kyen'de BilAinda não há avaliações

- How To Use TRACE32Documento7 páginasHow To Use TRACE32Vasile Morariu100% (1)

- Testability Architecture and Flow for EOCHL and Embedded IPsDocumento24 páginasTestability Architecture and Flow for EOCHL and Embedded IPssenthilkumarAinda não há avaliações

- Timing Design in Digital Systems: Dr. Paul D. FranzonDocumento24 páginasTiming Design in Digital Systems: Dr. Paul D. FranzonMaheshAinda não há avaliações

- Place & Route Tutorial #1: I. SetupDocumento13 páginasPlace & Route Tutorial #1: I. SetupDurgaPrasadAinda não há avaliações

- PDDocumento76 páginasPDKanhaiya MishraAinda não há avaliações

- Vector-Based Peak Current Analysis During Wafer Test of Flip-Chip DesignsDocumento206 páginasVector-Based Peak Current Analysis During Wafer Test of Flip-Chip DesignsLakshman YandapalliAinda não há avaliações

- Techfile Vs TLUPlus File Extraction Difference in ICCDocumento2 páginasTechfile Vs TLUPlus File Extraction Difference in ICCrashmi sAinda não há avaliações

- Timing Paths Static Timing Analysis STA Basic Part 1 VLSI Concepts PDFDocumento10 páginasTiming Paths Static Timing Analysis STA Basic Part 1 VLSI Concepts PDFravishopingAinda não há avaliações

- Cadence Virtuoso Setup GuideDocumento7 páginasCadence Virtuoso Setup Guidecold_faceAinda não há avaliações

- FPGA Applications in SpaceDocumento5 páginasFPGA Applications in SpacePiyush JainAinda não há avaliações

- Application-Specific Integrated Circuit ASIC A Complete GuideNo EverandApplication-Specific Integrated Circuit ASIC A Complete GuideAinda não há avaliações

- A Novel Adaptive Fusion Scheme For Cooperative Spectrum Sensing-Design DetailsDocumento2 páginasA Novel Adaptive Fusion Scheme For Cooperative Spectrum Sensing-Design DetailsverilogcourseteamAinda não há avaliações

- Offline Signature Recognition & Verification Using Neural NetworkDocumento8 páginasOffline Signature Recognition & Verification Using Neural NetworkverilogcourseteamAinda não há avaliações

- Cooperative Spectrum Sensing in Cognitive Radio Networks With Kernel LMS-Design DetailsDocumento1 páginaCooperative Spectrum Sensing in Cognitive Radio Networks With Kernel LMS-Design DetailsverilogcourseteamAinda não há avaliações

- A Multilayer Improved RBM Network Based Image Compression Method in Wireless Sensor NetworksDocumento11 páginasA Multilayer Improved RBM Network Based Image Compression Method in Wireless Sensor NetworksverilogcourseteamAinda não há avaliações

- Vlsi Design Unit 1Documento34 páginasVlsi Design Unit 1verilogcourseteamAinda não há avaliações

- IEEE Paper FormatDocumento3 páginasIEEE Paper FormatSanhith RaoAinda não há avaliações

- IEEE Paper FormatDocumento3 páginasIEEE Paper FormatSanhith RaoAinda não há avaliações

- A Distributed Canny Edge Detector Algorithm and FPGA ImplementationDocumento17 páginasA Distributed Canny Edge Detector Algorithm and FPGA ImplementationverilogcourseteamAinda não há avaliações

- Maths-1 For 12th Std-Book SolutionsDocumento109 páginasMaths-1 For 12th Std-Book Solutionsverilogcourseteam0% (1)

- Unit5 Verilog HDLDocumento70 páginasUnit5 Verilog HDLverilogcourseteam67% (3)

- Vlsi DesignDocumento215 páginasVlsi Designverilogcourseteam100% (9)

- Matlab Project Topics: 1. A System For Human Identification From X-Ray Dental RadiographsDocumento6 páginasMatlab Project Topics: 1. A System For Human Identification From X-Ray Dental RadiographsverilogcourseteamAinda não há avaliações

- An FPGA-Based Architecture For Real Time Image Feature ExtractionDocumento4 páginasAn FPGA-Based Architecture For Real Time Image Feature ExtractionverilogcourseteamAinda não há avaliações

- Vlsi Project Topics: Verilog Course TeamDocumento4 páginasVlsi Project Topics: Verilog Course Teamverilogcourseteam0% (1)

- Matlab Project TopicsDocumento6 páginasMatlab Project TopicsverilogcourseteamAinda não há avaliações

- Math 101Documento3 páginasMath 101Nitish ShahAinda não há avaliações

- Popular Mechanics 2010-06Documento171 páginasPopular Mechanics 2010-06BookshebooksAinda não há avaliações

- Mock PPT 2023 TietDocumento22 páginasMock PPT 2023 Tiettsai42zigAinda não há avaliações

- CHB1 Assignmen5Documento2 páginasCHB1 Assignmen5anhspidermenAinda não há avaliações

- Unit 3.1 - Hydrostatic ForcesDocumento29 páginasUnit 3.1 - Hydrostatic ForcesIshmael MvunyiswaAinda não há avaliações

- Workflowy - 2. Using Tags For NavigationDocumento10 páginasWorkflowy - 2. Using Tags For NavigationSteveLangAinda não há avaliações

- 9.tools and Equipment 1Documento13 páginas9.tools and Equipment 1NKH Mega GasAinda não há avaliações

- University Reserch Worksheet PDFDocumento7 páginasUniversity Reserch Worksheet PDFapi-410567922Ainda não há avaliações

- BA 302 Lesson 3Documento26 páginasBA 302 Lesson 3ピザンメルビンAinda não há avaliações

- Abiding LonelinessDocumento9 páginasAbiding Lonelinessgrupodelectura04Ainda não há avaliações

- EMI: English As A Medium of Instruction: A New Methodology To Teach English As A Foreign LanguageDocumento18 páginasEMI: English As A Medium of Instruction: A New Methodology To Teach English As A Foreign Languagepaola suarezAinda não há avaliações

- COP Oil: For Epiroc Components We Combine Technology and Environmental SustainabilityDocumento4 páginasCOP Oil: For Epiroc Components We Combine Technology and Environmental SustainabilityDavid CarrilloAinda não há avaliações

- 2VAA001695 en S Control NTCS04 Controller Station Termination UnitDocumento43 páginas2VAA001695 en S Control NTCS04 Controller Station Termination UnitanbarasanAinda não há avaliações

- Lux MeterDocumento4 páginasLux MeterNmg KumarAinda não há avaliações

- Analysis of Piled Raft of Shanghai Tower in Shanghai by The Program ELPLADocumento18 páginasAnalysis of Piled Raft of Shanghai Tower in Shanghai by The Program ELPLAAmey DeshmukhAinda não há avaliações

- Lower Congo Basin 3D SurveyDocumento2 páginasLower Congo Basin 3D SurveyTalis TemAinda não há avaliações

- wt-and-fds-practical-slipsDocumento32 páginaswt-and-fds-practical-slipsRohidas SapkalAinda não há avaliações

- Brake System PDFDocumento9 páginasBrake System PDFdiego diaz100% (1)

- REFLEKSI KASUS PLASENTADocumento48 páginasREFLEKSI KASUS PLASENTAImelda AritonangAinda não há avaliações

- Sinavy Pem Fuel CellDocumento12 páginasSinavy Pem Fuel CellArielDanieli100% (1)

- Packing, Transportation and Marketing of Ornamental FishesDocumento16 páginasPacking, Transportation and Marketing of Ornamental Fishesraj kiranAinda não há avaliações

- Tomas Del Rosario College: Department: EDUCATIONDocumento12 páginasTomas Del Rosario College: Department: EDUCATIONveehneeAinda não há avaliações

- 713 Catalog PagesDocumento2 páginas713 Catalog PagesJosé AcostaAinda não há avaliações

- ASIA INTERNATIONAL FURNITURE MATERIALS CONTRACTDocumento2 páginasASIA INTERNATIONAL FURNITURE MATERIALS CONTRACTSALOME URUCHI AGUILARAinda não há avaliações

- CA Module Franklin Gari RDocumento28 páginasCA Module Franklin Gari RFranklin GariAinda não há avaliações

- Saes H 201Documento9 páginasSaes H 201heartbreakkid132Ainda não há avaliações

- Technology and Livelihood Education: Agri - Fishery Arts (Agricultural Crops Production) Marketing Agricultural ProductsDocumento14 páginasTechnology and Livelihood Education: Agri - Fishery Arts (Agricultural Crops Production) Marketing Agricultural Productslana del rey100% (1)

- Movement Joints (NHBC)Documento5 páginasMovement Joints (NHBC)hemendraengAinda não há avaliações

- 1993 - Kelvin-Helmholtz Stability Criteria For Stratfied Flow - Viscous Versus Non-Viscous (Inviscid) Approaches PDFDocumento11 páginas1993 - Kelvin-Helmholtz Stability Criteria For Stratfied Flow - Viscous Versus Non-Viscous (Inviscid) Approaches PDFBonnie JamesAinda não há avaliações

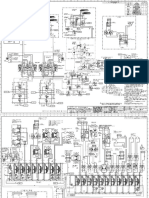

- Hyd Schematic 2658487205 - 005Documento3 páginasHyd Schematic 2658487205 - 005Angelo Solorzano100% (2)