Escolar Documentos

Profissional Documentos

Cultura Documentos

PD1 Grupo 3 YeinerArias JeffersonGonzalez Calificados

Enviado por

Jeferson Gonzalez0 notas0% acharam este documento útil (0 voto)

15 visualizações4 páginasDireitos autorais

© © All Rights Reserved

Formatos disponíveis

PDF, TXT ou leia online no Scribd

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato PDF, TXT ou leia online no Scribd

0 notas0% acharam este documento útil (0 voto)

15 visualizações4 páginasPD1 Grupo 3 YeinerArias JeffersonGonzalez Calificados

Enviado por

Jeferson GonzalezDireitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato PDF, TXT ou leia online no Scribd

Você está na página 1de 4

ITCR. Y. Arias, J. Gonzlez.

Reporte de primer proyecto de diseo en VHDL 1

Abstract Este artculo contiene el reporte del primer proyecto

de diseo en VHDL para el curso de Lenguajes de Descripcin de

Hardware. La primera seccin describe una pequea

introduccin al proyecto, as como un enfoque de la solucin del

mismo. En la segunda seccin se incluyen los aspectos ms

importantes de la solucin, separndola en cada uno de sus

enunciados. Igualmente se incluyen los cdigos y diagramas, a

nivel de RTL, de los mdulos principales. La tercera seccin de

este artculo exhibe los resultados y simulaciones de los mdulos

ms importantes. Por ltimo, la seccin de conclusiones presenta

un resumen final de los principales aspectos del proyecto, as

como informacin adicional que se obtuvo a partir de los

resultados del mismo.

Palabras clave VHDL, multiplexor, BCD, sumador

complete, RTL.

I. INTRODUCCIN

STE documento presenta el cdigo, resultados y las

simulaciones realizadas para llevar a cabo el Proyecto de

Diseo I del curso Lenguajes de Descripcin de Hardware. El

proyecto se divide en 5 enunciados, ms uno opcional, en los

que desarrollan mdulos que son necesarios para el diseo del

enunciado final. El tema central de dicho proyecto es el

manejo y la conversin de nmeros decimales codificados en

binario (Binary Coded Decimal), esto se logr mediante la

creacin de distintos mdulos para tareas especficas

(decodificaciones, multiplexaciones, sumas, entre otras)

donde a medida que se implementaban nuevas funciones fue

necesario instanciar las diseadas anteriormente, dando como

resultado un sistema modular, que finalmente realizaba la

funcin de sumar dos nmeros en BCD de dos dgitos.

En las secciones posteriores se presenta, con un mayor

nivel de detalle, el diseo y los resultados obtenidos de las

diferentes etapas del proyecto.

II. DISEO DE LA SOLUCIN

En general, el diseo de la solucin se bas enteramente en

las especificaciones de cada seccin, haciendo uso de

herramientas de diseo, por ejemplo simplificacin de

funciones por mapas de Karnaugh para el caso de las tablas de

verdad de los diferentes decodificadores y comparadores.

Las siguientes subsecciones incluyen el desarrollo de la

solucin para cada una de las etapas del proyecto.

A. Parte I

En la primera parte del proyecto, se debi disear un

sistema que permitiera visualizar cuatro nmeros entre 0 a 9

en un display de 7 segmentos. Para lograr esto, se dise un

convertidor de BCD a 7 segmentos, segn la tabla de verdad

sugerida en el enunciado. El diagrama a nivel de RTL del

convertidor diseado se muestra en la Figura 1.

Posteriormente se realizaron cuatro instancias de este

mismo mdulo para ser conectadas a cada una de las entradas

del sistema.

Fig 1. Diagrama a nivel de RTL del convertidor de BCD a 7 segmentos.

B. Parte II

Para dar solucin a la parte 2 fue necesario implementar un

mdulo capaz de convertir un nmero de binario de cuatro bits

a un nmero decimal de dos dgitos codificado en binario. Una

vez finalizada la conversin el resultado es mostrado en dos

displays siete segmentos con ayuda de un decodificador siete

segmentos.

La solucin consisti en un circuito donde se comparaba el

nmero binario, cuando este fuese mayor a nueve el sistema

actuaria para cambiar los bits siguientes e iniciar la cuenta de

Reporte de primer proyecto de diseo con

VHDL

Yeiner Arias, Instituto Tecnolgico de Costa Rica

yeinerarias@gmail.com

Jeferson Gonzlez, Instituto Tecnolgico de Costa Rica

jefg89@gmail.com

E

Esta presentacin de la estructura del documento es ms

adecuada hacia el final de la introduccin del documento,

no en el abstract

se podra omitir esta frase

se podra cambiar por generado, pues esto lo genera la

herramienta a partir de la descripcin que realizaron

Formato 20/20

Estructura 20/20

Figuras 15/20

Ortografa 18/20

Redaccin 18/20

______________

Nota 91/100

Notas

PD1> 108.6

TD1> 100

ITCR. Y. Arias, J. Gonzlez. Reporte de primer proyecto de diseo en VHDL 2

las unidas desde cero y adems cambiar las decenas a uno. Las

partes ms relevantes del cdigo diseado se muestran a

continuacin e la figura 2.

Fig 2. Cdigo de VHDL implementado en la parte 2.

C. Parte III

En la parte 3 se realizaron dos diseos, el primero un

sumador completo (Full Adder) el cual suma dos bits "a" y "b"

adems de un acareo de entrada "cin" y tiene como salida el

resultado de la suma "s" y una acareo de salida "cout". El RTL

del sumador de muestra en la figura 3.

Fig 3. Diagrama RTL de mdulo sumador completo

El segundo diseo consisti en sumar dos numero binario

de cuatro bits cada uno, para esto se utiliz un arreglo de

sumadores completos donde, el acareo de salida de un

sumador se conecta al acareo de entrada del siguiente as hasta

unir cuatro de estos. El resultado fue un sumador completo de

cuatro entradas como acareo de entrada y de salida y se

muestra en la Figura 4.

Fig 4. Diagrama RTL del mdulo principal de la parte 4.

D. Parte IV

La parte 4 del proyecto corresponde a la suma de dos

dgitos en BCD, tomando en cuenta un acarreo de entrada, de

tal forma que el mximo nmero que pudiera obtenerse

mediante esta suma correspondiera a 9 + 9 +1 = 19. Para la

solucin de este circuito, se utiliz una instancia al sumador

completo de la parte 3, as como un convertidor de binario a

BCD, muy similar al de la parte 2, que fue modificado para

convertir nmeros binarios entre 0 y 19 (nmero mximo

representable en esta suma). Adems se dise un mdulo

para la deteccin de errores, en caso de que las entradas no se

encontraran codificados en BCD. Este circuito es,

bsicamente, dos instancias del comparador diseado en la

parte 2, unidos por medio de una compuerta OR, para generar

una seal de error en caso de que el dgito A o el dgito B

fueran mayores a 9.

El diagrama RTL correspondiente a esta parte del proyecto

se muestra en la figura 5.

Fig 5. Diagrama RTL del mdulo de la parte 4.

E. Parte V

La parte 5 corresponde al diseo de un sumador de dos

nmeros de dos dgitos BCD para uno, cuya salida

corresponde a un nmero de 3 dgitos que debe ser visualizado

en tres displays de 7 segmentos. Para llevar a cabo este

circuito, se instanci dos veces el mdulo desarrollado en la

parte 4; una instancia para las unidades y otra para las

decenas. El acarreo de salida correspondiente a las unidades

usualmente no se presenta cdigo en los papers. El objetivo es mostrar como se resolvi el problema y no como se desarroll a nivel tcnico

ITCR. Y. Arias, J. Gonzlez. Reporte de primer proyecto de diseo en VHDL 3

ingresa al mdulo de las decenas por medio del acarreo de

entrada. Adems se uni, por medio de una OR, las seales de

error para ambos dgitos. El diagrama de este sistema se

muestra en la Figura 6.

Fig 6. Diagrama RTL del mdulo de la parte 5

.

F. Parte VI : Opcional

Como parte opcional, se propuso realizar el mismo diseo

de la parte 5 pero utilizando un seudo-cdigo, en vez de

implementarlo mediante mdulos de hardware. El cdigo

generado finalmente en VHDL para realizar esta funcin, as

como su diagrama a nivel de RTL se muestra en las figuras 7 y

8 respectivamente.

Fig 7. Cdigo implementado para realizar la suma en la parte 6.

Fig 8. Diagrama RTL del mdulo de la parte 6

III. RESULTADOS

En esta seccin se trataran los resultados obtenidos

mediante la simulacin de los diseos. Dado que en la parte 5

del proyecto se utilizan todas las dems secciones mediante

instancias, los datos presentados corresponden nicamente a

dicho punto. Adems se incluye la simulacin de la parte

opcional y se detallan aspectos comparativos entre ambas.

La simulacin del mdulo principal, correspondiente a la

parte 4 (suma de dos nmeros de dos dgitos BCD cada uno)

se muestra en la figura 9. Como se puede apreciar, el circuito

fue probado para diferentes valores de entradas. Estas entradas

se muestran en representacin Hexadecimal; en los casos en

que algn digito de la entrada es mayor a 9, se puede notar

como la seal de error se dispara. Para el resto de los casos, al

no tener error, se puede observar como la salida corresponde

(en codificacin de 7 segmentos) con el resultado de la suman

de ambas entradas. En uno de los casos especficos, mostrados

en el tiempo 13970000 ps de la simulacin, se presenta el

mayor nmero representable mediante esta suma que

corresponde a 99 + 99 + 1= 199, como se puede observar,

este es el nmero obtenido mediante los 3 displays de 7

segmentos (Hex0, Hex1, Hex2).

Fig 9. Simulacin de la parte 5. Sumador de dos nmeros de dos dgitos en

BCD.

En el diseo de la seccin opcional a diferencia de la

seccin 5 se utilizaron mdulos de suma y resta creados

automticamente por Quartus durante la sntesis del cdigo, lo

cual reduce y simplifica considerablemente el tamao y la

complejidad del mismo. En la Figura 10 de se muestra una

simulacin del mdulo.

Fig 10. Simulacin de la parte opcional. Sumador de dos nmeros de dos

dgitos en BCD mediante cdigo (software like).

Como se puede observar al comparar el resultado de la

Figura 9 con el de la Figura 10, se obtiene el mismo

comportamiento. Lo que quiere decir que aunque las

implementaciones son distintas su funcin es la misma.

estas imgenes no se aprecian bien, seria mejor colocarlas a todo el

ancho de la pgina

Las imgenes deben ser siempre legibles

ITCR. Y. Arias, J. Gonzlez. Reporte de primer proyecto de diseo en VHDL 4

IV. CONCLUSIONES

El diseo modular, mediante la instanciacin, reduce

significativamente el tiempo de diseo, al mismo tiempo que

facilita la comprensin del mismo.

La visualizacin del circuito por medio del RTL facilita la

interpretacin del funcionamiento e implementacin del

diseo.

Las simulaciones permiten encontrar errores de

funcionamiento y sirve como gua para la correccin en el

cdigo.

La utilizacin de mdulos prediseados y diseo de

mdulos por comportamiento reducen el tamao del cdigo y

simplifica la implementacin. Sin embargo, no da claridad

sobre la implementacin fsica de los circuitos.

REFERENCIAS

[1] Altera. Basics of Programable Logic.

http://www.altera.com/customertraining/webex/PLDBasics/presentation.

html

[2] Altera. Using the Quartus Software.

http://www.altera.com/customertraining/webex/QII_Intro/player.html

reutilizacin de bloques bsicos

tambin

Você também pode gostar

- SP Web TEW-651BR (1.04)Documento15 páginasSP Web TEW-651BR (1.04)Johnny Di SantoAinda não há avaliações

- Carta Al EstudianteDocumento3 páginasCarta Al EstudianteJeferson GonzalezAinda não há avaliações

- Intrigas - Jeferson GonzálezDocumento12 páginasIntrigas - Jeferson GonzálezJeferson GonzalezAinda não há avaliações

- Jef MadrugadaDocumento1 páginaJef MadrugadaJeferson GonzalezAinda não há avaliações

- Instrucciones Paper IEEEDocumento3 páginasInstrucciones Paper IEEENBELTRANCUELLARAinda não há avaliações

- Movileschinos.comDocumento1 páginaMovileschinos.comJeferson GonzalezAinda não há avaliações

- Tutorial OpencvDocumento61 páginasTutorial OpencvLed-on100% (1)

- Proceso de AdmisionDocumento8 páginasProceso de AdmisionJeferson GonzalezAinda não há avaliações

- Memoria Final PFCDocumento100 páginasMemoria Final PFCRuth Mora HernandezAinda não há avaliações

- Temporizadores y ContadoresDocumento78 páginasTemporizadores y ContadoresEsteban GomezAinda não há avaliações

- ACTIVIDAD #3 G.C.R.P 2 Año A y BDocumento1 páginaACTIVIDAD #3 G.C.R.P 2 Año A y BNoemi ZambranoAinda não há avaliações

- Emprendimiento en CordobaDocumento4 páginasEmprendimiento en CordobaNestor Hernandez VidezAinda não há avaliações

- Protecciones Sobre CorrienteDocumento25 páginasProtecciones Sobre CorrienteJuan Pablo Reyes CalagazAinda não há avaliações

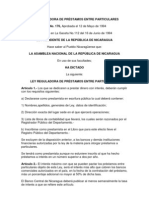

- LEY REGULADORA DE PRÉSTAMOS ENTRE PARTICULARES NicaraguaDocumento5 páginasLEY REGULADORA DE PRÉSTAMOS ENTRE PARTICULARES Nicaragualuis_camiloAinda não há avaliações

- Angela Mileth Perez Curvelo - 6.MUEBLES DE OFICINA NECESARIOSDocumento13 páginasAngela Mileth Perez Curvelo - 6.MUEBLES DE OFICINA NECESARIOSMileidys CurveloAinda não há avaliações

- Qué Es Una Aplicación WebDocumento9 páginasQué Es Una Aplicación WeblinoquispeAinda não há avaliações

- Tema 3Documento80 páginasTema 3Ruth Bort GomezAinda não há avaliações

- Unidad II - La Registración Contable - Material InformativoDocumento25 páginasUnidad II - La Registración Contable - Material InformativoCarol rojasAinda não há avaliações

- Capitulo 3-Sistemas de InformacionDocumento6 páginasCapitulo 3-Sistemas de InformacionWendy RodriguezAinda não há avaliações

- FGPR - 110 - 06 - Red Del ProyectoDocumento2 páginasFGPR - 110 - 06 - Red Del ProyectoNestor JuarezAinda não há avaliações

- Planta de TratamientoDocumento59 páginasPlanta de TratamientoJerry Florentino Cusi AranaAinda não há avaliações

- Comunicado de Solicitud de Materiales 2020Documento2 páginasComunicado de Solicitud de Materiales 2020Emeliza ARIAS ROMEROAinda não há avaliações

- Icia-Pmtd-Picb1 2021Documento62 páginasIcia-Pmtd-Picb1 2021Francisco Tapia0% (1)

- Mapa Conceptual Unidad 2 AlejaDocumento1 páginaMapa Conceptual Unidad 2 AlejaYamila peñaAinda não há avaliações

- TDR CamionetaDocumento4 páginasTDR CamionetaJoelMejiaAinda não há avaliações

- Acto Modelo Notificacion de AudienciaDocumento1 páginaActo Modelo Notificacion de AudienciaPedro Cruz100% (5)

- Administración TributariaDocumento5 páginasAdministración Tributariacarlos GonzalezAinda não há avaliações

- Elaboracion de Biol Mejorado Apartir de La Adicion de Visceras de PescadoDocumento8 páginasElaboracion de Biol Mejorado Apartir de La Adicion de Visceras de Pescadovibehuan100% (1)

- Vias de Administracion XDocumento11 páginasVias de Administracion XCristian Edsel Hernández ReyesAinda não há avaliações

- Examen - (AAB02) Cuestionario 3 - Resuelva La Evaluación Parcial 3Documento6 páginasExamen - (AAB02) Cuestionario 3 - Resuelva La Evaluación Parcial 3Gia Mora100% (1)

- Hoja de Excel para El Calculo de Ladrillos y MorterosDocumento9 páginasHoja de Excel para El Calculo de Ladrillos y MorterosEdwin Sanchez100% (1)

- El BasquetbolDocumento8 páginasEl BasquetbolMoises FerjosAinda não há avaliações

- Fraccionamiento de Los Liquidos Del Gas Natural JhazDocumento12 páginasFraccionamiento de Los Liquidos Del Gas Natural JhazGeorge Giron0% (1)

- 2023 12 22T16 10 38 423 - DecretoDocumento2 páginas2023 12 22T16 10 38 423 - DecretoLicitaciones 01 IMCAinda não há avaliações

- M2 U1 A2 BDIA InformeDocumento6 páginasM2 U1 A2 BDIA InformeBlanca IbarraAinda não há avaliações

- Cuando Caigan Las Hojas Canción para Piano de Luis A CalvoDocumento2 páginasCuando Caigan Las Hojas Canción para Piano de Luis A CalvoHonorato Castrillón OchoaAinda não há avaliações

- Caja Huancayo 2020Documento5 páginasCaja Huancayo 2020Jean Pierre Garay SotoAinda não há avaliações

- Idoc - Tips Calculos Vaso de Expansion y Separador Aguja HidraDocumento40 páginasIdoc - Tips Calculos Vaso de Expansion y Separador Aguja HidraAlin Cristian BaraAinda não há avaliações

- Etapas de Construcción de Una Obra VialDocumento9 páginasEtapas de Construcción de Una Obra VialJhon JC100% (1)