Escolar Documentos

Profissional Documentos

Cultura Documentos

MI As Filter

Enviado por

Madhumitha RajasekaranTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

MI As Filter

Enviado por

Madhumitha RajasekaranDireitos autorais:

Formatos disponíveis

IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 60, NO.

11, NOVEMBER 2013 5019

A Model-Based Controller for the Cascade H-Bridge

Multilevel Converter Used as a Shunt Active Filter

Andrs A. Valdez-Fernndez, Member, IEEE, Pnlo R. Martnez-Rodrguez, Member, IEEE,

Gerardo Escobar, Senior Member, IEEE, Cesar A. Limones-Pozos, and Jos M. Sosa, Member, IEEE

AbstractThis paper presents the modeling and control pro-

cesses of the single-phase cascade H-bridge multilevel converter

used as a shunt active lter. Based on the obtained model, a

controller is proposed to compensate for harmonic distortion and

reactive power caused by a nonlinear load. These issues are solved

by guaranteeing tracking of the line current toward an appro-

priately dened current reference. In the proposed approach, the

current reference has been selected to be a signal proportional to

either the line voltage or to its fundamental component; however,

the proposed method can also be extended to other reference

denitions. The proposed controller also includes voltage loops

to guarantee regulation and balance of the involved capacitor

voltages toward constant references. Experimental results on a

2-kVA prototype are presented to assess the performance of the

proposed controller.

Index TermsActive lters, adaptive control, multilevel sys-

tems, reactive power control.

I. INTRODUCTION

I

N THE recent years, multilevel converters have become

popular in medium- [1] and high-power applications [2],

[3]. The advantages that multilevel converters offer are well

known from the early 1980s [4] to nowadays [5]. They have

been able to meet the increasing demand of power ratings and

power quality associated with reduced harmonic distortion and

lower electromagnetic interference (EMI) [6]. The idea behind

these systems is that, by synthesizing the ac output voltage from

several levels of voltages, staircase waveforms are produced

approaching the sinusoidal waveform with reduced harmonic

distortion. Moreover, they have the remarkable capability of

increasing the output voltage magnitude as they are composed

of the cascade connection of several semiconductor devices

operating at a reduced switching frequency and under lower

voltage stresses. This may lead to a considerable reduction of

the system losses, which represents an increase in efciency.

Manuscript received February 9, 2012; revised May 16, 2012 and July 13,

2012; accepted July 17, 2012. Date of publication September 12, 2012; date of

current version June 6, 2013.

A. A. Valdez-Fernndez is with the School of Sciences, Autonomous Uni-

versity of San Luis Potosi (UASLP), San Luis Potosi 78290, Mexico (e-mail:

andres.valdez@ieee.org).

P. R. Martnez-Rodrguez, C. A. Limones-Pozos, and J. M. Sosa are with

the Laboratory of Electrical and Power Electronics, Technological Institute

of Superior Studies of Irapuato (ITESI), Irapuato 36821, Mexico (e-mail:

pamartinez@itesi.edu.mx; cesar.limones@itesi.edu.mx; jmsosa@itesi.

edu.mx).

G. Escobar is with the School of Engineering, Autonomous University of

Yucatan (UADY), Merida 97310, Mexico (e-mail: gescobar@ieee.org).

Color versions of one or more of the gures in this paper are available online

at http://ieeexplore.ieee.org.

Digital Object Identier 10.1109/TIE.2012.2218558

Among the several multilevel converter topologies [2], the

cascade H-bridge (CHB) multilevel converter [7] has received

special attention due mainly to its modularity, reliability, and

feasibility. A CHB converter is composed of a cascade connec-

tion of H-bridge (or full-bridge) single-phase converters, whose

ac outputs are combined to reproduce a desired output voltage

reference. However, all these H-bridges have separated dc

buses, where separate dc supplies or separate capacitors can be

connected. In contrast to other topologies, CHB converters have

achieved larger output voltage levels (up to 17) in commercial

applications [5], and they have shown a better efciency and

dynamic performance [8], all these with a reduced number of

switching devices [2], [9].

A growing interest has been observed in the recent past in the

use of this topology in aircraft applications. This is derived of

the more electric aircraft initiative [10], [11], where high power

density is the main objective. Notice that the CHB allows the

reduction of voltage stress in semiconductors, which enables

the use of devices able to switch at higher frequencies. This

fact has, as a result, the considerable size reduction of the lter

involved, in particular the inductors, in addition to a cleaner

generation of signals.

To correctly exploit all the earlier discussed advantages of

the CHB in a given application, both an adequate modulation

algorithm [1], [12], [13] and an adequate control strategy must

be applied [14][24]. It is important to notice that the success of

a controller design depends, in many cases, on the good knowl-

edge of a mathematical model that can accurately describe the

system dynamics [14]. However, as the number of switching

devices increases in multilevel converters, the modeling and

control design processes become much more involved [14],

[15]. Moreover, in the case that capacitors are used in the

dc buses, the control of such a system becomes much more

challenging [16]. In this case, the controller must include an

additional balancing scheme to guarantee that each dc capacitor

maintains a desired constant level [2], [17].

Different controllers for CHB converters have been re-

ported in the power electronics literature [14][24]. In [18],

a proportionalintegral (PI)-based solution is proposed. A re-

view of different PI-based control solutions is presented in

[15], where the independent control of the H-bridges con-

nected in cascade has been highlighted. In [19], a control

algorithm based on the phasephase-shifted unipolar sinusoidal

pulsewidth modulation is presented. A robust control strategy

using an auto-disturbance rejection scheme has been presented

in [20]. In [21][23], the authors have successfully applied

the passivity-based control (PBC) design approach [25] to

0278-0046/$31.00 2012 IEEE

5020 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 60, NO. 11, NOVEMBER 2013

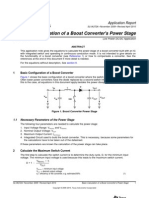

Fig. 1. Single-phase CHB-5L converter as a shunt active lter.

single-phase CHB multilevel converters. PBC is a nonlinear

design technique, which exploits the dynamical structure of

the system. Roughly speaking, the PBC technique considers

the system dynamics as composed by the sum of energy

transformation subsystems, where the controller is designed to

manipulate the energy exchanges. For this, the energy of the

closed-loop system is reshaped, and additional damping is in-

cluded to guarantee convergence toward the desired equilibrium

point.

This paper presents the modeling and control design pro-

cesses of the single-phase

1

CHB multilevel converter used as

a shunt active lter. In fact, the proposed controller can also

be used in a rectier application without any further modi-

cation. The active lter application has been selected here as

it is more challenging than the rectier application. Based on

the obtained model, a controller is proposed to compensate

harmonic distortion and reactive power caused by a nonlinear

load. The proposed controller guarantees tracking of the line

current toward a given current reference. In this case, a current

reference proportional to the line voltage has been selected;

however, the controller can be easily modied to consider other

current references. This part of the controller design follows

the ideas of the PBC approach [25]. In addition, the proposed

controller includes voltage loops to guarantee regulation and

balance of all capacitor voltages on the dc buses. Crucial for the

developments of this work is the representation of the proposed

model in terms of the sum and the difference of the squares

of the capacitor voltages. This allows to decouple current

tracking and voltage regulation issues from the balancing issue,

which facilitates the control design. The ve-level topology

is studied here as an example to facilitate the presentation;

however, the proposed control scheme can be easily scaled to

consider topologies with more levels. Experimental results in a

2-kVA prototype are presented to assess the performance of the

proposed controller strategy.

II. SYSTEM DESCRIPTION

In this paper, an active lter using the single-phase ve-level

CHB (CHB-5L) converter shown in Fig. 1 is considered. In

1

The extension to the three-phase case is more involved, and it is left for a

future research.

this system, a single-phase ac power supply represented by v

SG

feeds a nonlinear distorting load composed by a noncontrolled

diode rectier with a capacitive lter C

0

and a resistive load

R

0

. The power supply v

SG

has an associated impedance, which

is represented by the inductor L

G

and the resistor r

G

. The

CHB-5L is connected in parallel to the load in the point of

common coupling (PCC).

The model of the system in Fig. 1 can be obtained by sim-

ple application of Kirchhoffs laws. This yields the following

model that describes the system dynamics:

L

G

di

S

dt

= r

G

i

S

+ v

SG

v

S

(1)

L

di

dt

= u

1

v

C1

u

2

v

C2

+ v

S

(2)

C

dv

C1

dt

=u

1

i

v

C1

R

(3)

C

dv

C2

dt

=u

2

i

v

C2

R

i

S

=i + i

0

(4)

where v

S

is the voltage in the PCC, also referred to as the grid

voltage, i

S

is the grid current, i is the current injected by the

active lter, i

0

is the distorting load current, v

C1

and v

C2

are

the capacitor voltages on the dc buses, and parameters L and

C are the input inductance and the dc capacitance of the active

lter, respectively. Notice that, without loss of generality, the

same capacitance C has been assumed for both H-bridges; the

losses have been modeled as simple resistors R in parallel to

the dc capacitors, and u

1

and u

2

denote the switch position

functions for each H-bridge. In fact, u

1

and u

2

represent the

actual control inputs taking values in the discrete set {1, 0, 1}.

The operation of the converter is as follows. For the upper

H-bridge converter, when u

1

= 1, transistors Q

1

and Q

4

are

turned on, while transistors Q

2

and Q

3

are turned off. The

opposite happens for u

1

= 1. Moreover, for u

1

= 0, Q

1

and

Q

2

(or Q

3

and Q

4

) are simultaneously on. The lower H-bridge

operates in a similar way.

For control design purposes, the averaged model is consid-

ered instead of the exact switching model. For this, the switch

positions u

1

and u

2

will represent, from now on, the duty ratios,

i.e., continuous signals taking values in the range [1, 1].

This is supported by the fact that, in a real implementation,

a relatively high effective switching frequency is considered

together with an appropriate modulation technique, such as

multicarrier phase shifted or level shifted.

Moreover, to facilitate the controller design and to reduce the

model expressions, it has been found very convenient to trans-

form the aforementioned model (2)(4) by using the following

denitions:

x

1

=i

S

(5)

x

2

=

v

2

C1

+ v

2

C2

2

(6)

x

3

=

v

2

C1

v

2

C2

2

(7)

=u

1

v

C1

+ u

2

v

C2

(8)

=u

1

v

C1

u

2

v

C2

(9)

VALDEZ-FERNNDEZ et al.: CONTROLLER FOR CHB MULTILEVEL CONVERTER USED AS SHUNT ACTIVE FILTER 5021

which yield the following transformed model

(L + L

G

) x

1

= r

G

x

1

1

+ v

SG

+ L

di

0

dt

(10)

C x

2

=

1

(x

1

i

0

)

2

R

x

2

(11)

C x

3

=

2

(x

1

i

0

)

2

R

x

3

. (12)

Notice that, the model (10)(12) is expressed in terms of the

grid current i

S

instead of the injected current i. This allows a

more natural and effective compensation of the grid current, in

the sense that the reference for this current is easier to establish,

and with the possibility of reducing the number of current

sensors. In fact, this current reference could be now proposed

as a simple sinusoidal signal, or a signal proportional to the grid

voltage, which is much easier to track than a distorted reference

as is usually done in most current controllers. Notice that x

2

and x

3

represent the sum and the difference, respectively, of

the squares of the capacitor voltages, while

1

and

2

represent

the sum and the difference of the injected voltages, respectively.

These latter two signals represent the actual control inputs in the

transformed system (10)(12). Notice that, from (8) and (9), the

original control signals u

1

and u

2

can be obtained according to

u

1

=

1

+

2

2v

C1

u

2

=

1

2

2v

C2

. (13)

A. Main Assumptions

A1. [Decoupling assumption] Inductor current dynamics is

considered faster than capacitor voltage dynamics. Thus,

based on time-scale separation, the control design can be

split into two parts, namely, a fast inner (tracking) current

loop and a slow outer voltage loop.

A2. The fundamental frequency

0

= 2f

0

is considered a

known constant.

A3. The load current i

0

and grid voltage v

S

are periodic

signals that contain higher order harmonics of the fun-

damental frequency

0

= 2f

0

. In this application, only

odd harmonics are considered, i.e., harmonics in the set

H = {1, 3, 5, 7, 11, . . .}. Notice that v

S

includes the effect

of the voltage drop in the line impedance, and thus, it has

the same harmonic contents as current i

S

.

A4. System parameters L, C, and R are considered unknown

positive constants.

A5. The only measured signals are the capacitor voltages v

C1

and v

C2

, the PCC voltage v

S

, and the grid current i

S

.

Notice that the power supply voltage v

SG

is not available.

B. Control Objectives

The objectives to be solved with the proposed controller

scheme are the following.

1) A current tracking loop has to be designed to force the

grid current i

S

to follow a given current reference signal

represented by i

S

. This control objective can be expressed

in mathematical form as follows:

x

1

i

S

as t (14)

where the current reference is dened as

i

S

=

P

ref

v

2

S,RMS

v

S

(15)

with P

ref

representing the active power reference. Hence,

P

ref

/v

2

S,RMS

is a scalar representing the apparent conduc-

tance observed by the source, which is due to the parallel

connection of the load and the active lter.

2

Remark II.1: Notice that the current reference i

S

, as dened

earlier, would be as distorted as the grid voltage v

S

. This is

a necessary condition to force the parallel connection of the

load and active lter to behave like a single resistor. As a

consequence, the grid current i

S

will inject harmonics to the

grid. This is a situation that might not be acceptable in cases

where the grid voltage is highly distorted. A simple solution for

this issue consists in modifying the current reference denition

as follows:

i

S

=

P

ref

v

2

S,RMS

v

S,1

(16)

where v

S,1

represents the fundamental component of the grid

voltage v

S

. Notice that, based on this denition, the current

reference i

S

represents now a pure sinusoidal signal in phase

with v

S,1

. The fundamental component v

S,1

can be obtained,

for instance, by means of an additional phase-locked loop

scheme or by using the following bandpass lter (BPF):

v

S,1

=

0

S,1

+

f

(v

S

v

S,1

) (17)

S,1

=

0

v

S,1

(18)

where

f

is a positive design gain that xes the speed of

response and

S,1

represents a signal of the same characteristics

as v

S,1

, except for a phase shift of 90

ahead. This signal is also

referred to as the square-phase companion signal. The transfer

function of (17) and (18) from v

S

to v

S,1

is given by

v

S,1

v

S

=

f

s

s

2

+

f

s +

2

0

(19)

which has a peak of resonance at the fundamental frequency

0

with unitary gain and zero phase shift.

Remark II.2: A more complete denition for the current

reference including both active and reactive current injection

is given by

i

S

=

P

ref

v

2

S,RMS

v

S,1

+

Q

ref

v

2

S,RMS

S,1

(20)

where reference signal Q

ref

represents a component of reactive

power that could be allowed to circulate in the grid and

S,1

is

the square-phase companion signal that can be obtained using

the aforementioned BPF (17) and (18). However, it is common

in practice to select Q

ref

= 0 to guarantee a power factor close

to unity.

2

Notice that working toward this objective is equivalent to seeking for an

operation with power factor close to unity.

5022 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 60, NO. 11, NOVEMBER 2013

2) A voltage regulation loop has to be designed to regulate, in

average,

3

the sum of the squares of the capacitor voltages

toward a desired constant reference V

2

d

, i.e.,

x

2

V

2

d

as t (21)

where V

d

is the desired reference for each capacitor volt-

age. This guarantees that enough energy has been stored in

both capacitors for the correct fulllment of the previous

objective. Out of this control loop, an expression for the

scalar P

ref

is obtained, which is required to construct the

reference i

S

earlier dened.

3) A voltage balance loop has to be designed to reduce, in

average, the difference of the squares of the capacitor

voltages to zero, i.e.,

x

3

0 as t . (22)

Remark II.3: Notice that the simultaneous fulllment of (21)

and (22) guarantees the regulation of both capacitor voltages

toward the constant reference V

d

, i.e., v

C1

V

d

and v

C2

V

d

. This is supported by the fact that the capacitor voltages are

limited, by physical construction, to take only positive values.

III. CONTROLLER DESIGN

Based on A1, the design of the controller can be split into

two main parts, namely, an inner (current tracking) loop and an

outer (voltage) loop. The latter is composed by voltage regu-

lation and balance loops. The inner loop deals with subsystem

(10), where an expression for

1

has to be obtained to guarantee

current tracking. The design of this controller is based on the

energy shaping plus damping injection technique of the PBC

approach [25]. The outer loop deals with subsystems (11) and

(12), where expressions are obtained for the power reference

P

ref

(used to design the current reference i

S

) and

2

.

A. Current Tracking Loop

The design of this loop involves subsystem (10). Its purpose

is to design a control signal

1

to force the grid current i

S

to

follow its reference i

S

. Expressing subsystem (10) in terms of

the increments x

1

= x

1

i

S

yields

(L + L

G

)

x

1

= r

G

x

1

. .

damping

1

+ v

SG

+ (L + L

G

)

di

S

dt

r

G

x

1

+ L

di

0

dt

. .

harmonic disturbance

. (23)

In (23), it is possible to identify a small amount of damping,

due to parasitic resistor r

G

, that must be reinforced. There

is also certain amount of harmonic distortion that must be

3

An unavoidable second harmonic ripple arises in the capacitor voltages

due to the power uctuation in single-phase systems; therefore, this regulation

objective can only be fullled in average.

compensated. Based on the structure of subsystem (23), the

following controller is proposed

1

= v

S

+ k

1

x

1

+

(24)

where k

1

> 0 is a design parameter used to insert the required

damping. Notice that the aforementioned controller includes a

feedforward term v

S

, a damping term k

1

(x

1

i

S

) to reinforce

the stability, and nally, it includes a harmonic compensation

term represented by

. See [26] for further details on the design

of this loop.

The closed-loop system of the subsystem (23) and controller

(24) yields the following perturbed linear time-invariant (LTI)

system, which is referred to as the error dynamics

L

x

1

= k

1

x

1

+ (25)

where

= L(di

0

/dt di

S

/dt) represents a periodic distur-

bance according to A3. Notice that the introduction of the

feedforward term v

S

in controller (24) causes the decoupling of

the line impedance dynamics. That is, the terms associated with

this impedance are eliminated from the error dynamics (25).

However, the effect of the voltage drop in this impedance is

still observed in v

S

, which is propagated to both the load and

the active lter.

4

Following a similar approach as in [28], an expression for the

harmonic compensation term

can be proposed. It consists of

a bank of harmonic oscillators (resonant lters), as described as

follows:

s

s

2

+

2

2

0

x

1

(26)

where

( H) is a positive design parameter representing

the gain of the th harmonic oscillator. Notice that, in this har-

monic compensation mechanism, the harmonic oscillators are

tuned at the harmonics under concern, i.e., the odd harmonics,

which are in agreement with the internal model principle. A

complete stability analysis and more details on the derivation

of this inner loop can be found in [28]. A block diagram of

the current tracking loop composed by (24) and (26) is shown

in Fig. 2.

Remark III.1: Notice that the proposed current controller

applies, without any change, to either of the aforementioned

current reference i

S

denitions, either using v

S

(15) or using

the fundamental component v

S,1

(16).

B. Voltage Regulation Loop

The design of the regulation loop involves subsystem (11).

Moreover, based on A1, it is considered that the current tracking

objective has been fullled after a relatively short time, i.e.,

x

1

= i

S

,

= , and thus,

1

= v

S

+ . Direct substitution

of these in (11) and considering only the dc component of

4

If the dynamics of the load is considered, then the problem becomes much

more involved as presented in [27]. Studies concerning this issue are out of the

scope of this paper.

VALDEZ-FERNNDEZ et al.: CONTROLLER FOR CHB MULTILEVEL CONVERTER USED AS SHUNT ACTIVE FILTER 5023

Fig. 2. Block diagram of the overall proposed controller including the voltage

regulation and balance loops, the current tracking loop, and a block where duty

ratios are computed and used in a modulation scheme to generate the switching

signals to the gates.

all terms, i.e., neglecting the harmonic components, yield the

following system:

C x

2

=

2

R

x

2

+ P

ref

P

0

(27)

where P

0

is the dc component of the instantaneous output

power p

0

. The latter is dened as p

0

= v

S

i

0

. Hence, P

0

is an

unknown constant.

Notice that P

ref

appears as the actual control input of the

rst-order system (27). The proposed controller consists of

proportional-plus-integral terms, where the proportional term

is of limited bandwidth. Both terms operate on the error signal

x

2

= (x

2

V

2

d

). This control loop is given as follows in its

transfer function form:

P

ref

=

_

k

p2

s + 1

+

k

i2

s

_

x

2

(28)

where k

p2

and k

i2

are the proportional and integral gains of the

PI controller, respectively, and is the time constant of a low-

pass lter (LPF) affecting the proportional term. This controller

guarantees that x

2

V

2

d

in average, as t , while keeping

P

ref

bounded. A block diagram of the regulation loop is shown

in Fig. 2.

C. Voltage Balance Loop

The design of the balance loop is based on the structure of

subsystem (12). Based on A1, it is assumed that x

1

= i

S

after

a relatively short time. Direct substitution of this in (12) yields

the following system:

C x

3

=

2

R

x

3

+

2

_

P

ref

v

2

S,RMS

v

S

i

0

_

. (29)

For this system, the following controller is proposed:

2

=

v

2

S,RMS

v

S

(30)

where is a modulating gain to be dened next. Notice that the

expression of controller

2

consists of a signal proportional to

the line voltage v

S

.

The closed loop between (29) and (30) yields

C x

3

=

2

R

x

3

v

2

S,RMS

(P

ref

P

0

) (31)

where only the dc component of all terms has been considered,

i.e., the higher order harmonics have been neglected. As ob-

served in (31), the division by v

2

S,RMS

in (30) is necessary to

prevent from taking extremely small values, which may entail

numerical errors.

Notice that if this dynamics is made much slower than the

rest of the dynamics, then P

ref

P

0

equals the dissipated

power in resistors R, i.e., P

ref

P

0

= 2V

2

d

/R. Therefore, this

difference between powers has predominantly a positive sign.

The modulating gain can thus be proposed as the following

PI controller:

=

_

k

p3

+

k

i3

s

_

x

3

(32)

where k

p3

and k

i3

are the proportional and integral gains of the

PI controller. A block diagram of this proposed balance loop is

shown in Fig. 2.

Remark III.2: The proposed balancing controller might have

a slow dynamical response as it depends on the amount of

power dissipated in resistors R. However, this scheme has the

advantage of not requiring an extra current sensor.

A faster response on the balancing loop can be obtained at

the expenses of adding an extra current sensor to involve the

information of the compensating current i. For this, notice that

the control signal

2

in (12) is multiplying the compensating

current i = x

1

i

0

. Based on this, an alternative proposal for

the balance control loop could be

2

= sign(i) (33)

=

_

k

p3

+

k

i3

s

_

x

3

(34)

where signal

2

has the same frequency and phase as the

compensating current i, whose amplitude is modulated by .

IV. PARAMETER TUNING

As it has been stated before, the tracking error x

1

converges

to zero provided that the control parameter k

1

is positive.

However, more specic design rules for k

1

are still necessary

to achieve a desired dynamic performance. For this, recall that

the current loop dynamics is considered as the fastest dynamics

from the overall system. These dynamics (also referred as

error dynamics), formed by subsystem (23) in closed loop with

controller (24), are given by

L

x

1

+ k

1

x

1

=

(35)

where

represents the disturbance rejection error.

Notice that the bandwidth of (35) is given by

bwx

1

= k

1

/L.

It is proposed to tune k

1

by xing

bwx

1

to be, at most,

5024 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 60, NO. 11, NOVEMBER 2013

one-tenth of the sampling frequency given by 2f

s

[29], i.e.,

bwx

1

f

s

/5. Hence, the control parameter can be xed

according to

k

1

f

s

L

5

. (36)

The voltage regulation loop control parameters k

i2

and k

p2

can be tuned using the closed-loop dynamics between system

(27) and controller (28). The state-space representation of these

dynamics is given by

C

x

2

= k

p2

1

k

i2

2

R

x

2

2V

2

d

R

(37)

1

=( x

2

1

) (38)

2

= x

2

(39)

where

1

and

2

are auxiliary variables of the controller (28)

that represent the states of the LPF and the integral term,

respectively.

It is common in practice to select 1/(2

0

), with

0

as the fundamental frequency. In this way, the effect of the

pole located at 1/ can be neglected as it is far enough with

respect to the remaining dominant poles of system (37)(39).

Hence, the characteristic polynomial of system (37)(39) can

be reduced to

s

2

+

k

p2

R + 2

RC

s +

k

i2

C

= 0 (40)

where the natural oscillation frequency is

n2

=

_

k

i2

/C and

the damping factor is

2

= (k

p2

R + 2)/(2R

k

i2

C). Now, if

the damping factor is restricted to

2

1/

2, then the voltage

dynamics bandwidth fullls

bwx

2

n2

. To be consistent

with the appealed time-scale separation assumption A1,

bwx

2

must be, at most, one-tenth of the current dynamics bandwidth

bwx

1

, i.e.,

bwx

2

bwx

1

/10. However, to avoid the effect of

the second harmonic ripple present in the dc capacitor voltages,

it is proposed to restrict even more

bwx

2

to about

0

/5. Out of

this, the parameters can be tuned as

k

i2

2

0

C

25

k

p2

0

C

5

2

(41)

where it is assumed that

0

RC 10

2.

The voltage balance loop control parameters k

i3

and k

p3

can

be tuned using the dynamics of system (31) in closed loop

with controller (32). The state-space representation of these

dynamics is given by

C x

3

=

_

k

p3

(P

ref

P

0

)

v

2

S,RMS

+

2

R

_

x

3

k

i3

(P

ref

P

0

)

v

2

S,RMS

(42)

=x

3

(43)

where is the state of the integral part of the PI.

If these dynamics are made much slower than the rest of

the system, then it can be assumed that P

ref

P

0

= 2V

2

d

/R.

Thus, the characteristic polynomial of systems (42) and (43) is

given by

s

2

+

2V

2

d

k

p3

+ 2v

2

S,RMS

RCv

2

S,RMS

s +

2V

2

d

k

i3

RCv

2

S,RMS

= 0 (44)

where the natural oscillation frequency is

n3

=

(V

d

/v

S,RMS

)

_

2k

i3

/(RC) and the damping factor is

3

= (k

p3

V

2

d

+ v

2

S,RMS

)/(

n3

RCv

2

S,RMS

). As in the voltage

regulation loop, the damping factor is restricted to

3

1/

2.

Out of this, the bandwidth of the voltage balance dynamics

fullls

bwx

3

n3

. As pointed out before, these dynamics

must be the slowest. Therefore, it is proposed to restrict their

bandwidth to about 0.1 Hz, i.e.,

bwx

3

0.63. Hence, the

parameters can be tuned according to the following rules:

k

i3

0.2RCv

2

S,RMS

V

2

d

(45)

k

p3

(0.45RC 1)v

2

S,RMS

V

2

d

. (46)

V. EXPERIMENTAL RESULTS

The proposed controller has been experimentally tested in a

2-kVA active lter prototype. A voltage source of 120 V

RMS

,

f

0

= 60 Hz (

0

= 377 rad/s), is considered. A single-phase

diode bridge rectier is considered as the nonlinear load. It

includes a dc capacitor of 80 F and a resistive load that can

be changed between 64 and 36 to test load step changes.

This nonlinear load produces a distorted current containing

all odd harmonics of the fundamental frequency (60 Hz). The

active lter has been designed with parameters L = 3 mH,

C = 2200 F, and R = 22 k. The voltage reference for both

dc capacitors is xed to V

d

= 110 V.

The controller scheme has been implemented in a dSPACE

board ACE1103 with a sampling frequency of f

s

= 40.5 kHz.

A phase-shifted multicarrier modulation scheme [30] has been

used to generate the switching signals to the gates. The switch-

ing frequency of the devices is xed to f

sw

= 6 kHz, which

produces an effective inverter switching frequency of 24 kHz.

The control parameters are xed according to conditions (36),

(41), (45), and (46) as follows: k

1

= 60, k

p2

= 0.5, k

i2

= 1,

= 0.0001, k

p3

= 25, and k

i3

= 10. The set of harmonics

under consideration is given by H = {1, 3, 5, 7, 9, 11, 13, 15}.

To guarantee a safer operation, the resonant lters in the

harmonic compensation mechanism (26) have been imple-

mented using a BPF structure, with relatively large gains and

quality factors. Notice that resonant lters have, ideally, in-

nite gain at the resonant frequency, while BPFs have limited

gain. The BPFs have been implemented following the guide-

lines in [31]. The harmonic compensation mechanism is thus

approximated as

H

sA

o,

0

Q

s

2

+ s

0

/Q

+

2

2

0

x

1

(47)

where the design parameter A

o,

> 0 is the gain of the BPF

at the th resonance frequency, i.e.,

0

, and Q

is the

VALDEZ-FERNNDEZ et al.: CONTROLLER FOR CHB MULTILEVEL CONVERTER USED AS SHUNT ACTIVE FILTER 5025

Fig. 3. Steady-state response of the active lter under the proposed control

solution. (From top to bottom) Grid voltage v

S

(x-axis 4 ms/div; y-axis

220 V/div), compensated grid current i

S

, load current i

0

, and injected current

i (x-axis 4 ms/div; y-axis 10 A/div).

Fig. 4. (From top to bottom) Load current i

0

(x-axis: 10 ms/div; y-axis:

10 A/div), frequency spectrum of i

0

(x-axis: 125 Hz/div; y-axis: 20 dB/div),

compensated grid current i

S

(x-axis: 10 ms/div; y-axis: 10 A/div), and fre-

quency spectrum of i

S

(x-axis: 125 Hz/div; y-axis: 20 dB/div).

corresponding quality factor. These gains have been xed

to A

1

= 120, A

3

= 1350, A

5

= 1410, A

7

= 1200, A

9

= 900,

A

11

= 1500, A

13

= 1100, and A

15

= 330, and the quality fac-

tors have been xed to Q

1

= 20, Q

3

= 30, Q

5

= 30, Q

7

= 30,

Q

9

= 30, Q

11

= 55, Q

13

= 55, and Q

15

= 55.

Figs. 38 show the results considering the construction of the

reference current as a signal proportional to the grid voltage,

i.e., i

S

= P

ref

v

S

/v

2

S,RMS

.

Fig. 3 shows that, under the proposed controller, the grid

current i

S

(second plot from the top) gets a shape proportional

Fig. 5. Frequency spectra of (top) grid voltage v

S

and (bottom) compensated

grid current i

S

(x-axis: 62.5 Hz/div; y-axis: 20 dB/div).

Fig. 6. Transient response of the active lter under the proposed solution

during load step changes (a) from R

L

= 64 to R

L

= 36 and (b) back

from R

L

= 36 to R

L

= 64 . (From top to bottom) Compensated grid

current i

S

, load current i

0

, and injected current i (x-axis: 40 ms/div; y-axis:

10 A/div).

(and in phase) to the grid voltage v

S

(top plot) despite the highly

distorted load current i

0

(third plot from the top).

Fig. 4 shows that the load current is composed mainly by

odd harmonics (1, 3, 5, 7, 9, 11, 13, and 15) of the fundamental

frequency. The distorted load current has a total harmonic dis-

tortion (THD) of 49.55%, while the THD of the compensated

grid current is reduced to 1.78%. Fig. 5 shows that the remanent

harmonic contents of the compensated grid current i

S

(bottom

plot) is, as expected, very similar to that of the line voltage v

S

(top plot). In fact, v

S

has a slight distortion representing a THD

of 1.62%.

Fig. 6 shows the transient responses of the proposed solution

when the load resistor in the diode bridge rectier is changed

5026 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 60, NO. 11, NOVEMBER 2013

Fig. 7. (From top to bottom) Transient responses of the capacitor voltages

v

C1

and v

C2

(x-axis: 200 ms/div; y-axis: 110 V/div), the voltage difference

v

C1

v

C2

(x-axis: 200 ms/div; y-axis: 11 V/div), and the power reference

P

ref

computed in the regulation loop (x-axis: 200 ms/div; y-axis: 1 kW/div).

Fig. 8. (From top to bottom) Transient responses of capacitor voltages v

C1

and v

C2

(x-axis: 2 s/div; y-axis: 27.5 V/div) and the voltage difference v

C1

v

C2

(x-axis: 2 s/div; y-axis: 11 V/div). (a) Start-up of capacitor voltages

under unbalanced initial conditions and (b) creating unbalance in the capacitor

voltages by connecting and disconnecting a resistor of 200 from the lower dc

capacitor in Fig. 1.

from64 to 36 [Fig. 6(a)] and back from36 to 64 [Fig. 6(b)].

Notice that, in either case, the envelopes of all currents reach

constant values after relatively short transients. In particular,

the transient of the grid current is sufciently smooth with a

relatively small overshoot.

Fig. 7 shows that, after relatively short transients, the ca-

pacitor voltages v

C1

and v

C2

converge toward their constant

reference xed at V

d

= 110 V. Similarly, the voltage difference

v

C1

v

C2

converges to zero after almost imperceptible tran-

sients. Finally, this gure also shows that, after relatively short

Fig. 9. Steady-state response of the active lter under the proposed control

solution, where the fundamental component of the grid voltage v

S,1

is used to

dene i

S

. (From top to bottom) Grid voltage v

S

(x-axis: 4 ms/div; y-axis:

220 V/div), compensated grid current i

S

, load current i

0

, and injected current

i (x-axis: 4 ms/div; y-axis: 10 A/div).

transients, the power reference P

ref

reaches constant levels,

which are representative of the total dissipated power.

Fig. 8 shows the transient responses of capacitor voltages v

C1

and v

C2

(rst two plots from the top) and the voltage difference

v

C1

v

C2

(bottom plot). Fig. 8(a) shows the responses during

the start-up. In this case, an unbalance initial condition is

created on v

C1

and v

C2

by connecting a resistor of 200 across

the lower dc capacitor in Fig. 1 before starting. Fig. 8(b) shows

the transient responses when the resistor of 200 is connected

and disconnected from the lower dc capacitor in Fig. 1, thus

creating an unbalanced situation. Notice that, in either case,

after relatively short transients, both capacitor voltages v

C1

and

v

C2

converge toward their constant reference xed at V

d

=

110 V, and thus, the voltage difference v

C1

v

C2

converges

to zero as well.

As previously mentioned, the proposed scheme can be easily

modied to consider a current reference i

S

proportional to the

fundamental component of the grid voltage v

S,1

, i.e., i

S

=

P

ref

v

S,1

/v

2

S,RMS

. Figs. 9 and 10 show the results using this

simple modication.

Fig. 9 shows that, under the proposed scheme, the grid

current i

S

(second plot from the top) reaches an almost pure

sinusoidal waveformin phase with the grid voltage v

S

(top plot)

despite the highly distorted load current i

0

(third plot from the

top).

Finally, Fig. 10 shows that the THD of the compensated grid

current i

S

is reduced to 1.02%, as, in this case, it is forced to

track a pure sinusoidal signal reference.

VI. CONCLUDING REMARKS

This paper has presented a controller for the single-phase

CHB multilevel converter used as an active lter. The proposed

VALDEZ-FERNNDEZ et al.: CONTROLLER FOR CHB MULTILEVEL CONVERTER USED AS SHUNT ACTIVE FILTER 5027

Fig. 10. Steady-state response of the active lter under the proposed control

solution, where the fundamental component of the grid voltage v

S,1

is used to

dene i

S

. (From top to bottom) Load current i

0

, frequency spectrum of i

0

,

compensated grid current i

S

, and frequency spectrum of i

S

. For time-domain

signals, x-axis: 10 ms/div and y-axis: 10 A/div, and for frequency spectra,

x-axis: 125 Hz/div and y-axis: 20 dB/div.

controller was designed based on the structure of the system

model, in this case, a ve-level converter. The decoupling as-

sumption was invoked to split and, thus, facilitate the controller

design. Out of this, three control loops could be identied,

namely, current tracking loop, voltage regulation loop, and

voltage balance loop. The current tracking loop was composed

of a damping term plus a bank of harmonic oscillators tuned

at the harmonics of interest, which is in agreement with the

internal model principle. The harmonic oscillators were im-

plemented using BPFs with high gain and high quality factor

to guarantee a safer operation. The voltage regulation loop

consisted of a conventional PI of limited bandwidth. Finally,

to solve the voltage balance issue, a control signal is syn-

thesized as an amplitude-modulated signal proportional to the

line voltage, where the modulating gain is obtained out of a

conventional PI. Two reference structures for the grid current

have been presented: First, a current reference proportional to

the grid voltage, and second, a current reference proportional

to the fundamental component of the grid voltage. The former

produced a grid current as distorted as the grid voltage, while

the latter guaranteed an almost pure sinusoidal grid current. In

both cases, most part of the controller remained unchanged. The

proposed scheme was tested in a 2-kVA active lter prototype.

The experimental results conrmed that the current tracking,

voltage regulation, and balance objectives can be achieved with

a good performance in spite of the existence of a relatively high

harmonic distortion in the load current.

REFERENCES

[1] S. Kouro, M. Perez, H. Robles, and J. Rodriguez, Switching loss analysis

of modulation methods used in cascaded H-bridge multilevel converters,

in Proc. IEEE PESC, Jun. 1519, 2008, pp. 46624668.

[2] J. Rodriguez, J. S. Lai, and F. Z. Peng, Multilevel Inverters: A survey of

topologies, controls and applications, IEEE Trans. Ind. Electron., vol. 49,

no. 4, pp. 724738, Aug. 2002.

[3] J. Rodrguez, L. G. Franquelo, S. Kouro, J. I. Leon, R. C. Portillo,

M. A. M. Prats, and M. A. Perez, Multilevel converters: An enabling

technology for high-power applications, Proc. IEEE, vol. 97, no. 11,

pp. 17861817, Nov. 2009.

[4] A. Nabae, I. Takahashi, and H. Akagi, A neutral-point clamped PWM

inverter, IEEE Trans. Ind. Appl., vol. IA-17, no. 5, pp. 518523,

Sep./Oct. 1981.

[5] S. Kouro, M. Malinowski, K. Gopakumar, J. Pou, L. G. Franquelo, B. Wu,

J. Rodriguez, M. A. Perez, and J. I. Leon, Recent advances and industrial

applications of multilevel converters, IEEE Trans. Ind. Electron., vol. 57,

no. 8, pp. 25532580, Aug. 2010.

[6] R. Teodorescu, F. Blaabjerg, J. K. Pederses, E. Cengelci, S. U. Sulistijo,

B. O. Woo, and P. Enjeti, Multilevel converters: A survey, in Proc. 8th

EPE, 1999, CD-ROM.

[7] F. Z. Peng and J. S. Lai, Multilevel cascade voltage-source inverter with

separate DC sources, U.S. Patent 5 642 275, Jun. 24, 1997.

[8] Y. Cheng, C. Qian, M. L. Crow, S. Pekarek, and S. Atcitty, A comparison

of diode-clamped and cascaded multilevel converters for a STATCOM

with energy storage, IEEE Trans. Ind. Electron., vol. 53, no. 5, pp. 1512

1521, Oct. 2006.

[9] L. M. Tolbert, F. Z. Peng, and T. G. Habetler, Multilevel PWM methods

at low modulation indices, IEEE Trans. Power Electron., vol. 15, no. 4,

pp. 719725, Jul. 2000.

[10] M. Odavic, M. Sumner, and P. Zanchetta, Control of a multi-level ac-

tive shunt power lter for more electric aircraft, in Proc. 13th EPE,

Sep. 810, 2009, pp. 110.

[11] M. Odavic, V. Biagini, M. Sumner, P. Zanchetta, and M. Degano, Multi-

sampled carrier-based PWM for multilevel active shunt power lters

for aerospace applications, in Proc. IEEE ECCE, Sep. 1722, 2011,

pp. 14831488.

[12] V. G. Agelidis, A. I. Balouktsis, and M. S. A. Dahidah, A ve-level sym-

metrically dened selective harmonic elimination PWM strategy: Analy-

sis and experimental validation, IEEE Trans. Power Electron., vol. 23,

no. 1, pp. 1926, Jan. 2008.

[13] J. I. Leon, S. Kouro, S. Vazquez, R. Portillo, L. Garcia, J. M. Carrasco,

and J. Rodriguez, Multidimensional modulation technique for cascaded

multilevel converters, IEEE Trans. Ind. Electron., vol. 58, no. 2, pp. 412

420, Feb. 2011.

[14] G. Escobar, A. A. Valdez, M. F. Martinez-Montejano, and

V. M. Rodriguez-Zermeo, A model-based controller for the cascade

multilevel converter used as a shunt active lter, in Proc. IAS, Sep.

2228, 2007, pp. 18371843.

[15] A. DellAquila, M. Liserre, V. G. Monopoli, and P. Rotondo, Overview

of PI-based solutions for the control of DC buses of a single-phase

H-bridge multilevel active rectier, IEEE Trans. Ind. Appl., vol. 44, no. 3,

pp. 857866, May/Jun. 2008.

[16] H. Sepahvand, J. Liao, and M. Ferdowsi, Investigation on capacitor

voltage regulation in cascaded H-bridge multilevel converters with funda-

mental frequency switching, IEEE Trans. Ind. Electron., vol. 58, no. 11,

pp. 51025111, Nov. 2011.

[17] A. Barrena, L. Marroyo, M. A. Rodriguez, and J. R. Torrealday, Indi-

vidual voltage balancing strategy for PWM cascaded H-bridge converter-

based STATCOM, IEEE Trans. Ind. Electron., vol. 55, no. 1, pp. 2129,

Jan. 2008.

[18] F. Z. Peng and J. S. Lai, Dynamic performance and control of a static

var generator using cascade multilevel inverters, IEEE Trans. Ind. Appl.,

vol. 33, no. 3, pp. 748755, May/Jun. 1997.

[19] H. Akagi, S. Inoue, and T. Yoshii, Control and performance of a trans-

formerless cascade PWM STATCOM with star conguration, IEEE

Trans. Ind. Appl., vol. 43, no. 4, pp. 10411049, Jul./Aug. 2007.

[20] X. Xu, Q. Zhang, Q. Cheng, Y. Yuan, and Y. Xiao, An auto-disturbance

rejection controller for STATCOM based on cascaded multilevel invert-

ers, in Proc. IPEMC, May 1720, 2009, pp. 23492353.

[21] C. Cecati, A. DellAquila, M. Liserre, and V. G. Monopoli, Design of

H-bridge multilevel active rectier for traction systems, IEEE Trans. Ind.

Appl., vol. 39, no. 5, pp. 15411550, Sep./Oct. 2003.

[22] C. Cecati, A. DellAquila, M. Liserre, and V. G. Monopoli, A passivity-

based multilevel active rectier with adaptive compensation for traction

applications, IEEE Trans. Ind. Appl., vol. 39, no. 5, pp. 14041413,

Sep./Oct. 2003.

[23] A. DellAquila, M. Liserre, V. G. Monopoli, and P. Rotondo, An energy-

based control for an n-H-bridges multilevel active rectier, IEEE Trans.

Ind. Electron., vol. 52, no. 3, pp. 670678, Jun. 2005.

[24] G. Escobar, M. F. Martinez-Montejano, P. R. Martinez-Rodriguez, and

M. Hernandez-Gomez, A model-based controller for the cascade

H-bridge multilevel converter used as a shunt active lter, in Proc. IEEE

PESC, Jun. 1822, 2006, pp. 15.

5028 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 60, NO. 11, NOVEMBER 2013

[25] R. Ortega, A. Loria, P. J. Nicklasson, and H. Sira-Ramirez, Passivity-

Based Control of EulerLagrange Systems. New York: Springer-Verlag,

1998.

[26] G. Escobar, A. Stankovic, and P. Mattavelli, An adaptive controller in

stationary reference frame for D-STATCOM in unbalanced operation,

IEEE Trans. Ind. Electron., vol. 51, no. 2, pp. 401409, Apr. 2004.

[27] A. A. Valdez, G. Escobar, and R. Ortega, An adaptive controller for the

shunt active lter considering a dynamic load and the line impedance,

IEEE Trans. Control Syst. Technol., vol. 17, no. 2, pp. 458464,

Mar. 2009.

[28] G. Escobar, A. M. Stankovi c, and D. Perrault, Regulation and compen-

sation of source harmonics for the boost-converter based power factor

precompensator, in Proc. IEEE PESC, Jun. 1722, 2001, pp. 539544.

[29] G. Escobar, A. A. Valdez, R. Torres-Olguin, and M. Martinez-Montejano,

A model-based controller for a three-phase four-wire shunt active l-

ter with compensation of the neutral line current, IEEE Trans. Power

Electron., vol. 22, no. 6, pp. 22612270, Nov. 2007.

[30] B. Wu, High-Power Converters and AC Drives. Piscataway, NJ: IEEE

Press, 2006.

[31] G. Clayton and S. Winder, Operational Ampliers, 4th ed. London,

U.K.: Butterworth, Jun. 2000.

Andrs A. Valdez-Fernndez (S05M08) re-

ceived the Ph.D. degree in control and dynamical

systems from the Potosi Institute of Scientic and

Technological Research (IPICyT), San Luis Potosi,

Mexico, in 2009.

From 2008 to 2012, he was a Professor

Researcher with the Technological Institute of Supe-

rior Studies of Irapuato (ITESI), Irapuato, Mexico.

He is currently a Professor with the Electronic En-

gineering Group, School of Sciences, Autonomous

University of San Luis Potosi (UASLP), San Luis

Potosi. His main research interests include analysis, modeling, and control de-

sign of active power lters, inverters, rectiers, and renewable energy systems.

Pnlo R. Martnez-Rodrguez (M10) received

the Ph.D. degree from the Potosi Institute of Scien-

tic and Technological Research (IPICyT), San Luis

Potosi, Mexico, in 2007.

Since August 2006, he has been with the Labora-

tory of Electrical and Power Electronics, Technolog-

ical Institute of Superior Studies of Irapuato (ITESI),

Irapuato, Mexico, where he is currently a Professor/

Researcher. His main research interests include mod-

eling, analysis, and control design for power elec-

tronics systems and renewable energy systems.

Gerardo Escobar (M02SM08) received the

Ph.D. degree from the LSS, SUPELEC/CNRS/

University of Paris Sud XI, Paris, France, in 1999.

From 2010 to 2012, he was a Principal Scientist

with the Power Electronics Group, ABB Corporate

Research Center, Baden-Dattwil, Switzerland. He is

currently a ProfessorResearcher with the School

of Engineering, Autonomous University of Yucatan

(UADY), Merida, Mexico. His main research inter-

ests include analysis and control design of switching

power converters, active lters, inverters, electrical

drives, and renewable energy systems.

Cesar A. Limones-Pozos received the M.Sc. degree

in electronic engineering from the Technological

Institute of Superior Studies of Irapuato (ITESI),

Irapuato, Mexico, in 2012.

Since 2011, he has been with the Laboratory of

Electrical and Power Electronics, ITESI, where he is

currently an Associated Professor. His main research

interest is the application of control theory to power

electronics systems.

Jos M. Sosa (M02) received the Ph.D. degree in

applied sciences from the Potosi Institute of Scien-

tic and Technological Research (IPICyT), San Luis

Potosi, Mexico, in 2009.

He is currently with the Laboratory of Electri-

cal and Power Electronics, Technological Institute

of Superior Studies of Irapuato (ITESI), Irapuato,

Mexico, where he has been a Professor/Researcher

since 2008. His current research interests include

nonlinear control theory and applications to under-

actuated mechanical systems and control design for

power electronics converters.

Você também pode gostar

- Me Ped 2013Documento52 páginasMe Ped 2013Madhumitha RajasekaranAinda não há avaliações

- FGMO - PDF FGMO - PDF FGMO - PDF FGMO PDFDocumento5 páginasFGMO - PDF FGMO - PDF FGMO - PDF FGMO PDFabhi24shekAinda não há avaliações

- IT6502-Digital Signal ProcessingDocumento10 páginasIT6502-Digital Signal ProcessingMadhumitha RajasekaranAinda não há avaliações

- Group NamesDocumento3 páginasGroup NamesMadhumitha RajasekaranAinda não há avaliações

- Current Affairs For VaoDocumento105 páginasCurrent Affairs For VaoMadhumitha RajasekaranAinda não há avaliações

- Detailed SyllabusDocumento17 páginasDetailed SyllabusArinder SinghAinda não há avaliações

- MRAC BhatDocumento61 páginasMRAC BhatMadhumitha RajasekaranAinda não há avaliações

- NCPD 2014 - 18 12 2013Documento8 páginasNCPD 2014 - 18 12 2013Madhumitha RajasekaranAinda não há avaliações

- Objective Type Questions: DE05 Electrical EngineeringDocumento59 páginasObjective Type Questions: DE05 Electrical EngineeringMadhumitha RajasekaranAinda não há avaliações

- Paper 17Documento4 páginasPaper 17Aong AongAinda não há avaliações

- PVarray Demos HelpDocumento4 páginasPVarray Demos HelpManav Kumar0% (1)

- An Adaptive Load Shedding Method With Time-Based Design For Isolated Power SystemsDocumento8 páginasAn Adaptive Load Shedding Method With Time-Based Design For Isolated Power SystemsMadhumitha RajasekaranAinda não há avaliações

- 39 Kirubakaran.BDocumento2 páginas39 Kirubakaran.BMadhumitha RajasekaranAinda não há avaliações

- 12MPS1024 1modiDocumento17 páginas12MPS1024 1modiMadhumitha RajasekaranAinda não há avaliações

- Harmonic Mitigation Using Single Phase Shunt Active Power Filter With Fuzzy Logic Controller For The Improvement of Power QualityDocumento6 páginasHarmonic Mitigation Using Single Phase Shunt Active Power Filter With Fuzzy Logic Controller For The Improvement of Power QualityMadhumitha RajasekaranAinda não há avaliações

- Tourism Guide ErodeDocumento3 páginasTourism Guide ErodeMadhumitha RajasekaranAinda não há avaliações

- Analytic Calculation of The DC LinkDocumento9 páginasAnalytic Calculation of The DC LinkMadhumitha RajasekaranAinda não há avaliações

- Reg FormDocumento2 páginasReg FormMadhumitha RajasekaranAinda não há avaliações

- 1 s2.0 S221267161200114X MainDocumento7 páginas1 s2.0 S221267161200114X MainMadhumitha RajasekaranAinda não há avaliações

- 2.5 PlantwidecontrolDocumento11 páginas2.5 PlantwidecontrolMadhumitha RajasekaranAinda não há avaliações

- Adaptive Voltage Control PDFDocumento141 páginasAdaptive Voltage Control PDFMadhumitha RajasekaranAinda não há avaliações

- ModellingDocumento9 páginasModellingdoud98Ainda não há avaliações

- Fuzzy PID ControllerDocumento7 páginasFuzzy PID ControllerMadhumitha RajasekaranAinda não há avaliações

- Spical Electrical Machines 2 MarksDocumento20 páginasSpical Electrical Machines 2 Markskarthicgroup100% (1)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNo EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNota: 4 de 5 estrelas4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItNo EverandNever Split the Difference: Negotiating As If Your Life Depended On ItNota: 4.5 de 5 estrelas4.5/5 (838)

- The Yellow House: A Memoir (2019 National Book Award Winner)No EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Nota: 4 de 5 estrelas4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNo EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNota: 4 de 5 estrelas4/5 (5794)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNo EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNota: 4.5 de 5 estrelas4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingNo EverandThe Little Book of Hygge: Danish Secrets to Happy LivingNota: 3.5 de 5 estrelas3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNo EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNota: 4.5 de 5 estrelas4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNo EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNota: 3.5 de 5 estrelas3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerNo EverandThe Emperor of All Maladies: A Biography of CancerNota: 4.5 de 5 estrelas4.5/5 (271)

- The Unwinding: An Inner History of the New AmericaNo EverandThe Unwinding: An Inner History of the New AmericaNota: 4 de 5 estrelas4/5 (45)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNo EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNota: 4.5 de 5 estrelas4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnNo EverandTeam of Rivals: The Political Genius of Abraham LincolnNota: 4.5 de 5 estrelas4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNo EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNota: 4 de 5 estrelas4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyNo EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyNota: 3.5 de 5 estrelas3.5/5 (2259)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)No EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Nota: 4.5 de 5 estrelas4.5/5 (121)

- Vol20no4 PDFDocumento2 páginasVol20no4 PDFRICHARD100% (1)

- Basic Calculation of A Boost Converter's Power StageDocumento8 páginasBasic Calculation of A Boost Converter's Power StageGiao NguyenAinda não há avaliações

- Microchips 2edDocumento208 páginasMicrochips 2edMichelle Marzan CaranguianAinda não há avaliações

- Phase Angle Control D STATCOMDocumento8 páginasPhase Angle Control D STATCOMtabendaaarzuAinda não há avaliações

- GHF - S of TT - Technical CurriculumDocumento65 páginasGHF - S of TT - Technical CurriculumDxmplesAinda não há avaliações

- On The Mathematical Foundations of Electrical Circuit TheoryDocumento18 páginasOn The Mathematical Foundations of Electrical Circuit TheorysdAinda não há avaliações

- H.voltage (Chapter#05 (B) )Documento64 páginasH.voltage (Chapter#05 (B) )Nicholas FosterAinda não há avaliações

- MACH 5 Power: Application NoteDocumento4 páginasMACH 5 Power: Application NoteBeroxi MihaiAinda não há avaliações

- Submitted To: Subject Manual of Lab WorkDocumento61 páginasSubmitted To: Subject Manual of Lab WorkRana FaizanAinda não há avaliações

- SCT9320Documento20 páginasSCT9320Charith PereraAinda não há avaliações

- The Hallicrafters SR 75 SW Spectum Monitor Feb2017FinalDocumento7 páginasThe Hallicrafters SR 75 SW Spectum Monitor Feb2017Finalwilliam_V_LeeAinda não há avaliações

- Hybrid Transformer Model For Transient Simulation: Part I - Development and ParametersDocumento8 páginasHybrid Transformer Model For Transient Simulation: Part I - Development and ParametersJosAinda não há avaliações

- PCB Troubleshooting Techniques 818958Documento3 páginasPCB Troubleshooting Techniques 818958Edgar Dauzon50% (2)

- Xtravert Manual 707Documento84 páginasXtravert Manual 707Daria Gabriela Valimareanu0% (1)

- Current Resonant Control IC FA6B20N: DatasheetDocumento56 páginasCurrent Resonant Control IC FA6B20N: DatasheetCube7 Geronimo100% (8)

- Room Air Conditioner Service ManualDocumento63 páginasRoom Air Conditioner Service ManualBarry Burkan100% (1)

- Build This Stun-GunDocumento6 páginasBuild This Stun-GunagustinzmAinda não há avaliações

- Ds Stckliste k1823Documento8 páginasDs Stckliste k1823sdtrnkAinda não há avaliações

- Nema MG2 PDFDocumento40 páginasNema MG2 PDFRyukiAinda não há avaliações

- Astm F 528 - 99Documento7 páginasAstm F 528 - 99o_l_0Ainda não há avaliações

- LG Bb5430a PDFDocumento153 páginasLG Bb5430a PDFboroda241067% (12)

- Manual de Servicio RX GEDocumento52 páginasManual de Servicio RX GEKristian HernandezAinda não há avaliações

- A Fixed Frequency Series Parallel Resonant Converter With Capacitive Output Filter Analysis Design Simulation and Experimental ResultsDocumento10 páginasA Fixed Frequency Series Parallel Resonant Converter With Capacitive Output Filter Analysis Design Simulation and Experimental ResultsArsalan AtharAinda não há avaliações

- Physics G11 QueDocumento3 páginasPhysics G11 QueYan KyawAinda não há avaliações

- User Manual: 1305 Adjustable Frequency AC Drive (Series C)Documento170 páginasUser Manual: 1305 Adjustable Frequency AC Drive (Series C)gmdeucsAinda não há avaliações

- 400kv Nelamangana SubstationDocumento4 páginas400kv Nelamangana Substationtanwar_anuj199067% (3)

- A Comparative Study of Energy Management Schemes For A Fuel-Cell Hybrid Emergency Power System of More-Electric AircraftDocumento15 páginasA Comparative Study of Energy Management Schemes For A Fuel-Cell Hybrid Emergency Power System of More-Electric AircraftSouf Hack-digitalAinda não há avaliações

- P242 Basic Electronics LabDocumento61 páginasP242 Basic Electronics LabGanesh NandgaonkarAinda não há avaliações

- Power Flex 755Documento40 páginasPower Flex 755Alejandro HernandezAinda não há avaliações