Escolar Documentos

Profissional Documentos

Cultura Documentos

Universidade Federal Do Rio Grande Do Norte Projeto Final

Enviado por

Lwhyz Dantas0 notas0% acharam este documento útil (0 voto)

9 visualizações25 páginasDireitos autorais

© © All Rights Reserved

Formatos disponíveis

PDF, TXT ou leia online no Scribd

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato PDF, TXT ou leia online no Scribd

0 notas0% acharam este documento útil (0 voto)

9 visualizações25 páginasUniversidade Federal Do Rio Grande Do Norte Projeto Final

Enviado por

Lwhyz DantasDireitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato PDF, TXT ou leia online no Scribd

Você está na página 1de 25

UNIVERSIDADE FEDERAL DO RIO GRANDE DO NORTE

INSTITUTO METRPOLE DIGITAL

DISCIPLINA: CIRCUITO LGICO

RELATRIO DO PROJETO 3 UNIDADE

DISCENTES:

FELIPE ALBUQUERQUE

LUIZ CARLOS DANTAS DE OLIVEIRA

NATAL/RN

JUNHO DE 2014

UNIVERSIDADE FEDERAL DO RIO GRANDE DO NORTE

INSTITUTO METRPOLE DIGITAL

DISCIPLINA: CIRCUITO LGICO

RELATRIO DO PROJETO 3 UNIDADE

Relatrio da disciplina de

Circuito Logico do Curso de

Tecnologia da Informao da

Universidade Federal do Rio

Grande do Norte, para fins

avaliativos.

NATAL/RN

JUNHO DE 2014

RESUMO

Este trabalho foi realizado mediante ao contedo administrado durante o semestre

letivo. Os resultados obtidos durante as aulas, pratica e terica, ministrada pela disciplina de

Circuito Lgico. O resultado final de todo o contedo foi o projeto de um microprocessador

genrico. Este relatrio mostra a lgica implementada para obtermos o resultado final.

INTRODUO

Apesar de cada microprocessador ter seu prprio desenho interno, todos os

Microprocessadores compartilham do mesmo conceito bsico o qual explicaremos

neste relatrio .O processador que tambm chamado de microprocessador, CPU

(Central Processing Unit) ou UCP (Unidade Central de Processamento) o

encarregado de processar informaes. Como ele vai processar as informaes vai

depender do programa. O programa pode ser uma planilha, um processador de textos ou

um jogo: para o processador isso no faz a menor diferena, j que ele no entende o

que o programa est realmente fazendo. Ele apenas obedece s ordens (chamadas

comandos ou instrues) contidas no programa.

DESENVOLVIMETO

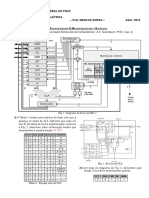

Na primeira parte do projeto foi desenvolvido o diagrama de bloco. Esse diagrama

um esboo geral do projeto final da disciplina.

Na segunda parte do projeto foi implementado o cdigo VHDL. Na qual foi testado e

implementada cada parte modulo, todos devidamente testado e resultado positivo. A tabela

abaixo mostra a descrio do trabalho pedido. O passo a passo .

Algumas explanaes sobre a Tabela 1:

RC=RA+RB, por exemplo, significa que os registradores RA e RB devem ser lidos

do banco de registradores, em seguida ser feito uma operao de adio com os valores

lidos e ento salvar esse resultado no registrador RC. A mesma lgica se aplica as

demais operaes que seguem esse formato.

m[RA+Const] representa o valor do registrador RA somado com a constante. Esse

valor (RA+Const) funciona como o endereo a ser acessado na memria, seja para

leitura ou escrita.

RB=RA+Const significa que deve ser lido o valor contido no registrador RA e somar

o mesmo com a constante. (O valor da constante est presente nos prprios bits da

operao).

O resultado deve ser armazenado no registrador RB.

LW uma operao que l um dado da memria e salva em um registrador. J a

operao SW o inverso: l do registrador e salva na memria.

Em ambos os casos, o resultado de RA+Const quem fornece a posio a ser acessada

na memria.

Logo acima foi explicado cada funo da tabela.

Vale ressaltar que no foi desenhado o diagrama de blocos da maquia de estados

(FSM). Outro problema que no obtivemos sucesso foi com a operao de leitura e escrita na

memoria. O dado feito a leitura, porm quando para escrita o valor escrito o mesmo da

memoria, ou seja, o valor da memorio e copiado para prxima memoria com o mesmo valor.

CONCLUSO

Durante o decorrer da disciplina e a solues de outros algoritmos, vimos que a

produo de um processador no uma tarefa to fcil, mas a emoo de um trabalho bastante

complexo ver funcionalidade do projeto.

Cdigos e simulaes de cada modulo do projeto

Cdigo do controle

Bloco principal

Contador

Cdigo VHDL

Maquina de Estados

Acima foi mostrado a descrio em VHDL maquina de estados, logo em seguida ser a

simulao da maquina de estados

Cdigo Resgistradores

Simulao do registrador

ULA

Simulao ULA

Você também pode gostar

- Entomologia Agrícola - Controle ComportamentalDocumento25 páginasEntomologia Agrícola - Controle ComportamentalLwhyz DantasAinda não há avaliações

- Controle de Plantas Daninhas Pelo MétodoDocumento3 páginasControle de Plantas Daninhas Pelo MétodoLwhyz DantasAinda não há avaliações

- SCHWARCZ Lilia Moritz. Racismo No Brasil - Quando Incluso C 2Documento7 páginasSCHWARCZ Lilia Moritz. Racismo No Brasil - Quando Incluso C 2Lwhyz DantasAinda não há avaliações

- 01 Fertilidade Do Solo e Produtividade AgricolaDocumento47 páginas01 Fertilidade Do Solo e Produtividade AgricolaLwhyz DantasAinda não há avaliações

- Cap 1 - Fertilidade Do Solo e Produtividade Agrícola - HistóricoDocumento60 páginasCap 1 - Fertilidade Do Solo e Produtividade Agrícola - HistóricoLwhyz DantasAinda não há avaliações

- 402 PDFDocumento38 páginas402 PDFLwhyz DantasAinda não há avaliações

- Tratores AgriculasDocumento24 páginasTratores AgriculasLwhyz DantasAinda não há avaliações

- Economia Florestal Atividade 1Documento1 páginaEconomia Florestal Atividade 1Lwhyz DantasAinda não há avaliações

- Introdução à Geologia GeralDocumento89 páginasIntrodução à Geologia Geraltonnylove2009Ainda não há avaliações

- Genética: conceitos, história e importânciaDocumento24 páginasGenética: conceitos, história e importânciaLwhyz DantasAinda não há avaliações

- Economia Florestal Atividade 1Documento1 páginaEconomia Florestal Atividade 1Lwhyz DantasAinda não há avaliações

- Aula 4 Apres FinalDocumento45 páginasAula 4 Apres FinalLwhyz DantasAinda não há avaliações

- 919 Questoes de Fisica ResolvidasDocumento273 páginas919 Questoes de Fisica ResolvidasPolly40864% (11)

- Mapa de KarnaughDocumento34 páginasMapa de KarnaughJosé PedroAinda não há avaliações

- Microcontroladores 2 Exercicios Macro e Microarquitetura v2Documento4 páginasMicrocontroladores 2 Exercicios Macro e Microarquitetura v2Marcelo LimaAinda não há avaliações

- Falhas FH4 FCIOMDocumento5 páginasFalhas FH4 FCIOMVINI100% (6)

- Gestão de serviços ISO 20000Documento11 páginasGestão de serviços ISO 20000Vanildo SouzaAinda não há avaliações

- Instalação do painel J3P em elevadores Selectron ACDocumento3 páginasInstalação do painel J3P em elevadores Selectron ACAlexandre JorgeAinda não há avaliações

- Implantação de Sistema de Gerenciamento de Parque AquaticoDocumento25 páginasImplantação de Sistema de Gerenciamento de Parque AquaticoAcademicosTIAinda não há avaliações

- Opm-ombr-oem-18-0037-Edbr - Gom Mobile para Inspeções Via TabletDocumento44 páginasOpm-ombr-oem-18-0037-Edbr - Gom Mobile para Inspeções Via TabletIvanildo pereiraAinda não há avaliações

- APQ ISO20000-1 2018-Webinar v.1.2 Final PDFDocumento16 páginasAPQ ISO20000-1 2018-Webinar v.1.2 Final PDFVanildo SouzaAinda não há avaliações

- Fornecimento em tensão secundáriaDocumento113 páginasFornecimento em tensão secundáriaDiogo Feltrin100% (1)

- Aula Microcontroladores 2 RegistradoresDocumento35 páginasAula Microcontroladores 2 RegistradoresLendione BatistaAinda não há avaliações

- AP2 - Atividade Teórica de Aprendizagem 02 - 2022A - Fundamentos de Marketing (57725)Documento3 páginasAP2 - Atividade Teórica de Aprendizagem 02 - 2022A - Fundamentos de Marketing (57725)Hugo EstevesAinda não há avaliações

- Relatório de Autoavaliação Institucional da Faculdade de Tecnologia ENIAC - FAPI 2014Documento124 páginasRelatório de Autoavaliação Institucional da Faculdade de Tecnologia ENIAC - FAPI 2014Claudio SantosAinda não há avaliações

- Excel Básico MÓDULO 1Documento37 páginasExcel Básico MÓDULO 1abdhuljafarAinda não há avaliações

- O que é robótica e seus principais tiposDocumento3 páginasO que é robótica e seus principais tiposJandir NevesAinda não há avaliações

- Sistema de Administração de Concursos DSEADocumento1 páginaSistema de Administração de Concursos DSEAnantesAinda não há avaliações

- Fechamento de Motor ElétricoDocumento5 páginasFechamento de Motor ElétricoGuilherme DombroskiAinda não há avaliações

- BIOCON READER 300 - Manual de OperaçõesDocumento33 páginasBIOCON READER 300 - Manual de Operaçõeshebertrocha76Ainda não há avaliações

- Candidatos 2a Fase MecânicaDocumento45 páginasCandidatos 2a Fase MecânicaEvandro RaphaloskiAinda não há avaliações

- COMPILADOASIDocumento62 páginasCOMPILADOASILia VieiraAinda não há avaliações

- Tabela Handytech - Ssa e Ios Quinta Feira 31 05Documento50 páginasTabela Handytech - Ssa e Ios Quinta Feira 31 05Danilo Costa RamalhoAinda não há avaliações

- 05 - The Torid AffairDocumento204 páginas05 - The Torid AffairJadna Rodrigues100% (1)

- Livro Automacao 2 EdDocumento18 páginasLivro Automacao 2 EdAtila DavidAinda não há avaliações

- Nastran Metodos Dos Elementos FinitosDocumento27 páginasNastran Metodos Dos Elementos FinitosronillmiguleAinda não há avaliações

- Log mantém transações em BDDocumento3 páginasLog mantém transações em BDSilvano AndradeAinda não há avaliações

- FORMAS DE REPRESENTAÇÃO DE CONHECIMENTODocumento6 páginasFORMAS DE REPRESENTAÇÃO DE CONHECIMENTOxth1Ainda não há avaliações

- Aula 3 Arquiteturas Microcontroladores e Microprocessadores PDFDocumento24 páginasAula 3 Arquiteturas Microcontroladores e Microprocessadores PDFAllas JonyAinda não há avaliações

- Acessando e configurando OLT IntelbrasDocumento19 páginasAcessando e configurando OLT IntelbrasJilvan jilAinda não há avaliações

- Arduino Básico - Conceitos e aplicações do microcontrolador ATmegaDocumento42 páginasArduino Básico - Conceitos e aplicações do microcontrolador ATmegaMozart ÁvilaAinda não há avaliações

- Franquias TelecelulaDocumento29 páginasFranquias TelecelulaRaul LimaAinda não há avaliações

- GUIA PROGRAMAÇÃO ESPÍRITO V3.10Documento9 páginasGUIA PROGRAMAÇÃO ESPÍRITO V3.10JonnhyAinda não há avaliações

- A Tic Tecnologia Da Informacao e Comunicacao Na EducacaoDocumento32 páginasA Tic Tecnologia Da Informacao e Comunicacao Na EducacaoEnio LucioAinda não há avaliações