Escolar Documentos

Profissional Documentos

Cultura Documentos

VHDL Slutions To Problems

Enviado por

InarajTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

VHDL Slutions To Problems

Enviado por

InarajDireitos autorais:

Formatos disponíveis

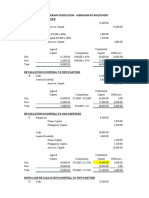

Paul Rajani Lassen E2DSD 19-05-2014

Exercises 5-8

1

Contents

Contents ........................................................................................................................................................ 1

Exercise 5 ........................................................................................................................................................... 2

Process Statements ....................................................................................................................................... 2

Question 1 ................................................................................................................................................. 2

Question 2 ................................................................................................................................................. 2

Question 3 ................................................................................................................................................. 3

Question 4 ................................................................................................................................................. 4

Binary to 7-segment hexadecimal with case statement. ........................................................................... 5

Question 1 ................................................................................................................................................. 5

Question 2 ................................................................................................................................................. 6

Guess a Hex Number Game. .......................................................................................................................... 6

Question 1 ................................................................................................................................................. 6

Question 2 ................................................................................................................................................. 8

Question 3 ................................................................................................................................................. 9

8 input NAND using the for loop .............................................................................................................. 11

Question 1 ............................................................................................................................................... 11

Count 1 using the for loop ...................................................................................................................... 11

Question 1 ............................................................................................................................................... 11

Exercise 6 ......................................................................................................................................................... 13

Counter one digit. ..................................................................................................................................... 13

Question 1 ............................................................................................................................................... 13

Watch six digits. ........................................................................................................................................ 14

Question 1 ............................................................................................................................................... 14

Question 2 ............................................................................................................................................... 15

Question 3 ............................................................................................................................................... 16

Alarm Watch ................................................................................................................................................ 17

Question 1 ................................................................................................................................................... 17

Exercise 7 ......................................................................................................................................................... 19

MeeMoo State Machine .............................................................................................................................. 19

Question 1 ............................................................................................................................................... 19

Paul Rajani Lassen E2DSD 19-05-2014

Exercises 5-8

2

Exercise 5

Process Statements

Question 1

Write a behavioural style description of the logic circuit below. The description must have a

separate process corresponding to each gate in the logic diagram. Each process must consist

of a single sequential signal assignment statement.

Figure1ThelogiccircuittobecodedinVHDL

One process was used per gate (ag for the and gate and og for the or gate).

Figure2VHDLcodeforthelogiccircuitinFigure1

Question 2

Perform a functional simulation to verify the correctness of the design.

Paul Rajani Lassen E2DSD 19-05-2014

Exercises 5-8

3

Figure3FunctionalSimulationofthelogiccircuitfromFigure1

The functional simulation agrees with the logic circuit.

Question 3

Given the truth table below, write a component that accomplishes the function defined by

the truth table below. Use a behavioural style architecture that consists of two processes, one

to assign a value to x and the other to assign a value to y.

Figure4TruthTabletobecodedinVHDL

Paul Rajani Lassen E2DSD 19-05-2014

Exercises 5-8

4

Figure5VHDLcodeforthetruthtableinFigure4

Question 4

Perform a functional simulation to verify the correctness of the design.

Figure6TheFunctionalsimulationofthecodefromFigure5mirrorsthetruthtableofFigure4

Paul Rajani Lassen E2DSD 19-05-2014

Exercises 5-8

5

Binary to 7-segment hexadecimal with case statement.

Question 1

Design a Binary to 7-segment hexadecimal converter using the case statement. The bit

pattern for 0-9 is practically the same as in exercise 4 with the exception of the number 6

which should be changed so it does not look like the letter b. Add the A-F letters, of you

own design, to the converter.

Figure7Binaryto7-segmenthexadecimalconverterVHDLcode

Paul Rajani Lassen E2DSD 19-05-2014

Exercises 5-8

6

Question 2

With all of the switches set (1111) the 7-segment display displays F

Guess a Hex Number Game.

The guess game is basically a game, where the player should guess a target number. After the

player trys out a guess, the player gets information about if the guess is right or lower/higher than

the target number. Because we have not learned about registers we can not count how many turns

have been used to guess the numbers (next lecture stuff). Furthermore we are still not able to

generate a random number, so we will have to set the target number manually.

Question 1

Design a guess game with the following functionality.

1.) When no key is asserted, the corresponding input number is shown on the 7-segments.

2.) When set is asserted the current input number is stored as the target number to be guessed

3.) When show is asserted the stored target number is shown on the 7 segments

4.) When try is asserted the guess is evaluated and Lo, Hi or is displayed depending

on if the guess is: higher, lower or equal to the target number.

Paul Rajani Lassen E2DSD 19-05-2014

Exercises 5-8

7

Figure 8 VHDL code for the guess game

Paul Rajani Lassen E2DSD 19-05-2014

Exercises 5-8

8

Question 2

Download and test the design on the DE2 board, are any latches generated in the RTL

viewer? If so - why?

The images above show a user choosing a value (fa) setting it, making sure that it is set (--) and then trying

to check a value higher than fa.

Paul Rajani Lassen E2DSD 19-05-2014

Exercises 5-8

9

There are 19 latches. This is due to having many places in the code where information is temporarily stored.

Figure 9 RTL diagram of the Guess game

Question 3

Extend the design to at two-player game with two instances of the GuessGame(meaning

dont change GuessGame) plus some additional behavioural code. Download and test the

design on the DE2 board using SW[17] to switch back and forth between player 1 and

player 2 and display the current player number on HEX3.

Paul Rajani Lassen E2DSD 19-05-2014

Exercises 5-8

10

Figure 10 VHDL code for the 2 player guessing game.

In the above image, the 2 on the left indicates that it is player 2 currently playing. The CF indicate the

current state of the switches.

Paul Rajani Lassen E2DSD 19-05-2014

Exercises 5-8

11

8 input NAND using the for loop

Question 1

Write a behavioural style component that uses a for loop to describe an eight-input NAND gate,

illustrated below. Perform a functional simulation to verify the correctness of the design.

Figure 11 VHDL code for the NAND gate using a for loop

Figure 12 Functional Simulation of the NAND gate

To do a full functional simulation there would be 256 values for input. Quartas Simulation Waveform

Editor is too messy for that, so 9 rather arbitrary values were chosen, while the last one was deliberately

chosen because it is the one case where the NAND gate is supposed to change its state.

Count 1 using the for loop

Question 1

Write a behavioural style component that uses a for loop to count the number of 1

occurring at the input and display it on the 7-segment output. Download and test the design

on the DE2 board

Paul Rajani Lassen E2DSD 19-05-2014

Exercises 5-8

12

Figure 13 VHDL code for the '1' counter

The 8 sensitive switches were set alternating between high and low, 4 up and 4 down.

Paul Rajani Lassen E2DSD 19-05-2014

Exercises 5-8

13

Exercise 6

Counter one digit.

Question 1

Design a binary circular counter (returns to zero after reaching maximum value) that

increments every positive edge of the CLK. Display the current counter value on the 7-

segment display. Use the 7-segment decoder component from former exercises.

Figure 14 VHDL code for the counter

Paul Rajani Lassen E2DSD 19-05-2014

Exercises 5-8

14

After counting up to the maximum the counter resets and sets COUT high.

After one button press, the counter increments, COUT is set to low and BIN_VAL is set to 0001, which

due to a pin assignment error appears mirrored.

Watch six digits.

Question 1

Design a new component called watch containing a clockGen component that generates a

one clock width pulse. The pulse is generated every second when SPEED is 1 and every 5

milliseconds when SPEED is 0. Connect the CLK_OUT output of the clockGen to the

CLK input of the multiCounter component. CLOCK_50 is found in the pin assignment and

is a 50 MHz 50% duty cycle clock. /RESET must be an active low asynchronous reset.

HI NT: use a variable integer type in the clockGen component for the counter and set

CLK_OUT high every time the counter reaches 50.000.000 - otherwise the CLK_OUT

should be set to low.

Paul Rajani Lassen E2DSD 19-05-2014

Exercises 5-8

15

Figure 15 VHDL code for the clockGen component

Figure 16 Architecture of the 'Watch' entity. Note that the CLK_OUT from clockGen goes directly into the CLK of the One digit

counter, via the signal i_clk

Question 2

Download and test the design on the DE2 board

The DE2 board counts once per second, respecting the maximums from the one digit count in all

modes.

Paul Rajani Lassen E2DSD 19-05-2014

Exercises 5-8

16

Question 3

Extend the design with 6 cascade coupled instances of the multiCounter component, so it

will end up as a 6 digit 24 hours clock (eg.. ::). Refer to the drawing on the next page

for design inspiration. Use the BI N_VAL, from the hour counters, output to RESET all

counters to :: when they hits . Leave the rest of BI N_VAL unconnected. This can

be done by using the open keyword in the port mapping (eg. BIN_VAL => open).

Figure 17 VHDL Code for the 24 Hour Watch. It is made up of 6 chained One digit counters and a clockGen

This clock ticks once a second and goes from 00:00:00 until 23:59:59 after which the time is reset to

00:00:00

Paul Rajani Lassen E2DSD 19-05-2014

Exercises 5-8

17

Alarm Watch

Question 1

Extend the watch component with an alarm feature with a one minute resolution (meaning:

only hours and minutes can be set). Use the BI N_VAL output from the counters to detect an

alarm.

Although these two images look as though they were taken 22 seconds apart, they were in fact taken

only seconds apart. The upper image shows what the alarm was set to, while the lower image shows

the time. Note the red ALARM! light.

Paul Rajani Lassen E2DSD 19-05-2014

Exercises 5-8

18

Figure 18 VHDL code for the Alarm Watch

Paul Rajani Lassen E2DSD 19-05-2014

Exercises 5-8

19

Exercise 7

MeeMoo State Machine

Question 1

Implement the state-diagram for the MeeMoo state machine illustrated below using the three process

template in the book. The diagram has both Moore and Mealy outputs with conditional and

unconditional transitions. In other words: if you can solve this exercise you will actually be able to

implement VHDL code for both state machine types.

Figure 19 VHDL code for the MeeMoo state machine, utilising the three process template

Paul Rajani Lassen E2DSD 19-05-2014

Exercises 5-8

20

Question 2

Figure 20 Functional Simulation of the MeeMoo state machine

Notice that with the exception of an asynchronous reset the Moore output only changes at the positive

edge of the next clock, regardless of changing inputs. The Mealy outputs can change within a clock cycle, if

the input changes before the next clock cycle. This can also be easily demonstrated by getting to the init

state and flipping SW[1] while SW[0] is high. (No pictures were added because there is not much to see on

the DE2 board in this case.

Code Lock

The code lock accepts a sequence of three correct codes, each followed by an enter press, to let the

lock output change from locked (1) to unlocked (0). The code lock remains unlocked until enter

is pressed again. Three wrongly entered codes will lock the code lock permanently until reset is

asserted.

In solving the exercise you must explain in text how the listed SysML terms correspond to

Moore/Mealy terms and explain how they can be implemented in VHDL using snippets from your code:

SysML triggers, guards and effects (no effects in exercise)

SysML do actions

SysML entry actions (err_cnt++ in Wrong Code)

SysML exit action (None in the exercise)

Note that entry- and exit actions are properties of a state, but can also be interpreted as common

effects on the in- and outgoing transitions.

Paul Rajani Lassen E2DSD 19-05-2014

Exercises 5-8

21

Paul Rajani Lassen E2DSD 19-05-2014

Exercises 5-8

22

Figure 21 VHDL Code for CodeLock

Even though this code resembles a Moore state machine, there are many elements of SysML state

machines. To change from state to state in SysML there need to be triggers, guards and (to a lesser extent

effects). There are triggers and guards in this Moore state machine, just under different names. In this case

Paul Rajani Lassen E2DSD 19-05-2014

Exercises 5-8

23

the trigger is a key press. For Mealy and Moore state machines these are simply called inputs. The guards in

SysML are simply achieved here by if and when statements. Although there are no effects in this exercise

they do also occur in Mealy diagrams, as the output. In that case the trigger is usually a change of the

inputs and the effect is an immediate change in the output (and possibly a state change.

Do actions in SysML are what occur within a state. These are simplest in Moore diagrams, where the do

statement is the output, as seen in lines 82-90.

Entry actions in SysML occur as a new state is entered into. Lines 61and 62 are examples of this. As w state

wrongCode is entered into, err_cnt is incrementally increased, but only on entry, not passively while

waiting within wrongCode. That would be a do action.

An exit action is very similar to an entry action, but, as its name suggests, it happens as a state is left.

Exercise 8

A simple procedure and function

Question 1 and 2

Design the component illustrated below and download it on the DE2 board.

Make the procedures and functions visible for all components in the project by

encapsulating the functions and procedures into a package. Download and test the new

design on the DE2 board.

Figure 22 A Package containg an xor function and an and/or procedure

Paul Rajani Lassen E2DSD 19-05-2014

Exercises 5-8

24

Figure 23 The "Main" program or top level entity

On the left SW[1] (b) and SW[0](a) are both high on the right SW[1] is high and SW[2] is low.

LEDR0 = a xor b

LEDR1 = a and b

LEDR2 = a or b

The Italian flag on VGA

I was unable to test this due to time constraints and poor management on my part, but I went as far as I

could without a monitor including the reverse engineering and creating the sync generator class.

Question 1

Reverse engineer the template project and make sure you understand how the template

works. Write a brief description in your documentation. You can read about VGA in the

DE2 user manual page 38-39.

Paul Rajani Lassen E2DSD 19-05-2014

Exercises 5-8

25

The Template starts by declaring the entity and the incoming and outgoing signals. It goes on to

define many constants which have to do with screen size and synchronization. This is done for both

horizontal and vertical.

It goes on to define one process for halving the clock frequency and two more, one for horizontal

sync and one for vertical sync, before trying to draw out green white and red stripes, vertically

down the screen.

Question 2

Looking at the declarations made at the beginning of the architecture, we can see that most are natural

constants, while syncOut and blankout are outgoing.

Você também pode gostar

- Research Proposal: Herbal Leaves Identification AppDocumento4 páginasResearch Proposal: Herbal Leaves Identification AppMary Jane PagayAinda não há avaliações

- Introduction To ProModelDocumento82 páginasIntroduction To ProModelVoni Meistherson100% (1)

- Assignment MethodDocumento17 páginasAssignment MethodMa-an MaromaAinda não há avaliações

- Adversarial Search: Course: Artificial Intelligence Effective Period: September 2018Documento35 páginasAdversarial Search: Course: Artificial Intelligence Effective Period: September 2018wizyjckoAinda não há avaliações

- Arduino 110901051202 Phpapp01Documento41 páginasArduino 110901051202 Phpapp01rbenseghierAinda não há avaliações

- Summative Assessment-Partnership Dissolution - Admission by InvestmentDocumento10 páginasSummative Assessment-Partnership Dissolution - Admission by InvestmentAllondra DapengAinda não há avaliações

- Capital Structure TheoryDocumento8 páginasCapital Structure TheoryAshirbad Kundu100% (1)

- LAB 3 - Verilog For Combinatorial Circuits: GoalsDocumento7 páginasLAB 3 - Verilog For Combinatorial Circuits: GoalsJoey WangAinda não há avaliações

- 7 SegmentDocumento14 páginas7 SegmentTudor CiotloșAinda não há avaliações

- Parity Checker and GeneratorDocumento8 páginasParity Checker and GeneratoranjusmAinda não há avaliações

- Rabadon FirstVHDLDocumento16 páginasRabadon FirstVHDLChristian RabadonAinda não há avaliações

- Rechie Jhon Relator Alyounous Ibrahim Rene Ray Duran Mark Anthony JavierDocumento2 páginasRechie Jhon Relator Alyounous Ibrahim Rene Ray Duran Mark Anthony JavierMark Anthony JAVIERAinda não há avaliações

- AY2021-2022, S2, EEEB1041 Project v2Documento3 páginasAY2021-2022, S2, EEEB1041 Project v2Pavahaariny KathegesenAinda não há avaliações

- Department of Electrical Engineering: Lab 07: Design A Display System of A Rolling DiceDocumento4 páginasDepartment of Electrical Engineering: Lab 07: Design A Display System of A Rolling DiceEisha FatimaAinda não há avaliações

- WebSphere® Development Studio ILE RPG Reference SummaryDocumento78 páginasWebSphere® Development Studio ILE RPG Reference SummaryJeremy SerratoAinda não há avaliações

- FPGA Lab Journal 11032022 104353amDocumento98 páginasFPGA Lab Journal 11032022 104353amAFTAB ALIAinda não há avaliações

- Jasim Abbasi Uppgift Engineering Job BDocumento36 páginasJasim Abbasi Uppgift Engineering Job BManieAinda não há avaliações

- CSE369 Lab6 Wi22Documento4 páginasCSE369 Lab6 Wi22Deniz Melek TürkAinda não há avaliações

- 7-Segment Display Interfacing and Programming - Embedded Club 4 UDocumento8 páginas7-Segment Display Interfacing and Programming - Embedded Club 4 UManish Kumar VermaAinda não há avaliações

- Assignment 7Documento2 páginasAssignment 7NeeleswarAinda não há avaliações

- Lab1 DocDocumento14 páginasLab1 DocThanos GkanAinda não há avaliações

- Lab 08Documento17 páginasLab 08salloum18Ainda não há avaliações

- Lab 21Documento12 páginasLab 21mithila_aloAinda não há avaliações

- Sir Syed CASE Institute of Technology, Islamabad: Digital System Design LabDocumento9 páginasSir Syed CASE Institute of Technology, Islamabad: Digital System Design LabIrfan HaiderAinda não há avaliações

- Lab 5Documento8 páginasLab 5robertoAinda não há avaliações

- CSE20221 Keyboard Interface ProjectDocumento2 páginasCSE20221 Keyboard Interface ProjectpranjalAinda não há avaliações

- Lab 4Documento5 páginasLab 402chng.jiadeAinda não há avaliações

- 1 Data (7 Points) : Img Cv2.imreadDocumento2 páginas1 Data (7 Points) : Img Cv2.imreadVictor CanoAinda não há avaliações

- CSE369 Lab1&2 Wi22Documento5 páginasCSE369 Lab1&2 Wi22Deniz Melek TürkAinda não há avaliações

- FPGA-Based-System-Design LAB JOURNAL 2Documento56 páginasFPGA-Based-System-Design LAB JOURNAL 2talha42103Ainda não há avaliações

- Lab - 8, Implementation of Combinational Circuits Using VHDL Design EntryDocumento18 páginasLab - 8, Implementation of Combinational Circuits Using VHDL Design EntrySeif-El-Islam BayAinda não há avaliações

- Rabadon Excercises No1Documento24 páginasRabadon Excercises No1Christian RabadonAinda não há avaliações

- Lab 2Documento10 páginasLab 2zagarzusemAinda não há avaliações

- Lab 5Documento5 páginasLab 5Syed Junaid IqbalAinda não há avaliações

- CSE369 Lab4 Wi22Documento4 páginasCSE369 Lab4 Wi22Deniz Melek TürkAinda não há avaliações

- Arduino and 7 Segment LEDDocumento5 páginasArduino and 7 Segment LEDAnonymous h2VaB0Ainda não há avaliações

- Final DDCOLab ManualDocumento31 páginasFinal DDCOLab Manualsusheela NatarajuAinda não há avaliações

- Lab2 ManualDocumento13 páginasLab2 ManualAbdul JabbarAinda não há avaliações

- 281 Final Project - Eli and BaylorDocumento18 páginas281 Final Project - Eli and Baylorapi-696541991Ainda não há avaliações

- Beginning FPGA Programming - Partie74Documento5 páginasBeginning FPGA Programming - Partie74ali alilouAinda não há avaliações

- Ex - No 7 Interfacing-Seven-Segment-DisplayDocumento7 páginasEx - No 7 Interfacing-Seven-Segment-DisplaytdsuresheeeAinda não há avaliações

- Fall 2020 Lab 5Documento9 páginasFall 2020 Lab 5R BagriAinda não há avaliações

- Lab 7Documento9 páginasLab 7zaqAinda não há avaliações

- Lab Report #2Documento9 páginasLab Report #2Noura MDAinda não há avaliações

- CSE369 Lab5 Wi22Documento6 páginasCSE369 Lab5 Wi22Deniz Melek TürkAinda não há avaliações

- DLD Lab Report 07Documento11 páginasDLD Lab Report 07Muneeb ahmadAinda não há avaliações

- R I J Type DatapathDocumento4 páginasR I J Type Datapathprasad357Ainda não há avaliações

- Calculator 1Documento39 páginasCalculator 1RatnakarVarunAinda não há avaliações

- CSE369 Lab7 Wi22Documento5 páginasCSE369 Lab7 Wi22Deniz Melek TürkAinda não há avaliações

- Lab1 ReportDocumento5 páginasLab1 ReportLukeAinda não há avaliações

- Introduction To Logic Circuits Lab #7 - Combinational Logic Design 3 (Discrete Parts)Documento2 páginasIntroduction To Logic Circuits Lab #7 - Combinational Logic Design 3 (Discrete Parts)Cepheid FaarjanaAinda não há avaliações

- CSE370 Laboratory Assignment 8Documento5 páginasCSE370 Laboratory Assignment 8Alexaa AAinda não há avaliações

- Experiment8 Student1Documento14 páginasExperiment8 Student1Nicholas ThomasAinda não há avaliações

- "Pong" The Game, Implemented On An Altera Flex EPF10K70CR240-4 FPGADocumento18 páginas"Pong" The Game, Implemented On An Altera Flex EPF10K70CR240-4 FPGAminhmendAinda não há avaliações

- Digital Logic Design - CS302 Spring 2005 Mid Term PaperDocumento4 páginasDigital Logic Design - CS302 Spring 2005 Mid Term PaperRameen QureshiAinda não há avaliações

- Practica5 - Resultados Digital SystemsDocumento4 páginasPractica5 - Resultados Digital SystemslaramecaAinda não há avaliações

- DLD Lab Report 08Documento9 páginasDLD Lab Report 08Muneeb ahmadAinda não há avaliações

- Lab Manual No 15Documento6 páginasLab Manual No 15ThoughtsAinda não há avaliações

- FCDS 2019 V1Documento33 páginasFCDS 2019 V1Kannan KannanAinda não há avaliações

- AVR Assembler User GuideDocumento26 páginasAVR Assembler User Guidewm53100% (1)

- CambodiaDocumento3 páginasCambodiaInarajAinda não há avaliações

- Amazon DeforestationDocumento4 páginasAmazon DeforestationInarajAinda não há avaliações

- Monicas SuperkageDocumento1 páginaMonicas SuperkageInarajAinda não há avaliações

- NCS Dummy - Taking The Expert Out of NCS Expert: FSW - PSW - TRC Nettodat - TRCDocumento48 páginasNCS Dummy - Taking The Expert Out of NCS Expert: FSW - PSW - TRC Nettodat - TRCКонстантин ШпакAinda não há avaliações

- MT3337 Platform NMEA Message Specification V1.00Documento46 páginasMT3337 Platform NMEA Message Specification V1.00Dejan SpasovskiAinda não há avaliações

- Python Data Representation Notes.Documento14 páginasPython Data Representation Notes.Husain NalwalaAinda não há avaliações

- EEE 3115/CSE237: Digital Electronics / DPTDocumento18 páginasEEE 3115/CSE237: Digital Electronics / DPTWho AmAinda não há avaliações

- CS8261-C Programming Lab - by LearnEngineering - inDocumento68 páginasCS8261-C Programming Lab - by LearnEngineering - inbiniAinda não há avaliações

- Computer Notes KLB F3Documento117 páginasComputer Notes KLB F3dzelbabuAinda não há avaliações

- VU-Assignment CS101Documento3 páginasVU-Assignment CS101mc220203866 JAWAD SARWARAinda não há avaliações

- EC 8392 Digital ElectronicsDocumento46 páginasEC 8392 Digital Electronicspadmaa1Ainda não há avaliações

- Java Important Programs ICSEDocumento13 páginasJava Important Programs ICSEAnmol AgarwalAinda não há avaliações

- PWP Notes (Chapter Wise)Documento123 páginasPWP Notes (Chapter Wise)NIKOLA100% (1)

- EDC15PSuite ManualDocumento31 páginasEDC15PSuite Manuallampropeltis71% (7)

- Export CDR Data For Further AnalysisDocumento4 páginasExport CDR Data For Further AnalysisOchie RomeroAinda não há avaliações

- Python 2 Python 3Documento4 páginasPython 2 Python 3Shubham Sati100% (1)

- Inovance H0u PLC Manual English 20 4 20Documento56 páginasInovance H0u PLC Manual English 20 4 20Ngọc NhấtAinda não há avaliações

- Lakshya Rautela 12-B CS Pratical FileDocumento34 páginasLakshya Rautela 12-B CS Pratical Filelakshya rautelaAinda não há avaliações

- Lyla B Das 0 & 1 PDFDocumento53 páginasLyla B Das 0 & 1 PDFAnkit Sethia100% (4)

- Section 2 Microprocessors Course Dr. S.O.Fatemi By: Mahdi HassanpourDocumento77 páginasSection 2 Microprocessors Course Dr. S.O.Fatemi By: Mahdi HassanpoursivnathAinda não há avaliações

- Unicode UTF 8 Character TableDocumento8 páginasUnicode UTF 8 Character TablePravin K PatelAinda não há avaliações

- WREG Register in Pic Microcontroller Assembly LanguageDocumento11 páginasWREG Register in Pic Microcontroller Assembly LanguageDenzel TajoAinda não há avaliações

- The Servant For The Commodore 128Documento66 páginasThe Servant For The Commodore 128Thomas Conté100% (4)

- Practical Lab 1Documento11 páginasPractical Lab 1Vishal KumarAinda não há avaliações

- Programming With Mobiflight & Prosim - The SimDocumento1 páginaProgramming With Mobiflight & Prosim - The Simbondomargalitadze margalitadzeAinda não há avaliações

- SwiftDocumento463 páginasSwiftimtoaekqAinda não há avaliações

- Programmable Logic Controller PLCDocumento53 páginasProgrammable Logic Controller PLCokk chuAinda não há avaliações

- Grade 10 - Unit 03Documento3 páginasGrade 10 - Unit 03AsmaAinda não há avaliações

- ARM AssyLangDocumento156 páginasARM AssyLangxuanvinhspktvlAinda não há avaliações

- Microprocessor 8086 Lecture 1 by Ayad M.KwadDocumento31 páginasMicroprocessor 8086 Lecture 1 by Ayad M.KwadAyad M Al-AwsiAinda não há avaliações

- Microprocessor System Syllabus OBEDocumento7 páginasMicroprocessor System Syllabus OBEGilCuajuncoAinda não há avaliações

- Conversionworksheet PDFDocumento2 páginasConversionworksheet PDFGustavo FerreiraAinda não há avaliações

- Divided by Two Least-Significant BitDocumento5 páginasDivided by Two Least-Significant BitMhaykan's DaughterAinda não há avaliações