Escolar Documentos

Profissional Documentos

Cultura Documentos

AND9075/D Understanding Data Eye Diagram Methodology For Analyzing High Speed Digital Signals

Enviado por

Hoàng Việt Cường0 notas0% acharam este documento útil (0 voto)

30 visualizações7 páginasData eye diagram allows key parameters of the electrical quality of the signal to be quickly visualized and determined. Data eye diagram is constructed from a digital waveform by folding the parts of the waveform corresponding to each individual bit into a single graph. Real world high speed digital signals suffer significant impairments including attenuation, noise, crosstalk, etc.

Descrição original:

Título original

AND9075-D

Direitos autorais

© © All Rights Reserved

Formatos disponíveis

PDF, TXT ou leia online no Scribd

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoData eye diagram allows key parameters of the electrical quality of the signal to be quickly visualized and determined. Data eye diagram is constructed from a digital waveform by folding the parts of the waveform corresponding to each individual bit into a single graph. Real world high speed digital signals suffer significant impairments including attenuation, noise, crosstalk, etc.

Direitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato PDF, TXT ou leia online no Scribd

0 notas0% acharam este documento útil (0 voto)

30 visualizações7 páginasAND9075/D Understanding Data Eye Diagram Methodology For Analyzing High Speed Digital Signals

Enviado por

Hoàng Việt CườngData eye diagram allows key parameters of the electrical quality of the signal to be quickly visualized and determined. Data eye diagram is constructed from a digital waveform by folding the parts of the waveform corresponding to each individual bit into a single graph. Real world high speed digital signals suffer significant impairments including attenuation, noise, crosstalk, etc.

Direitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato PDF, TXT ou leia online no Scribd

Você está na página 1de 7

Semiconductor Components Industries, LLC, 2012

March, 2012 Rev. 0

1 Publication Order Number:

AND9075/D

AND9075/D

Understanding Data Eye

Diagram Methodology for

Analyzing High Speed

Digital Signals

Introduction

The data eye diagram is a methodology to represent and

analyze a high speed digital signal. The eye diagram allows

key parameters of the electrical quality of the signal to be

quickly visualized and determined. The data eye diagram is

constructed from a digital waveform by folding the parts of

the waveform corresponding to each individual bit into a

single graph with signal amplitude on the vertical axis and

time on horizontal axis. By repeating this construction over

many samples of the waveform, the resultant graph will

represent the average statistics of the signal and will

resemble an eye. The eye opening corresponds to one bit

period and is typically called the Unit Interval (UI) width of

the eye diagram. An ideal digital waveform with sharp rise

and fall times and constant amplitude will have an eye

diagram as shown in Figure 1 below.

Figure 1. Ideal High Speed Digital Signal with Eye Diagram

Obviously, this ideal eye diagram offers little additional

information beyond the time domain waveform display.

Real world high speed digital signals suffer significant

impairments including attenuation, noise, crosstalk, etc. The

data eye diagram for a typical high speed digital signal is

shown in Figure 2 below. Notice how the diagram more

resembles the shape of an eye.

http://onsemi.com

APPLICATION NOTE

AND9075/D

http://onsemi.com

2

Figure 2. Typical High Speed Digital Signal with Eye Diagram

Data Eye Diagram Fundamentals

High Speed Digital Signaling

Digital signaling is the transmission of baseband data over

a cabled connection. This data is usually modulated or coded

according to the telecommunication protocol set as a

standard for the intended interface. The type of baseband

coding (commonly called Line Coding) chosen for a

standard best optimizes performance, given the electrical

characteristics of the data and the transport medium. Legacy

highspeed digital standards including USB 1.1/2.0 use a

form of nonreturn to zero (NRZ) for the data coding where

a high (positive) pulse represents a logic one and a low

(negative) pulse a logic zero. By controlling the data format

(i.e., bit stuffing, etc) to make the number of ones and zeros

equal, NRZ waveforms can be DC balanced and limit the DC

content in the signal. This allows the signal to be

capacitively (or AC) coupled and also provides common

mode voltages or DC power to be combined with the signal

on the same cable.

Baseband coding using returntozero (RZ) signaling is

usually not used on highspeed digital interfaces because it

has excessive bandwidth requirements due to its inherent

DC imbalance which in turn adds significant DC content.

Besides controlling DC content and bandwidth, data

formatting can also enable clock recovery for the high speed

signal. For reliable clock recovery at the receiver, the

maximum number of consecutive ones or zeros needs to be

bounded to a reasonable number since the waveform clock

is recovered by observing transitions in the received

sequence. A common method to bound the number of ones

and zeros in a waveform is to use 8b/10b encoding. 8b/10b

is a line code that maps 8bit symbols to 10bit symbols to

provide DCbalance for the waveform and also provide

enough state changes to allow reasonable clock recovery.

After line coding, the signal is put through a physical

channel. The linecoded signal can either be directly put on

a transmission line or can be level shifted and pulse shaped

to reduce its bandwidth, improve EMI/RFI performance or

match system interfacing requirements. Low Voltage

Differential Signaling (LVDS) is a commonly used interface

standard for high speed digital signals. By providing a

relatively small signal amplitude and tight electric and

magnetic field coupling between the two differential lines,

LVDS significantly reduces the amount of radiated

electromagnetic noise and power lost to conductor

resistance.

Eye Diagram Basics

As stated previously, the data eye diagram is a

representation of a high speed digital signal that allows key

parameters of the electrical quality of a signal to be quickly

visualized and determined. The requirements for high speed

AND9075/D

http://onsemi.com

3

data signals mentioned in the previous section are some of

the key metrics that can be measured using eye diagrams.

Eye Diagrams are used to characterize a high speed signal

source or transmitter (receiver testing usually requires bit

error rate testing). A typical eye diagram test setup is shown

in figure 3 below.

DUT

Oscilloscope

Pulse Generator

Data

Clock

Figure 3. Eye Diagram Test Setup

The Pulse Generator is required to generate a random bit

pattern since the eye diagram is a statistical average of many

thousands or even millions of samples of a waveform. The

pattern required for a particular data standard is defined by

the protocol and is usually a pseudorandom bit sequence of

hundreds or thousands of bits. The high speed sampling

oscilloscope has a typical bandwidth of 10 to 25 GHz in

order to capture the full characteristics of the waveform.

Using the persistence mode of the oscilloscope, the

superstition of millions of timedomain waveforms can be

displayed.

A representative eye diagram is shown below along with

some of the typical measurements that can be performed on

the diagram.

Figure 4. Typical Eye Diagram Measurements

All of the measurement results are the statistical average

of the samples of the waveform at the point shown. The

measurements are defined as follows:

One Level

The one level in an eye pattern is the mean value of a logic

one. The actual computed value of the one level comes from

the histogram mean value of all the data samples captured

inside the middle 20% (40 to 60% points) of the eye period.

Zero Level

The zero level in an eye pattern is the mean value of a logic

zero. The zero level is computed from the same 40 to 60%

AND9075/D

http://onsemi.com

4

region of the baseline area during the eye period as the one

level.

Eye Amplitude

Eye amplitude is the difference between the one and zero

levels. The data receiver logic circuits will determines

whether a received data bit is a 0 or 1, based on the eye

amplitude.

Eye Height

Eye height is a measure of the vertical opening of an eye

diagram. An ideal eye opening measurement would be equal

to the eye amplitude measurement. For a real eye diagram

measurement, noise on the eye will cause the eye to close.

As a result, the eye height measurement determines the eye

closure due to noise. The signal to noise ratio of the high

speed data signal is also directly indicated by the amount of

eye closure.

Eye Crossing Percentage

The crossing level is the mean value of a thin vertical

histogram window centered on the crossing point of the eye

diagram. The eye crossing percentage is then calculated

using the following equation:

Eye Crossing % = 100 * [(crossing level zero level)/(one

level zero level)]

Eye crossing percentage gives an indication of duty cycle

distortion or pulse symmetry problems in the high speed

data signal. Figure 5 below shows an example of a waveform

with bad pulse symmetry (shown left) with the resultant eye

diagram with eye crossing of 75% (shown right). Eye

crossing percentage is valuable for measuring amplitude

distortions caused by differences in the one and zerolevel

durations. It also reveals pulse symmetry problems for

diagnosis. When the eye crossing symmetry value deviates

from the perfect 50% point, the eye closes and thus the

electrical quality of the signal is degraded.

Figure 5. Waveform and resultant eye diagram with 75% eye crossing percentage

Bit Period

The bit period is a measure of the horizontal opening of an

eye diagram at the crossing points of the eye and is usually

measured in picoseconds for a high speed digital signal (i.e.,

200 ps is used for a 5Gbps signal). The data rate is the inverse

of bit period (1 / bit period). The bit period is commonly

called the Unit Interval (UI) when describing an eye

diagram. The advantage of using UI instead of actual time

on the horizontal axis is that it is normalized and eye

diagrams with different data rates can be easily compared.

Eye Width

Eye width is a measure of the horizontal opening of an eye

diagram. It is calculated by measuring the difference

between the statistical mean of the crossing points of the eye.

Rise Time

Rise time is a measure of the mean transition time of the

data on the upward slope of an eye diagram. The

measurement is typically made at the 20 and 80 percent or

10 and 90% levels of the slope.

Fall Time

Fall time is a measure of the mean transition time of the

data on the downward slope of an eye diagram. The

measurement is typically made at the 20 and 80 percent or

10 and 90 percent levels of the slope.

Jitter

Jitter is the time deviation from the ideal timing of a

databit event and is perhaps one of the most important

characteristics of a high speed digital data signal. To

compute jitter, the time deviations of the transitions of the

rising and falling edges of an eye diagram at the crossing

point are measured. Fluctuations can be random and/or

deterministic. The time histogram of the deviations is

analyzed to determine the amount of jitter. The pp jitter is

defined as the full width of the histogram, meaning all data

points present. RMS jitter is defined as the standard

deviation of the histogram. The units for a jitter

measurement on a high speed digital signal are normally in

picoseconds.

AND9075/D

http://onsemi.com

5

Differential Signals and Differential Eye Pattern

Measurements

Differential signals offer superior noise immunity and

overall improved signal integrity, which is highly desirable

in the transmission and distribution of highspeed signals.

Techniques for conducting eye pattern measurements

involve using trace math operations to view these signals

both separately and as a pair. On a modern high speed

oscilloscope, eye and pulse pattern measurements can be

measured separately (Ch1 and Ch2) and with trace math

(Ch1 Ch2, Ch1 + Ch2). By examining and overlaying

measurements of the signal both separately and combined,

differential and common mode effects including skew

caused by common mode imbalance and noise can be

determined.

Eye Pattern Diagnostics and Mask Compliance

The quality of a high speed digital signal can be quickly

determined by using a compliance mask overlay on the eye

diagram display. A typical mask includes both time and

amplitude limits. An eye diagram with compliance masks is

shown in Figure 6 below.

Figure 6. Eye Diagram with Compliance Mask

In the above diagram, the gray block areas represent

keepout areas. In order to pass the mask compliance test,

the transmitter output must not have ANY samples fall

within the keepout regions.

The mask regions are defined as follows:

Top region: The maximum expected value. Voltages

exceeding this value will fail.

Middle Region: The size and shape of the eye diagram as

defined by the interface standard for the high speed digital

signal.

Bottom Region: The minimum expected value. Voltages

below this value will fail.

Lowest Capacitance Products for High Speed

Signal Quality

It is vital for high speed interfaces to maintain impedance

matching throughout the signal paths. Any traditional ESD,

surge or filter components added to the signal paths must

have minimum capacitance so the signal quality can be

maintained at the highest level. Todays highest speed

interfaces such as USB3.0, eSATAIII, HDMI, and

Thunderbolt require stringent capacitance limits for

external components added to the signal paths. ON

Semiconductor manufactures a wide line of ultralow

capacitance ESD protection devices for high speed

interfaces. Below is a partial list of the products.

ESD7004, ESD7016, ESD7008, MG2040

Figure 7 below shows an example of a data eye diagram

for USB3.0 interface without any ESD protection device

placed on the differential signal path. Immediately below

Figure 7, an eye diagram is shown using

ON Semiconductors ESD7016 as the ESD protection

device placed on the differential signal path. This eye

diagram shows that ESD7016 has minimum impact on the

data signal.

AND9075/D

http://onsemi.com

6

USB3.0 Data

Signal

USB3.0 Data

Signal Zoomed

In to Show Eye

Figure 7. USB3.0 Eye Diagram without ESD Protection

Figure 8. USB3.0 Eye Diagram with ONsemi ESD7016

Summary

As high speed digital signals exceed many gigabit per

second speeds, eye diagrams provide the means to quickly

and accurately measure signal quality and system

performance. ON Semiconductor understands the

capacitance constraints that designers are faced with when

using these high speed interfaces and offers a wide line of

ultralow capacitance ESD protection devices that service

these interfaces.

AND9075/D

http://onsemi.com

7

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice

to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability

arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.

Typical parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All

operating parameters, including Typicals must be validated for each customer application by customers technical experts. SCILLC does not convey any license under its patent rights

nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications

intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should

Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,

and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death

associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal

Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

PUBLICATION ORDERING INFORMATION

N. American Technical Support: 8002829855 Toll Free

USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81358171050

AND9075/D

Thunderbolt is trademark of Intel Corporation in the U.S. and/or other countries.

LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor

P.O. Box 5163, Denver, Colorado 80217 USA

Phone: 3036752175 or 8003443860 Toll Free USA/Canada

Fax: 3036752176 or 8003443867 Toll Free USA/Canada

Email: orderlit@onsemi.com

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local

Sales Representative

Você também pode gostar

- Arduino Measurements in Science: Advanced Techniques and Data ProjectsNo EverandArduino Measurements in Science: Advanced Techniques and Data ProjectsAinda não há avaliações

- AND9075/D Understanding Data Eye Diagram Methodology For Analyzing High Speed Digital SignalsDocumento7 páginasAND9075/D Understanding Data Eye Diagram Methodology For Analyzing High Speed Digital SignalsJohnJachersonAinda não há avaliações

- Aug 94 A 3Documento9 páginasAug 94 A 3Norazimah Mat ZainAinda não há avaliações

- How Analog-To-Digital Converters (ADCs) WorkDocumento6 páginasHow Analog-To-Digital Converters (ADCs) Workdiether.gozumAinda não há avaliações

- Advanced Calibration Techniques To Improve Extinction Ratio Measurement in DCA-X and DCA-MDocumento15 páginasAdvanced Calibration Techniques To Improve Extinction Ratio Measurement in DCA-X and DCA-MGordinhorsAinda não há avaliações

- High-Performance D/A-Converters: Application to Digital TransceiversNo EverandHigh-Performance D/A-Converters: Application to Digital TransceiversAinda não há avaliações

- EI Assignment 1 PDFDocumento6 páginasEI Assignment 1 PDFFirozAinda não há avaliações

- Lab ManualDocumento48 páginasLab ManualA'ziz MoAinda não há avaliações

- Iscas06 Random SamplingDocumento4 páginasIscas06 Random SamplingJaswinder Pal BehlAinda não há avaliações

- Simplifying HDMI 2.0 Source Impedance Measurements With A VNA-Based MethodologyDocumento4 páginasSimplifying HDMI 2.0 Source Impedance Measurements With A VNA-Based MethodologyArun KumarAinda não há avaliações

- 64 QAM Modulator Demodulator MatlabDocumento22 páginas64 QAM Modulator Demodulator MatlabAlexandru Dragos DimofteAinda não há avaliações

- Eye Diagram of Digital Baseband Received SignalsDocumento11 páginasEye Diagram of Digital Baseband Received Signalsgosala-kulupana-5193Ainda não há avaliações

- Intersymbol InterferenceincompleteDocumento21 páginasIntersymbol InterferenceincompleteEvan FebriantoAinda não há avaliações

- Working Principle of Digital Storage OscilloscopeDocumento4 páginasWorking Principle of Digital Storage OscilloscopeNihal KoriAinda não há avaliações

- Experiment 1 Familiarization With Laboratory Instruments: Oscilloscope, Function Generator, Digital Multimeter, and DC Power SupplyDocumento7 páginasExperiment 1 Familiarization With Laboratory Instruments: Oscilloscope, Function Generator, Digital Multimeter, and DC Power Supplypappuyadav1996Ainda não há avaliações

- 10step To A Perfect Digital DemodulationDocumento16 páginas10step To A Perfect Digital Demodulationbayman66Ainda não há avaliações

- Multi Controlled WheelchairDocumento7 páginasMulti Controlled WheelchairmafiaishotAinda não há avaliações

- AN10073 How To Setup A Real Time Oscilloscope To Measure JitterDocumento12 páginasAN10073 How To Setup A Real Time Oscilloscope To Measure JitterMOHSENAinda não há avaliações

- EEE 201 Assignment: Name: Ajibulu OluwadunsinDocumento11 páginasEEE 201 Assignment: Name: Ajibulu OluwadunsinJohn AlabiAinda não há avaliações

- Implementation of Doppler Radar: Executive SummaryDocumento7 páginasImplementation of Doppler Radar: Executive SummaryjatonfireAinda não há avaliações

- Poster SDI - Digital VideoDocumento2 páginasPoster SDI - Digital Videoreis00Ainda não há avaliações

- Basics of Analog-To-digital ConvertionDocumento9 páginasBasics of Analog-To-digital ConvertionThanh Nhan LeAinda não há avaliações

- Xyzs of Oscilloscopes: Vertical SystemDocumento7 páginasXyzs of Oscilloscopes: Vertical SystemBom_Jovi_681Ainda não há avaliações

- Data Acquisition SystemDocumento14 páginasData Acquisition SystemAditi Saha33% (3)

- 9 IndexDocumento25 páginas9 IndexbuturcasAinda não há avaliações

- Experiment04 Bandwidth-LimitingDocumento19 páginasExperiment04 Bandwidth-LimitingMary Rose P Delos SantosAinda não há avaliações

- Tofd Calibration: (8) : ChecksDocumento6 páginasTofd Calibration: (8) : ChecksLương Hồ Vũ0% (1)

- Dijagram OkaDocumento42 páginasDijagram OkaJelena CerovinaAinda não há avaliações

- EIT Exp 5 DSOscilloscopeDocumento17 páginasEIT Exp 5 DSOscilloscopeMahadevAinda não há avaliações

- The Eye Diagram: 1 Zero Level 2 One LevelDocumento9 páginasThe Eye Diagram: 1 Zero Level 2 One LevelAkramAinda não há avaliações

- PAPER EI (2) by Pankaj SirDocumento247 páginasPAPER EI (2) by Pankaj SirMahesh SinghAinda não há avaliações

- Eye AnatomyDocumento9 páginasEye Anatomysasa68Ainda não há avaliações

- ESC 201A ExpDocumento9 páginasESC 201A Expanshikamittal2626Ainda não há avaliações

- Apparatus:: AIM: Acquire The Knowledge of Output Devices Like CRO and DSO For Observing OutputDocumento5 páginasApparatus:: AIM: Acquire The Knowledge of Output Devices Like CRO and DSO For Observing OutputAdwait BorikarAinda não há avaliações

- Signal Resolution For ADCDocumento2 páginasSignal Resolution For ADCRolando FernandezAinda não há avaliações

- Digital Control of Switching Mode Power Supply Simone Buso 2Documento77 páginasDigital Control of Switching Mode Power Supply Simone Buso 2Ahmed58seribegawanAinda não há avaliações

- Es1107 Assignment-01Documento6 páginasEs1107 Assignment-01K. BHANU PRAKASH REDDYAinda não há avaliações

- An Intro To Digital Comms - Part 1Documento56 páginasAn Intro To Digital Comms - Part 1BEN GURIONAinda não há avaliações

- P-P Volts DivisionDocumento12 páginasP-P Volts DivisionG.Srinivasa sagarAinda não há avaliações

- Application of Digital Signal ProcessorsDocumento10 páginasApplication of Digital Signal ProcessorsAditya VelanjkarAinda não há avaliações

- Bel - 16 - ADC and DACDocumento26 páginasBel - 16 - ADC and DACBharavi K SAinda não há avaliações

- Simplified Analogue Realization of The Digital Direct Synthesis (DDS) Technique For Signal GenerationDocumento5 páginasSimplified Analogue Realization of The Digital Direct Synthesis (DDS) Technique For Signal GenerationInternational Organization of Scientific Research (IOSR)Ainda não há avaliações

- SCOPE Article - Automotive Oscilloscopes: by Bernie Thompson December 2017Documento4 páginasSCOPE Article - Automotive Oscilloscopes: by Bernie Thompson December 2017hakyAinda não há avaliações

- Chapter 2 Discrete Data Control SystemsDocumento78 páginasChapter 2 Discrete Data Control SystemsAmruth ThelkarAinda não há avaliações

- K Flop ManualDocumento306 páginasK Flop Manualhappydude7632Ainda não há avaliações

- Fairchild Lm7805cDocumento5 páginasFairchild Lm7805cGautam BalharaAinda não há avaliações

- تجربة 1Documento17 páginasتجربة 1Moaid BinAinda não há avaliações

- Eye PatternDocumento12 páginasEye PatternPawan Kumar JaiswalAinda não há avaliações

- An Innovative Method To Increase The Resolution of Optical EncodersDocumento6 páginasAn Innovative Method To Increase The Resolution of Optical EncodersFuadMuzaki09Ainda não há avaliações

- Digital SignalDocumento40 páginasDigital SignalKavita PuriAinda não há avaliações

- Xyzs of Oscilloscopes: Figure 22. Front-Panel Control Section of An OscilloscopeDocumento16 páginasXyzs of Oscilloscopes: Figure 22. Front-Panel Control Section of An OscilloscopeBom_Jovi_6810% (1)

- Digital Signal ProcessingDocumento9 páginasDigital Signal ProcessingChaitanyaAinda não há avaliações

- Digital Storage OscilloscopeDocumento4 páginasDigital Storage OscilloscopesushilAinda não há avaliações

- Delta ModulationDocumento5 páginasDelta Modulationian.maximillianAinda não há avaliações

- APSP - Lecture Notes 2Documento7 páginasAPSP - Lecture Notes 2Manjula sAinda não há avaliações

- Experiment No. 1 Familiarization With Laboratory Instruments: Oscilloscope, Function Generator, Digital Multimeter, and DC Power SupplyDocumento12 páginasExperiment No. 1 Familiarization With Laboratory Instruments: Oscilloscope, Function Generator, Digital Multimeter, and DC Power SupplyMukul ChandraAinda não há avaliações

- High-Resolution of Rotary EncoderDocumento5 páginasHigh-Resolution of Rotary EncoderGoran MiljkovicAinda não há avaliações

- ECE448 Lecture6 FSMDocumento77 páginasECE448 Lecture6 FSMHoàng Việt CườngAinda não há avaliações

- 3ADocumento12 páginas3AHoàng Việt CườngAinda não há avaliações

- Ir DADocumento17 páginasIr DAHoàng Việt CườngAinda não há avaliações

- Unit 10 My ClassmatesDocumento16 páginasUnit 10 My ClassmatesHoàng Việt CườngAinda não há avaliações

- Answer Key For Grade 4Documento2 páginasAnswer Key For Grade 4Hoàng Việt CườngAinda não há avaliações

- Lop 4 From Week 7 To 35Documento179 páginasLop 4 From Week 7 To 35Hoàng Việt CườngAinda não há avaliações

- Question 1: Listen and Number. There Is An Example (1 PT) : Part 1: Listening (20 Mins)Documento6 páginasQuestion 1: Listen and Number. There Is An Example (1 PT) : Part 1: Listening (20 Mins)Hoàng Việt CườngAinda não há avaliações

- A Design & Comparative Analysis of 320 Gbs DWDM Optical Network With CSRZ, DRZ & MDRZ Modulation FormatsDocumento6 páginasA Design & Comparative Analysis of 320 Gbs DWDM Optical Network With CSRZ, DRZ & MDRZ Modulation FormatsHoàng Việt CườngAinda não há avaliações

- Pennell Ipodwdm (IP Over DWDMDocumento45 páginasPennell Ipodwdm (IP Over DWDMBien Costorio CuaAinda não há avaliações

- IndexDocumento159 páginasIndexHoàng Việt CườngAinda não há avaliações

- 184 685 1 PBDocumento10 páginas184 685 1 PBHoàng Việt CườngAinda não há avaliações

- Dense Width DivisionMultiplexingDocumento35 páginasDense Width DivisionMultiplexingdsuntewAinda não há avaliações

- Point-to-Point DWDM System Design and Simulation: Gao Yan, Zhang Ruixia, Du Weifeng, and Cui XiaorongDocumento3 páginasPoint-to-Point DWDM System Design and Simulation: Gao Yan, Zhang Ruixia, Du Weifeng, and Cui XiaorongHoàng Việt CườngAinda não há avaliações

- Rate-Constrained Coder Control and Comparison of Video Coding StandardsDocumento19 páginasRate-Constrained Coder Control and Comparison of Video Coding StandardsHoàng Việt CườngAinda não há avaliações

- Final Fantasy Viii Na B 2 2Documento315 páginasFinal Fantasy Viii Na B 2 2Hoàng Việt CườngAinda não há avaliações

- Load - Map Tank - Show Tank - Shoot AI - Init AI - Show AI - Shoot (MS) (MS) (MS) (MS) (MS) (MS)Documento1 páginaLoad - Map Tank - Show Tank - Shoot AI - Init AI - Show AI - Shoot (MS) (MS) (MS) (MS) (MS) (MS)Hoàng Việt CườngAinda não há avaliações

- 5 - MSC - Prasanth (Modelling and Simulation of An Underwater Acoustic Communication)Documento115 páginas5 - MSC - Prasanth (Modelling and Simulation of An Underwater Acoustic Communication)Hoàng Việt CườngAinda não há avaliações

- CorrelationsDocumento29 páginasCorrelationsHoàng Việt CườngAinda não há avaliações

- Mpeg 7Documento69 páginasMpeg 7congbienAinda não há avaliações

- Bluetooth 130516090846 Phpapp01Documento24 páginasBluetooth 130516090846 Phpapp01Hoàng Việt CườngAinda não há avaliações

- MPLAB® X Integrated Development Environment: Universal and Integrated Tool SetDocumento2 páginasMPLAB® X Integrated Development Environment: Universal and Integrated Tool SetHoàng Việt CườngAinda não há avaliações

- VocabularyDocumento1 páginaVocabularyHoàng Việt CườngAinda não há avaliações

- sg300 PDFDocumento341 páginassg300 PDFalex mirelesAinda não há avaliações

- Intel® NUC Products NUC10i3FN/NUC10i5FN/ NUC10i7FN: Technical Product SpecificationDocumento75 páginasIntel® NUC Products NUC10i3FN/NUC10i5FN/ NUC10i7FN: Technical Product SpecificationmilebaleAinda não há avaliações

- Balun Pasivo 16 CHPFM809-4MPDocumento4 páginasBalun Pasivo 16 CHPFM809-4MPMauricio Conus SanchezAinda não há avaliações

- BraktoothDocumento16 páginasBraktoothSivakumar SelvamAinda não há avaliações

- Advanced ElectronicsDocumento19 páginasAdvanced ElectronicsKevin G. TolentinoAinda não há avaliações

- PV MPPT PoDocumento26 páginasPV MPPT PoBaidyanath JenaAinda não há avaliações

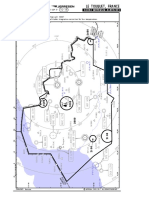

- Lfat/Ltq Le Touquet, France: .Radar - Minimum.AltitudesDocumento10 páginasLfat/Ltq Le Touquet, France: .Radar - Minimum.AltitudesAurelien FLUTEAUXAinda não há avaliações

- FAVI Mini Wireless Keyboard User GuideDocumento10 páginasFAVI Mini Wireless Keyboard User GuideDudley DorightAinda não há avaliações

- Rockchip RK3588 Datasheet V0 1-20210727Documento35 páginasRockchip RK3588 Datasheet V0 1-20210727scribd2Ainda não há avaliações

- Activity Module 1 (LED)Documento39 páginasActivity Module 1 (LED)naughty dela cruzAinda não há avaliações

- Bode Plot Bds 26 3 2015 PDFDocumento148 páginasBode Plot Bds 26 3 2015 PDFNikhil PatwariAinda não há avaliações

- ScheduleDocumento5 páginasSchedulercAinda não há avaliações

- Micro Controller Based Code LookDocumento9 páginasMicro Controller Based Code LookHimanshu MehtaAinda não há avaliações

- Biodata To MIDIDocumento18 páginasBiodata To MIDIJoão Carlos PintoAinda não há avaliações

- Inputing Data in Other WaysDocumento9 páginasInputing Data in Other WaysFai ShAinda não há avaliações

- Eikon E2Documento64 páginasEikon E2Jonathan GarciaAinda não há avaliações

- Datasheet 16F1938 PDFDocumento488 páginasDatasheet 16F1938 PDFAnonymous ZMx8heAinda não há avaliações

- LAB 2 Kenny Rich WenDocumento14 páginasLAB 2 Kenny Rich WenKenny RAinda não há avaliações

- LM117/217 LM317: 1.2V To 37V Voltage RegulatorDocumento11 páginasLM117/217 LM317: 1.2V To 37V Voltage RegulatorchzelAinda não há avaliações

- Manual LG An110w PDFDocumento48 páginasManual LG An110w PDFWayne WondAinda não há avaliações

- Origin AND ATA Standards: by Er - Swarnpreet SinghDocumento17 páginasOrigin AND ATA Standards: by Er - Swarnpreet SinghNupur GumberAinda não há avaliações

- Pressure Switch ManualDocumento19 páginasPressure Switch ManualJason TanAinda não há avaliações

- Comparison of CDMA and GSMDocumento4 páginasComparison of CDMA and GSMniteshg11Ainda não há avaliações

- Smartbridges 3212 Ve 3412 Data SheetDocumento5 páginasSmartbridges 3212 Ve 3412 Data SheetsagoreAinda não há avaliações

- Automatic Over Temperature Detection and AlertDocumento5 páginasAutomatic Over Temperature Detection and Alertsmartxdigital marketAinda não há avaliações

- Sensor de Flujo HoneywellDocumento4 páginasSensor de Flujo HoneywellMartin ArevaloAinda não há avaliações

- Electric Circuits Design: Department of Computer and Electrial Engineering (UENR)Documento32 páginasElectric Circuits Design: Department of Computer and Electrial Engineering (UENR)Boateng ElvisAinda não há avaliações

- CMC-Testing of Restricted Earth Fault Protection With OMICRON Advanced DifferentialDocumento12 páginasCMC-Testing of Restricted Earth Fault Protection With OMICRON Advanced Differentialskylimit.skylimit100% (4)

- Volvo Penta - D9-D16 - Instalation Overview - Diagram PDFDocumento2 páginasVolvo Penta - D9-D16 - Instalation Overview - Diagram PDFHugo Soberano100% (3)

- SETPOINT Machinery Protection System Overview Data SheetDocumento32 páginasSETPOINT Machinery Protection System Overview Data SheetBrickvilleAinda não há avaliações

- Microsoft Certified Azure Fundamentals Study Guide: Exam AZ-900No EverandMicrosoft Certified Azure Fundamentals Study Guide: Exam AZ-900Ainda não há avaliações

- AWS Certified Solutions Architect Study Guide: Associate SAA-C02 ExamNo EverandAWS Certified Solutions Architect Study Guide: Associate SAA-C02 ExamAinda não há avaliações

- Set Up Your Own IPsec VPN, OpenVPN and WireGuard Server: Build Your Own VPNNo EverandSet Up Your Own IPsec VPN, OpenVPN and WireGuard Server: Build Your Own VPNNota: 5 de 5 estrelas5/5 (1)

- Concise Guide to OTN optical transport networksNo EverandConcise Guide to OTN optical transport networksNota: 4 de 5 estrelas4/5 (2)

- Hacking Network Protocols: Complete Guide about Hacking, Scripting and Security of Computer Systems and Networks.No EverandHacking Network Protocols: Complete Guide about Hacking, Scripting and Security of Computer Systems and Networks.Nota: 5 de 5 estrelas5/5 (2)

- Microsoft Azure Infrastructure Services for Architects: Designing Cloud SolutionsNo EverandMicrosoft Azure Infrastructure Services for Architects: Designing Cloud SolutionsAinda não há avaliações

- The Compete Ccna 200-301 Study Guide: Network Engineering EditionNo EverandThe Compete Ccna 200-301 Study Guide: Network Engineering EditionNota: 5 de 5 estrelas5/5 (4)

- PHP BLUEPRINT: An Essential Beginners Guide to Learn the Realms of PHP From A-ZNo EverandPHP BLUEPRINT: An Essential Beginners Guide to Learn the Realms of PHP From A-ZAinda não há avaliações

- Azure Networking: Command Line Mastery From Beginner To ArchitectNo EverandAzure Networking: Command Line Mastery From Beginner To ArchitectAinda não há avaliações

- Cybersecurity: A Simple Beginner’s Guide to Cybersecurity, Computer Networks and Protecting Oneself from Hacking in the Form of Phishing, Malware, Ransomware, and Social EngineeringNo EverandCybersecurity: A Simple Beginner’s Guide to Cybersecurity, Computer Networks and Protecting Oneself from Hacking in the Form of Phishing, Malware, Ransomware, and Social EngineeringNota: 5 de 5 estrelas5/5 (40)

- Evaluation of Some Websites that Offer Virtual Phone Numbers for SMS Reception and Websites to Obtain Virtual Debit/Credit Cards for Online Accounts VerificationsNo EverandEvaluation of Some Websites that Offer Virtual Phone Numbers for SMS Reception and Websites to Obtain Virtual Debit/Credit Cards for Online Accounts VerificationsNota: 5 de 5 estrelas5/5 (1)

- Computer Systems and Networking Guide: A Complete Guide to the Basic Concepts in Computer Systems, Networking, IP Subnetting and Network SecurityNo EverandComputer Systems and Networking Guide: A Complete Guide to the Basic Concepts in Computer Systems, Networking, IP Subnetting and Network SecurityNota: 4.5 de 5 estrelas4.5/5 (13)

- Unlock Any Roku Device: Watch Shows, TV, & Download AppsNo EverandUnlock Any Roku Device: Watch Shows, TV, & Download AppsAinda não há avaliações

- Computer Networking: The Complete Guide to Understanding Wireless Technology, Network Security, Computer Architecture and Communications Systems (Including Cisco, CCNA and CCENT)No EverandComputer Networking: The Complete Guide to Understanding Wireless Technology, Network Security, Computer Architecture and Communications Systems (Including Cisco, CCNA and CCENT)Ainda não há avaliações

- Hacking: A Beginners Guide To Your First Computer Hack; Learn To Crack A Wireless Network, Basic Security Penetration Made Easy and Step By Step Kali LinuxNo EverandHacking: A Beginners Guide To Your First Computer Hack; Learn To Crack A Wireless Network, Basic Security Penetration Made Easy and Step By Step Kali LinuxNota: 4.5 de 5 estrelas4.5/5 (67)

- Designing and Building Security Operations CenterNo EverandDesigning and Building Security Operations CenterNota: 3 de 5 estrelas3/5 (3)

- Alcatel-Lucent Service Routing Architect (SRA) Self-Study Guide: Preparing for the BGP, VPRN and Multicast ExamsNo EverandAlcatel-Lucent Service Routing Architect (SRA) Self-Study Guide: Preparing for the BGP, VPRN and Multicast ExamsAinda não há avaliações

- Cybersecurity: The Beginner's Guide: A comprehensive guide to getting started in cybersecurityNo EverandCybersecurity: The Beginner's Guide: A comprehensive guide to getting started in cybersecurityNota: 5 de 5 estrelas5/5 (2)