Escolar Documentos

Profissional Documentos

Cultura Documentos

Verilog l14 Mit

Enviado por

Nishant JainDescrição original:

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Verilog l14 Mit

Enviado por

Nishant JainDireitos autorais:

Formatos disponíveis

6.

111 Fall 2007 Lecture 14, Slide 1

Lab 4 overview

ac97

ac97-

commands

audio

Serial links

to/from AC97

chip

recorder

(your job!)

ready

8

8

64K x 8 BRAM

w

e

8 8 Addr 16

ENTER button

(push to record)

lab3.v

Assignment: build a voice recorder that records

and plays back 8-bit PCM data @ 6KHz

About 11 seconds of speech @ 6KHz

6.111 Fall 2007 Lecture 14, Slide 2

AC97: PCM data

Slot 0 (16) Slot 1 (20) Slot 20 (20)

AC97_SYNCH

READY

Slot 2 (20)

256 bits @ 12.288Mhz = 48kHz frame rate

Slot 3 (20)

Frame info commands LData

ready selects a particular clock_27mhz clock edge when you

should store input data from the AC97 (from_ac97_data) and

provide new output to the AC97 (to_ac97_data).

PCM = pulse code modulation

Sample waveform at 48kHz,

encode results as an N-bit

signed number. For our AC97

chip, N = 18.

Slot 4 (20)

RData

FPGA sends output frame to AC97 while AC97 sends input frame to FPGA

6.111 Fall 2007 Lecture 14, Slide 3

6.111 Final Project

6.111 Fall 2007 Lecture 14, Slide 4

Final Project: Schedule

Choose project teams (email cjt by Oct.22)

Teams of two (or maybe three). A single person project

requires approval of lecturer.

Project Abstract (due Oct. 29, submit on-line)

Start discussing ideas now with 6.111 staff

About 1 page long, clearly identify whos doing what

Proposal Conference with staff mentor (by Nov. 2)

Bring your proposal with you and submit on-line

Block Diagram Conference with mentor (by Nov. 9)

Review major components and overall design approach

Specify the device components you need to acquire (small

budget allocated for each project if component does not

exist in the stock room). Get approval from the 6.111

staff and your TA will contact John Sweeney to obtain

the parts.

6.111 Fall 2007 Lecture 14, Slide 5

Schedule (contd.)

Project Design Presentation to staff (Nov 13 15)

Each group will make a 15 min electronic presentation

(~10 slides) dividing presentation among team members

Submit PDF on-line, will be posted on website

Example: S2004 FROGGER presentation slides

Project Checkoff Checklist to staff (Nov 16)

Each group in discussion with TA creates a checklist of

deliverables (i.e., what we can expect each team member

to demonstrate). Submit PDF on-line.

Final Project Presentations (Dec 10 - 12)

Videotaped and posted on-line with your permission

Final Project Report (Dec 12, 5p)

Submit PDF on-line, will be posted on website

Sorry, no late checkoffs or reports will be accepted

6.111 Fall 2007 Lecture 14, Slide 6

Team Organization

Most importantly, you need one

Key decisions made jointly

Requirements

High level design

Schedule

Who will work on what, wholl take the lead

Response to slippage

Lower level design exchanged for examination

Everyone responsible for everything

Design reviews tremendously helpful

Try it, youll like it

Communicate with each other early and often

6.111 Fall 2007 Lecture 14, Slide 7

Controlling Schedule

First, you must have one

Need verifiable milestones

Some non-verifiable

milestones

90% of coding done,

90% of debugging

done, Design complete

Need 100% events

Module 100% coded,

Unit testing complete

Need critical path chart

Know effects of

slippage

Know what to work on

when

35% Planning

(not all up front)

15% Coding

25% module

test/dubug

25% system

test/debug

Provide a 4-7 day contingency

to deal with unforeseen issues

(youll use it all!)

6.111 Fall 2007 Lecture 14, Slide 8

Choosing A Topic

You only have 6 weeks total (once your proposal abstract is

turned in) to do this project.

It is important to complete your project.

It is very difficult to receive an A in the class without

having something working for the final project.

The complexity for each team member should greater than the

complexity of the lab assignments.

Some projects include analog building blocks or mechanical

assemblies (infrared, wireless, motors, etc.). However, keep in

mind that this is a digital design class and your design will be

evaluated on its digital design aspects.

Complexity, risk and innovation factor.

We will give credit to innovative applications, design approaches

More complex is not necessarily better

Look through previous projects for inspiration (see website)

6.111 Fall 2007 Lecture 14, Slide 9

Example Projects

Music Transcriber

Roberto Carli, Alessandro Yamhure

Fall 2005

Virtual Juggling

David Rush, Christopher Wilkens

Fall 2005

6.111 Fall 2007 Lecture 14, Slide 10

Some Suggestions

Be ambitious!

But choose a sequence of milestones that are increasingly

ambitious (that way at least part of your project will

work and you can debug features incrementally).

But dont expect 400Mhz operating frequencies, etc.

Its motivating if theres something to see or hear

Video and graphics projects are fun (and with the labkit

basic video input and output are pretty straightforward

which means you can concentrate on the processing)

Audio/Music is low-bandwidth, so its easy to do

interesting processing in real-time (real-time is harder

with video).

Memories are often the limiting factor

Figure out how youll use memory blocks early-on

6.111 Fall 2007 Lecture 14, Slide 11

More Suggestions

Be modular!

Figure out how test your modules incrementally (good for

debugging and checkoff!)

Be clear about what information is passed between

modules (format, timing)

Dont be caught by the maana principle

Six weeks goes by quickly: have a weekly task list.

How does a project run late: one day at a time!

Effort is not the same as progress: Written but not

tested only means youve made a start

Tasks will take longer than you think

Final integration will uncover bugs/thinkos so test module-

to-module interactions as earlier as you can

6.111 Fall 2007 Lecture 14, Slide 12

Grading (40 points Total)

Report and Presentation (10 points)

Problem Definition and Relevance, Architecture,

Design methodology (10 points)

What is the problem

Why is it important

System architecture and partitioning

Design choices and principles used

Style of coding

All of the above should be stated in the project and

report

Functionality (10 points)

Did you complete what your promised (i.e., graded by

the checklist)

Complexity, Innovation, Risk (10 points)

6.111 Fall 2007 Lecture 14, Slide 13

Design Rules

Use hierarchical design

Partition your design into small subsystems that are easier

to design and test.

Design each sub-system so they can be tested individually.

When appropriate, use Major/Minor FSMs.

Use the same clock edge for all edge-triggered

flip-flops

Beware of clock skew, dont gate the clock

Avoid problems from glitches.

Always assume that combinational logic glitches

Never drive a critical asynchronous control signal (register

clock, write enable) from the output of combinational logic.

Ensure a stable combinational output before it is sampled

by CLK.

When needed, create glitch-free signals by registering

outputs.

6.111 Fall 2007 Lecture 14, Slide 14

Design Rules (contd.)

Avoid tristate bus contention by design

Synchronize all asynchronous signals

Use two back to back registers

Use memory properly

Avoid high Z address to SRAM when CE is asserted.

Avoid address changes when WE is true.

Make sure your write pulse is glitch free.

Power supply can be noisy

Use bypass capacitors to filter noise

Chip-to-chip communication

Beware of noise (inductance)

Might need to synchronize signals

Can also use asynchronous protocols

6.111 Fall 2007 Lecture 14, Slide 15

How to Make Your Project Work

(see website)

Sections that are particularly relevant are:

Wiring Errors

Care and Feeding of the Power Supply

Unused Inputs

Behavior of Ungrounded Parts

Tri-State Logic Signals

Handling CMOS Parts

Wire Routing

Clock Distribution

Gating the Clock

RAM Write Pulses

Synchronizer Errors

Testing Strategies

Driving High Current Devices

Document Courtesy of

Tom Knight and Don

Troxel

Você também pode gostar

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNo EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNota: 4 de 5 estrelas4/5 (5794)

- Verilog l16 MitDocumento11 páginasVerilog l16 MitNishant JainAinda não há avaliações

- MIT VerilogDocumento17 páginasMIT VerilogNishant JainAinda não há avaliações

- Verilog Mit Fifo.VDocumento1 páginaVerilog Mit Fifo.VNishant JainAinda não há avaliações

- VERILOG Pipelined Beta.VDocumento6 páginasVERILOG Pipelined Beta.VNishant JainAinda não há avaliações

- Verilog l15 MitDocumento21 páginasVerilog l15 MitNishant JainAinda não há avaliações

- Verilog l17 MitDocumento30 páginasVerilog l17 MitNishant JainAinda não há avaliações

- Verilog l08 MitDocumento20 páginasVerilog l08 MitNishant JainAinda não há avaliações

- Verilog l11 MitDocumento24 páginasVerilog l11 MitNishant JainAinda não há avaliações

- Verilog l13 MitDocumento22 páginasVerilog l13 MitNishant JainAinda não há avaliações

- Verilog l10 MitDocumento24 páginasVerilog l10 MitNishant JainAinda não há avaliações

- Verilog l12 MitDocumento23 páginasVerilog l12 MitNishant JainAinda não há avaliações

- LQR For Rotating Inverted PendulumDocumento14 páginasLQR For Rotating Inverted PendulumValery GaulinAinda não há avaliações

- Level To PulseDocumento18 páginasLevel To PulseVineet JeswaniAinda não há avaliações

- Verilog l09 MitDocumento22 páginasVerilog l09 MitNishant JainAinda não há avaliações

- VerilogDocumento24 páginasVerilogMaheshwar ReddyAinda não há avaliações

- Something We Can't Build (Yet)Documento22 páginasSomething We Can't Build (Yet)John DingAinda não há avaliações

- Verilog L06 MITDocumento24 páginasVerilog L06 MITNishant JainAinda não há avaliações

- Verilog L01 MITDocumento24 páginasVerilog L01 MITNishant JainAinda não há avaliações

- Verilog l02 MitDocumento28 páginasVerilog l02 MitNishant JainAinda não há avaliações

- Verilog l03 MitDocumento24 páginasVerilog l03 MitNishant JainAinda não há avaliações

- New Text DocumentDocumento1 páginaNew Text DocumentNishant JainAinda não há avaliações

- Total Quality ManagementDocumento14 páginasTotal Quality ManagementNishant Jain60% (10)

- Verilog Beta2 MitDocumento1 páginaVerilog Beta2 MitNishant JainAinda não há avaliações

- The Yellow House: A Memoir (2019 National Book Award Winner)No EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Nota: 4 de 5 estrelas4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNo EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNota: 4 de 5 estrelas4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNo EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNota: 4.5 de 5 estrelas4.5/5 (344)

- The Little Book of Hygge: Danish Secrets to Happy LivingNo EverandThe Little Book of Hygge: Danish Secrets to Happy LivingNota: 3.5 de 5 estrelas3.5/5 (399)

- The Emperor of All Maladies: A Biography of CancerNo EverandThe Emperor of All Maladies: A Biography of CancerNota: 4.5 de 5 estrelas4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNo EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNota: 4.5 de 5 estrelas4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItNo EverandNever Split the Difference: Negotiating As If Your Life Depended On ItNota: 4.5 de 5 estrelas4.5/5 (838)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNo EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNota: 3.5 de 5 estrelas3.5/5 (231)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNo EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNota: 4.5 de 5 estrelas4.5/5 (474)

- Team of Rivals: The Political Genius of Abraham LincolnNo EverandTeam of Rivals: The Political Genius of Abraham LincolnNota: 4.5 de 5 estrelas4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyNo EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyNota: 3.5 de 5 estrelas3.5/5 (2259)

- The Unwinding: An Inner History of the New AmericaNo EverandThe Unwinding: An Inner History of the New AmericaNota: 4 de 5 estrelas4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNo EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNota: 4 de 5 estrelas4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)No EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Nota: 4.5 de 5 estrelas4.5/5 (121)

- Computers Vs Humans 1Documento7 páginasComputers Vs Humans 1Frena1Ainda não há avaliações

- MTech Thesis ListDocumento62 páginasMTech Thesis ListmohanAinda não há avaliações

- DBX 266xl SCHDocumento9 páginasDBX 266xl SCHFazar AhmadAinda não há avaliações

- Argon Recovery From Silicon Crystal FurnaceDocumento7 páginasArgon Recovery From Silicon Crystal FurnaceasdfqwerAinda não há avaliações

- Reference Manual: Date: 10/17/08Documento31 páginasReference Manual: Date: 10/17/08Abhishek RanjanAinda não há avaliações

- C 102Documento1 páginaC 102Nicky DragutescuAinda não há avaliações

- 2SK241Documento7 páginas2SK241ytnateAinda não há avaliações

- Practical Electronics 1966 10 PDFDocumento84 páginasPractical Electronics 1966 10 PDFCarlos SoaresAinda não há avaliações

- Regius 110 Service ManualDocumento312 páginasRegius 110 Service ManualWellington Trajano75% (8)

- L7 - Fundamental of Electric DrivesDocumento17 páginasL7 - Fundamental of Electric Drivesatul pandeyAinda não há avaliações

- Lateral Monolayer MoSe2-WSe2 P-N Heterojunctions With Giant Built-In PotentialsDocumento7 páginasLateral Monolayer MoSe2-WSe2 P-N Heterojunctions With Giant Built-In PotentialsNgô Gia QuyếtAinda não há avaliações

- Lab Answers p3Documento16 páginasLab Answers p3api-343575651Ainda não há avaliações

- Abstract of IE Rules For DP StructureDocumento2 páginasAbstract of IE Rules For DP StructureJignesh ParmarAinda não há avaliações

- ABB Traction Rectifiers Brochure enDocumento16 páginasABB Traction Rectifiers Brochure eniaiscan1009Ainda não há avaliações

- Cortinas GL r63fDocumento3 páginasCortinas GL r63fviernes06Ainda não há avaliações

- Is Now Part ofDocumento25 páginasIs Now Part ofkilowatt СкворцовAinda não há avaliações

- Logic Lab 1 - Digital Abstraction (5 Gates)Documento16 páginasLogic Lab 1 - Digital Abstraction (5 Gates)ram010Ainda não há avaliações

- Sboa 290 CSHXGHDCXCFXDDCGDocumento6 páginasSboa 290 CSHXGHDCXCFXDDCGKarthik SuryaAinda não há avaliações

- 2D Electron GasDocumento16 páginas2D Electron GastridevmishraAinda não há avaliações

- 6 Power Generation From Piezoelectric Footstep Muhammad Aamir Vol 13 No 4Documento7 páginas6 Power Generation From Piezoelectric Footstep Muhammad Aamir Vol 13 No 4N MeghanaAinda não há avaliações

- Chapter One 1.0 Background of The StudyDocumento50 páginasChapter One 1.0 Background of The StudyNduka GodwinAinda não há avaliações

- Fix William Edgar Cayce La Grande Pyramide Et LAtlantideDocumento92 páginasFix William Edgar Cayce La Grande Pyramide Et LAtlantideManuelAinda não há avaliações

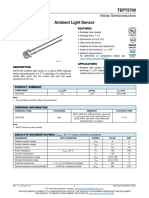

- TEPT5700, Ambient Light SensorDocumento5 páginasTEPT5700, Ambient Light SensorHugoAinda não há avaliações

- NDBDocumento58 páginasNDBSumindak GultomAinda não há avaliações

- NanotechnologyDocumento55 páginasNanotechnologySachin BajpaiAinda não há avaliações

- Noise Margin Criteria For Digital Logic Circuits: Ieee Transactions On Education, Vol. 30, No. 4, Novemlitlt Ly3Documento6 páginasNoise Margin Criteria For Digital Logic Circuits: Ieee Transactions On Education, Vol. 30, No. 4, Novemlitlt Ly3Khadir AhmedAinda não há avaliações

- Disclosure To Promote The Right To InformationDocumento39 páginasDisclosure To Promote The Right To InformationA.YOGAGURUAinda não há avaliações

- 1.2A Step-Down Converter With 1.4Mhz Switching Frequency: Ap5100 Ap5100Documento2 páginas1.2A Step-Down Converter With 1.4Mhz Switching Frequency: Ap5100 Ap5100bilalAinda não há avaliações

- GEN PROTN CombiflexDocumento68 páginasGEN PROTN CombiflexRK K100% (1)

- Static Var CompensatorDocumento6 páginasStatic Var Compensatoralexandre_foxtrotAinda não há avaliações