Escolar Documentos

Profissional Documentos

Cultura Documentos

ECEN654 Lab2

Enviado por

Anand Krishna Ghatty0 notas0% acharam este documento útil (0 voto)

64 visualizações14 páginasThis document provides instructions for implementing a digital filter in MATLAB and Verilog. It involves:

1. Using the FDA tool in MATLAB to design an IIR filter and parameterize the coefficients.

2. Quantizing the filter coefficients and inputs/outputs in MATLAB to meet noise and performance targets.

3. Extracting the test data and design parameters from the MATLAB model.

4. Implementing a sample biquad filter module in Verilog, and writing a testbench to verify it by applying the test vectors generated from MATLAB.

Descrição original:

Filters

Título original

ECEN654_Lab2

Direitos autorais

© © All Rights Reserved

Formatos disponíveis

PDF, TXT ou leia online no Scribd

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoThis document provides instructions for implementing a digital filter in MATLAB and Verilog. It involves:

1. Using the FDA tool in MATLAB to design an IIR filter and parameterize the coefficients.

2. Quantizing the filter coefficients and inputs/outputs in MATLAB to meet noise and performance targets.

3. Extracting the test data and design parameters from the MATLAB model.

4. Implementing a sample biquad filter module in Verilog, and writing a testbench to verify it by applying the test vectors generated from MATLAB.

Direitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato PDF, TXT ou leia online no Scribd

0 notas0% acharam este documento útil (0 voto)

64 visualizações14 páginasECEN654 Lab2

Enviado por

Anand Krishna GhattyThis document provides instructions for implementing a digital filter in MATLAB and Verilog. It involves:

1. Using the FDA tool in MATLAB to design an IIR filter and parameterize the coefficients.

2. Quantizing the filter coefficients and inputs/outputs in MATLAB to meet noise and performance targets.

3. Extracting the test data and design parameters from the MATLAB model.

4. Implementing a sample biquad filter module in Verilog, and writing a testbench to verify it by applying the test vectors generated from MATLAB.

Direitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato PDF, TXT ou leia online no Scribd

Você está na página 1de 14

In Bis Name

ECEN 6S4 Lab 2 Filtei Besign

!"#$%&"'()

Using Matlab FDA tool to parameterize infinite impulse response (IIR)

coefficients

Safe scaling Parasitic oscillation effects

Hardware implementation and test of digital filters fully combinational

method

+,-$.#&/$()

In this lab you will implement a filter, whose characteristics are given. During

the implementation, you will experience using Matlab FDA tool to parameterize filter

coefficients. And do quantize the filter in Matlab and understand how quantization

affects a DSP design. Finally, you will design your filter using Verilog code and verify

it with a self-diagnostic test bench that obtains its data from Simulink model.

0&'#$% 1"%2$# 34"%".#$%&(#&.()

0&'#$%)

Rp = 1db, Rs = 60db, Fs = 44100Hz, Fp = 3400Hz, Order=6.

Quantization signal-to-noise ratio (SNR) >= 35 dB

5678#)

Sample voice signal which is normalized to the (-1, +1) amplitudes with sample

frequency equal to 44100.

9&%$.#&:6()

1. Launch Matlab

Log in to the serve by using your NETID. Open the terminal and type below

to open .tschrc file.

gedit ./.tschrc

Add following line into the file:

alias matlab /softwares/Linux/matlab2012b/bin/matlab

Save the file and quit to terminal. By typing following command, validate the

shortcut for matlab

source ./.tschrc

Then type matlab in terminal to launch Matlab

2. Parameterize the IIR by using FDA tool

After launching the Matlab, create a directory where you want to save all stuff

in this lab and change the path to the created directory. Then by typing fdatool in the

console window of matlab, you can launch the FDA tool. Set the characteristics as

given before and click design filter, as shown in Figure 1.

After designing filter, click the realize model label, the fourth label in the left

bar. Check the option Build model using basic elements and press Realize Model as

shown in Figure 2. Then the IIR filter will be automatically parameterized in a

Simulink model in Figure 3. In the Simulink window, click File-> Save to save the

model in the local folder. If you double click the filter, you can see the internal

structure of the filter.

Figure 2

Figure 3

Next step, we will quantize and simulate the parameterized the IIR filter.

3. Quantizing the filter to target performance

In this section, we will quantize the coefficients in the IIR filter. First of all, we

will set up the quantized model based on the floating-point filter model. Then we will

simulate the quantized model and see how the quantization affects the performance.

Finally, we can determine how we quantize the model with acceptable degradation in

performance.

Before simulating the quantization, go to lab webpage to download the test

wave file, test.mat to local directory. This file will be used as signal source.

3.1 Quantize the Coefficients

Double click the quantized filter model. And check the swings of all

coefficients. So that you can determine how many bits are necessary for the integer

part.

Next step we need do experiments to examine how many bits necessary for

precision. Open the coefficients gains. And edit the gain as shown in Figure 4, where

ck is the precision bit length for quantized coefficients.

Doing this modification on all coefficients so that all of them are quantized.

Next step, we need port out ck value setting from this model. In the top model, right

click the quantized filter model and click mask->create mask. And add parameter as

shown in figure 5.

Now you can change the value of ck easily from top model by double-click the

quantized model.

Figure 4

Figure 5

After adding those quantization blocks, we now start to find best quantization.

Click View->Library Browser to launch the library browser, you can find any

blocks you need by typing name to search.

Use the library browser to add block of band-limited white noise, mux and

spectrum scope as shown in Figure 6.

Figure 6

Double click the band-limited white noise, replace the default value of 0.1 with

1. And set the sample time is 1/44100.

Double click the spectrum scope and set it as shown in Figure 7.

Figure 7

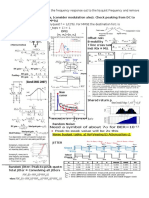

Then run the Simulink. You will see the spectrum from floating-point model

and fixed-point model. Change the quantization to make sure the difference in pass

band less than 0.1 dB and less than 1 dB in stop band as shown in Figure 8.

Figure 8

3.2 Quantize the Input and Output

Double click the saved model.

Once you open the model, click View->Library Browser to launch the library

browser. Type From file to search for the source block and drag the block into

model. Double click the model and select test.mat as the source file and type

1/44100 in the sample time, since our filter is designed for fs = 44100Hz.

Duplicate the IIR filter in the same model, and rename the duplicated model as

Quantized Model:

Add other blocks as shown in Figure 9. All blocks could be found in Library

Browser. After adding RMS block, double click it check running rms and choose

sample based input processing.

Figure 9

If you run the Simulink now, you could find the SNR is infinite because two

filters are exactly same and product same results.

To quantize the I/O, firstly we need know the swing of I/O. We using to

work space block to acquire the input and output from the Simulink as shown in

Figure 10.

Figure 10

By doing this we can know the magnitude of input and output. Now, we start

quantizing the I/O. Double click the quantized model, add quantization part after

input and before output. Quantization segment consists of three components: gain,

round, saturation.

The quantization part looks as below:

Figure 11

The first gain blocks increase the values to make precision reserved. The

corresponding gain should be 2^(k-1), where k is the precision.

The round block truncates redundant precision.

The saturation part prevent overflow from designed swing amplitude. The

value of saturation should be 2^(k+s-1)-1 for upper bound, -2^(k+s-1) for lower

bound, where s is number of assigned bits for swing.

The second gain block decrease the values to approach the quantized value.

The corresponding gain should be 1/(2^(k-1)).

By adding quantization section in input and output, we can do safe

quantization for input and output.

By applying different values of k, SNR will differ. Choose the minimum k

which makes SNR larger than 35 dB.

At this point, we finish quantizing the I/O. Now you can start the Bus

Quantization by the same method we used in I/O quantization.

3.3 Quantize the Bus

Repeat the way we quantized the I/O to determine the bus width in every node.

In this case, you need make sure that the quantization will not degrade the SNR lower

than 35 dB.

4. Implementation

After quantization of the filter you need to extract the data from Simulink

model to be used in verification part. The implementation of the hardware is

described as flows:

Besign: After extracting the real implementation parameters of the system properly,

you would be able to model the system (one of the biquads of 6 ordered IIR filter)

using HDL languages (Verilog in this case). For this purpose, design two basic

modules named mult_sr and add_s for bit-true multiplication and addition

respectively. Verify these modules for proper operation. The length of inputs and

outputs for these modules were the same as you extracted in your former experiences.

Consider these two modules as basic functions and model the entire biquad filter. In

this part, consider the state variables (register outputs) and also input/output values.

The sample biquad module should be able to compute the filtering operation for an

instance of input data.

veiification: After completing the design phase of your sample biquad filter, you

should verify the design using proper input and output samples. Applying input samples,

updating the state variables and dumping the output results to output file are performed

in the biquad testbench. For better understanding of how to write a proper Self-

diagnostic testbench, consider that the verification part consists of three following

phases:

Test dat a generat i on: Monitor the input and output lines of the samples

biquad filter in your MATLAB model during a complete simulation cycle. For

this, apply a sample input to the filter (6th otdered) and send the input and

output lines of the sample biquad part to the workspace. Then, write the

extracted test data from workspace to standard files (mat_data_in.dat and

mat_data_out.dat) regarding the extracted bit-length parameters.

Appl yi ng t est dat a: In this phase, generated test data are automatically applied

to the verilog biquad module. For this, write a testbench over the designed

module. The testbench do the following operations at each positive clock edge:

read the data from Matlab Input data file and apply them to the Verilog module.

Aut omat i c veri f i c at i on: In this phase, the Verilog model is verified using the

generated samples from MATLAB model. For this, read samples from Matlab

output data file and compare that with Verilog output data. In this part, any

existing inconsistency demonstrates the fault in your design process and should

be removed.

9$'&/$%",'$()

Compare SNR degradation after data bus quantization for different structures.

Report appropriate additional word length for precision adjustment of internal

nodes in swing measurement and safe scaling method.

Verilog models (both design and testbench)

Extracted test data and test extraction program for MATLAB

A complete description about the test data generation, HDL design and

modeling, and verification strategy.

;$'7<8' ;&6#()

!"#$%&$'()#$*+ ! !"#

!

! ! ! !"#$%&'

!

!!!

, Where h is the impulse

response from the input to node (safe scaling).

For writing the generated test data into standard IO files, you may use fprintf

and fopen commands.

For writing the self-diagnostic testbench you may use $fopen and $readmemb

($readmemh).

Xilinx ISE can not synthesis the multipliers use one of the structures presented

here: http://fpga-guru.com/multipli.htm

Figure 1- The structure of a simple filter at left and warp around adder at right.

Figure 2- The three different inputs from left to right a, b, and c.

Figure 3- The block diagram of the system to be implemented in Simulink.

Você também pode gostar

- Advanced C++ Interview Questions You'll Most Likely Be Asked: Job Interview Questions SeriesNo EverandAdvanced C++ Interview Questions You'll Most Likely Be Asked: Job Interview Questions SeriesAinda não há avaliações

- Hacks To Crush Plc Program Fast & Efficiently Everytime... : Coding, Simulating & Testing Programmable Logic Controller With ExamplesNo EverandHacks To Crush Plc Program Fast & Efficiently Everytime... : Coding, Simulating & Testing Programmable Logic Controller With ExamplesNota: 5 de 5 estrelas5/5 (1)

- Ar10 Jig Instructions PDFDocumento5 páginasAr10 Jig Instructions PDFterrencebelles100% (2)

- 2008 Nissan Teana J32 Service Manual-HacDocumento245 páginas2008 Nissan Teana J32 Service Manual-HacMrihexAinda não há avaliações

- 260 Postulates of The Dynamics of TimeDocumento78 páginas260 Postulates of The Dynamics of Timesmartjohnsmith10100% (2)

- System Generator TutorialDocumento33 páginasSystem Generator TutorialAthul KsAinda não há avaliações

- How To Troubleshoot An Error 77 in DevicenetDocumento12 páginasHow To Troubleshoot An Error 77 in DevicenetJuscelio Damascena0% (1)

- Projects With Microcontrollers And PICCNo EverandProjects With Microcontrollers And PICCNota: 5 de 5 estrelas5/5 (1)

- Simulink Code GenerationDocumento45 páginasSimulink Code GenerationKen LeAinda não há avaliações

- Cadence IntroductionDocumento15 páginasCadence Introductiondragos_bondAinda não há avaliações

- Frequency Analysis Vibration Spectrum Analysis Steve GoldmanDocumento9 páginasFrequency Analysis Vibration Spectrum Analysis Steve GoldmantylerdurdaneAinda não há avaliações

- Matlab Interview Questions PDFDocumento15 páginasMatlab Interview Questions PDFFebin George100% (2)

- Optimized Design of A Bagasse Dryer System For The Sugar IndustryDocumento6 páginasOptimized Design of A Bagasse Dryer System For The Sugar IndustryTJ BolorAinda não há avaliações

- 19A Time Collection Device Integration Activity Guide PDFDocumento78 páginas19A Time Collection Device Integration Activity Guide PDFAliya AmarAinda não há avaliações

- Evaporator Design CalculationDocumento58 páginasEvaporator Design CalculationManoj BAinda não há avaliações

- Laboratory Exercise 4 Cmos Inverter LayoutDocumento10 páginasLaboratory Exercise 4 Cmos Inverter Layoutapi-3696675Ainda não há avaliações

- TM 9-792 M21 AMMUNITION TRAILERDocumento128 páginasTM 9-792 M21 AMMUNITION TRAILERAdvocate100% (1)

- Lab 2Documento4 páginasLab 2geoaamer100% (1)

- Indicsoft ProfileDocumento13 páginasIndicsoft ProfileMahmood AkhtarAinda não há avaliações

- Simulink Exercise: Prepared by Jayakrishna Gundavelli and Hite NAME: - DATEDocumento12 páginasSimulink Exercise: Prepared by Jayakrishna Gundavelli and Hite NAME: - DATEKarthikeyan SubbiyanAinda não há avaliações

- Hamming Codes Matlab SimulinkDocumento8 páginasHamming Codes Matlab SimulinkAnonymous oP3Hdx100% (1)

- Tutorial: Introduction To DSP Using Sysgen and Introductory AssignmentDocumento11 páginasTutorial: Introduction To DSP Using Sysgen and Introductory AssignmentshivaspyAinda não há avaliações

- Lab 3 - Signal RoutingDocumento5 páginasLab 3 - Signal RoutingkyfeeeAinda não há avaliações

- Lab-DC Motor ControlDocumento5 páginasLab-DC Motor Controlahmed3423Ainda não há avaliações

- Lab 2 - Hierarchical Design and Linear SystemsDocumento7 páginasLab 2 - Hierarchical Design and Linear SystemsErcanŞişkoAinda não há avaliações

- Lab 1 - Intro To Simulink and Frequency AnalysisDocumento9 páginasLab 1 - Intro To Simulink and Frequency AnalysisErcanŞişkoAinda não há avaliações

- SystemC Questa TutorialDocumento11 páginasSystemC Questa TutorialmanavalaAinda não há avaliações

- ELEC313 Lab#3Documento10 páginasELEC313 Lab#3Ali MoharramAinda não há avaliações

- Assign 3Documento5 páginasAssign 3api-252659046Ainda não há avaliações

- Simulink LabDocumento11 páginasSimulink LabMohsin BhattiAinda não há avaliações

- Simulink & GUI in MATLAB: Experiment # 5Documento10 páginasSimulink & GUI in MATLAB: Experiment # 5Muhammad Ubaid Ashraf ChaudharyAinda não há avaliações

- Jalwin Cpe301 Ex5 PDFDocumento14 páginasJalwin Cpe301 Ex5 PDFSiegrique Ceasar A. JalwinAinda não há avaliações

- Lab 7Documento7 páginasLab 7Vikas GuptaAinda não há avaliações

- SystemC IntroductionDocumento21 páginasSystemC IntroductionMuhammad IsmailAinda não há avaliações

- 2-TX FSK 15-16 Part 1Documento8 páginas2-TX FSK 15-16 Part 1Đặng Hoài Sơn100% (1)

- Lab Session 5pptDocumento17 páginasLab Session 5pptMuhammad HishamAinda não há avaliações

- Lab 05 Modeling of Mechanical Systems Using Simscap Multibody 2nd Generation Part 1Documento19 páginasLab 05 Modeling of Mechanical Systems Using Simscap Multibody 2nd Generation Part 1Reem GheithAinda não há avaliações

- Create Model That Uses MATLAB Function BlockDocumento5 páginasCreate Model That Uses MATLAB Function BlockVipan SharmaAinda não há avaliações

- Digital Signal Processing: Labno9Documento8 páginasDigital Signal Processing: Labno9Muhammad hamza awanAinda não há avaliações

- Cadence Tutorial 4Documento14 páginasCadence Tutorial 4bk249Ainda não há avaliações

- Matlab Simulink Lab Exercises Designed For Teaching Digital Signal Processing ApplicationsDocumento14 páginasMatlab Simulink Lab Exercises Designed For Teaching Digital Signal Processing Applicationsjomer_juan14Ainda não há avaliações

- Add SubDocumento5 páginasAdd SubJeff WillAinda não há avaliações

- ELECTRONIC CIRCUIT ANALYSIS (ECA) Lab ManualDocumento24 páginasELECTRONIC CIRCUIT ANALYSIS (ECA) Lab Manualjeravi8475% (4)

- NI Tutorial 7592 en PDFDocumento9 páginasNI Tutorial 7592 en PDFParameswararao BillaAinda não há avaliações

- Timing, Shift Registers, and Case Structures - National InstrumentsDocumento13 páginasTiming, Shift Registers, and Case Structures - National InstrumentsRa BalamuruganAinda não há avaliações

- Experiment 7 - 2FSKDocumento8 páginasExperiment 7 - 2FSKHussain Ageel NaseerAinda não há avaliações

- An 347Documento8 páginasAn 347sjpritchardAinda não há avaliações

- Search For Potential Functional Issues With Code InspectorDocumento11 páginasSearch For Potential Functional Issues With Code InspectorEsther VizarroAinda não há avaliações

- LAB 6: I IIR: Lastname: - 5digit SSDocumento9 páginasLAB 6: I IIR: Lastname: - 5digit SSmrithyunjaysivAinda não há avaliações

- Easy Guide 14Documento37 páginasEasy Guide 14Trilobite3000Ainda não há avaliações

- Self Checking TestbenchDocumento4 páginasSelf Checking TestbenchSrinu TummalaAinda não há avaliações

- Step by Step Tutorial On DSP Using Xilinx System Generator (NOT HOMEWORK)Documento20 páginasStep by Step Tutorial On DSP Using Xilinx System Generator (NOT HOMEWORK)vipula123Ainda não há avaliações

- Mini ProjectDocumento3 páginasMini ProjectNUR HAFRIZ BIN HARUNAinda não há avaliações

- Eca Lab Manual Using PspiceDocumento30 páginasEca Lab Manual Using PspiceArjun AryanAinda não há avaliações

- Small ProjectDocumento3 páginasSmall Projectabdo hussienAinda não há avaliações

- Experiment # 3 Amplitude Modulation and Demodulation: 1 PurposeDocumento9 páginasExperiment # 3 Amplitude Modulation and Demodulation: 1 PurposeGeorgeAinda não há avaliações

- Exercise 07Documento5 páginasExercise 07Doublev OmerAinda não há avaliações

- Exp 2Documento9 páginasExp 2gvkovindAinda não há avaliações

- Matlab, Simulink Building A Direct Sequence Spread Spectrum ModelDocumento7 páginasMatlab, Simulink Building A Direct Sequence Spread Spectrum Modelsir_jon43100% (1)

- Matlab Laboratory 1. Introduction To MATLABDocumento8 páginasMatlab Laboratory 1. Introduction To MATLABRadu NiculaeAinda não há avaliações

- Module 5Documento21 páginasModule 51232023Ainda não há avaliações

- Ab Inition ScenarioDocumento28 páginasAb Inition ScenarioSandeep ShawAinda não há avaliações

- Assignment 3Documento6 páginasAssignment 3Aditya PriyadarshiAinda não há avaliações

- Simple Exercises in Matlab/Simulink IIDocumento8 páginasSimple Exercises in Matlab/Simulink IIGarunendra BunkarAinda não há avaliações

- LAN Lab 2 ManualDocumento10 páginasLAN Lab 2 ManualsalimmanzurAinda não há avaliações

- Lab1 - Vlsi EceDocumento19 páginasLab1 - Vlsi EceMichelleCYLAinda não há avaliações

- Exp1 dSPACEDocumento19 páginasExp1 dSPACEVisheshAinda não há avaliações

- Lab 4Documento5 páginasLab 402chng.jiadeAinda não há avaliações

- Tutorial4 Layout and DRC of OP-AMPDocumento3 páginasTutorial4 Layout and DRC of OP-AMPmerdafedidaAinda não há avaliações

- Test 2 Cheat SheetDocumento2 páginasTest 2 Cheat SheetAnand Krishna GhattyAinda não há avaliações

- Huang Yunteng 1997Documento172 páginasHuang Yunteng 1997Anand Krishna GhattyAinda não há avaliações

- Project DescriptionDocumento1 páginaProject DescriptionAnand Krishna GhattyAinda não há avaliações

- Hilton Floor PlanDocumento1 páginaHilton Floor PlanAnand Krishna GhattyAinda não há avaliações

- ADCsurveyDocumento65 páginasADCsurveyAnand Krishna GhattyAinda não há avaliações

- Interpolation & Decimation: - Sampling Period at The OutputDocumento32 páginasInterpolation & Decimation: - Sampling Period at The OutputAnand Krishna GhattyAinda não há avaliações

- For If Else End End For End: %plot (F, Func,'x',f, Func2,'.',f, Func3,'o')Documento2 páginasFor If Else End End For End: %plot (F, Func,'x',f, Func2,'.',f, Func3,'o')Anand Krishna GhattyAinda não há avaliações

- MontecarloDocumento44 páginasMontecarloAnand Krishna GhattyAinda não há avaliações

- FactorialDocumento4 páginasFactorialAnand Krishna GhattyAinda não há avaliações

- 1762 Um002 - en PDocumento144 páginas1762 Um002 - en PDavid LucioAinda não há avaliações

- SAP ABAP ResumeDocumento3 páginasSAP ABAP Resumeshakti1392821Ainda não há avaliações

- C ElanchezhianDocumento8 páginasC ElanchezhiankeshavuvceAinda não há avaliações

- Design of Staircase by Limit State Method UNIT-5: C.risers Minus OneDocumento5 páginasDesign of Staircase by Limit State Method UNIT-5: C.risers Minus OneVAIJAYANTHI PAinda não há avaliações

- RedBull MediaHouseDocumento15 páginasRedBull MediaHousedr989981Ainda não há avaliações

- Profile Measurement Full ReportDocumento16 páginasProfile Measurement Full ReportAman RedhaAinda não há avaliações

- Software: Measurlink Is An Easy-To-Use, Windows-Based Family of Quality Data Management Software ApplicationsDocumento8 páginasSoftware: Measurlink Is An Easy-To-Use, Windows-Based Family of Quality Data Management Software ApplicationsBrandi DaleAinda não há avaliações

- FORCE CatalogueDocumento85 páginasFORCE CatalogueMaterialsOne100% (1)

- Felkoder Jeep Grand Cherokee 1993Documento41 páginasFelkoder Jeep Grand Cherokee 19931LEFFEAinda não há avaliações

- ASH ReportDocumento3 páginasASH ReportChandra SekharAinda não há avaliações

- Android User GuideDocumento15 páginasAndroid User GuideAnonymous 1Wb6JCkAinda não há avaliações

- Lec 2 - Tall Building Criteria and Loading-2003Documento30 páginasLec 2 - Tall Building Criteria and Loading-2003JibonGhoshPritomAinda não há avaliações

- Cu Ext 2015Documento4 páginasCu Ext 2015mohammedzuluAinda não há avaliações

- VLSI Design FlowDocumento20 páginasVLSI Design FlowPranav DarganAinda não há avaliações

- Introduction To Boltzmann LearningDocumento2 páginasIntroduction To Boltzmann LearningnvbondAinda não há avaliações

- SAS Hot Fix Analysis Download and Deployment ToolDocumento11 páginasSAS Hot Fix Analysis Download and Deployment ToolAdrian GallegosAinda não há avaliações

- Chhattisgarh Swami Vivekanand Technical University, BhilaiDocumento26 páginasChhattisgarh Swami Vivekanand Technical University, BhilaiSK BeharAinda não há avaliações

- IOT SyllabusDocumento3 páginasIOT Syllabuspoojan thakkarAinda não há avaliações

- Iare WCN Tutorial Question BankDocumento7 páginasIare WCN Tutorial Question BankVigneshAinda não há avaliações

- Diff BW CBO and RBODocumento2 páginasDiff BW CBO and RBORamreddy BollaAinda não há avaliações