Escolar Documentos

Profissional Documentos

Cultura Documentos

MTech 1st Semester

Enviado por

Anish Bansal0 notas0% acharam este documento útil (0 voto)

30 visualizações7 páginasADVANCED DIGITAL SIGNAL PROCESSING

INFORMATION AND COMMUNICATION THEORY

Direitos autorais

© © All Rights Reserved

Formatos disponíveis

DOCX, PDF, TXT ou leia online no Scribd

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoADVANCED DIGITAL SIGNAL PROCESSING

INFORMATION AND COMMUNICATION THEORY

Direitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato DOCX, PDF, TXT ou leia online no Scribd

0 notas0% acharam este documento útil (0 voto)

30 visualizações7 páginasMTech 1st Semester

Enviado por

Anish BansalADVANCED DIGITAL SIGNAL PROCESSING

INFORMATION AND COMMUNICATION THEORY

Direitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato DOCX, PDF, TXT ou leia online no Scribd

Você está na página 1de 7

MTEC-501-B ADVANCED DIGITAL SIGNAL PROCESSING

Class Work : 25 Marks

Theory : 75 Marks

Total : 100 Marks

Duration of Exam. : 3 Hrs.

UNIT I

Sampling and Multi rate Digital Signal Processing:

Sampling: Review of Basic Sampling theorem, Sampling for Band limited Signals with sampling

rate less than twice of maximum frequency, integer band positioning, Arbitrary band Positioning,

Reconstruction, sampling rate conversion.

Multi rate Signal Processing (MSP): Need for MSP, Increasing & Decreasing sampling rate by

integer factor (Interpolation & Decimation), Changing the sampling rate by rational factor,

Structures for sampling rate conversion: Polyphase Filter implementation, cascaded integrator

comb Filters; Multistage Structures, Applications of MSP.

UNIT II

Linear Prediction & Optimum Linear Filters:

Random Process, Stationary Random Process, Statistical/Ensemble Averages, Ensemble Averages

for joint Random Processes, Power Density Spectrum, Discrete Time Random Signals, Time-

Averages for a discrete-time Random Process, Mean Ergodicity, Correlation Ergodic Process.

Stationary Random Process Representation: AR, MA & ARMA Processes, autocorrelation sequence

and filter coefficients association; Linear Prediction: Backward & Forward; Optimum Reflection

coefficients for lattice backward & forward predictors, AR process and linear prediction

Relationship.

UNIT III

Power Spectrum Estimation:

Nonparametric methods: Spectra Estimation from finite duration Observations of signals:

Energy Density Spectrum, Autocorrelation and power spectrum of Random signals: The Period

gram; Use of DFT in Power Spectrum Estimation;

Nonparametric methods: Bartlett Method, The Welch Method, Blackman & Tukey method,

Performance characteristics of nonparametric power spectrum estimators, Computational

Requirements of Nonparametric Power Spectrum Estimates.

Parametric methods: Relationship between Autocorrelation and the Model parameters, Yule-

Walker method for AR Model Parameters, Burg method for AR model parameters, Unconstrained

Least Squares method for AR model parameters, Sequential Estimation methods for the AR Model

parameters, AR Model order selection, MA model for Power Spectrum Estimation, ARMA Model for

Power spectrum Estimation.

UNIT IV

Finite word length effects and DSP applications:

Finite word length effects in Digital Filters: Number Representation Systems: Binary, Fixed

Point Arithmetic, Floating Point Arithmetic, Number Quantization, Error due to coefficient

Quantization, Low Sensitive Realizations, Quantization of product, Signal Scaling, Output Round off

Noise Minimization, Limit Cycle Oscillations.

Applications of DSP: Applications to Speech Processing: Model of Speech production, Short-Time

Spectrum Analysis, Speech processing system, Homomorphic Processing of speech; Hilbert

Transformers, Adaptive Digital Filters: Wiener Filter, Newton Algorithm, Steepest Descent

Algorithm, Least Mean Square Algorithm, Recursive Filters, Applications of Adaptive Filters.

Text Books:

1. J. G. Proakis, D. G. Manolakis, Digital Signal Processing, Principles, Algorithms, & Applications,

Prentice Hall India.

2. L. R. Rabiner & B. Gold, Theory and Application of Digital Signal Processing, Prentice Hall

India.

Reference Books:

3. Andreas Antoniou, Digital Signal Processing, Signals, Systems, and Filters, Tata McGraw Hill\

4. V. Oppenheim, R. W. Schafer, J. R. Buck, Discrete Time Signal Processing, Prentice Hall

India.

5. V. Oppenheim, R. W. Schafer, Digital Signal Processing, Prentice Hall India.

MTEC-503-B INFORMATION AND COMMUNICATION THEORY

Class Work : 25 Marks

Theory : 75 Marks

Total : 100 Marks

Duration of Exam. : 3 Hrs.

UNIT I

Field Algebra: Introduction, Binary operations, Groups, Characteristics of the field, Binary field

arithmetic, Galois field, vector spaces, matrices.

Block Codes: Linear block codes, The Generator & parity check matrices, Syndrome decoding,

Hamming codes, BCH codes, Reed Solomon codes, Justeen codes, MDS code, Reed Muller Code.

UNIT II

Channel Coding: Waveform Coding, types of error control, structured sequences, error detecting

and correcting capability, usefulness of standard array, cyclic codes, interleaving and concatenated

codes, coding and interleaving applied to the compact disc, turbo codes.

Source Coding: Sources, amplitude quantizing, adaptive prediction, transform coding, source

coding for digital data, examples of source coding.

UNIT III

Modulation and coding tradeoffs :Goals of communication system designer, error probability

plane, Nyquist minimum bandwidth, Shannon Hartley capacity theorem, bandwidth efficiency

plane, modulation and coding tradeoffs, designing and evaluating digital communication systems,

bandwidth efficient modulation, modulation and coding for band limited channels, trellis coded

modulation

Performance of codes: Performance of linear block codes & convolution codes, Bounds on code

performance, Bounds on error performance.

UNIT IV

Estimation and Hypothesis Testing: Time and Ensemble Averages, Covariance and Correction

Functions. Simple binary hypothesis tests, Decision Criteria, Neyman Pearson tests, Bayes Criteria,

Multiple Hypothesis testing, Composite hypothesis testing, Asymptotic Error rate of LRT for simple

hypothesis testing.

Properties of Estimators and filtering: Unbiasedness, efficiency, C-R bound, asymptotic

properties, Wiener filter, Kalman filter.

Text Books:

1. Bernard Skylark & Pabitra Kumar Ray, Digital communications Fundamentals and Applications,

Pearson

2. J. Das., S.K. Mullik & P.K. Chatterjee, Principles of digitals communication, New Age

International Publishers

3. Papoulis, Athanasios, Probability Random Variables and Stochastic Processes, McGraw-Hill

(2008).

4. Taub Schilling, Principles of Communication Systems

5. Harry L Vantrees, Detection ,Estimation and modulation Theory A Willey Interscience Publication

Reference Books:

1. Statistical Signal Processing Detection, Estimation and Time-Series Analysis, Louis L. Scharf,

Addison-Wesley 1991,

ISBN 0-201-19038-9.

2. Probability, Random Processes, & Estimation Theory for Engineers, 3rd Edition, H. Stark & J. W.

Woods, 2002.

3. An Introduction to Signal Detection and Estimation, Vincent Poor, 2nd ed., 1991

4. L. Scharf, Statistical Signal Processing - Detection, Estimation and Time Series Analysis,

Addison-Wesley, 1991.

MTEC-505-B DIGITAL VLSI DESIGN

Class Work : 25 Marks

Theory : 75 Marks

Total : 100 Marks

Duration of Exam. : 3 Hrs.

UNIT I

Introduction: VLSI Design flow, Design hierarchy, VLSI design style, computer - Aided Design

Technology, Basic principle of MOS transistor, Introduction to large signal MOS models for digital

design, geometric scaling theory, small device models and effects.

The MOS Inverter: Inverter principle, Depletion and enhancement load inverters, the basic CMOS

inverter, transfer characteristics, logic threshold, Noise margins, and Dynamic behaviour, Latch-

up, Propagation Delay and Power Consumption.

UNIT II

Symbolic and Physical Layout Systems: MOS Layers Stick/Layout Diagrams, Layout Design

Rules, Transistor layout, Inverter layout, CMOS digital circuit layout Issues of Scaling, Scaling

factor for device parameters.

Performance Estimation: Resistance Estimation, Capacitance Estimation, Inductance Estimation,

Switching characteristics, CMOS-gate transistor Sizing,

UNIT III

Combinational Logic Structures: CMOS Logic Families - static, dynamic and differential logic

families, CMOS Complimentary logic, Pseudo NMOS logic, Dynamic CMOS logic, CMOS Domino

logic, Clocked CMOS logic, pass Transistor logic, transmission gates logic circuits, complimentary

switch logic.

Sequential Logic Design: SR latches, Flip flops: JK, D, Master- Slave & Edge triggered.

Registers, CMOS Schmitt trigger.

UNIT IV

Subsystem Design: Design of an ALU Subsystem: design 4-bit simple and carry look ahead

adder, multiplier design: serial-parallel multiplier, Braun Array, Wallace tree Multiplier, Design of

4-bit Shifter.

Low Power CMOS Logic: overview of power consumption, Low power design: Voltage Scaling,

optimization of switching activity.

Text Books:

1. J. M. Rabaey, A. P. Chandrakasan and B. Nikolic, Digital Integrated Circuits Second Edition,

PH/Pearson, 2003.

2. D. A. Pucknell and K. Eshraghian, Basic VLSI Design, Third Edition, PHI, 1994.

3. S. M. Kang and Y. Leblebici, CMOS Digital Integrated Circuits : Analysis and Design, Third

Edition, MH, 2002

Reference Books:

1. W. Wolf, Modern VLSI Design: System on Chip, Third Edition, PH/Pearson, 2002.

2. N. Weste, K. Eshraghian and M. J. S. Smith, Principles of CMOS VLSI Design Pearson, 2001.

3. John P.Uyemura, CMOS Logic Circuit Design

MTEC-507-B ADVANCED MICROPROCESSORS & APPLICATIONS

Class Work : 25 Marks

Theory : 75 Marks

Total : 100 Marks

Duration of Exam. : 3 Hrs.

UNIT I

DESIGN OF MICROPROCESSOR: Design of basic microprocessor architectural Concepts:

Microprocessor architecture, word Lengths, addressable memory, and Microprocessors speed

architectural characteristics, registers, instruction, memory addressing architecture, ALU, GPR's

Control logic & internal data bus.

MICROPROCESSOR INSTRUCTIONS & COMMUNICATION: Instruction Set, Mnemonics, Basic

Instruction Types, Addressing modes, Microprocessor I/O connecting I/O put to Microprocessor,

Polling and Interrupts, Interrupt and DM. Controllers.

UNIT II

ADVANCED MICROPROCESSOR: Advanced microprocessors: Intel X86 family of advanced

Microprocessor, programming model of 86 families, X86 addressing modes, instruction set,

hardware.

HIGH PERFORMANCE CISC ARCHITECTURE (PENTIUM): The software model, functional

description, CPU pin descriptions, RISC concepts, bus operations, super scalar architecture, pipe-

lining, Branch prediction.

UNITIII

PENTIUM PROCESSOR: The instruction and caches, Floating point unit, protected mode

operation, Segmentation, paging, multitasking, Exception and interrupts, Input / Output, Virtual

8086 model, Interrupt processing,

INSTRUCTIONS & PROGRAMMING WITH PENTIUM PROCESSOR: Instruction types,

Addressing modes, Processor flags, Instruction set, Basic programming the Pentium Processor.

UNIT IV

PENTIUM PROCESSOR I/O: Data Communication, parallel I/O serial communication, Serial

interface and UART modems, I/O devices, D/A, A/D interface, special I/O devices.

DEVELOPING PENTIUM PROCESSOR BASED APPLICATIONS: Introduction to the Design

Process, Preparing the specifications, Developing a design, Implementing and Testing and design,

Regulatory Compliance Testing, design tool for Development.

MTEC-509-B OPTIMIZATION TECHNIQUES

Class Work : 25 Marks

Theory : 75 Marks

Total : 100 Marks

Duration of Exam. : 3 Hrs.

UNIT I

Introduction: Operation Research Models, OR Model, Queuing & Simulation Models, Two Variable

LP Model, Graphical LP solution, Computer Solution with solver & AMPL, Linear Programming

Applications.

Sensitivity & Post Optimal Analysis: LP Model in Equation Form, Algebraic Solution, Simplex

Method, Artificial Starting Solution, Sensitivity Analysis, Dual Problem, Primal-Dual Relationships,

Economic Interpretation of Duality, Additional Simplex Algorithms, Post Optimal Analysis.

UNIT II

Models: Transportation Models and its variants, Transportation Algorithms, Assignment Models,

Shortest Route Problem and its Algorithms, Maximal Flow Model, CPM & PERT.

Programming: Simplex Method Fundamentals, Bounded Variables Algorithms, Parametric Linear

Programming, Goal Programming Algorithms, Integer Linear Programming & Algorithms, Heuristic

Programming, Greedy Heuristics, Meta Heuristics, TSP Algorithms(B&B, Cutting Plain, Nearest

Neighbour, Reversal Heuristic, Tabu, Simulated Annealing, Genetic), Deterministic & Dynamic

Programming.

UNIT III

Markov Chains: Continuous Review Models, Single & Multi Period Models, Absolute & n-step

Transition Probabilities, State in Markov Chain, First Passage Time, Analysis of Absorbing States.

Queuing Models: Elements of Queuing Model, Role of Exponential Distribution, Pure Birth &

Death Model, Specialized Poisson Queues, P-K Formula, Queuing Decision Models.

UNIT IV

Simulation Modeling: Monte Carlo Simulation, Type of Simulations, Unconstrained Problems,

Constrained Problems, Direct Search Method, Gradient Method, Separable, Quadratic, Chance-

Constrained Linear Combinations & SUMT Programming Algorithms.

Text and Reference Books:

1. Operation Research By Taha Pearson

2. Probability & Statistics with Reliability, Queuing & Computer Serine Application- Kishor S.

Trivedi Willey

3. Mathematical Modeling Principles & Applications:- CENGAGE Learning, Frank R. Giordano,

William P. Fox.

MTEC-531-B DIGITAL VLSI DESIGN LAB

Class Work : 20 Marks

Exams : 30 Marks

Total : 50 Marks

LIST OF EXPERIMENTS:

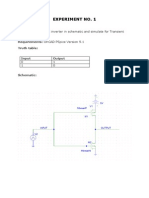

1. Design a CMOS inverter in schematic and simulate for Transient Characteristics.

2. Design a CMOS two input NAND gate, Two input NOR gate, Two input AND gate and

Two input OR gate in schematic and

simulate for Transient Characteristics.

3. Design the layout of a CMOS Inverter and simulate for DC (Transfer) and Transient

characteristics.

4. Design the layout for two inputs NAND gate, two input OR gate, two input AND gate

and two input NOR gate and simulate for

DC (Transfer) and Transient characteristics.

5. Realized a two input EXOR gate in schematic, draw its layout and simulate for DC

(Transfer) and Transient characteristics.

6. To realize a 1 bit full adder in CMOS schematic, design its layout using tool option and

simulate for Transient Characteristics.

7. To realize a Boolean expression Y=Not ((A+B)(C+D)E) in schematic, draw its layout

and simulate for Transient

Characteristics..

8. To realize a 4 X 1 MUX using transmission gates in schematic and simulate for

Transient Characteristics..

9. To Realize JK FLIPFLOP in CMOS schematic, design its layout and simulate for

Transient Characteristics.

10. To Realize D FLIPFLOP and T FLIPFLOP in CMOS schematic, design its layout and

simulate for Transient Characteristics.

11. To realize a four bit asynchronous counter using T flip-flop as a cell in schematic and

simulate for Transient Characteristics.

12. To realize a four bit shift register using D flip-flop as a cell in schematic and simulate

for Transient Characteristics.

MTEC-537-B ADVANCED MICROPROCESSORS & APPLICATIONS LAB

Class Work : 20 Marks

Exams : 30 Marks

Total : 50 Marks

LIST OF EXPERIMENTS:

(A few experiments may be designed & included in this list depending upon the

infrastructure available in the institute)

1. To study the architecture of Microprocessor 8086 Kit

2. Write an ALP to convert a hexadecimal No. to decimal No. in single step execution

(DEBUG)

3. Write an ALP to enter a word from keyboard and to display

4. Write an ALP for addition of two one digit Numbers.

5. Write an ALP to display a string

6. Write an ALP reverse a string

7. Write an ALP to check whether the No. is Palindrome

8. To study the MIcrocontroller Kit

9. Write an ALP to generate 10 KHz frequency square wave

10. Write an ALP to generate 10 KHz & 100KHz frequency using interrupt

11. Write an ALP to interface intelligent LCD display

12. Write an ALP to interface intelligent LED display

13. Write an ALP to Switch ON alarm when Microcontroller receive interrupt

14. Write an ALP to interface one microcontroller with other using serial / parallel

communication

Você também pode gostar

- SAP NetWeaver BIDocumento1 páginaSAP NetWeaver BIAnish BansalAinda não há avaliações

- Digital Image Processing Lab QuestionsDocumento2 páginasDigital Image Processing Lab QuestionsAnish Bansal100% (2)

- Biodata PERSONAL INFORMATIONDocumento1 páginaBiodata PERSONAL INFORMATIONAnish Bansal67% (3)

- Index Dvlsi: S. No. Experiment Name Date SignatureDocumento1 páginaIndex Dvlsi: S. No. Experiment Name Date SignatureAnish BansalAinda não há avaliações

- Index: S. No. Experiment Name Date SignatureDocumento1 páginaIndex: S. No. Experiment Name Date SignatureAnish BansalAinda não há avaliações

- Experiment No. 8: MATLAB ProgramDocumento2 páginasExperiment No. 8: MATLAB ProgramAnish BansalAinda não há avaliações

- Qualnet Lab FileDocumento1 páginaQualnet Lab FileAnish Bansal0% (1)

- Nand Nor Gate Vlsi dIGITAL DESIGNDocumento8 páginasNand Nor Gate Vlsi dIGITAL DESIGNAnish BansalAinda não há avaliações

- Program For Image Compression Using 2-D Discrete Cosine Transform.Documento3 páginasProgram For Image Compression Using 2-D Discrete Cosine Transform.Anish BansalAinda não há avaliações

- Write A Program To Generate Histogram For An Image and To Perform Histogram Equalization.Documento2 páginasWrite A Program To Generate Histogram For An Image and To Perform Histogram Equalization.Anish BansalAinda não há avaliações

- Design A 4×1 Multiplexer Using Pass Transistor Logic in Schematic and Simulate For Transient Characteristics.Documento6 páginasDesign A 4×1 Multiplexer Using Pass Transistor Logic in Schematic and Simulate For Transient Characteristics.Anish BansalAinda não há avaliações

- Synopsis Format DCRUSTDocumento1 páginaSynopsis Format DCRUSTAnish BansalAinda não há avaliações

- Design Xor Gate in SchematicDocumento5 páginasDesign Xor Gate in SchematicAnish BansalAinda não há avaliações

- Experiment No. 1: Aim: Design A CMOS Inverter in Schematic and Simulate For TransientDocumento5 páginasExperiment No. 1: Aim: Design A CMOS Inverter in Schematic and Simulate For TransientAnish BansalAinda não há avaliações

- Advanced Electronics Instrumentation MTEC-502-BDocumento6 páginasAdvanced Electronics Instrumentation MTEC-502-BAnish BansalAinda não há avaliações

- Chapter 2-1. Semiconductor Models: E H H Planck's Constant (H 6.63Documento6 páginasChapter 2-1. Semiconductor Models: E H H Planck's Constant (H 6.63Anish BansalAinda não há avaliações

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNo EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNota: 4 de 5 estrelas4/5 (5794)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNo EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNota: 4 de 5 estrelas4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)No EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Nota: 4 de 5 estrelas4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingNo EverandThe Little Book of Hygge: Danish Secrets to Happy LivingNota: 3.5 de 5 estrelas3.5/5 (400)

- The Emperor of All Maladies: A Biography of CancerNo EverandThe Emperor of All Maladies: A Biography of CancerNota: 4.5 de 5 estrelas4.5/5 (271)

- Never Split the Difference: Negotiating As If Your Life Depended On ItNo EverandNever Split the Difference: Negotiating As If Your Life Depended On ItNota: 4.5 de 5 estrelas4.5/5 (838)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyNo EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyNota: 3.5 de 5 estrelas3.5/5 (2259)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNo EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNota: 4.5 de 5 estrelas4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNo EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNota: 3.5 de 5 estrelas3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnNo EverandTeam of Rivals: The Political Genius of Abraham LincolnNota: 4.5 de 5 estrelas4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNo EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNota: 4.5 de 5 estrelas4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNo EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNota: 4.5 de 5 estrelas4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaNo EverandThe Unwinding: An Inner History of the New AmericaNota: 4 de 5 estrelas4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNo EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNota: 4 de 5 estrelas4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)No EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Nota: 4.5 de 5 estrelas4.5/5 (121)

- OOPM Theory QuestionsDocumento7 páginasOOPM Theory Questionssheenam_bhatiaAinda não há avaliações

- PPT 6 Pms-Remaining Service LifeDocumento22 páginasPPT 6 Pms-Remaining Service LifeSwagata SarkarAinda não há avaliações

- Isoparametric Elements.: - Finite Element Method For Structural AnalysisDocumento12 páginasIsoparametric Elements.: - Finite Element Method For Structural AnalysisAlvaro Garnica TrujilloAinda não há avaliações

- ASB-410 JQL in Jira Service Desk Slides and NotesDocumento198 páginasASB-410 JQL in Jira Service Desk Slides and NotesCarlos GarciaAinda não há avaliações

- Le y Yang - Tiny ImageNet Visual Recognition ChallengeDocumento6 páginasLe y Yang - Tiny ImageNet Visual Recognition Challengemusicalización pacíficoAinda não há avaliações

- Sek - Men.Keb. Tinggi Melaka (Malacca High School. Estd.1826)Documento19 páginasSek - Men.Keb. Tinggi Melaka (Malacca High School. Estd.1826)Lee Shi HockAinda não há avaliações

- Power SeriesDocumento2 páginasPower SeriesAbhi DebAinda não há avaliações

- Chapter 1 Assignment What Is Statistics?Documento2 páginasChapter 1 Assignment What Is Statistics?mimoAinda não há avaliações

- C Sample Two Mark Question and Answer: 1) Who Invented C Language?Documento13 páginasC Sample Two Mark Question and Answer: 1) Who Invented C Language?rajapst91% (11)

- Math PDFDocumento95 páginasMath PDFAnonymous kI39sJC1MAinda não há avaliações

- A New Versatile Electronic Speckle Pattern Interferometer For VibDocumento318 páginasA New Versatile Electronic Speckle Pattern Interferometer For Vibssunil7432Ainda não há avaliações

- Eu 2Documento15 páginasEu 2Ayush BhadauriaAinda não há avaliações

- Engineering Mathematics1 2015 PDFDocumento24 páginasEngineering Mathematics1 2015 PDFsenyonjo emmaAinda não há avaliações

- RM 4Documento37 páginasRM 4RHEALYN GEMOTOAinda não há avaliações

- Example: Triangle On A Face IconDocumento26 páginasExample: Triangle On A Face IconGinalyn QuimsonAinda não há avaliações

- 01otr 02ourDocumento53 páginas01otr 02ourKeerthana KAinda não há avaliações

- Deflection Considerations in Two-Way Reinforced CoDocumento13 páginasDeflection Considerations in Two-Way Reinforced CoHamid HassanzadaAinda não há avaliações

- Indian Institute of Technology Kharagpur Department of Mathematics MA11003 - Advanced Calculus Assignment - 1 Autumn 2020Documento1 páginaIndian Institute of Technology Kharagpur Department of Mathematics MA11003 - Advanced Calculus Assignment - 1 Autumn 2020Harsh GuptaAinda não há avaliações

- Why Textbooks Count Tim OatesDocumento23 páginasWhy Textbooks Count Tim OatesnguyenhoaianhthuAinda não há avaliações

- Programmable Logic ControllersDocumento31 páginasProgrammable Logic Controllersgpz10100% (15)

- CDMA Simulation: Alison Hightman Elaine Chung Alejandra GalvanDocumento30 páginasCDMA Simulation: Alison Hightman Elaine Chung Alejandra GalvanericnaneAinda não há avaliações

- 34ee79a9746d853ef9fa1f44acc55afeDocumento51 páginas34ee79a9746d853ef9fa1f44acc55afeSai Pavan MarojuAinda não há avaliações

- Ip AdaptorDocumento16 páginasIp Adaptorlaure9239Ainda não há avaliações

- 2139 12021 1 PB PDFDocumento9 páginas2139 12021 1 PB PDFSantosh Kumar PandeyAinda não há avaliações

- 33 As Statistics Unit 5 TestDocumento2 páginas33 As Statistics Unit 5 TestThomas BeerAinda não há avaliações

- Sabour & Poulin 2006Documento22 páginasSabour & Poulin 2006ali basyaAinda não há avaliações

- T M 34794 Representing Tenths Differentiated Activity Sheet - Ver - 1Documento7 páginasT M 34794 Representing Tenths Differentiated Activity Sheet - Ver - 1Thieu LeAinda não há avaliações

- How To Solve Fractions: Solving Quadratic EquationsDocumento7 páginasHow To Solve Fractions: Solving Quadratic Equationsapi-126876773Ainda não há avaliações

- 0607 QS026 - 2 PDFDocumento7 páginas0607 QS026 - 2 PDFjokydin92Ainda não há avaliações