Escolar Documentos

Profissional Documentos

Cultura Documentos

IR Drop Analysis

Enviado por

Rohith RajDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

IR Drop Analysis

Enviado por

Rohith RajDireitos autorais:

Formatos disponíveis

IR Drop Analysis ~ VLSI Basics And Interview Questions

file:///C|/Users/COMSOL/Desktop/IR%20Drop%20Analysis.htm[7/16/2014 8:22:07 PM]

IR Drop Analysis

What i s I R Dr op Anal ysi s? How i t ef f ec t s t he t i mi ng?

The power supply in the chip is distributed uniformly through metal layers (Vdd and

Vss) across the design. These metal layers have finite amount of resistance. When

voltage is applied to this metal wires current start flowing through the metal layers

and some voltage is dropped due to that resistance of metal wires and current. This

Drop is called as IR Drop. For example, a design needs to operate at 2 volts and has

a tolerance of 0.4 volts on either side, we need to ensure that the voltage across its

power pin (Vdd) and ground pin (Vss) in that design does not fall short of 1.6

Volts.The acceptable IR drop in this context is 0.4 volts. That means the design in this

context can allow upto 0.4 volts drop which does not effect the timing and

functionality of design.

How i t ef f ec t s t he t i mi ng?

IR Drop is Signal Integrity(SI) effect caused by wire resistance and current drawn off

Get this

VLSI Basics And Interview Questions

This Blog is created for Basic VLSI Interview Questions. This content is purely VLSI Basics.

IR Drop Analysis ~ VLSI Basics And Interview Questions

file:///C|/Users/COMSOL/Desktop/IR%20Drop%20Analysis.htm[7/16/2014 8:22:07 PM]

from Power (Vdd) and Ground (Vss) grids. According to Ohms law, V = IR. If wire

resistance is too high or the current passing through the metal layers is larger than

the predicted, an unacceptable Voltage drop may occur. Due to this un acceptable

voltage drop, The power supply voltage decreases. That means the required power

across the design is not reaching to the cells. This results in increased noise

susceptibility and poor performance.

The design may have different types of gates with different voltage levels. As the

voltage at gates decreased due to unacceptable voltage drop in the supply voltage,

the gate delays are increased non-linearly. This may lead to setup time and hold time

violations depending on which path these gates are residing in the design. As

technology node shrinking, there is decrease in the geometries of the metal layers

and the resistance of this wires increased which lead to decrease in power supply

voltage. During Clock Tree Synthesis, the buffers and inverters are added along the

clock path to balance the skew. The voltage drop on the buffers and inverters of clock

path will cause the delay in arrival of clock signal, resulting hold violation.

What ar e t he t ool s used f or I R Dr op Anal ysi s? I n w hi c h st age I R Dr op

Anal ysi s per f or med ?

Various tools are available for IR Drop Analysis. Voltagestorm from Cadence,

Redhawk from Apache are mainly used to show IR Drop on chip. Here we are going

to discuss about IR Drop using Redhawk. IR Drop Analysis using Redhawk is

possible at different stages of the design flow. When changes are in expensive and

they don't effect project's schedule, It is better to use Redhawk for IR drop analysis

from start of the design cycle. It can identify and fix power grid problems in the

design. This also reduces changes required in sign-off stage where final static and

dynamic voltage (IR) drops performed. So Redhawk can be used anywhere in the

design starting from the floorplanning stage through initial and final cell placement

stages.

Recommend this on Google

IR Drop Analysis ~ VLSI Basics And Interview Questions

file:///C|/Users/COMSOL/Desktop/IR%20Drop%20Analysis.htm[7/16/2014 8:22:07 PM]

Newer Post Older Post Home

12:16

KHADAR BASHA

NO COMMENTS

Related Posts:

Fl oor pl an Cont r ol Par amet er s

The following are the Control Parameters during Floorplan 1. Aspect Ratio: Core

Utilization Aspect ratio (H/W) Row/Core ratio 2.Width and Height: Width Height

Row/Core ratio 1. Aspect Ratio (Ar): Aspect ratio i Read More

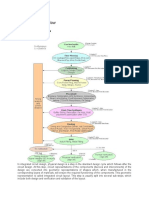

Physi c al Desi gn Fl ow

Physical Design Flow: The design flow of the physical implementation is mentioned

above in the figure. The physical design stage of the design flow is also known as the

place and route stage. This is based upon t Read More

I R Dr op Anal ysi s

What is IR Drop Analysis? How it effects the timing? The power supply in the chip is

distributed uniformly through metal layers (Vdd and Vss) across the design. These

metal layers have finite amount of resistance. When v Read More

Basi c Ter mi nol ogy i n Physi c al Desi gn

Design: A circuit that performs one or more logical functions. Cell: An instance of a

design or library primitive within a design. Port: The input or output of a design.

Pin: The input or output of a cell. Net: A wire t Read More

Fl oor pl anni ng

Floorplanning: Floorplanning includes macro/block placement, pin placement, power

planning, and power grid design. What makes the job more important is that the

decisions taken for macro/block placement, I/O-pad placement Read More

IR Drop Analysis ~ VLSI Basics And Interview Questions

file:///C|/Users/COMSOL/Desktop/IR%20Drop%20Analysis.htm[7/16/2014 8:22:07 PM]

0 comments:

Post a Comment

Notify me

Comment as:

Writing a business plan Download Download open office Internet Marketer Links

Function Performance Management SoftwareDownloads Or Library Inverter

Popular Posts

Static Timing Analysis (STA) Interview Questions

Static Timing Analysis Interview Questions Static Timing Analysis plays major role in physical

design(PD) flow. It checks the design...

IR Drop Analysis

What is IR Drop Analysis? How it effects the timing? The power supply in the chip is distributed

uniformly through metal layers (Vdd a...

Physical Design (PD) Interview Questions - Floorplanning

1. What is floorplaning? A. Floor planing is the process of placing Blocks/Macros in the chip/core

Publish Preview

IR Drop Analysis ~ VLSI Basics And Interview Questions

file:///C|/Users/COMSOL/Desktop/IR%20Drop%20Analysis.htm[7/16/2014 8:22:07 PM]

area, thereby determining ...

Clock Tree Synthesis (CTS) - Overview

Clock Tree Synthesis Clock Tree Synthesis (CTS) is the process of inserting buffers/inverters along

the clock paths of the ASIC design to...

Low Power Design

Power Planning: Power is limiting factor affection performance and features in most important

products. When you decided to buy a mobile,...

IR Drop Analysis Interview Questions

IR Drop Analysis Interview Questions 1. What is IR Drop Analysis? A. The power supply in the chip is

distributed uniformly through met...

Static Timing Analysis (STA) Overview

Timing Analysis: Timing Analysis is a method of validating the timing performance of a design. i.e.

How fast the design is going to oper...

Physical Design Flow

Physical Design Flow: The design flow of the physical implementation is mentioned above in the

figure. The physical design stag...

Basic Terminology in Physical Design

Design: A circuit that performs one or more logical functions. Cell: An instance of a design or library

primitive within a design. P...

Power Planning - Power Network Synthesis (PNS)

Power Planning - Power Network Synthesis (PNS) In ICC Design Planning flow, Power Network

Synthesis creates macro power rings, creates th...

Blog Archive

2014 (5)

2013 (21)

December (2)

IR Drop Analysis ~ VLSI Basics And Interview Questions

file:///C|/Users/COMSOL/Desktop/IR%20Drop%20Analysis.htm[7/16/2014 8:22:07 PM]

October (6)

September (2)

August (4)

IR Drop Analysis

Basic Terminology in Physical Design

Low Power Design

Blockages and Halos

J uly (6)

March (1)

Recent Posts

Definition List

Text Widget

Pages

IR Drop Analysis ~ VLSI Basics And Interview Questions

file:///C|/Users/COMSOL/Desktop/IR%20Drop%20Analysis.htm[7/16/2014 8:22:07 PM]

Home

Site Index - Content

VLSI Interview Questions

VLSI Video Tutorials

VLSI Books

About Us - Contact Us

Total Pageviews

Copyright @ VLSI Basics Team . Powered by Blogger.

Physical Design Tutorials

4 2 6 1 9

IR Drop Analysis ~ VLSI Basics And Interview Questions

file:///C|/Users/COMSOL/Desktop/IR%20Drop%20Analysis.htm[7/16/2014 8:22:07 PM]

Follow by Email

Contributors

vlsi.projectguru

khadar basha

VLSI Basics Team

+1

Recommend this on Google

Follow us on Twitter Now

Fol l ow @VLSI Basi c s 4 followers

Submit

IR Drop Analysis ~ VLSI Basics And Interview Questions

file:///C|/Users/COMSOL/Desktop/IR%20Drop%20Analysis.htm[7/16/2014 8:22:07 PM]

COPYRIGHT 20142014 VLSI BASICS AND INTERVIEW QUESTIONS | POWERED BY

BLOGGER

DESIGN BY AUTOMATTIC | BLOGGER THEME BY NEWBLOGGERTHEMES.COM

Search This Blog

Infolinks Text Ads

Subscribe To

Posts

Comments

Search

Você também pode gostar

- VLSI Test Principles and Architectures: Design for TestabilityNo EverandVLSI Test Principles and Architectures: Design for TestabilityNota: 4.5 de 5 estrelas4.5/5 (4)

- SignOff checks: DRC, LVS, IR Drop, EM, Scan Tracing & DFMDocumento15 páginasSignOff checks: DRC, LVS, IR Drop, EM, Scan Tracing & DFMPraveen Ramesh KarnamAinda não há avaliações

- Physical Design FlowDocumento42 páginasPhysical Design Flowelumalaianitha100% (1)

- VLSI Interview Questions 2 2Documento18 páginasVLSI Interview Questions 2 2Rohith RajAinda não há avaliações

- High Fanout Nets Optimized in Design CompilerDocumento26 páginasHigh Fanout Nets Optimized in Design CompilerAditya Devarakonda100% (3)

- From RTL To GDS Using Synopsys Flow Within Less Then 10 WeeksDocumento15 páginasFrom RTL To GDS Using Synopsys Flow Within Less Then 10 WeeksLohitAinda não há avaliações

- VLSI Interview Questions - RoutingDocumento36 páginasVLSI Interview Questions - Routing3nadhs100% (1)

- Physical Design Interview QuestionsDocumento37 páginasPhysical Design Interview Questionsmaheshsamanapally100% (1)

- Interview VlsiDocumento47 páginasInterview VlsiKulwant Nagi100% (1)

- PD InterviewDocumento8 páginasPD InterviewPraveen Ramesh KarnamAinda não há avaliações

- PD Flow I - Floorplan - Physical Design, STA & Synthesis, DFT, Automation & Flow Dev, Verification Services. Turnkey ProjectsDocumento21 páginasPD Flow I - Floorplan - Physical Design, STA & Synthesis, DFT, Automation & Flow Dev, Verification Services. Turnkey ProjectsShwethAinda não há avaliações

- ASIC and Physical Design QuestionsDocumento46 páginasASIC and Physical Design QuestionsKool Rakesh100% (1)

- Interview QuestionsDocumento23 páginasInterview QuestionsSumanth VarmaAinda não há avaliações

- Special CelllsDocumento14 páginasSpecial Celllspdnoob100% (4)

- Backend (Physical Design) Interview Questions and AnswersDocumento11 páginasBackend (Physical Design) Interview Questions and AnswersJanarthanan DevarajuluAinda não há avaliações

- PD InterviewqsDocumento3 páginasPD Interviewqschakra_024100% (2)

- Backend (Physical Design) Interview Questions and Answers - BipeenKulkarniDocumento30 páginasBackend (Physical Design) Interview Questions and Answers - BipeenKulkarniRohith RajAinda não há avaliações

- ASIC Physical Design Interview QuestionsDocumento10 páginasASIC Physical Design Interview QuestionsRohith Raj50% (2)

- PrimeTime SlidesDocumento47 páginasPrimeTime SlidesRamakrishnaRao SoogooriAinda não há avaliações

- Vlsi FaqsDocumento29 páginasVlsi Faqsanon-417212100% (4)

- Wire Load ModelDocumento18 páginasWire Load Modelvincentvln100% (1)

- Physical Design PD Interview Questions PDFDocumento17 páginasPhysical Design PD Interview Questions PDFVamsi Krishna100% (1)

- ASIC PHYSICAL DESIGN - Backend (Physical Design) Interview Questions and AnswersDocumento7 páginasASIC PHYSICAL DESIGN - Backend (Physical Design) Interview Questions and Answersdinesh reddy100% (1)

- Ir Drop and Electro Migeration Desing Flow PDFDocumento29 páginasIr Drop and Electro Migeration Desing Flow PDFSonu SangwanAinda não há avaliações

- Physical Verification1Documento163 páginasPhysical Verification1Praveen Kumar100% (1)

- Summary of Rtl-To-Gdsii Tool Flow Using Synopsys DC and Cadence Soc EncounterDocumento3 páginasSummary of Rtl-To-Gdsii Tool Flow Using Synopsys DC and Cadence Soc EncounterUtkarsh AgrawalAinda não há avaliações

- CMOS Interview QuestionsDocumento4 páginasCMOS Interview QuestionsLuca Reni100% (1)

- Physical Design CompleteDocumento303 páginasPhysical Design CompleteVenkata KarthikAinda não há avaliações

- Synopsys PrimeTime - Introduction To Static Timing Analysis WorkshopDocumento21 páginasSynopsys PrimeTime - Introduction To Static Timing Analysis WorkshopApoorva Bhatt100% (2)

- STA CornersDocumento39 páginasSTA Cornerscannister100% (1)

- 7 CLK Tree SynthesisDocumento64 páginas7 CLK Tree Synthesisdharma_panga8217100% (1)

- Training 3Documento17 páginasTraining 3Thomas George100% (1)

- Primetime SynopsysDocumento3 páginasPrimetime SynopsysPrabakaran EllaiyappanAinda não há avaliações

- IntelDocumento5 páginasIntelrAM50% (2)

- Physical Design CompleteDocumento303 páginasPhysical Design CompleteReddicool89100% (47)

- Timing Analysis in Physical DesignDocumento32 páginasTiming Analysis in Physical Designgoud.mahesh0584269100% (2)

- Advanced Fusion Compiler Synthesis and P& R Technologies To Drive Performance andDocumento37 páginasAdvanced Fusion Compiler Synthesis and P& R Technologies To Drive Performance andyang hu100% (1)

- Vlsi Physical DesignDocumento26 páginasVlsi Physical Designilias ahmed100% (1)

- VLSI Basics And Interview Questions Macro PlacementDocumento3 páginasVLSI Basics And Interview Questions Macro Placementprasanna810243100% (1)

- System-on-Chip Test Architectures: Nanometer Design for TestabilityNo EverandSystem-on-Chip Test Architectures: Nanometer Design for TestabilityAinda não há avaliações

- MOS Integrated Circuit DesignNo EverandMOS Integrated Circuit DesignE. WolfendaleAinda não há avaliações

- Power Gating - Power Management Technique: VLSI Basics and Interview QuestionsDocumento12 páginasPower Gating - Power Management Technique: VLSI Basics and Interview QuestionsRohith RajAinda não há avaliações

- Physical Design Engineer Interview Questions & AnswersDocumento6 páginasPhysical Design Engineer Interview Questions & AnswersRohit SomkuwarAinda não há avaliações

- VLSI Design Lab NewDocumento45 páginasVLSI Design Lab NewmtariqanwarAinda não há avaliações

- Cadence Ir Drop MacroDocumento7 páginasCadence Ir Drop MacroAnil Babu NamalaAinda não há avaliações

- ASIC Interview QuestionsDocumento6 páginasASIC Interview QuestionsNandeesh VeerannaAinda não há avaliações

- ASIC Backend Physical Design Questions - ElectronicsBus 2014Documento4 páginasASIC Backend Physical Design Questions - ElectronicsBus 2014Rohith RajAinda não há avaliações

- Electronics Research Paper TopicsDocumento8 páginasElectronics Research Paper Topicst1s1gebes1d3100% (1)

- Low Power Techniques For VLSI DesignDocumento6 páginasLow Power Techniques For VLSI DesignjainatinAinda não há avaliações

- ASIC Interview Questions 1Documento5 páginasASIC Interview Questions 1ramAinda não há avaliações

- Voltus151 LabsDocumento105 páginasVoltus151 LabsNguyen Hung0% (2)

- 3096 Batchdata 1540142462010Documento58 páginas3096 Batchdata 1540142462010Ashish BharatAinda não há avaliações

- The Extraction and Measurement of On-Die Impedance For Power Delivery AnalysisDocumento4 páginasThe Extraction and Measurement of On-Die Impedance For Power Delivery Analysissabkumar.rAinda não há avaliações

- Voltus-Fi Custom Power Integrity Solution - Electromigration and IR Drop at The Transistor Level - Industry Insights - Cadence Blogs - Cadence Community PDFDocumento3 páginasVoltus-Fi Custom Power Integrity Solution - Electromigration and IR Drop at The Transistor Level - Industry Insights - Cadence Blogs - Cadence Community PDFSudatta MohantyAinda não há avaliações

- PAPER 11 EDATool-BasedMethodologyfor ChandrasekarDocumento20 páginasPAPER 11 EDATool-BasedMethodologyfor ChandrasekarReynaldo LOERAAinda não há avaliações

- VLSI Design Lab NewDocumento48 páginasVLSI Design Lab NewJubin JainAinda não há avaliações

- Research Paper On LVDTDocumento8 páginasResearch Paper On LVDTgz49w5xr100% (1)

- HW Kakoee 2Documento105 páginasHW Kakoee 2ballisticanaAinda não há avaliações

- DWF13 Amf Ent T0194 PDFDocumento132 páginasDWF13 Amf Ent T0194 PDFsumitzz4737Ainda não há avaliações

- Cross Talk Details and RoutingDocumento29 páginasCross Talk Details and RoutingRohith RajAinda não há avaliações

- IR DropDocumento6 páginasIR DropRohith RajAinda não há avaliações

- Ch05 2Documento43 páginasCh05 2Aar Kay GautamAinda não há avaliações

- Basic Terminology in Physical Design VLSI Basics and Interview QuestionsDocumento14 páginasBasic Terminology in Physical Design VLSI Basics and Interview QuestionsRohith RajAinda não há avaliações

- 10-Transistor Full Adder Design Based On Degenerate Pass Transistor LogicDocumento4 páginas10-Transistor Full Adder Design Based On Degenerate Pass Transistor LogicRohith RajAinda não há avaliações

- MOS EquationsDocumento1 páginaMOS EquationsYoni SolelAinda não há avaliações

- Buffer CircuitDocumento8 páginasBuffer CircuitRohith RajAinda não há avaliações

- Body Effect: What Do You Need To Know To Understand This Topic?Documento4 páginasBody Effect: What Do You Need To Know To Understand This Topic?Rohith RajAinda não há avaliações

- High Speed Low Power Adder For Error Tolerant Applications: Submitted To TheDocumento16 páginasHigh Speed Low Power Adder For Error Tolerant Applications: Submitted To TheRohith RajAinda não há avaliações

- Ee466 MOSCVDocumento5 páginasEe466 MOSCVRohith RajAinda não há avaliações

- Power Gating - Power Management Technique: VLSI Basics and Interview QuestionsDocumento12 páginasPower Gating - Power Management Technique: VLSI Basics and Interview QuestionsRohith RajAinda não há avaliações

- FinfetDocumento8 páginasFinfetRohith RajAinda não há avaliações

- Cmos FabricationDocumento57 páginasCmos FabricationRohith RajAinda não há avaliações

- Perl Basics 06Documento28 páginasPerl Basics 06Rohith RajAinda não há avaliações

- HspiceDocumento37 páginasHspiceRohith RajAinda não há avaliações

- Floorplan Control Parameters: VLSI Basics and Interview QuestionsDocumento10 páginasFloorplan Control Parameters: VLSI Basics and Interview QuestionsRohith RajAinda não há avaliações

- HSPICE TutorialDocumento16 páginasHSPICE TutorialSantiago PiñerosAinda não há avaliações

- ASIC Physical Design Interview QuestionsDocumento10 páginasASIC Physical Design Interview QuestionsRohith Raj50% (2)

- Physical Design Interview QuestionsDocumento32 páginasPhysical Design Interview QuestionsRohith Raj100% (3)

- Physical Design Interview Questions 2Documento3 páginasPhysical Design Interview Questions 2Rohith Raj50% (2)

- Physical Design (PD) Interview QuestionsDocumento17 páginasPhysical Design (PD) Interview QuestionsRohith RajAinda não há avaliações

- Backend (Physical Design) Interview Questions and Answers GGDocumento6 páginasBackend (Physical Design) Interview Questions and Answers GGRohith RajAinda não há avaliações

- ASIC-System On Chip-VLSI Design Backend (Physical Design) Interview Questions and AnswersDocumento7 páginasASIC-System On Chip-VLSI Design Backend (Physical Design) Interview Questions and AnswersRohith RajAinda não há avaliações

- Backend (Physical Design) Interview Questions and Answers - BipeenKulkarniDocumento30 páginasBackend (Physical Design) Interview Questions and Answers - BipeenKulkarniRohith RajAinda não há avaliações

- Floorplan Control Parameters: VLSI Basics and Interview QuestionsDocumento10 páginasFloorplan Control Parameters: VLSI Basics and Interview QuestionsRohith RajAinda não há avaliações

- SiCon Design Technology Interview QuestionsDocumento2 páginasSiCon Design Technology Interview QuestionsRohith RajAinda não há avaliações

- ASIC Backend Physical Design Questions - ElectronicsBus 2014Documento4 páginasASIC Backend Physical Design Questions - ElectronicsBus 2014Rohith RajAinda não há avaliações

- Isolation Cells, Power Witches, Retention RegistersDocumento10 páginasIsolation Cells, Power Witches, Retention RegistersRohith RajAinda não há avaliações

- Single PhasingDocumento6 páginasSingle PhasingQuek Swee XianAinda não há avaliações

- MAP MicroprojectDocumento11 páginasMAP Microprojectjhjh0% (1)

- Final Revised AbstractttttDocumento25 páginasFinal Revised AbstractttttDaniella BeltranAinda não há avaliações

- 2N4416-Hifrequency Amp JFETDocumento2 páginas2N4416-Hifrequency Amp JFETsandhantusharAinda não há avaliações

- Detector 70-02 - Photo Smoke Detector Model CPD-7157 - 2010Documento4 páginasDetector 70-02 - Photo Smoke Detector Model CPD-7157 - 2010DM2Ainda não há avaliações

- jm103 BILICHECKDocumento76 páginasjm103 BILICHECKNIMSI ASTIVIAAinda não há avaliações

- Clippers and Clampers-3 - PPT DownloadDocumento8 páginasClippers and Clampers-3 - PPT DownloadAlejandroAinda não há avaliações

- Lsa 36 - 4-Pole - Single-Phase: AlternatorsDocumento15 páginasLsa 36 - 4-Pole - Single-Phase: AlternatorsJulio IllanesAinda não há avaliações

- Calculations of Buck Boost ConverterDocumento3 páginasCalculations of Buck Boost ConverterUmar AkhtarAinda não há avaliações

- 12f508 509 16f505Documento98 páginas12f508 509 16f505Leng SovannarithAinda não há avaliações

- ErviceDocumento103 páginasErviceHitesh PanigrahiAinda não há avaliações

- 9A02305 Electrical CircuitsDocumento8 páginas9A02305 Electrical CircuitssivabharathamurthyAinda não há avaliações

- CB#1 Journeyman examDocumento57 páginasCB#1 Journeyman examEarl Jenn AbellaAinda não há avaliações

- Det01cfc High Speed Detector IngaasDocumento20 páginasDet01cfc High Speed Detector Ingaasnithin_v90Ainda não há avaliações

- t75 750 PDFDocumento7 páginast75 750 PDFEnache GabrielAinda não há avaliações

- 555 DC Boost Converter CircuitsDocumento5 páginas555 DC Boost Converter CircuitsFelipe VargasAinda não há avaliações

- Uee403 - High Voltage Engineering: University of Moratuwa, Sri LankaDocumento4 páginasUee403 - High Voltage Engineering: University of Moratuwa, Sri LankaSarinda JayasingheAinda não há avaliações

- Electronics Project ProposalDocumento5 páginasElectronics Project ProposalObaid Ur Rehman33% (3)

- A Study On Insulation Coordination of A Wind Turbine Generator System and A Distribution LineDocumento6 páginasA Study On Insulation Coordination of A Wind Turbine Generator System and A Distribution Linejomoran100% (1)

- Mobile Repair TrainingDocumento10 páginasMobile Repair Trainingwarwar50% (2)

- 1.5v To 220v AC Simple InverterDocumento3 páginas1.5v To 220v AC Simple Inverterspiderwebcafe2012100% (1)

- Primamax PVT LTDDocumento30 páginasPrimamax PVT LTDSalman HashmiAinda não há avaliações

- Homework # 10: Show All Work!Documento7 páginasHomework # 10: Show All Work!thienvu truongAinda não há avaliações

- Counters and Clocks: Building a Nixie ClockDocumento12 páginasCounters and Clocks: Building a Nixie ClockJoseGarciaRuizAinda não há avaliações

- (Latch SR CMOS) .MC14044BCP PDFDocumento7 páginas(Latch SR CMOS) .MC14044BCP PDFAndreaOlivaresAinda não há avaliações

- uBer SWITCH V1.1 Microcontroller Relay True-Bypass CircuitDocumento3 páginasuBer SWITCH V1.1 Microcontroller Relay True-Bypass CircuitUjang PriyantoAinda não há avaliações

- Project Report of Be 7TH Sem FinalDocumento15 páginasProject Report of Be 7TH Sem FinalpayalAinda não há avaliações

- Simulation of A Solar MPPT Charger Using Cuk Converter For Standalone ApplicationDocumento6 páginasSimulation of A Solar MPPT Charger Using Cuk Converter For Standalone ApplicationcashnuiAinda não há avaliações

- Ngspice ManualDocumento631 páginasNgspice ManualHikage23Ainda não há avaliações