Escolar Documentos

Profissional Documentos

Cultura Documentos

74HC138

Enviado por

Tomás Saavedra Fernández0 notas0% acharam este documento útil (0 voto)

55 visualizações7 páginasThe 74HC / HCT138 are high-speed Si-gate CMOS devices. They are pin compatible with low power Schottky TTL (LSTTL) the "138" is identical to the "238" but has inverting outputs.

Descrição original:

Direitos autorais

© © All Rights Reserved

Formatos disponíveis

PDF, TXT ou leia online no Scribd

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoThe 74HC / HCT138 are high-speed Si-gate CMOS devices. They are pin compatible with low power Schottky TTL (LSTTL) the "138" is identical to the "238" but has inverting outputs.

Direitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato PDF, TXT ou leia online no Scribd

0 notas0% acharam este documento útil (0 voto)

55 visualizações7 páginas74HC138

Enviado por

Tomás Saavedra FernándezThe 74HC / HCT138 are high-speed Si-gate CMOS devices. They are pin compatible with low power Schottky TTL (LSTTL) the "138" is identical to the "238" but has inverting outputs.

Direitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato PDF, TXT ou leia online no Scribd

Você está na página 1de 7

Product specication

File under Integrated Circuits, IC06

September 1993

INTEGRATED CIRCUITS

74HC/HCT138

3-to-8 line decoder/demultiplexer;

inverting

For a complete data sheet, please also download:

The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications

The IC06 74HC/HCT/HCU/HCMOS Logic Package Information

The IC06 74HC/HCT/HCU/HCMOS Logic Package Outlines

September 1993 2

Philips Semiconductors Product specication

3-to-8 line decoder/demultiplexer; inverting 74HC/HCT138

FEATURES

Demultiplexing capability

Multiple input enable for easy expansion

Ideal for memory chip select decoding

Active LOW mutually exclusive outputs

Output capability: standard

I

CC

category: MSI

GENERAL DESCRIPTION

The 74HC/HCT138 are high-speed Si-gate CMOS devices

and are pin compatible with low power Schottky TTL

(LSTTL). They are specified in compliance with JEDEC

standard no. 7A.

The 74HC/HCT138 decoders accept three binary

weighted address inputs (A

0

, A

1

, A

2

) and when enabled,

provide 8 mutually exclusive active LOW outputs (Y

0

to

Y

7

).

The 138 features three enable inputs: two active LOW

(E

1

and E

2

) and one active HIGH (E

3

). Every output will be

HIGH unless E

1

and E

2

are LOW and E

3

is HIGH.

This multiple enable function allows easy parallel

expansion of the 138 to a 1-of-32 (5 lines to 32 lines)

decoder with just four 138 ICs and one inverter.

The 138 can be used as an eight output demultiplexer by

using one of the active LOW enable inputs as the data

input and the remaining enable inputs as strobes. Unused

enable inputs must be permanently tied to their

appropriate active HIGH or LOW state.

The 138 is identical to the 238 but has inverting outputs.

QUICK REFERENCE DATA

GND = 0 V; T

amb

= 25 C; t

r

= t

f

= 6 ns

Notes

1. C

PD

is used to determine the dynamic power dissipation (P

D

in W):

P

D

= C

PD

V

CC

2

f

i

+ (C

L

V

CC

2

f

o

) where:

f

i

= input frequency in MHz

f

o

= output frequency in MHz

(C

L

V

CC

2

f

o

) = sum of outputs

C

L

= output load capacitance in pF

V

CC

= supply voltage in V

2. For HC the condition is V

I

= GND to V

CC

For HCT the condition is V

I

= GND to V

CC

1.5 V

ORDERING INFORMATION

See 74HC/HCT/HCU/HCMOS Logic Package Information.

SYMBOL PARAMETER CONDITIONS

TYPICAL

UNIT

HC HCT

propagation delay C

L

= 15 pF; V

CC

= 5 V

t

PHL

/ t

PLH

A

n

to Y

n

12 17 ns

t

PHL

/ t

PLH

E

3

to Y

n

E

n

to Y

n

14 19 ns

C

I

input capacitance 3.5 3.5 pF

C

PD

power dissipation capacitance per package notes 1 and 2 67 67 pF

September 1993 3

Philips Semiconductors Product specication

3-to-8 line decoder/demultiplexer; inverting 74HC/HCT138

PIN DESCRIPTION

PIN NO. SYMBOL NAME AND FUNCTION

1, 2, 3 A

0

to A

2

address inputs

4, 5 E

1

, E

2

enable inputs (active LOW)

6 E

3

enable input (active HIGH)

8 GND ground (0 V)

15, 14, 13, 12, 11, 10, 9, 7 Y

0

to Y

7

outputs (active LOW)

16 V

CC

positive supply voltage

Fig.1 Pin configuration. Fig.2 Logic symbol.

handbook, halfpage

MLB312

A

0

A

1

A

2

1

2

3

15

13

11

7

9

10

12

14

Y

0

Y

1

Y

2

Y

3

Y

4

Y

5

Y

6

Y

7

4

5

6

E

1

E

2

E

3

Fig.3 IEC logic symbol.

(a) (b)

Fig.4 Functional diagram.

September 1993 4

Philips Semiconductors Product specication

3-to-8 line decoder/demultiplexer; inverting 74HC/HCT138

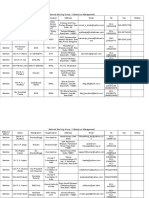

FUNCTION TABLE

Notes

1. H = HIGH voltage level

L = LOW voltage level

X = dont care

INPUTS OUTPUTS

E

1

E

2

E

3

A

0

A

1

A

2

Y

0

Y

1

Y

2

Y

3

Y

4

Y

5

Y

6

Y

7

H

X

X

X

H

X

X

X

L

X

X

X

X

X

X

X

X

X

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

L

L

L

L

L

L

L

L

H

H

H

H

L

H

L

H

L

L

H

H

L

L

L

L

L

H

H

H

H

L

H

H

H

H

L

H

H

H

H

L

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

L

L

L

L

L

L

L

L

H

H

H

H

L

H

L

H

L

L

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

L

H

H

H

H

L

H

H

H

H

L

H

H

H

H

L

Fig.5 Logic diagram.

September 1993 5

Philips Semiconductors Product specication

3-to-8 line decoder/demultiplexer; inverting 74HC/HCT138

DC CHARACTERISTICS FOR 74HC

For the DC characteristics see 74HC/HCT/HCU/HCMOS Logic Family Specifications.

Output capability: standard

I

CC

category: MSI

AC CHARACTERISTICS FOR 74HC

GND = 0 V; t

r

= t

f

= 6 ns; C

L

= 50 pF

SYMBOL PARAMETER

T

amb

(C)

UNIT

TEST CONDITIONS

74HC

V

CC

(V)

WAVEFORMS

+25 40 to +85 40 to +125

min. typ. max. min. max. min. max.

t

PHL

/ t

PLH

propagation delay

A

n

to Y

n

41

15

12

150

30

26

190

38

33

225

45

38

ns

2.0

4.5

6.0

Fig.6

t

PHL

/ t

PLH

propagation delay

E

3

to Y

n

47

17

14

150

30

26

190

38

33

225

45

38

ns

2.0

4.5

6.0

Fig.6

t

PHL

/ t

PLH

propagation delay

E

n

to Y

n

47

17

14

150

30

26

190

38

33

225

45

38

ns

2.0

4.5

6.0

Fig.7

t

THL

/ t

TLH

output transition

time

19

7

6

75

15

13

95

19

16

110

22

19

ns

2.0

4.5

6.0

Figs 6 and 7

September 1993 6

Philips Semiconductors Product specication

3-to-8 line decoder/demultiplexer; inverting 74HC/HCT138

DC CHARACTERISTICS FOR 74HCT

For the DC characteristics see 74HC/HCT/HCU/HCMOS Logic Family Specifications.

Output capability: standard

I

CC

category: MSI

Note to HCT types

The value of additional quiescent supply current (I

CC

) for a unit load of 1 is given in the family specifications. To

determine I

CC

per input, multiply this value by the unit load coefficient shown in the table below.

AC CHARACTERISTICS FOR 74HCT

GND = 0 V; t

r

= t

f

= 6 ns; C

L

= 50 pF

INPUT UNIT LOAD COEFFICIENT

A

n

1.50

E

n

1.25

E

3

1.00

SYMBOL PARAMETER

T

amb

(C)

UNIT

TEST CONDITIONS

74HCT

V

CC

(V)

WAVEFORMS

+25 40 to +85 40 to +125

min. typ. max. min. max. min. max.

t

PHL

/ t

PLH

propagation delay

A

n

to Y

n

20 35 44 53 ns 4.5 Fig.6

t

PHL

/ t

PLH

propagation delay

E

3

to Y

n

18 40 50 60 ns 4.5 Fig.6

t

PHL

/ t

PLH

propagation delay

E

n

to Y

n

19 40 50 60 ns 4.5 Fig.7

t

THL

/ t

TLH

output transition

time

7 15 19 22 ns 4.5 Figs 6 and 7

September 1993 7

Philips Semiconductors Product specication

3-to-8 line decoder/demultiplexer; inverting 74HC/HCT138

AC WAVEFORMS

PACKAGE OUTLINES

See 74HC/HCT/HCU/HCMOS Logic Package Outlines.

Fig.6 Waveforms showing the address input (A

n

) and enable input (E

3

) to output (Y

n

) propagation delays and

the output transition times.

(1) HC : V

M

= 50%; V

I

= GND to V

CC

.

HCT: V

M

= 1.3 V; V

I

= GND to 3 V.

Fig.7 Waveforms showing the enable input (E

n

) to output (Y

n

) propagation delays and the output transition

times.

(1) HC : V

M

= 50%; V

I

= GND to V

CC

.

HCT: V

M

= 1.3 V; V

I

= GND to 3 V.

Você também pode gostar

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNo EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNota: 4 de 5 estrelas4/5 (5794)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNo EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNota: 4 de 5 estrelas4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)No EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Nota: 4 de 5 estrelas4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingNo EverandThe Little Book of Hygge: Danish Secrets to Happy LivingNota: 3.5 de 5 estrelas3.5/5 (400)

- The Emperor of All Maladies: A Biography of CancerNo EverandThe Emperor of All Maladies: A Biography of CancerNota: 4.5 de 5 estrelas4.5/5 (271)

- Never Split the Difference: Negotiating As If Your Life Depended On ItNo EverandNever Split the Difference: Negotiating As If Your Life Depended On ItNota: 4.5 de 5 estrelas4.5/5 (838)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyNo EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyNota: 3.5 de 5 estrelas3.5/5 (2259)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNo EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNota: 4.5 de 5 estrelas4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNo EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNota: 3.5 de 5 estrelas3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnNo EverandTeam of Rivals: The Political Genius of Abraham LincolnNota: 4.5 de 5 estrelas4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNo EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNota: 4.5 de 5 estrelas4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNo EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNota: 4.5 de 5 estrelas4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaNo EverandThe Unwinding: An Inner History of the New AmericaNota: 4 de 5 estrelas4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNo EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNota: 4 de 5 estrelas4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)No EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Nota: 4.5 de 5 estrelas4.5/5 (121)

- CeldekDocumento2 páginasCeldekPK SinghAinda não há avaliações

- From To: Airtel Logo Change: Does It Make Marketing SenseDocumento3 páginasFrom To: Airtel Logo Change: Does It Make Marketing SenseAvinash HaryanAinda não há avaliações

- Roland Mdx-650 Milling TutorialDocumento28 páginasRoland Mdx-650 Milling TutorialRavelly TelloAinda não há avaliações

- 563000-1 Web Chapter 4Documento22 páginas563000-1 Web Chapter 4Engr Ahmad MarwatAinda não há avaliações

- Ooad Question BankDocumento5 páginasOoad Question Bankkhusboo_bhattAinda não há avaliações

- Contact List For All NWGDocumento22 páginasContact List For All NWGKarthickAinda não há avaliações

- Decline Curve AnalysisDocumento37 páginasDecline Curve AnalysisAshwin VelAinda não há avaliações

- An Introduction To Coolants PDFDocumento57 páginasAn Introduction To Coolants PDFPETER ADAMAinda não há avaliações

- Operations Management: William J. StevensonDocumento36 páginasOperations Management: William J. StevensonRubel Barua100% (4)

- Bobcat 3 Phase: Quick SpecsDocumento4 páginasBobcat 3 Phase: Quick SpecsAnonymous SDeSP1Ainda não há avaliações

- Introduction To Compressed Air SystemDocumento23 páginasIntroduction To Compressed Air SystemMohd Zulhairi Mohd NoorAinda não há avaliações

- High Pressure Accessories CatalogDocumento117 páginasHigh Pressure Accessories CatalogRijad JamakovicAinda não há avaliações

- Bearer Independent Call Control Protocol (Cs2) and Signalling System No.7 - Isdn User Part General Functions of Messages and ParametersDocumento31 páginasBearer Independent Call Control Protocol (Cs2) and Signalling System No.7 - Isdn User Part General Functions of Messages and Parameterssahil_chandna25Ainda não há avaliações

- Proposal Tripurainfo Job PortalDocumento10 páginasProposal Tripurainfo Job PortalEkta DevAinda não há avaliações

- Environmental SustainabilityDocumento3 páginasEnvironmental SustainabilityJoseph Michael Perez100% (1)

- Stand-mount/Books Helf Louds Peaker System Product SummaryDocumento1 páginaStand-mount/Books Helf Louds Peaker System Product SummaryCatalin NacuAinda não há avaliações

- PDFDocumento7 páginasPDFJose JohnAinda não há avaliações

- Week 11b ViewsDocumento26 páginasWeek 11b ViewsKenanAinda não há avaliações

- NGO-CSR Internship Report TemplateDocumento4 páginasNGO-CSR Internship Report TemplatePriyanka Singh100% (1)

- MT Company PresentationDocumento30 páginasMT Company Presentationjose manuelAinda não há avaliações

- Bhavin Desai ResumeDocumento5 páginasBhavin Desai Resumegabbu_Ainda não há avaliações

- Vibration Isolaton SelectionDocumento24 páginasVibration Isolaton SelectionvelmuruganAinda não há avaliações

- C D C SDocumento4 páginasC D C SandriAinda não há avaliações

- StatementDocumento3 páginasStatementSachinBMetre87 SachinBMetreAinda não há avaliações

- All C PG and CPP Service ManualDocumento60 páginasAll C PG and CPP Service Manualhurantia100% (1)

- Manual Bombas Pozo e ImpulsionDocumento112 páginasManual Bombas Pozo e ImpulsionFernando PuentesAinda não há avaliações

- Sony Chassis Ba-4 (C-TV KV-13M40 - 50 - 51, KV-14MB40, KV-20M40, KV-20S40 - 41, KV-20V80, Kv-21se80, Kv-21se40, Kv-21me40... Service Manual)Documento94 páginasSony Chassis Ba-4 (C-TV KV-13M40 - 50 - 51, KV-14MB40, KV-20M40, KV-20S40 - 41, KV-20V80, Kv-21se80, Kv-21se40, Kv-21me40... Service Manual)Mauro Mendez100% (1)

- Oracle® Auto Service Request: Exadata Database Machine Quick Installation Guide Release 5.0Documento12 páginasOracle® Auto Service Request: Exadata Database Machine Quick Installation Guide Release 5.0ManifoldAinda não há avaliações

- Scan 0001Documento1 páginaScan 0001ochiroowitsAinda não há avaliações

- Top Links October 2018Documento122 páginasTop Links October 2018Andrew Richard ThompsonAinda não há avaliações