Escolar Documentos

Profissional Documentos

Cultura Documentos

Com Cuestionario Basica Electronica Examen Piloto Fin Carrera 08-11-2013

Enviado por

Angela AbadDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Com Cuestionario Basica Electronica Examen Piloto Fin Carrera 08-11-2013

Enviado por

Angela AbadDireitos autorais:

Formatos disponíveis

Planteamiento

Opcion A 1 D - 2 A - 3 C - 4 B

Opcion B 1 B - 2 A - 3 C - 4 D

Opcin C 1 D - 2 C - 3 A - 4 B

Opcin D 1 B - 2 A - 3 D - 4 B

Respuesta correcta A

Planteamiento

Opcion A I1= -1,43 [mA] ; I2= -6,3[mA]

Opcion B I1= 6,3 [mA] ; I2= 1,43[mA]

Opcin C I1= 1,43 [mA] ; I2= 6,3[mA]

Opcin D I1= 1,43 [mA] ; I2= -6,3[mA]

Respuesta correcta C

Planteamiento

Opcion A D1:"OFF" y Z1:"OFF"

Opcion B D1:"OFF" y Z1:"fuente"

Opcin C D1:"OFF" y Z1:"ON"

Q1 2N1711 R1 1k R2 20 V3 3 V V1 10 V D2 1N4467

Q1 2N1711 R1 1k R2 20 V3 3 V V1 10 V D2 1N4467

R1

1k

R2

3k

R3

1k

R4

2k

R5

1k

R6

2k

5 V

5 V

5 V

D1

Z1

Opcin D D1:"ON" y Z1:"fuente"

Respuesta correcta B

Planteamiento

Opcion A D1:"OFF" y Z1:"OFF"

Opcion B D1:"OFF" y Z1:"fuente"

Opcin C D1:"OFF" y Z1:"ON"

Opcin D D1:"ON" y Z1:"fuente"

Respuesta correcta B

Planteamiento Determine el voltaje V

E

(voltaje en el emisor) del transistor Q

1

Opcion A 4.0V

Q1 2N1711 R1 1k R2 20 V3 3 V V1 10 V D2 1N4467

R7

500

R8

250

Iin

7 v

Vz = 5V

VT= 1V

Iz min = 1mA

Opcion B 3.3V

Opcin C 12.0V

Opcin D 4.6V

Respuesta correcta D

Solucin

Opcin A

Argumento de opcin A Alternativa Correcta

Argumento de opcin B Las respuestas 1 B y 4 D no son correctas

Argumento de opcin C Las respuestas 2 C y 3 A no son correctas

Argumento de opcin D Las respuestas 1 B y 3 D no son correctas

Referencia bibliogrfica Teora y solucionario de Problemas

Solucin

El problema consiste primero en observarlo detenidamente y luego escoger el

estado del diodo

Argumento de opcin A Aplica incorrectamente la definicion de diodos

Argumento de opcin B Aplica incorrectamente la definicion de diodos

Argumento de opcin C OPCION CORRECTA

Argumento de opcin D Aplica incorrectamente la definicion de diodos

Referencia bibliogrfica Anlisis de circuitos en Ingenieria .- Hayt Kemmerly.-7ma Edicion

Solucin

El problema consiste primero en observarlo detenidamente y luego escoger los

estados de los diodos.

Argumento de opcin A Aplica incorrectamente la definicion de diodos

Argumento de opcin B OPCION CORRECTA

Argumento de opcin C Aplica incorrectamente la definicion de diodos

Argumento de opcin D Aplica incorrectamente la definicion de diodos

Referencia bibliogrfica Anlisis de circuitos en Ingenieria .- Hayt Kemmerly.-7ma Edicion

Solucin

El problema consiste primero en observarlo detenidamente y luego escoger los

estados de los diodos.

Argumento de opcin A Aplica incorrectamente la definicion de diodos

Argumento de opcin B OPCION CORRECTA

Argumento de opcin C Aplica incorrectamente la definicion de diodos

Argumento de opcin D Aplica incorrectamente la definicion de diodos

Referencia bibliogrfica Anlisis de circuitos en Ingenieria .- Hayt Kemmerly.-7ma Edicion

Argumento de opcin A Voltaje IVpI

Argumento de opcin B Voltaje IVpI-0.7

Argumento de opcin C mitad de Vcc

Argumento de opcin D Calculo de I

D

, V

D

, V

E

Referencia bibliogrfica

Planteamiento

Opcion A

Opcion B

Opcin C

Opcin D

Respuesta correcta

Calcule el voltaje de salida Vo y la ganancia del circuito cuando V2=100mVpp, de la figura que se muestra a

continuacin . Asuma que V1 =0

V

o

= -454,54mVpp y A

V

= +1

V

o

= -454,54mVpp y A

V

= -1

V

o

= +454,54mVpp y A

V

= +1

V

o

= +454,54,55mVpp y A

V

= -1

B

Solucin

Opcin B

Argumento de opcin A

De acuerdo a la Solucin la Ganancia Av no es

correcta

Argumento de opcin B Alternativa Correcta

Argumento de opcin C

De acuerdo a la Solucin ninguna respuesta es

correcta

Argumento de opcin D

De acuerdo a la Solucin Vo no es correcta

Referencia bibliogrfica Prcticas de Laboratorio de Electrnica A

Planteamiento

Opcion A

Opcion B

Opcin C

Opcin D

Respuesta correcta

Dado el siguiente oscilador con un timer 555, y suponiendo al transistor BJT en zona

lineal, determinar el tipo de carga del capacitor C cuando se genera un impulso (flanco

negativo) en Vi.

Capacitor se carga de manera exponencial.

Capacitor se carga de manera lineal.

Capacitor se carga de manera sinusoidal.

Capacitor se carga y descarga linealmente de manera periodica.

B

Solucin

Argumento de opcin A

Argumento de opcin B

Argumento de opcin C

Argumento de opcin D

Referencia bibliogrfica

Es una aplicacin de un toemr 555 monoestable. La salida en Vo es un pulso cuya

duracin es controlada por el tiempo de carga del capacitor C1. Suponiendo que el

transistor opera en zona activa, la carga del capacitor se hara con una fuente de

corriente constante, por tanto es de tipo lineal.

Falso. Esto es en condiciones de red RC con alimentacin VDC.

Verdadero.

Falso. No corresponde a las posibles formas de carga.

Falso , es un monoestable. No es oscilador astable.

Planteamiento

Opcion A

Opcion B

Opcin C

Opcin D

Respuesta correcta

La etapa de oscilacin esta dada por:

Q1 y Q2

Q3 y Q4

Q1 y Q4

Q2 y Q3

A

Argumento de opcin A Primero oscila, luego amplifica. 2 transistores, 2 circuitos RC

Argumento de opcin B Confusion con circuito amplificador de corriente

Argumento de opcin C 2 transistores

Argumento de opcin D 2 transistores

Referencia bibliogrfica http://www.unicrom.com/cir_sirena4transistores.asp

Planteamiento

Opcion A

Opcion B

Opcin C

Opcin D

Respuesta correcta

Con respecto a un Oscilador Controlado por Voltaje (VCO) cual de las siguientes

alternativas es verdadera?

Entrega en su salida un voltaje proporcional a la frecuencia de entrada

La salida es siempre un voltaje multiplicado por su frecuencia

Su salida, presenta una frecuencia que es una funcin directa del voltaje de entrada.

La salida est siempre modulada en amplitud y frecuencia

C

Argumento de opcin A

Argumento de opcin B

Argumento de opcin C

Argumento de opcin D

Referencia bibliogrfica

Respuesta Falsa

Respuesta Falsa

Respuesta Correcta

Respuesta Falsa

Manual gua de Prcticas del Lab de Electrnica B

Planteamiento

Opcion A

Opcion B

Opcin C

Opcin D

Respuesta correcta

Ejecute las lineas de codigo siguientes, asuma DS=1508H.

1508:0200 90 NOP

1508:0201 B008 MOV AL, 08H

1508:0203 B415 MOV AH, 15H

1508:0205 8ED0 MOV SS, AX

1508:0207 BD0002 MOV BP, 0200H

1508:020A BE0800 MOV SI, 0003H

1508:020D 8A5201 MOV DL, [BP+SI]

1508:0210 90 NOP

Despus de ejecutar la ultima instruccin NOP el contenido del registro DL es:

15H

8AH

B4H

52H

Opcion C.

Argumento de opcin A

Argumento de opcin B

Argumento de opcin C

Argumento de opcin D

Referencia bibliogrfica

No correpone con el byte que apunta [BP+SI] en segmento DS.

No correpone con el byte que apunta [BP+SI] en segmento DS.

Solucion Correcta.

No correpone con el byte que apunta [BP+SI] en segmento DS.

Libro: MICROPROCESADORES INTEL autor BARRY B. BREY.

Planteamiento

Opcion A

Opcion B

Opcin C

Opcin D

Respuesta correcta

Considere la siguiente secuencia de instrucciones en lenguaje ensamblador

para un PIC de la gama media que funciona con un XTAL de 16 MHz.

Observe que CNT2 es una variable previamente definida. MOVLW

.5 MOVWF

CNT2 LAZO

DECFSZ CNT2, F

GOTO LAZO

GOTO $

Cuanto tiempo tarda en salir de LAZO?

2 microsegundos.

4 microsegundos.

8 microsegundos.

16 microssegundos.

Opcion B

Argumento de opcin A

Argumento de opcin B

Argumento de opcin C

Argumento de opcin D

Referencia bibliogrfica

Numero total de ciclos de instruccion incorrecto.

Solucion correcta.

Numero total de ciclos de instruccion incorrecto.

Numero total de ciclos de instruccion incorrecto.

Hoja datos de microcontroladores de gama media de Microchip.

Tema

Planteamiento

Opcion A

Opcion B

Opcin C

Opcin D

Respuesta correcta

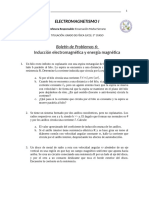

Calcular el voltaje a traves de la resistencia marcada como R6

2.1 Voltios 2.7mA

2.1 Voltios 0.27 A

1.8 Voltios 2.7mA

1.8 Voltios 0.27 A

A

V1 40 V V2 200 V I1 10 A R1 20 R2 80 R3 200 R4 40 R5 100

Solucin

El problema consiste primero en observarlo

detenidamente y luego escoger el camino

correcto para realizar una ley de voltaje de

Kirchhoff con el propsito de encontrar la

corriente de base y con esta corriente

calcular el voltaje colector emisor.

Argumento de opcin A OPCION CORRECTA

Argumento de opcin B

Aplica incorrectamente la Ley de voltaje de

Kirchhoff

Argumento de opcin C

Aplica incorrectamente la Ley de voltaje de

Kirchhoff

Argumento de opcin D

Aplica incorrectamente la Ley de voltaje de

Kirchhoff

Referencia bibliogrfica

Anlisis de circuitos en Ingenieria .- Hayt

Kemmerly.-7ma Edicion

Planteamiento

Opcion A

Opcion B

Opcin C

Opcin D

Respuesta correcta

Tema

Al realizar las siguientes conexiones:

Obtenemos que el ampermetro A1 marca 785 mA y A2 marca 386 mA. Indique la

polaridad relativa entre las bobinas para ambos casos.

CIRCUITO 1 representa polaridad aditiva y CIRCUITO 2 polaridad sustractiva.

Ambos circuitos representan polaridad sustractiva.

CIRCUITO 2 representa polaridad aditiva y CIRCUITO 1 polaridad sustractiva.

Ambos circuitos representan polaridad aditiva.

C

Q1 2N1711 R1 1k R2 20 V3 3 V V1 10 V D2 1N4467

Solucin

Argumento de opcin A

Argumento de opcin B

Argumento de opcin C

Argumento de opcin D

Referencia bibliogrfica

El problema consiste en aplicar correctamente la Convencin de puntos o marcas

.

Aplica incorrectamente la Convencin de puntos o marcas.

Aplica incorrectamente la Convencin de puntos o marcas.

OPCION CORRECTA

Aplica incorrectamente la Convencin de puntos o marcas.

Guia de Practicas del Laboratorio de Redes Elctricas .- Ing. Luis Vasquez Vera.-

1ra Edicion

Planteamiento

Opcion A

Opcion B

Opcin C

Opcin D

Respuesta correcta

Planteamiento

Opcion A

Opcion B

Opcin C

Opcin D

Respuesta correcta

Con un decodificador de n entrada podemos implementar:

Funciones de n variables

Funciones de n+1 variables

Varias funciones de n variables

Funciones de 2^n variables

D

De acuerdo al diagrama ASM de la figura, el decodificador para la salida OUT1 y OUT2, es:

OUT1=Ta.In ; OUT2=Td

OUT1=Ta.NOT(In) ; OUT2=Td

OUT1=Ta.In ; OUT2=NOT(Td)

OUT1=Ta ; OUT2=Td.In

D

74107 J 1 K 4 C L R 1 3Q 3 Q 2 CLK 12 7408 12 3 7408 45 6 CLK A Q +5V

Solucin

Argumento de opcin A

Argumento de opcin B

Argumento de opcin C

Argumento de opcin D

Referencia bibliogrfica

Solucin

Argumento de opcin A

Argumento de opcin B

Argumento de opcin C

Argumento de opcin D

Referencia bibliogrfica

Funciones de 2^n variables

Conceptualmente errado

Conceptualmente errado

Conceptualmente errado

Correcta

Bronw and Zvonko. Fundamentals Digital Logic with VHDL Design

Opcin A.

Alternativa Correcta

Incorrecta operacin NOT en In

Incorrecta operacin NOT en Td

Falta operacin AND entre Ta e In.

Digital Design, Principles and Practices, McGraw Hill.

Planteamiento

Opcion A

Opcion B

Opcin C

Opcin D

Respuesta correcta

De acuerdo a lo establecido en la asignatura, defina la diferencie de la salida entre una

Maquina Secuencial Sncrona modelo MOORE y modelo MEALY.

El modelo MOORE la salida solo depende del estado presente sin importar la

entreda.En el modelo MEALY la salida depende del estado presente y del valor de la

entrada.

En ambos modelos la salida dependen de la entrada, pero en el modelo MOORE

depende tambin del estado actual.

En ambas modelos la salida dependen del estado presente, pero el modelo MOORE

depende tambin de la entreda.

El modelo MEALY la salida solo depende del estado presente sin importar la

entreda.En el modelo MOORE la salida depende del estado presente y del valor de la

entrada.

C

Solucin

Argumento de opcin A

Argumento de opcin B

Argumento de opcin C

Argumento de opcin D

Referencia bibliogrfica

En el modelo MOORE de una Maquina Secuencial Sncrona, la salida depende solo del

estado presente. En el modelo MEALY la salida depende del estado presente y el valor de la

entreda.

Definicin Correcta

De acuerdo a la Solucin, la alternativa es Incorrecta

De acuerdo a la Solucin, la alternativa es Incorrecta

Los conceptos antes definidos no son iguales

Digital Design, Principles and Practices, McGraw Hill.

Planteamiento

Opcion A

Opcion B

Opcin C

Opcin D

Respuesta correcta

Planteamiento

OPCIN A

OPCIN B

Opcin C

Opcin D

Respuesta correcta

Considerando la siguiente lista Cul de las opciones representa la secuencia

correcta del proceso de construccin de un prototipo de un sistema digital?

1. Simulacin

2. Cableado del prototipo

3. Interpretacin de especificaciones

4. Diseo preliminar

5. Pruebas finales

4, 3, 2, 1, 5

3, 1, 4, 2, 5

3, 4, 2, 1, 5

3, 4, 1, 2, 5

D

La complejidad de un circuito integrado digital puede medirse por el nmero de puertas

lgicas que contiene. stos se clasifican en niveles o escalas de integracin. La capacidad

de integracin depende fundamentalmente de dos factores

El rea ocupada por cada puerta y del consumo total del chip.

La fuente de alimentacin y la velocidad de procesamiento

La forma de fabricacin y del tipo de integracin

Ninguna de las anteriores

A

Argumento de opcin A

Argumento de opcin B

Argumento de opcin C

Argumento de opcin D

Referencia bibliogrfica

Solucin

Argumento de opcin A

Argumento de opcin B

Argumento de opcin C

Argumento de opcin D

Referencia bibliogrfica

Primero debe ir la interpretacin de especificaciones. Opcin incorrecta.

Luego de la interpretacin de especificaciones debe ir el diseo preliminar. Opcin

incorrecta.

Luego del diseo preliminar debe ir la simulacin y no el cableado del prototipo. Opcin

incorrecta.

Respuesta correcta ya que es el orden de construccin utilizado por los diseadores.

"Fundamentos de Lgica Digital con diseo VHDL", Stephen Brown & Zvonko Vranesic, Segunda

Edicin, McGraw Hill

El rea ocupada por cada puerta y de consumo total del chip.

Definicin Correcta

De acuerdo a la Solucin, la alternativa es Incorrecta

De acuerdo a la Solucin, la alternativa es Incorrecta

De acuerdo a la Solucin, la alternativa es Incorrecta

Sistemas Digitales, Principios y Aplicaciones. Ronald Tocci., 10 ma Edicin. Prentice Hall

Formato Dependiente de la Grafica

Planteamiento

En el siguiente Sistema Masa-Resorte-Amortiguador. Determine la Funcin de

Transferencia:

Solucin

Opcin A

Opcion A Argumento de opcin A

Alternativa Correcta

Opcion B Argumento de opcin B De acuerdo a la solucin del problema esta alternativa no es correcta

Opcin C Argumento de opcin C De acuerdo a la solucin del problema esta alternativa no es correcta

Opcin D Argumento de opcin D De acuerdo a la solucin del problema esta alternativa no es correcta

Respuesta correcta A Referencia bibliogrfica Sistema Moderno de Control, Dorf & Bishop

Planteamiento

Opcion A

Opcion B

Opcin C

Opcin D

Respuesta correcta

Planteamiento

Opcion A

Opcion B

Opcin C

Opcin D

Respuesta correcta

Dada la funcin de transferencia H(s), representativo de una sistema LTI-CT

causal, es verdad que :

El sistema es BIBO estable

Los polos deben ubicarse dentro del circulo unitario del plano complejo.

Los ceros de la funcin de transferencia deteminan la estabilidad del sistema

No se puede determinar la estabilidad del sistema a partir de los datos dados.

A

Dada la siguinete seal x(t), es verdad que:

La frecuencia Wo de x(t) es igual a 15

Los coeficientes de fourier de x(t) son:

Los coeficientes de fourier de x(t) son:

La suma de los coeficientes de fourier es:

B

()=(2)^2/((^2+3+2)(+7)^2 )

()=cos(3)+2(5)+2

_0=2 _3=1/2 _(3)=1/2 _5=

_0= _3=(1)/2 _(3)=1/2 _5=

Solucin

Argumento de opcin A

Argumento de opcin B

Argumento de opcin C

Argumento de opcin D

Referencia bibliogrfica

Solucin

Argumento de opcin A

Argumento de opcin B

Argumento de opcin C

Argumento de opcin D

Referencia bibliogrfica

Criterios de estabilidad de un sistema en base a la ubicacin de polos de la

funcin de transferencia. Todas las componentes reales delas raices del

denominador deben ser negativas.

Si cumple la condicin de biboestabilidad.

No cumple la condicin de biboestabilidad.

Falso.

Falso.

Seales y Sistemas- Serie Shaum.

La frecuencia de la seal es igual al MCD de las frecuencias individuales, cuando

la seal finalmente es periodica. En este caso la relacin de periodos es un

numero racional 5/3, lo cual indica que si es periodica x(t). Wo=1. Para

identificar los coeficientes de fourier, se obtiene:

Falso. Wo=1

TRUE

Falso.

Falso. La suma es igual a 2+1

Seales y Sistemas-Serie Shaum.

()=1/2 ^(3(1))+1/2 ^(3(1))+2/2 ^(5(1

Você também pode gostar

- EjerciciosDocumento2 páginasEjerciciosAngela AbadAinda não há avaliações

- Hoja Aforo TraficoDocumento5 páginasHoja Aforo TraficoAngela AbadAinda não há avaliações

- Clase 1Documento2 páginasClase 1Angela AbadAinda não há avaliações

- Topografía DefinitivaDocumento6 páginasTopografía DefinitivaAngela AbadAinda não há avaliações

- Tabla Estadistica 1Documento16 páginasTabla Estadistica 1Angela AbadAinda não há avaliações

- Columnas de GravaDocumento16 páginasColumnas de GravaAngela AbadAinda não há avaliações

- EeeeDocumento2 páginasEeeeAngela AbadAinda não há avaliações

- A Partir Del Siguiente Sistema, Determine Las Ecuaciones Del MismoDocumento2 páginasA Partir Del Siguiente Sistema, Determine Las Ecuaciones Del MismoAngela AbadAinda não há avaliações

- Tablas LimitesDocumento8 páginasTablas LimitesAngela AbadAinda não há avaliações

- 6 Mod Empir Predic PropagacDocumento38 páginas6 Mod Empir Predic PropagacbuyesyohanAinda não há avaliações

- CCNA1Documento1 páginaCCNA1Esther Arenas YatacoAinda não há avaliações

- Propiedades Físicas de Los AgregadosDocumento8 páginasPropiedades Físicas de Los AgregadosAngela AbadAinda não há avaliações

- OpampDocumento69 páginasOpampJosué Tristán AlmonasiAinda não há avaliações

- RM - 175 - 2008 - DM Modif Al CNE, Conductor Libre HalógenosDocumento3 páginasRM - 175 - 2008 - DM Modif Al CNE, Conductor Libre HalógenosRENEL InversionesAinda não há avaliações

- Doyson Tarifa 2021-2022Documento12 páginasDoyson Tarifa 2021-2022VEMATEL100% (1)

- Ensamblaje de Una ComputadoraDocumento8 páginasEnsamblaje de Una ComputadoraCaQui PameAinda não há avaliações

- Manual Tecnico Instalaciones Electricas Industriales.Documento174 páginasManual Tecnico Instalaciones Electricas Industriales.Gustavo Canela98% (90)

- DGM8500 SpanishDocumento4 páginasDGM8500 SpanishLuis Francisco Gómez MottaAinda não há avaliações

- Tarea Unidad 1Documento2 páginasTarea Unidad 1José ManuelAinda não há avaliações

- Toyota Land Cruiser PDFDocumento8 páginasToyota Land Cruiser PDFJarlinson OyuelaAinda não há avaliações

- UF0149 2.2 TransformadoresDocumento10 páginasUF0149 2.2 Transformadoresgam3rsbejAinda não há avaliações

- Universidad Nacional Autónoma de MéxicoDocumento5 páginasUniversidad Nacional Autónoma de MéxicoUrso ColinAinda não há avaliações

- Iei03 Tarea1Documento7 páginasIei03 Tarea1miuvAinda não há avaliações

- Ti2 U5 t4 Tarea1 Ficha v02Documento5 páginasTi2 U5 t4 Tarea1 Ficha v02Ryuzaki KuroShin クロしんAinda não há avaliações

- GCX3 - Manual-EspDocumento63 páginasGCX3 - Manual-EspRodrigo caballeroAinda não há avaliações

- Case E1 E3Documento27 páginasCase E1 E3Estrella CamachoAinda não há avaliações

- Fuerzas Entre Cuerpos CargadosDocumento14 páginasFuerzas Entre Cuerpos CargadosAnder EscorciaAinda não há avaliações

- Investigación EléctricasDocumento7 páginasInvestigación EléctricasLOAIZA JUAREZ AILEEN YANETH LICENCIATURA EN ARQUITECTURAAinda não há avaliações

- Boletín 6 EM IDocumento3 páginasBoletín 6 EM ICruz CampoAinda não há avaliações

- Laboratorio Electronica de Potencia-18-22Documento5 páginasLaboratorio Electronica de Potencia-18-22Ariel DutanAinda não há avaliações

- Manual de Operacion de Central Electronica MB 2011Documento4 páginasManual de Operacion de Central Electronica MB 2011jgpeyAinda não há avaliações

- Circuitos eléctricos, capacitores y resistenciasDocumento1 páginaCircuitos eléctricos, capacitores y resistenciasRobertoAinda não há avaliações

- La PC Enciende Pero No Da VIDEODocumento6 páginasLa PC Enciende Pero No Da VIDEOMiguel Angel Roa BecerrilAinda não há avaliações

- LogoperiódicasDocumento6 páginasLogoperiódicasAmpuriabravaAinda não há avaliações

- TrabajoDocumento77 páginasTrabajoMoises MbtAinda não há avaliações

- P7 Haro RemigioDocumento19 páginasP7 Haro RemigioRemigio HaroAinda não há avaliações

- Control de sistemasDocumento7 páginasControl de sistemasAugusto AlarconAinda não há avaliações

- Lista de Precios Clientes 2021Documento285 páginasLista de Precios Clientes 2021J Camilo CepedaAinda não há avaliações

- Normas taller mecánico eléctricoDocumento6 páginasNormas taller mecánico eléctricoPlaneamiento 7Ainda não há avaliações

- Catálogo Cables Coaxiales (CONDUMEX, 2007)Documento35 páginasCatálogo Cables Coaxiales (CONDUMEX, 2007)Leo Cruz CataneoAinda não há avaliações

- Taller FSMDocumento4 páginasTaller FSMcristianAinda não há avaliações

- General Efapel CatalogoDocumento112 páginasGeneral Efapel CatalogoNelsonAinda não há avaliações