Escolar Documentos

Profissional Documentos

Cultura Documentos

A Fast Locking All-Digital Phase-Locked Loop

Enviado por

sanoopmkDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

A Fast Locking All-Digital Phase-Locked Loop

Enviado por

sanoopmkDireitos autorais:

Formatos disponíveis

All DPLLs Based on Fuzzy PI Control Algorithm

Changhong Shan, Zhongze Chen, Yong Li, Hua Yuan

Institute of Electrical Engineering

University of South China

Hengyang, China

e-mail: shanch801@126.com

Abstract

An all DPLL(All-Digital Phase Locked Loop)

based on fuzzy PI control algorithm is proposed in this paper.

On analyzing system performance of a second-order PI control

based PLL(Phase Locked Loop), the relationship between noise

bandwidth with PI control parameters is derived, and fuzzy

controller of the system is designed. Under the Matlab/Simulink

environment, system-level PLL is directly modeled by using DSP

Builder

, and then is represented by using VHDL. Software

simulation confirms the correctness of the design. The PLL can

automatically adjust noise bandwidth according its working

state, and it is characteristic of its fast lock speed, small phase

jitter, outstanding anti-interference performance and prone to

integration and so on.

Keywords

-

fuzzy PI control; all-digital phase locked loop;

noise bandwidth

I. INTRODUCTION

With the development of communication and control in

discrete direction, its becoming necessary to make signals be

phase locked in digital mode. And digital PLLs have already

been widely used in digital communications, radars, radio

electronics, instruments, high-speed computer and navigation

systems. In traditional DPLLs, a low-pass filter is usually

adopted as a loop filter for processing a pulse train. The filter

makes a count operation on the phase error pulse produced by

its front phase detector, and outputs as control parameters of

back-end controlled oscillator[1-4]. However, the method for

counting the pulse sequence by the low pass filter is a complex

nonlinear process, it is difficult to convert it approximately to

linear one, or the design parameters of the PLL can not be

determined by using transfer function based analysis method,

and thus decoupling control of phase range, speed and stability

for phase-locked PLL can not be achieved. PI control

algorithm based DPLL overcome the shortcomings by

traditional DPLL, and it is characteristic of its simple structure,

flexible control, high tracking accuracy and good steady-state

performance[5-6]. In practical applications, however, the PLL

is always accompanied by noise and interference, and if the

noise is strong enough, the working state of the system will be

completely destroyed. To improve performance of the PLL on

resisting disturbance, the equivalent noise bandwidth of the

loop should be limited to a narrow range through proper

system design, for the more narrow the equivalent noise

bandwidth, the stronger noise inhibition ability the loop owns,

and the greater the improvement of signal to noise ratio; but

reducing the equivalent noise bandwidth of the loop leads to

lowering acquisition performance, reducing the capture

bandwidth, and increasing the capture time, which is a

contradiction. In a PI control algorithm based DPLL,

proportional-integral control parameter is fixed, so the noise

bandwidth remains the same once it be selected, therefore, the

performance of this kind of DPLL on disturbance resistance is

weak, and dynamic features is bad.

To resolve these problems, we propose a new method for

designing all-digital phase-locked loop. In this method, fuzzy

control and PI control are combined to adopt a kind of variable

bandwidth technology, i.e. at the beginning of capturing

signals, a wide noise bandwidth is used, which will facilitate

the increase of capture bandwidth, and reduce the capture time;

while after the loop is locked, a narrow noise bandwidth is

used in order to reduce the phase jitter, and enhance

anti-interference ability. In this paper, the performance of

DPLLs is analyzed, a design method of fuzzy PI control based

DPLL is proposed, implementation of design and system

simulation under the MATLAB

and by using EDA

technologies are given.

II. ANALYSIS OF DPLL SYSTEM PERFORMANCE

A. Performance analysis of second-order PLL based on PI

control

Model of PI control based second-order DPLL in discrete

domain is shown as Figure 1, and the closed-loop transfer

function is as:

1 2 1

2

1 2 1

( ) ( )

( )

( ) ( 2) (1 )

out

ADPLL

ref

z K K z K

H z

z z K K z K

+

= ==

+ + +

1

where

1

K means proportional control parameters,

2

K integral control parameters, they have following

relationship with parameters

n

and :

1

2 2

2

2

n

n

K T

K T

2

Where

n

denotes the system's natural frequency,

the damping oefficient, and

T

the sampling period.

Figure 1 Model of PI control based second-order DPLL in

discrete domain

7150

978-1-4244-9439-2/11/$26.00 2011 IEEE

Closed-loop transfer function of second-order analog PLL

can also be represented by the standard closed-loop transfer

function of second-order system:

2

2 2

( ) 2

( )

( ) 2

+

= =

+ +

out n n

APLL

in n n

s s

H s

s s s

The above transfer function of second-order PLL in

continuous domain can be transformed into the following

discrete domain transfer function by using bilinear

transformation method:

( ) ( ) ( )

( ) ( ) ( )

2 2 2

1 2

2 2 2

1 2

[4 ] 2 [ 4 ]

( )

[4 4 ] [2 8] [4 4 ]

n n n n n

ADPLL

n n n n n

T T T z T T z

H z

T T T z T T z

+ + +

=

+ + + + + +

4

On comparing equation (1) and (4), we found that the two

expressions are for the same system, and then obtain the

expression about parameters

1

K and

2

K as following:

( )

( )

( )

1 2

2

2 2

8

4 4

4

4 4

n

n n

n

n n

T

K

T T

T

K

T T

+ +

+ +

5

B. Performance analysis of fuzzy PI control based DPLL

System architecture of DPLL based on fuzzy PI control is

shown as figure 2. The DPLL includes a digital phase detector

(DPD), a fuzzy controller, a digital loop filter (DLF) and a

numerically controlled oscillator (NCO). In the figure,

) (n

rfe

represents the input signal, ) (n

out

output signal,

) (n

err

error signal (including a phase error

e

and change

rate of phase error

'

e

).

Figure 2 System model of second-order DPLL based on

fuzzy PI control

When the PLL begins to work or some external

disturbances occur, the phase error

e

and change rate of the

phase error

'

e

are both high, fuzzy control parameter

L

B

will be increased by the fuzzy controller, and also an increase

to the loop noise bandwidth, and thus through PI control the

system dynamic process as well as the process of arriving

phase-locked state is sped up; when PLL is locked in a phase

steady state,

e

and

'

e

are both relatively small, fuzzy

control parameter

L

B will be decreased by the fuzzy

controller, and followed by an decrease to the loop noise

bandwidth, and through the PI control steady state error is

eliminated, while anti-interference ability is enhanced and the

phase jitter is reduced.

Noise hemi-bandwidth of the loop is defined as:

( )

2

0

L

B H j df

6

In equation (3), let j s = , we obtain frequency

response ) ( j H of the closed-loop system, with which and

from Eq (6) the loop noise bandwidth is represented as:

2

(1 4 )

8

n

L

B

= + 7

Under MATLAB

, the relationship of

n

L

B

and can

be obtained according to

8

4 1

2

+

=

n

L

B

and shown as curve

in Figure 3. As can be seen from the figure, given a

narrow-band Gaussian white noise,

L

B of the ideal

second-order PLL has a unique minimum

n L

B 5 . 0

min

= ,

when 5 . 0 = holds, and from the point view of noise

suppression, the best damping coefficient of the ideal

second-order PLL system should be selected as 5 . 0 = .

Considering that the transient response of second-order system

should not last too long, its best to make the system work in

the critical damping state, so we take 707 . 0 = , when

n L

B 53 . 0

min

= , almost the same with the minimum value.

Taken together, the system damping coefficient can be chosen

as 707 . 0 = .

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1 1.1 1.2 1.3 1.4 1.5 1.6 1.7 1.8 1.9 2

0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9

1

1.1

1.2

1.3

1.4

1.5

1.6

1.7

1.8

1.9

2

B

L

/

n

BL/n--

Figure 3 Curve for relationship / ~

L n

B

7151

Substitute

1 4

8

2

+

=

L

n

B

into equation (5) we have:

2 2 2 2 2

2

1

) ( 64 ) 4 1 ( 32 ) 1 4 ( 4

64

T B T B

T B

K

L L

L

+ + + +

=

8

2 2 2 2 2

2

2

) ( 64 ) 4 1 ( 32 ) 4 1 ( 4

) ( 256

T B T B

T B

K

L L

L

+ + + +

=

9

From above analysis we have, once and T are

chosen, the relationship between

L

B and

1

K also

2

K is

determined. Therefore, when the loop noise bandwidth

L

B changes, the proportional and integral control parameters

1

K and

2

K would change accordingly, and then through

the digital loop filter the NCO is controlled.

III. DESIGN OF PHASE LOCK SYSTEM

A. Design of Fuzzy Controller

Since the relationship between the error signal and the

loop noise bandwidth is difficult to be accurately modeled, a

fuzzy scheme is used [7-9]. Here we adopt a two-input

single-output fuzzy controller. Membership functions of input

and output variables are all chosen as trigonometric functions,

the linguistic variables for the input phase error

e

and change

rate of phase error

'

e

are both defined as {PB, PM, PS, ZE,

NS, NM, NL}, while output linguistic variables as {ZE, PSS,

PS, PSM, PM, PMB, PB, PBB}. Given

e

and

'

e

, the

self-tuning of parameter

L

B

should meet the following rules:

(1) if

e

and '

e

are large, a large

L

B

should be

taken in order to speed up system response;

(2) if

e

and '

e

are medium, an appropriate

L

B

should be taken so that the system has a small overshoot;

(3) if

e

and '

e

are small, a small

L

B

should be

taken to avoid shock in the vicinity of the equilibrium point,

through which the system has good performance on

steady-state as well as anti-interference state. According to the

above three rules we get a set of fuzzy rules as shown in table

1.

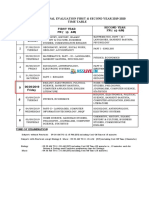

Table 1 Control rules table

L

B

PB PM PS ZE NS NM NB

PB PBB PB PB PMB PB PB PBB

PM PB PMB PM PSM PM PMB PB

PS PMB PM PS PSS PS PM PMB

ZE PM PS PSS ZE PSS PS PM

NS PMB PM PS PSS PS PM PMB

NM PB PMB PM PSM PM PMB PB

NB PBB PB PB PMB PB PB PB

B. Simulation of the fuzzy PI controller by Using

Matlab/Simulink

Structure model of the Fuzzy PI control based PLL is

constructed under MATLAB/Simulink

[10]. And simulation

result is as Figure 4.

Figure 4 Step response of PI control based PLL

The solid line in Figure 4 means step response curve

of an optimal PLL based on fuzzy PI control, while the dashed

line is step response curve of an optimal PLL based on

conventional PI control. As can be seen from the figure, the

step response of PLL based on conventional PI control has an

overshoot % 45 % , and response time s T

s

175 ; while

step response of PLL based on fuzzy PI control has an

overshoot % 18 % , and response time s T

s

80 . Thus,

PLL based on fuzzy PI control has much better dynamic

performance than that of PLL based on conventional PI

e

'

e

7152

control.

IV. DESIGN OF PLL HARDWARE

DSP Builder

is a set of tools for DSP development

provided by Altera

. As a toolbox under Matlab/Simulink

, it

make the design of complex digital systems be implemented

through graphical user interface. As a third-party software of

Quartus

II and Matlab, DSP Builder

provides module

named Signal Compiler as interface for Quartus

II and

Matlab

, with this interface module system-level model can

be easily established and then be compiled into VHDL source

code. After simulation under Quartus

II environment,

compiled code can be downloaded to an FPGA chip, which

may be our target circuit.

Above mentioned ADPLL can be automatically converted

to VHDL code by using DSP Builder

, under Quartus

we

get simulation results of ADPLL based on fuzzy PI control (as

Figure 5). The simulation results indicate that when a jump

occurs on the frequency of input signal, the system can arrive

phase re-locked state in a few clock cycles.

Figure 5: simulation results of ADPLL based on fuzzy PI control

V. CONCLUSIONS

This paper presents a fuzzy PI control algorithm based

DPLL, including performance analysis and design methods of

this kind of DPLL. Under Matlab/ Simulink environment,

system-level model is also established by using DSP

Builder, modeling and simulation results have been

obtained under Quartus . Software simulation confirms

the correctness and feasibility of the design. The PLL can

automatically adjust the noise bandwidth according to the

system working conditions, through which overcomes the

contradiction between increasing the speed of PLL for

arriving phase locked state and enhancing system

performance on anti-Interference, and it is characterized small

phase jitter, outstanding anti-Interference performance and

prone to integration. Furthermore, it can be as modules

embedded within the SOC, and owns a wide range of

applications.

REFERENCES

[1] Huachun Hu, Yu Hu. Principle and applications of digital phase locked

loop [M]. Shanghai: Shanghai Science and Technology Press, 1990 (In

Chinese).

[2] Juesheng Zhang. Phase Lock Technology [M]. Xi'an: Xidian

University Press, 1994 (In Chinese).

[3] Changhong Shan, XieYuan Meng. Design of DPLL based on FPGA

[J]. Electronic Technology Application, 2001 (9): 58 ~ 60 (In

Chinese).

[4] Wenli Wang, Zhang Xia. Design of DPLL based on FPGA[J].

Electronic Design Engineering, 2009 17 (1): 39 ~ 43 (In Chinese).

[5] Hao Pang, sky ZU, Zan-ji Wang. A new all-digital phase-locked loop

[J]. CSEE, 2003,23 (2) :37-41 (In Chinese).

[6] Changhong Shan, Yan Wang, Chen Wen-Guang, Zhongze Chen.

Design and implementation of FPGA-based high-order ADPLL[J].

Circuits and Systems .2005,10 (3): 76 ~ 79 (In Chinese).

[7] Yao-nan Wang, Wei SUN. Intelligent Control Theory and

Applications[M]. Machinery Industry Press, 2008 (In Chinese).

[8] Xue-Yi Qi, Yijiang Cai, Jiang Wu. Simulation of Air Conditioner

System with Variable Air Volume Based on Fuzzy PID Control[J].

Jiangsu University (Natural Science), 2005,26 (4) :364-368 (In

Chinese).

[9] J. Kim, M.A. Horowitz, and G. Wei, Design of CMOS

adaptive-bandwidth PLL/DLLs: A general approach, IEEE

Trans.CIircuits and SystemsII: Analogand Digital Signal

Processing,Vol. 50, pp. 860-869, Nov. 2003.

[10] Jinkun Liu. Advanced PID control and simulation under Matlab[M].

Electronic Industry Press, 2003 (In Chinese).

7153

Você também pode gostar

- A Fast Locking All-Digital Phase-Locked Loop Via TechniqueDocumento12 páginasA Fast Locking All-Digital Phase-Locked Loop Via TechniquesanoopmkAinda não há avaliações

- Power-Efficient Calibration and Reconfiguration For On-Chip Optical CommunicationDocumento6 páginasPower-Efficient Calibration and Reconfiguration For On-Chip Optical CommunicationsanoopmkAinda não há avaliações

- Compensation TechniqueDocumento4 páginasCompensation TechniquesanoopmkAinda não há avaliações

- A Fast Locking All-Digital Phase-Locked Loop Via Feed-Forward Compensation TechniqueDocumento12 páginasA Fast Locking All-Digital Phase-Locked Loop Via Feed-Forward Compensation TechniquesanoopmkAinda não há avaliações

- E 022236243Documento8 páginasE 022236243sanoopmkAinda não há avaliações

- Unit4 KCVDocumento52 páginasUnit4 KCVsanoopmkAinda não há avaliações

- Unit3 KCVDocumento118 páginasUnit3 KCVsanoopmkAinda não há avaliações

- A Low-Jitter ADPLL Via A Suppressive Digital Filter and An Interpolation-Based Locking SchemeDocumento6 páginasA Low-Jitter ADPLL Via A Suppressive Digital Filter and An Interpolation-Based Locking SchemesanoopmkAinda não há avaliações

- Unit2 KCVDocumento47 páginasUnit2 KCVsanoopmkAinda não há avaliações

- Unit6 KCVDocumento44 páginasUnit6 KCVsanoopmkAinda não há avaliações

- Unit5 KCVDocumento122 páginasUnit5 KCVsanoopmkAinda não há avaliações

- Line Follower ATMEGA16 WWW - Robotechno.usDocumento17 páginasLine Follower ATMEGA16 WWW - Robotechno.usSarang WadekarAinda não há avaliações

- Fibre Optic SimulationDocumento14 páginasFibre Optic SimulationSyam BabuAinda não há avaliações

- Ijpcsc 26Documento4 páginasIjpcsc 26sanoopmkAinda não há avaliações

- Ir Remote Based Stepper Motor Control PDFDocumento70 páginasIr Remote Based Stepper Motor Control PDFsanoopmk100% (1)

- Manual de MatlabDocumento5 páginasManual de MatlabLeo ClarkAinda não há avaliações

- Xilinx10.1 Quick Start PDFDocumento28 páginasXilinx10.1 Quick Start PDFsupriyasenapatiAinda não há avaliações

- Driving Unipolar Stepper Motors Using C51/C251: Application NoteDocumento15 páginasDriving Unipolar Stepper Motors Using C51/C251: Application Noteani8888Ainda não há avaliações

- Transposed Form FIR Filters: Core Generator ToolDocumento18 páginasTransposed Form FIR Filters: Core Generator ToolsanoopmkAinda não há avaliações

- Bart MSProject Report May 2005Documento35 páginasBart MSProject Report May 2005sanoopmkAinda não há avaliações

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNo EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNota: 4 de 5 estrelas4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)No EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Nota: 4 de 5 estrelas4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingNo EverandThe Little Book of Hygge: Danish Secrets to Happy LivingNota: 3.5 de 5 estrelas3.5/5 (399)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNo EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNota: 4 de 5 estrelas4/5 (5794)

- Never Split the Difference: Negotiating As If Your Life Depended On ItNo EverandNever Split the Difference: Negotiating As If Your Life Depended On ItNota: 4.5 de 5 estrelas4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNo EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNota: 4.5 de 5 estrelas4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNo EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNota: 3.5 de 5 estrelas3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerNo EverandThe Emperor of All Maladies: A Biography of CancerNota: 4.5 de 5 estrelas4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNo EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNota: 4 de 5 estrelas4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyNo EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyNota: 3.5 de 5 estrelas3.5/5 (2219)

- Team of Rivals: The Political Genius of Abraham LincolnNo EverandTeam of Rivals: The Political Genius of Abraham LincolnNota: 4.5 de 5 estrelas4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNo EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNota: 4.5 de 5 estrelas4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNo EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNota: 4.5 de 5 estrelas4.5/5 (265)

- The Unwinding: An Inner History of the New AmericaNo EverandThe Unwinding: An Inner History of the New AmericaNota: 4 de 5 estrelas4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)No EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Nota: 4.5 de 5 estrelas4.5/5 (119)

- IATA Travel Agent HandbookDocumento32 páginasIATA Travel Agent HandbookCaro Seijas100% (7)

- 1794 FLEX I/O Analog, TC and RTD Modules Specifications: Technical DataDocumento28 páginas1794 FLEX I/O Analog, TC and RTD Modules Specifications: Technical DataKelly Johana Moreno MendozaAinda não há avaliações

- Hsslive HSS First Term Exam Time Table Revised PDFDocumento1 páginaHsslive HSS First Term Exam Time Table Revised PDFCricket Creator100% (1)

- Impact of Next-Gen Technologies On Marketing: Manpreet SinghDocumento23 páginasImpact of Next-Gen Technologies On Marketing: Manpreet SinghRoronoa ZoldyckAinda não há avaliações

- A Teen Trader FTR Indicator: DisclosureDocumento14 páginasA Teen Trader FTR Indicator: DisclosureMohamad ehteshamAinda não há avaliações

- M817 13 4-GO-LW A4 E ScreenDocumento19 páginasM817 13 4-GO-LW A4 E ScreenRikyAinda não há avaliações

- User Manual: Flow-States For Growth, Prosperity and Spiritual EvolutionDocumento6 páginasUser Manual: Flow-States For Growth, Prosperity and Spiritual EvolutionTezcatzinAinda não há avaliações

- ECE OLED TechnologyDocumento22 páginasECE OLED Technologygourav VermaAinda não há avaliações

- Remote SensingDocumento31 páginasRemote SensingKousik BiswasAinda não há avaliações

- SLHT Grade 7 CSS Week 2Documento6 páginasSLHT Grade 7 CSS Week 2princeyahweAinda não há avaliações

- Rev.8 RBMviewDocumento216 páginasRev.8 RBMviewdford8583Ainda não há avaliações

- Luxmeter: Downloaded From Manuals Search EngineDocumento12 páginasLuxmeter: Downloaded From Manuals Search Enginemetrologueha1Ainda não há avaliações

- Volcano Rabbit Videos, Photos and Facts - Romerolagus Diazi - ArkiveDocumento4 páginasVolcano Rabbit Videos, Photos and Facts - Romerolagus Diazi - ArkiveFer OssAinda não há avaliações

- SEC Form ICA-RRDocumento1 páginaSEC Form ICA-RRPatrick HarrisAinda não há avaliações

- Gerald Prince A Dictionary of Narratology PDFDocumento5 páginasGerald Prince A Dictionary of Narratology PDFAl GhamAinda não há avaliações

- Important Reminders: Step 1Documento4 páginasImportant Reminders: Step 1rmrd86w5h5Ainda não há avaliações

- IT Essentials Chapter 9 Exam Answers 2018 2019 Version 6.0 100% IT Essentials Chapter 9 Exam Answers 2018 2019 Version 6.0 100%Documento6 páginasIT Essentials Chapter 9 Exam Answers 2018 2019 Version 6.0 100% IT Essentials Chapter 9 Exam Answers 2018 2019 Version 6.0 100%Egy RenataAinda não há avaliações

- Fortiap SeriesDocumento41 páginasFortiap SeriesKamel BoumazaAinda não há avaliações

- Kubernetes Troubleshooting DocsDocumento15 páginasKubernetes Troubleshooting Docschandrashekar_ganesanAinda não há avaliações

- EK205 Quick Reference Guide enDocumento12 páginasEK205 Quick Reference Guide enmohamedwalyAinda não há avaliações

- Erased Log by SosDocumento2 páginasErased Log by SosStefanAinda não há avaliações

- Uml 3 PGDocumento114 páginasUml 3 PGGurwinder SinghAinda não há avaliações

- Bdkm2103 Introductory Marketing CommunicationDocumento12 páginasBdkm2103 Introductory Marketing Communicationdicky chongAinda não há avaliações

- Sony Hvr-V1j U N e P C Ver1.3Documento504 páginasSony Hvr-V1j U N e P C Ver1.3DanAinda não há avaliações

- Intelligent Systems in Big Data, Semantic Web and Machine LearningDocumento6 páginasIntelligent Systems in Big Data, Semantic Web and Machine LearningRachid BelfaqihAinda não há avaliações

- Lesson 1 Comprog2Documento21 páginasLesson 1 Comprog2api-288708232Ainda não há avaliações

- CV of Fairuz Areefin KhanDocumento2 páginasCV of Fairuz Areefin KhanAbu SaleahAinda não há avaliações

- Vdocuments - MX - ptc04 II Epon Access Hardware Installation Manualpdf PDFDocumento23 páginasVdocuments - MX - ptc04 II Epon Access Hardware Installation Manualpdf PDFJuan Ayala SizalimaAinda não há avaliações

- Oracle Database AdministratorDocumento3 páginasOracle Database Administratorapi-122235783Ainda não há avaliações

- 6.189: Introduction To Programming in Python: Course SyllabusDocumento6 páginas6.189: Introduction To Programming in Python: Course SyllabusexemplariAinda não há avaliações