Escolar Documentos

Profissional Documentos

Cultura Documentos

Puerto Paralelo

Enviado por

SergiomaguuDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Puerto Paralelo

Enviado por

SergiomaguuDireitos autorais:

Formatos disponíveis

CONTROL BSICO DEL PUERTO PARALELO PGINA NMERO 1

Control Bsico del Puerto Paralelo Control Bsico del Puerto Paralelo Control Bsico del Puerto Paralelo Control Bsico del Puerto Paralelo

Desde sus comienzos el puerto paralelo ha sido la principal interfaz

para la conexin de perifricos a la computadora, esto se debe a su

versatilidad y a que todas las computadoras poseen al menos uno. Pese a

su creciente popularidad siempre fue un reto manejar este puerto

debidamente por causa de la gran cantidad de sucesivas modificaciones que

se le han realizado al diseo original.

Fsicamente el puerto paralelo es identificado por el usuario por su

caracterstico conector de 25 pines (hembra). Es importante diferenciar bien

el conector del puerto paralelo de otros conectores, el texto est orientado

totalmente al conector descrito (DB25), aunque es posible encontrar viejas

placas controladoras con un conector de 36 pines tipo Centronics; se debe

tener especial precaucin al identificar el conector ya que algunos, si bien

cada vez menos, dispositivos SCSI utilizan el mismo tipo de conector para

su enlace con dispositivos externos. Es posible que una computadora posea

ms de un puerto paralelo, generalmente se pueden tener hasta tres,

aunque Windows y otros programas tienen capacidad para manejar hasta

cuatro de ellos; se debe tener en cuenta que el hecho de que estn instaladas las placas

controladoras, no significa que los puertos estn en condiciones de ser utilizados, para esto

deben estar configurados apropiadamente.

Debido a los cambios que se le han hecho al puerto paralelo, se definieron a lo largo de

su historia distintos estndares, por lo que debemos conocer por lo menos de forma breve cada

una de las normas para saber como es el puerto con que estamos trabajando.

Cada puerto paralelo posee una direccin Base, es decir, una direccin con la que se

identifica al puerto, y segn el tipo de puerto de que se trate, podr tener adems otra

direcciones (Base+1, Base+2, Base+3, etc.). Actualmente las direcciones por defecto para los

puertos son las siguientes:

Puerto Direccin base

LPT1 0x378

LPT2 0x278

LPT3 0x3BC

El BIOS (Basic Input/Output Services) construye una tabla en memoria cuando arranca

la computadora desde la direccin 40:08h a 40:0Dh que contiene las direcciones base de cada

puerto paralelo instalado, leyendo esta tabla de manera ordenada se puede conocer la

direccin base de cada puerto. En lenguaje C la tabla se puede leer como se muestra a

continuacin.

Peek(0x40 , 6 + 2 * LPTnum);

Tipos de Puerto

Es posible encontrar los siguientes tipos de puertos, por orden de aparicin.

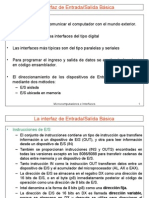

1.- SPP: Es el puerto ms sencillo, tiene tres buses o registros, en la direccin Base:

bus de datos, ste es de 8 bits y todos sus pines son salidas; en la direccin Base+1: bus de

estado, en ste registro slo 5 pines se encuentran cableados al conector, y todos ellos son

entradas, en las impresoras son los que llevan la informacin de Papel Atascado, Falta de

Papel, etc., una de las entradas (el bit 7) est complementada; por ltimo, en la direccin

Base+2: bus de control, este bus tiene cuatro salidas, de la cuales tres estn negadas.

CONTROL BSICO DEL PUERTO PARALELO PGINA NMERO 2

Direccin Base + 0: registro o bus de datos

Direccin Base + 1: registro o bus de estado

Direccin Base + 2: registro o bus de control

LPT1 LPT2 LPT3

Bus de Datos 0x378 0x278 0x3BC

Bus de Estado 0x379 0x279 0x3BD

Bus de Control 0x37A 0x27A 0x3BE

2.- Bidireccional (PS/2): Este puerto tiene las mismas caractersticas que el SPP con la

diferencia que el bus de datos es bidireccional, es decir que cambiando el estado de algunos

bits del bus de control se puede actuar sobre el bus de datos haciendo que trabaje en su

totalidad como entradas o como salidas (no se puede configurar algunos pines como entrada y

otros como salida).

Entrada: para configurar el bus de datos como entradas, se deben poner en

nivel alto el bit 5 y 7 del bus de control y en nivel bajo el bit 6 del bus de control.

Salida: para configurar el bus de datos como entradas, se deben llevar a nivel

bajo el bit 5 y 7 del bus de control y a nivel alto el bit 6 del bus de control.

Para hacer esto utilizaremos el concepto de mscara: supongamos que el bus de

control tiene contenido X (suponiendo que el registro es de un byte: xxxxxxxx),

entonces, a los bits que queramos poner en cero, les haremos una operacin AND,

con un nmero que tenga cero en los bits del mismo peso, y para poner a nivel

alto, lo que debemos hacer es realizar de forma anloga una OR. En el ejemplo se

configura el bus de datos como entrada.

Estado inicial del bus de control xxxxxxxx

AND

01011111

0x0xxxxx

OR

01000000

010xxxxx

3.- EPP (Enhaced Parallel Port): Este tipo de puerto tiene la caracterstica de ser tan

rpido como el bus del sistema (ISA), alcanzando velocidades de transferencia de hasta 1Mb

por segundo, fue desarrollado por Intel, Xircom y Zenith y tuvo amplia aceptacin por el resto

de los fabricantes, quienes comenzaron a construir sus puertos de tipo EPP, aunque no

totalmente compatibles con los creados por Intel, lo que llev a que se produjera un estndar

denominado EPP 1.7, que tiempo despus se combin con el estndar IEEE 1284, que

describe los puertos bidireccionales de alta velocidad para impresoras y se form un estndar

que actualmente se denomina IEEE 1284 EPP. Un puerto paralelo del estilo IEEE1284 soporta

mltiples modos: SPP, bidireccional PS/2, EPP y ECP. Otra particularidad de este puerto es

que posee otras cinco direcciones (desde Base+3 a Base+7), aunque esto hace que no pueda

existir un tercer puerto en la direccin 3BCh, ya que de ser as se solapara con las direcciones

asignadas a video. Es por esto que cuando se creo el puerto EPP, la direccin que antes sola

ser el primer puerto, paso a ser el tercero.

4.- ECP (Extended Capabilities Port): Puede, al igual que el EPP, escribir y leer a la

velocidad del bus, fue desarrollado por Microsoft y Hewlett Packard, y se distingue del anterior

por tener DMA (Direct Memory Access), FIFO (First In First Out) y compresin de datos. A su

vez puede emular los puertos del tipo SPP y bidireccional, y si bien la norma no contempla los

EPP, algunos fabricantes suelen usar algn bit no utilizado por ECP para la configuracin del

puerto como EPP. El puerto ECP agrega adems los registros desde Base+400h; a

Base+402h, en el cual est el registro ECR (Extended Control Register), mediante el cual se

pueden configurar los diferentes modos, el significado de los bits es el siguiente:

CONTROL BSICO DEL PUERTO PARALELO PGINA NMERO 3

Bit Significado

000 SPP (Compatible ISA)

001 Bidireccional (compatible PS/2)

010 Centronics rpido (Compatible ISA FIFO)

011 ECP

100 Reservado (EPP)

101 Reservado

110 Prueba

7:5

111 Configuracin

4 Deshabilita interrupciones de ERROR

3 Habilita DMA

2 Deshabilita el servicio de interrupcin FIFO/Terminal Count

1 Slo lectura (FIFO lleno)

0 Slo lectura (FIFO vaco)

ACLARACIN: Si el bit 3 es puesto a uno y el 2 a cero, se generar una interrupcin

en DMA - Terminal Count, por lo que este bit deber ser puesto a cero para limpiar la bandera

de interrupcin TC.

Si el puerto se encuentra configurado en el modo SPP o bidireccional se puede

cambiar a otro modo, por otro lado, si se est en otro modo se debe pasar primero a SPP o

bidireccional y luego al modo que se desee; a su vez, si estamos en el modo 010 111 y el bit

de direccin est en cero, debemos esperar a que la FIFO se borre antes de cambiar a los

modos 000 o 001.

En el modo 111, la direccin Base+400h ser el registro de configuracin A y la

direccin Base+401h ser el registro de configuracin B, aunque no se explicar cada bit de

estos registros puesto que escapa a los contenidos exigidos del curso.

Deteccin del Tipo de Puerto

Como ya se ha dicho el puerto puede ser de tipo SPP (comn), bidireccional

(compatible con el estndar IBM PS/2), EPP o ECP. Para conocer que tipo de puerto es el que

se tiene se debe comenzar testeando el de mayor complejidad y seguir en orden hasta el de

menor complejidad.

PRECAUCIN: Si la direccin base del puerto que se va a evaluar es 3BCh, no se

debe realizar la prueba de puerto ECP ni EPP, puesto que estas pruebas implican alterar

registros correspondientes a direcciones asignadas a video.

Deteccin de Puerto ECP

Para detectar si el puerto es de tipo ECP se debe leer el registro de control extendido

(ECR) en la direccin Base+402h y verificar que el bit 0 est en uno y el bit 1 est en cero;

estos bits no deben ser susceptibles de los cambios producidos en los bits 0 y 1 del bus de

control, por lo que otra prueba a realizar es poner en bajo el bit 0 y en alto el bit 1 del bus

mencionado, hecho esto, verificar que los bits del registro extendido de control no haya

cambiado; por ltimo, los bits 0 y 1 del registro extendido de control son de slo lectura, lo que

implica que no ser posible hacerlos cambiar de estado, entonces podemos escribir un dato

que conmute los estados de los bits 0 y 1 y luego leer el estado de esos bits, como lo que se

lee es lo que hay en el registro y no lo que se envi, podemos decir que si los bits no han

cambiado de estado y se han verificado las pruebas anteriores, estamos en presencia de un

puerto ECP.

Deteccin de Puerto EPP

Si el puerto fallase en las pruebas para determinar si es ECP, debemos proseguir

efectuando pruebas para comprobar, ahora, si es EPP. Para esto, se pone en nivel bajo el bit 7

del bus de estado y el bit de TimeOut (bit 0 del registro de estado), debido a la diversidad de

fabricantes existen distintos mtodos para limpiar este ltimo bit, por eso debemos contemplar

todos ellos para asegurar el funcionamiento en la mayor cantidad de mquinas posible, lo

CONTROL BSICO DEL PUERTO PARALELO PGINA NMERO 4

primero que haremos ser escribir el bit dos veces con un uno y luego pasarlo a cero, podemos

verificar ahora que el bit en cuestin est en nivel bajo, de no ser as, ya podemos descartar

que se trate de un puerto de tipo EPP. La segunda parte de la prueba consiste en escribir un

dato en el registro Base+3, y al no haber ningn perifrico que responda a la escritura

realizada, el bit de TimeOut deber cambiar su estado lgico a un uno, de no ser as debemos

seguir con las pruebas para determinar si el puerto es bidireccional o SPP.

Deteccin de Puerto Bidireccional (PS2 Compatible)

En esta prueba lo que haremos ser configurar el bus de datos como entrada y verificar

que al sacar un dato por el puerto no sea retenido.

Deteccin de Puerto SPP

Para detectar si un puerto es SPP verificamos la retencin de los datos enviados, para

lo cual enviamos un par de valores al bus de datos y comprobamos (en la direccin base) que

los valores ledos sean lo que se escribieron, es decir que el dato enviado haya sido retenido

por el puerto.

El Puerto Paralelo a Nivel Fsico

Direccin del puerto

(hexadecimal)

LPT1 LPT2 LPT3

Bit Pin DB-25 Entrada o Salida

Funcin Especial

Asignada al Pin

0 2 Entrada/Salida -

1 3 Entrada/Salida -

2 4 Entrada/Salida -

3 5 Entrada/Salida -

4 6 Entrada/Salida -

5 7 Entrada/Salida -

6 8 Entrada/Salida -

B

u

s

d

e

D

a

t

o

s

378 278 3BC

7 9 Entrada/Salida -

0 NC Lectura/Escritura -

1 NC - -

2 NC - -

3 15 Entrada Error

4 13 Entrada Printer On line

5 12 Entrada Out of Paper

6 10 Entrada Acknowledge

B

u

s

d

e

E

s

t

a

d

o

379 279 3BD

7 11 Entrada Complementada Busy

0 1 Salida Complementada Strobe

1 14 Salida Complementada Line Feed

2 16 Salida Initialize Printer

3 17 Salida Complementada Select Printer

4 NC - -

5 NC - -

6 NC - -

B

u

s

d

e

C

o

n

t

r

o

l

37A 27A 3BE

7 NC - -

Cuando se transmite informacin por un cable multipar (con varios conductores

aislados), cada conductor genera un campo electromagntico que influye en los otros

conductores, para reducir tal efecto el cable se confecciona enroscando un conductor sobre su

CONTROL BSICO DEL PUERTO PARALELO PGINA NMERO 5

retorno, de manera que los campos generados por cada conductor se anulen entre si y no

afecten a los otros; a su vez estos pares trenzados se enroscan nuevamente para evitar la

interferencia con otros cables. Tambin hay otras opciones que complementan la antes

mencionada a la hora de transmitir datos por un cable: para poder aumentar la longitud del

cable es necesario que el mismo posea mayor inmunidad al ruido, especialmente los de baja

frecuencia como los de la red elctrica, lo que se logra con una malla metlica que envuelve a

todos los conductores conectada a masa (chasis de la computadora), pero cuando la longitud

es considerable y los datos se transmiten a gran velocidad el cable debe ser considerado como

una lnea de transmisin, con todas las propiedades que esta posee, es entonces donde se

observa la necesidad de que el cable tenga un terminador para evitar los rebote de seal hacia

su fuente.

Cuando se dise el puerto paralelo tambin se dividieron las masas segn las seales

como lo indica la siguiente tabla, aunque actualmente es muy comn observarlas todas unidas,

lo que no est del todo mal, puesto que los circuitos de salida contienen todos la misma masa,

ya que con el nivel de integracin de hoy en da todos los buffer de salida estn prcticamente

en un mismo integrado, y de esta manera la corriente tomar el camino con menor impedancia

para su retorno.

Pin 18 Retorno de masa correspondiente a: C0 y D0

Pin 19 Retorno de masa correspondiente a: D1 y D2

Pin 20 Retorno de masa correspondiente a: D3 y D4

Pin 21 Retorno de masa correspondiente a: D5 y D6

Pin 22 Retorno de masa correspondiente a: D7 y S6

Pin 23 Retorno de masa correspondiente a: C3

Pin 24 Retorno de masa correspondiente a: S7

Pin 25 Retorno de masa correspondiente a: C2

Interrupciones

La mayora de los puertos paralelos son capaces de detectar interrupciones generadas

por el perifrico que se encuentre conectado. Para que el microprocesador detecte la

interrupcin el puerto debe tener asignado un Interrupt Request Level (IRQ). Generalmente se

utiliza IRQ7 para LPT1 e IRQ5 para LPT2, aunque este ltimo suele estar asociado con la

placa de sonido, por lo que es posible observar que los puertos tengan configurado otro IRQ.

Canales DMA

Los puertos de tipo ECP utilizan Direct Memory Access (DMA) para una transferencia a

mayor velocidad, hay que remarcar que utilizando DMA, mientras se produce la transferencia el

microprocesador est libre para ejecutar otra accin, el rango que utiliza el puerto paralelo es

de cero a tres.

El Puerto y su Hardware

El puerto trabaja con lgica TTL de baja potencia de tipo Schottky, aunque en puertos

viejos es posible encontrar algunos que trabajen con salidas de tipo colector abierto. La

corriente drenada del puerto puede tomar valores de hasta 2,6mA y la entregada hasta un

mximo de 24mA, aunque debido a la cantidad de fabricantes y a la falta o desconocimiento de

normas es conveniente no acercarse al mximo que aqu se menciona. En cuanto a las

tensiones de salida, el nivel bajo corresponde una tensin entre 0V y 0,8V, y para el nivel alto

la tensin de salida es de 2,4V a 5,5V.

En algunos de los puertos se pueden encontrar tambin capacitores de 2,2nF entre las lneas

de E/S y masa, lo que ayuda a establecer los tiempos de subida y de bajada de la seal,

especialmente cuando se transmite a altas velocidades donde es muy importante la deteccin

del flanco.

En el bus de control, generalmente, las salidas son de tipo TTL a colector abierto, con

resistencias de colector de 4,7K y teniendo en cuenta que lo que se lee por programa es el

estado del pin del puerto, es posible utilizar este bus como entradas, aunque esto no es

CONTROL BSICO DEL PUERTO PARALELO PGINA NMERO 6

recomendable, ya que como se ha mencionado antes no hay una norma firme respecto a la

electrnica interna; en el caso de querer hacerlo hay que poner a cero los bits del bus de

control que se vayan a utilizar como entrada, de esta manera los transistores de salida quedan

al corte, entonces, al quedar el colector sin nivel de masa se puede aplicar tensin al pin sin

provocar dao alguno.

En lenguaje C:

int inportb(int port)

esta funcin entrega un valor entero correspondiente a la lectura del

puerto almacenado en la variable entera port.

void outportb(int port, int value)

esta funcin escribe el valor almacenda en la variable entera value en

el puerto almacenado en la variable entera port.

Adems es necesario conocer las funciones para operar con bits:

~ X

NOT X

X & Y

X AND Y

X | Y

X OR Y

X ^ Y

X X-OR Y

X >> n

Desplazamiento hacia derecha de X, n posiciones

X << n Desplazamiento hacia izquierda de X, n posiciones

Funciones para la configuracin del bus de datos como entrada y como salida:

void BusDatosEntrada(int Base)

{

outportb(Base+2,(inportb(Base+2)|160) & 191);

return;

};

void BusDatosSalida(int Base)

{

outportb(Base+2,(inportb(Base+2)|64) & 95);

return;

};

Buffer de lectura Pin Conector

Comando de Salida

4K7

+5V

Você também pode gostar

- TPP003 - MartinilloDocumento2 páginasTPP003 - MartinilloArturo Avilés R.Ainda não há avaliações

- Prácticas de redes de datos e industrialesNo EverandPrácticas de redes de datos e industrialesNota: 4 de 5 estrelas4/5 (5)

- Manual Del At89c51Documento9 páginasManual Del At89c51Asdrubal GonzalezAinda não há avaliações

- Tecnologia 3 PDFDocumento20 páginasTecnologia 3 PDFDavidCangasCeniceros88% (8)

- Curso básico de teclado - Lecciones iniciales sobre el teclado y las notas musicalesDocumento26 páginasCurso básico de teclado - Lecciones iniciales sobre el teclado y las notas musicaleshuvillamilAinda não há avaliações

- Curso básico de teclado - Lecciones iniciales sobre el teclado y las notas musicalesDocumento26 páginasCurso básico de teclado - Lecciones iniciales sobre el teclado y las notas musicaleshuvillamilAinda não há avaliações

- Reporte Puertos Serial, Paralelo y USBDocumento12 páginasReporte Puertos Serial, Paralelo y USBGustavoAinda não há avaliações

- Introducción Al Psoc5Lp: Teoría y aplicaciones prácticaNo EverandIntroducción Al Psoc5Lp: Teoría y aplicaciones prácticaAinda não há avaliações

- Conocimientos Básicos Del Microcontrolador ATmega 328mientos Básicos Del Microcontrolador ATmega 328Documento32 páginasConocimientos Básicos Del Microcontrolador ATmega 328mientos Básicos Del Microcontrolador ATmega 328AngelCuevas100% (2)

- El Puerto LPTDocumento11 páginasEl Puerto LPTJose Marpartida CaceresAinda não há avaliações

- Puerto ParaleloDocumento41 páginasPuerto Paraleloedith02_18Ainda não há avaliações

- Proyecto InvestigacionDocumento68 páginasProyecto Investigaciontuxb92% (12)

- Anexo - Practica 4 - Descripción Del Puerto ParaleloDocumento11 páginasAnexo - Practica 4 - Descripción Del Puerto ParaleloAlan Garrido ValenciaAinda não há avaliações

- Puerto ParaleloDocumento6 páginasPuerto ParaleloAndrés A. PavónAinda não há avaliações

- Cuadernillo de Trabajo Tecnologia - 1Documento59 páginasCuadernillo de Trabajo Tecnologia - 1Roberto Montes ChavezAinda não há avaliações

- Interfaces de E/S básicas y sus instruccionesDocumento72 páginasInterfaces de E/S básicas y sus instruccionesJorge Gianotti HidalgoAinda não há avaliações

- Tema 06 - Puerto ParaleloDocumento18 páginasTema 06 - Puerto ParaleloOmar Milton Condori PeñaAinda não há avaliações

- El Puerto Paralelo Del PC PDFDocumento9 páginasEl Puerto Paralelo Del PC PDFPa SolAinda não há avaliações

- Puerto ParaleloDocumento12 páginasPuerto ParaleloSanchez T. MarioAinda não há avaliações

- db25Documento24 páginasdb25goyoelenAinda não há avaliações

- UNIDAD V - Sistemas Programables - TemarioDocumento8 páginasUNIDAD V - Sistemas Programables - TemarioAnonymous uoxMueAinda não há avaliações

- Unidad Entrada SalidaDocumento9 páginasUnidad Entrada SalidaPatriciaAinda não há avaliações

- Lab 7Documento53 páginasLab 7Ern SantosAinda não há avaliações

- Puertos ParalelosDocumento5 páginasPuertos ParalelosjavierAinda não há avaliações

- 2 Instrumentacion Mecatronica Puerto ParaleloDocumento8 páginas2 Instrumentacion Mecatronica Puerto Paralelosusys_666Ainda não há avaliações

- Puertos ParalelosDocumento10 páginasPuertos ParalelosCésar David HernándezAinda não há avaliações

- Induccion Microcontroladores PIC (Control Automatico Educacion) PDFDocumento79 páginasInduccion Microcontroladores PIC (Control Automatico Educacion) PDFlord593Ainda não há avaliações

- Tema 2Documento11 páginasTema 2Angel MartinezAinda não há avaliações

- S04s1 - Arq - PDS - Manejo de Puertos in - Out - Matlab X-XC16Documento41 páginasS04s1 - Arq - PDS - Manejo de Puertos in - Out - Matlab X-XC16renatto2089Ainda não há avaliações

- Significado de Paralelo y La Sigla LPTDocumento3 páginasSignificado de Paralelo y La Sigla LPTBetsie GuerreroAinda não há avaliações

- Tema 4.4 Programación Del Puerto ParaleloDocumento6 páginasTema 4.4 Programación Del Puerto ParaleloLuuizPossible IndianaAinda não há avaliações

- Puertos de Entrada/SalidaDocumento5 páginasPuertos de Entrada/SalidaAlán Montes De Oca ArcosAinda não há avaliações

- Programación de microcontroladores ATmega con división binariaDocumento4 páginasProgramación de microcontroladores ATmega con división binariaAngelogc2014Ainda não há avaliações

- Consulta 5 AyalaDocumento7 páginasConsulta 5 AyalaEDSON MISAEL RODR�GUEZ GARC�AAinda não há avaliações

- Ppi 8255Documento3 páginasPpi 8255Anonymous brY7BSidmAinda não há avaliações

- Catedra Interface A Perifericos 8255 PPIDocumento15 páginasCatedra Interface A Perifericos 8255 PPIMauricioAinda não há avaliações

- Sistemas Programables Unidad 5 TodoDocumento17 páginasSistemas Programables Unidad 5 TodoDeyvid Fifa CheAinda não há avaliações

- Proyecto Basico Puerto ParaleloDocumento4 páginasProyecto Basico Puerto Paralelooz7378Ainda não há avaliações

- Capítulo 2 - Puertos de Entrada y Salida PDFDocumento54 páginasCapítulo 2 - Puertos de Entrada y Salida PDFAndrea LHAinda não há avaliações

- Manejo de TablasDocumento5 páginasManejo de TablasPabloAinda não há avaliações

- Características y modos de funcionamiento del puerto paralelo 8255Documento29 páginasCaracterísticas y modos de funcionamiento del puerto paralelo 8255StalinCazaAinda não há avaliações

- El Puerto ParaleloDocumento3 páginasEl Puerto ParaleloRichard MeloAinda não há avaliações

- PuertosDocumento21 páginasPuertosErick BravoAinda não há avaliações

- Presentación de Unidad 3Documento51 páginasPresentación de Unidad 3José Armando Cruz VillaAinda não há avaliações

- Ppi 8255Documento4 páginasPpi 8255Mario GonzalezAinda não há avaliações

- Lab 03 Puertos de Entrada y SalidaDocumento15 páginasLab 03 Puertos de Entrada y SalidaJames Jerry YTAinda não há avaliações

- Arquitectura Del Microprocesador z80Documento9 páginasArquitectura Del Microprocesador z80Nilyan BertiAinda não há avaliações

- Puertos de Entrada y SalidaDocumento55 páginasPuertos de Entrada y SalidaJuanfer PCAinda não há avaliações

- Manejo Puerto Paralelo en LabviewDocumento7 páginasManejo Puerto Paralelo en LabviewI-ván Zandalio CAinda não há avaliações

- Tutorial Puertos 74ls373Documento19 páginasTutorial Puertos 74ls373ab_chilangoAinda não há avaliações

- Manipulacion de Puertos en Lenguaje CDocumento12 páginasManipulacion de Puertos en Lenguaje CSalvador Soria SalgadoAinda não há avaliações

- Puerto ParaleloDocumento8 páginasPuerto Paralelocuentas y mas cuentasAinda não há avaliações

- Como Usar Un Puerto de OrdenadorDocumento4 páginasComo Usar Un Puerto de OrdenadorDaniel CastroAinda não há avaliações

- Programación puertos E/S microcontroladoresDocumento9 páginasProgramación puertos E/S microcontroladoresPris ChucAinda não há avaliações

- PRACTICA 01: Operaciones Con Puertos I/O en EnsambladorDocumento17 páginasPRACTICA 01: Operaciones Con Puertos I/O en EnsambladorAns Shel Cardenas YllanesAinda não há avaliações

- EntregableDocumento11 páginasEntregablePAOLO VIZCONDE DIAZAinda não há avaliações

- Introducción A Los MicroprocesadoresDocumento10 páginasIntroducción A Los MicroprocesadoresBibiano Cortés ToledoAinda não há avaliações

- Microprocesador 8085Documento9 páginasMicroprocesador 8085Martín LañónAinda não há avaliações

- Configuración de Puertos de e - SDocumento30 páginasConfiguración de Puertos de e - Ssofy naranjoAinda não há avaliações

- Practica 15 RelojDocumento12 páginasPractica 15 RelojEmmanuel GonzalezAinda não há avaliações

- Puertos de ES y Su InterfazDocumento72 páginasPuertos de ES y Su InterfazAndres RomeroAinda não há avaliações

- Micro 8051Documento14 páginasMicro 8051Hugo ReyesAinda não há avaliações

- Tema 5Documento3 páginasTema 5HanniaGarciaAinda não há avaliações

- Procesos 01Documento4 páginasProcesos 01Manuel Beltran NoguesAinda não há avaliações

- Funcionamiento interno del 8085Documento7 páginasFuncionamiento interno del 8085Percy VillegasAinda não há avaliações

- Microcontrolador PIC18F2550Documento12 páginasMicrocontrolador PIC18F2550Franco Quispe ClementeAinda não há avaliações

- Instalar RockolaDocumento6 páginasInstalar RockolahuvillamilAinda não há avaliações

- Knoppix MantenimientoDocumento17 páginasKnoppix MantenimientohuvillamilAinda não há avaliações

- Cómo Construir Una Casa para El Perro - 19 PasosDocumento3 páginasCómo Construir Una Casa para El Perro - 19 PasoshuvillamilAinda não há avaliações

- Tenología 7Documento2 páginasTenología 7huvillamilAinda não há avaliações

- Diseño e Implementación de Un Laboratorio de Control A DistanciaDocumento4 páginasDiseño e Implementación de Un Laboratorio de Control A DistanciahuvillamilAinda não há avaliações

- COMPUMAXDocumento63 páginasCOMPUMAXhuvillamilAinda não há avaliações

- Tecnología Educativa, Medios de Comunicación y Métodos de Introducción.Documento78 páginasTecnología Educativa, Medios de Comunicación y Métodos de Introducción.Erick Andrade OvalleAinda não há avaliações

- Paola ConteDocumento11 páginasPaola ContehuvillamilAinda não há avaliações

- Texto N4Documento1 páginaTexto N4huvillamilAinda não há avaliações

- WQB 09Documento16 páginasWQB 09huvillamilAinda não há avaliações

- UMH LaboratoriosRemotos03 PDFDocumento7 páginasUMH LaboratoriosRemotos03 PDFhuvillamilAinda não há avaliações

- Lab Rem Virtual Ing Control Basado en Foundation FieldbusDocumento5 páginasLab Rem Virtual Ing Control Basado en Foundation FieldbushuvillamilAinda não há avaliações

- Remote Labs CUDIDocumento33 páginasRemote Labs CUDIhuvillamilAinda não há avaliações

- Weblab Deusto ImplementaciónLabRemtDistrBasWeb2.0Documento36 páginasWeblab Deusto ImplementaciónLabRemtDistrBasWeb2.0huvillamilAinda não há avaliações

- Desarrollo de Proyectos de Investigacion Final 17.6.2010.doc-138Documento99 páginasDesarrollo de Proyectos de Investigacion Final 17.6.2010.doc-138Nathaly HenaoAinda não há avaliações

- Matriz DDocumento6 páginasMatriz DhuvillamilAinda não há avaliações

- Ejemplo de La Matriz DOFADocumento3 páginasEjemplo de La Matriz DOFAPablo Alejandro OrtegaAinda não há avaliações

- Metodos Tecnicas InvestigacionDocumento93 páginasMetodos Tecnicas Investigacionhuvillamil100% (2)

- Emprendimiento e Innovación en Colombia ¿Que Nos Está Haciendo Falta?Documento16 páginasEmprendimiento e Innovación en Colombia ¿Que Nos Está Haciendo Falta?Red de Emprendedores100% (1)

- Matriz DOFADocumento2 páginasMatriz DOFAhuvillamilAinda não há avaliações

- Lectura FODADocumento9 páginasLectura FODACandace Kemp100% (1)

- METODDocumento209 páginasMETODjairohacker100% (2)

- Para Que Sirve La Matriz DOFADocumento2 páginasPara Que Sirve La Matriz DOFAhuvillamilAinda não há avaliações

- PDF Cartilla Identificacion y Valoracion de La Idea de NegociosDocumento58 páginasPDF Cartilla Identificacion y Valoracion de La Idea de NegocioshuvillamilAinda não há avaliações