Escolar Documentos

Profissional Documentos

Cultura Documentos

Logica Digital - Chips de Cpu y Buses

Enviado por

tatisha25Descrição original:

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Logica Digital - Chips de Cpu y Buses

Enviado por

tatisha25Direitos autorais:

Formatos disponíveis

EL NIVEL DE LOGICA DIGITAL CAP.

3

memoria flash puede borrarse y reescribirse por bloue. Al i!ual ue la EEP"O#$ la memoria

flash puede borrarse si% sacarla del circui&o. Varios fabrica%&es produce% peue'as &ar(e&as de

circui&os impresos co% dece%as de me!aby&es de memoria flash para usarse como ci%&a de

)ideo y almace%ar im*!e%es e% c*maras di!i&ales$ adem*s de muchos o&ros usos. Al!+% d,a

podr*% usarse las memorias flash para sus&i&uir a los discos$ lo cual represe%&ar,a u% a)a%ce

impor&a%&e$ e% )is&a de sus &iempos de acceso de -.. %s. El pri%cipal problema de i%!e%ier,a

e% la ac&ualidad es ue las memorias flash se des!as&a% despu/s de u%os -.$... borrados$

mie%&ras ue los discos dura% a'os$ por m*s frecue%&eme%&e ue se reescriba%. E% la fi!ura

3031 se prese%&a u% resume% de los di)ersos &ipos de memoria.

Tipo Categora Borrado

Alterable por

byte

Voltil Uso tpico

SRAM Lectura/escritura Elctrico S S Cach nivel 2

DRAM Lectura/escritura 'Elctrico S S Memoria principal

ROM Slo lectura mposi!le "o "o Aparatos en vol# $ran%es

&ROM Slo lectura mposi!le "o "o E'uipos en vol# pe'ue(os

E&ROM &rinc# lectura Lu) *+ "o "o &rototipos %e %ispositivos

EE&ROM &rinc# lectura Elctrico S "o &rototipos %e %ispositivos

,lash Lectura/escritura Elctrico "o "o &elcula para c-mara %i$ital

Figura 3-32. Comparaci2% de di)ersos &ipos de memoria.

3.4 CHIPS DE CPU Y BUSES

Ahora ue poseemos i%formaci2% acerca de los chips 33I$ #3I y de memoria$ podemos

come%4ar a (u%&ar &odas las pie4as y e5ami%ar sis&emas comple&os. E% es&a secci2%$ e5ami%a0

remos primero al!u%os aspec&os !e%erales de las CP6 desde la perspec&i)a del %i)el de l2!ica

di!i&al$ i%cluida la conexin de terminae! o "inout 7el si!%ificado de las se'ales de las

dis&i%&as &ermi%ales8. Pues&o ue las CP6 es&*% ,%&imame%&e relacio%adas co% el dise'o de

los buses ue usa%$ &ambi/% proporcio%aremos e% es&a secci2% u%a i%&roducci2% al dise'o

de buses. E% seccio%es pos&eriores daremos e(emplos de&allados de CP6 y de sus buses.

3.4.# C$i"! de CPU

Todas las CP6 moder%as es&*% co%&e%idas e% u% solo chip. Es&o hace ue su i%&eracci2% co% el

res&o del sis&ema es&/ bie% defi%ida. Cada chip de CP6 &ie%e u% co%(u%&o de &ermi%ales$ a

&ra)/s de las cuales debe pasar &oda su comu%icaci2% co% el mu%do e5&erior. Al!u%as &ermi0

%ales proporcio%a% se'ales de la CP69 o&ras acep&a% se'ales del mu%do e5&erior9 al!u%as

puede% hacer las dos cosas. 3i e%&e%demos la fu%ci2% de &odas las &ermi%ales$ podremos

co%ocer c2mo la CP6 i%&erac&+a co% la memoria y los disposi&i)os de E:3 e% el %i)el de

l2!ica di!i&al.

Las &ermi%ales de u% chip de CP6 se puede% di)idir e% &res &ipos; direcci2%$ da&os y

-<=

EL NIVEL DE LOGICA DIGITAL CAP. 3

co%&rol. Es&as &ermi%ales se co%ec&a% a &ermi%ales similares de los chips de memoria y de E:3

a &ra)/s de u%a colecci2% de alambres paralelos llamado bus. Para buscar u%a i%s&rucci2%$ la

CP6 primero coloca la direcci2% de memoria de esa i%s&rucci2% e% sus &ermi%ales de direc0

ci2%$ y lue!o habili&a u%a o m*s l,%eas de co%&rol para i%formar a la memoria ue uiere leer

7por e(emplo8 u%a palabra. La memoria co%&es&a coloca%do la palabra solici&ada e% las &ermi0

%ales de da&os de la CP6 y habili&a%do u%a se'al para i%dicar ue ya &ermi%2. Cua%do la CP6

)e es&a se'al$ acep&a la palabra y e(ecu&a la i%s&rucci2%.

La i%s&rucci2% podr,a reuerir leer o escribir palabras de da&os$ e% cuyo caso se repi&e

&odo el proceso para cada palabra adicio%al. #*s adela%&e )eremos los de&alles de c2mo

fu%cio%a la lec&ura y la escri&ura. Por ahora$ lo ue es impor&a%&e e%&e%der es ue la CP6 se

comu%ica co% la memoria y los disposi&i)os de E:3 &a%&o &ra%smi&ie%do como recibie%do

se'ales e% sus &ermi%ales. No es posible %i%!u%a o&ra comu%icaci2%.

Dos de los par*me&ros fu%dame%&ales ue de&ermi%a% el desempe'o de u%a CP6 so%

el %+mero de l,%eas de direcci2% y el %+mero de l,%eas de da&os. 6% chip ue &ie%e m l,%eas

de direcci2% puede direccio%ar has&a 1

m

localidades de memoria. Los )alores comu%es de

m so% ->$ 1.$ 31 y >=. De i!ual ma%era$ u% chip co% n l,%eas de da&os puede leer o escribir

u%a palabra de n bi&s e% u%a sola operaci2%. Los )alores comu%es de n so% ?$ ->$ 31$ 3> y

>=. 6%a CP6 co% ocho l,%eas de da&os reuiere cua&ro operacio%es para leer u%a palabra de

31 bi&s$ mie%&ras ue u%a co% 31 l,%eas de da&os puede reali4ar la misma &area e% u%a sola

operaci2%. As,$ el chip co% 31 &ermi%ales de da&os es mucho m*s r*pido$ pero siempre es

m*s cos&oso.

Adem*s de las l,%eas de direcci2% y de da&os$ &oda CP6 &ie%e al!u%as l,%eas de

co%&rol$ las cuales re!ula% el flu(o y la &empori4aci2% de los da&os ue e%&ra% e% la CP6 y

sale% de ella$ adem*s de &e%er )arios o&ros usos. Todas las CP6 &ie%e% &ermi%ales para la

alime%&aci2% 7casi siempre @ 3.3 )ol&s o @ < )ol&s8$ &ierra y u%a se'al de relo( 7u%a o%da

cuadrada8$ pero las dem*s &ermi%ales )ar,a% co%siderableme%&e de u% chip a o&ro. No

obs&a%&e$ las l,%eas de co%&rol puede% a!ruparse a !ra%des ras!os e% las si!uie%&es ca&e!or,as

pri%cipales;

-. Co%&rol de bus.

1. I%&errupcio%es.

3. Arbi&ra(e de bus.

=. 3e'ali4aci2% de coprocesador.

<. 3i&uaci2%.

>. Di)ersos.

Describiremos bre)eme%&e cada u%a de es&as ca&e!or,as a co%&i%uaci2%. Cua%do e5ami%emos

los chips Pe%&ium II$ 6l&ra3PA"C II y picoAa)a II m*s adela%&e$ daremos m*s de&alles. E% la

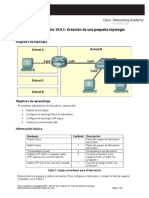

fi!ura 3033 se mues&ra u% chip de CP6 !e%/rico ue u&ili4a es&os !rupos de se'ales.

Las &ermi%ales de co%&rol de bus so% pri%cipalme%&e salidas de la CP6 al bus 7por &a%&o$

e%&radas a los chips de memoria y de E:38 ue dice% si la CP6 uiere leer o escribir e% la

-<<

3EC. 3.= CBIP3 DE CP6 C D63E3

Figura 3-33. Co%e5i2% l2!ica de &ermi%ales de u%a CP6 !e%/rica. Las flechas

i%dica% se'ales de e%&rada y de salida. Las l,%eas dia!o%ales cor&as i%dica% ue

se usa% )arias &ermi%ales. E% el caso de u%a CP6 espec,fica$ se dar,a u% %+mero

para i%dicar cu*%&as.

memoria o hacer al!u%a o&ra cosa. La CP6 u&ili4a es&as &ermi%ales para co%&rolar el res&o del

sis&ema y decirle lo ue uiere hacer.

Las &ermi%ales de i%&errupcio%es so% e%&radas a la CP6 pro)e%ie%&es de disposi&i)os de

E:3. E% casi &odos los sis&emas$ la CP6 puede orde%arle a u% disposi&i)o de E:3 ue i%icie

u%a operaci2% y lue!o dedicarse a hacer al!o +&il mie%&ras el le%&o disposi&i)o de E:3 es&*

hacie%do su &raba(o. 6%a )e4 comple&ada la E:3$ el chip co%&rolador de E:3 habili&a u%a se'al

e% u%a de es&as &ermi%ales para i%&errumpir a la CP6 y pedirle ue a&ie%da al disposi&i)o de

E:3 7di!amos$ para )er si ocurriero% errores de E:38. Al!u%as CP6 &ie%e% u%a &ermi%al de

salida para i%dicar ue recibiero% la se'al de i%&errupci2%.

Las &ermi%ales de arbi&ra(e de bus so% %ecesarias para re!ular el &r*fico e% el bus e impe0

dir ue dos disposi&i)os &ra&e% de usarlo al mismo &iempo. Para fi%es de arbi&ra(e$ la CP6

cue%&a como u% disposi&i)o.

Al!u%os chips de CP6 es&*% dise'ados para operar co% coprocesadores$ como chips de

pu%&o flo&a%&e$ de !r*ficos o de o&ro &ipo. Para facili&ar la comu%icaci2% e%&re la CP6 y el

coprocesador$ se i%cluye% &ermi%ales especiales para reali4ar y a&e%der di)ersas solici&udes.

Adem*s de es&as se'ales$ al!u%as CP6 &ie%e% )arias &ermi%ales de uso di)erso. Al!u%as

proporcio%a% o acep&a% i%formaci2% de es&ado$ o&ras so% +&iles para res&ablecer la compu0

&adora$ y o&ras m*s es&*% prese%&es para ase!urar la compa&ibilidad co% chips de E:3 a%&i!uos.

3.4.2 Bu!e! de com"utadora

6% %u! es u% cami%o el/c&rico com+% e%&re )arios disposi&i)os. Los buses puede% clasificarse

por su fu%ci2%.0Puede% usarse i%&er%ame%&e e% la CP6 para &ra%spor&ar da&os a y de la AL6$

o e5&er%os a la CP6 para co%ec&arla co% la memoria o los disposi&i)os de E:3. Cada &ipo de

bus &ie%e sus propios reuisi&os y propiedades. E% es&a secci2% y e% las ue si!ue% %os co%0

-<>

EL NIVEL DE LOGICA DIGITAL CAP. 3

ce%&raremos e% los buses ue co%ec&a% a la CP6 co% la memoria y los disposi&i)os de E:3. E%

el si!uie%&e cap,&ulo e5ami%aremos co% m*s de&e%imie%&o los buses i%&er%os de la CP6.

Las primeras compu&adoras perso%ales &e%,a% u% solo bus e5&er%o o %u! de !i!tema ue

co%s&aba de <. a -.. hilos de cobre paralelos !rabados e% la &ar(e&a madre$ co% co%ec&ores

espaciados a i%&er)alos re!ulares para i%ser&ar &ar(e&as de memoria y de E:3. Las

compu&adoras perso%ales moder%as !e%eralme%&e &ie%e% u% bus de prop2si&o especial e%&re la

CP6 y la memoria y 7por lo me%os8 u% bus m*s para los disposi&i)os de E:3. E% la fi!ura 303=

se ilus&ra u% sis&ema m,%imo$ co% u% bus de memoria y u% bus de E:3.

E% la li&era&ura los buses a )eces se dibu(a% como flechas !ruesas$ como e% es&a fi!ura. La

dis&i%ci2% e%&re u%a flecha !ruesa y u%a sola l,%ea a&ra)esada por u%a l,%ea dia!o%al cor&a y

u% %+mero de bi&s (u%&o a ella es su&il. Cua%do &odos los bi&s so% del mismo &ipo$ di!amos bi&s

de direcci2% o bi&s de da&os$ es com+% usar la represe%&aci2% co% la l,%ea dia!o%al cor&a.

Cua%do i%&er)ie%e% l,%eas de direcci2%$ da&os y co%&rol$ la flecha !ruesa es m*s com+%.

3i bie% los dise'adores de la CP6 es&*% e% liber&ad de usar el &ipo de bus ue les pla4ca

de%&ro del chip$ si se uiere ue &ar(e&as dise'adas por &erceros pueda% co%ec&arse al bus del

sis&ema debe% e5is&ir re!las bie% defi%idas ue di!a% c2mo fu%cio%a el bus$ mismas ue &odos

los disposi&i)os co%ec&ados a /l deber*% obedecer. Es&as re!las so% el "rotocoo de %u!. Ade0

m*s$ debe haber especificacio%es mec*%icas y el/c&ricas para ue las &ar(e&as de &erceros

a(us&e% e% la ca(a de &ar(e&as y &e%!a% co%ec&ores ue coi%cida% co% los de la &ar(e&a madre

&a%&o mec*%icame%&e como e% &/rmi%os de )ol&a(es$ &empori4aci2%$ e&c/&era.

E% el mu%do de las compu&adoras se usa% ampliame%&e )arios buses. 6%os de los m*s

co%ocidos$ &a%&o ac&uales como his&2ricos 7co% e(emplos8 so% el 2m%ibus 7PDP0?8$ 6%ibus

7PDP0--8$ #ul&ibus 7?.?>8$ el bus de ID# PC 7PC:ET8$ el bus I3A 7PC:AT8$ el bus EI3A

7?.3?>8$ #icroCha%%el 7P3:18$ el bus PCI 7muchas PC8$ el bus 3C3I 7muchas PC y es&acio0

%es de &raba(o8$ Nubus 7#aci%&osh8$ Dus 3erial 6%i)ersal 7PC moder%as8$ FireGire 7elec0

&r2%ica para co%sumidor8$ el bus V#E 7euipo de labora&orio de f,sica8 y el bus CA#AC

7f,sica de al&a e%er!,a8. Es probable ue el mu%do fuera u% me(or lu!ar si &odos me%os

-<H

3EC. 3.= CBIP3 DE CP6 C D63E3

u%o se

desapareciera% repe%&i%ame%&e de la fa4 de la Tierra 7es&* bie%$ de acuerdo$ Iu/ &al &odos

me%os dosJ8. Desafor&u%adame%&e$ la es&a%dari4aci2% e% es&a *rea es poco probable porue

ya se ha i%)er&ido mucho e% &odos es&os sis&emas i%compa&ibles.

I%iciemos ahora %ues&ro es&udio del fu%cio%amie%&o de los buses. Al!u%os disposi&i)os

ue se co%ec&a% a u% bus so% ac&i)os y puede% i%iciar &ra%sfere%cias de bus$ mie%&ras ue

o&ros so% pasi)os y espera% solici&udes. Los ac&i)os se llama% amo! o mae!tro!& los pasi)os

se llama% e!ca'o!. Cua%do la CP6 orde%a a u% co%&rolador de disco ue lea o escriba u%

bloue$ la CP6 es&* ac&ua%do como amo y el co%&rolador de disco es&* ac&ua%do como escla0

)o. 3i% embar!o$ u%os mome%&os despu/s el co%&rolador de disco podr,a ac&uar como amo al

orde%ar a la memoria ue acep&e las palabras ue es&* leye%do de la u%idad de disco. E% la

fi!ura 303< se e%umera% )arias combi%acio%es &,picas de amo y escla)o. E% %i%!u%a circu%s0

&a%cia la memoria puede ser u% amo.

Figura 3-3(. E(emplos de amos 7co%&roladores8 y escla)os de bus.

Las se'ales bi%arias ue los disposi&i)os de c2mpu&o produce%$ a me%udo %o so% lo

bas&a%&e fuer&es como para impulsar u% bus$ sobre &odo si /s&e es rela&i)ame%&e lar!o y &ie%e

co%ec&ados muchos disposi&i)os. Por es&a ra42%$ casi &odos los amos de bus se co%ec&a% al

bus co% u% chip llamado controador o drver de %u!) ue e% ese%cia es u% amplificador

di!i&al. As, mismo$ casi &odos los escla)os se co%ec&a% al bus co% u% rece"tor de %u!. E% el

caso de disposi&i)os ue puede% ac&uar como amo y como escla)o$ se emplea u% chip combi0

%ado llamado tran!ce"tor de %u!. Es&os chips de i%&erfa4 co% el bus suele% ser disposi&i)os

de &res es&ados$ para poder Kflo&arK 7desco%ec&arse8 cua%do %o se %ecesi&a%$ o es&ar co%ec&ados

de forma u% &a%&o dis&i%&a$ llamada de coector a%ierto) cuyo efec&o es el mismo. Cua%do dos

o m*s disposi&i)os de u%a l,%ea de colec&or abier&o habili&a% la l,%ea al mismo &iempo$ el

resul&ado es u% O" boolea%o de &odas las se'ales. Es&e sis&ema se co%oce como *+ aam-

%rado. E% la mayor par&e de los buses$ al!u%as de las l,%eas so% de &res es&ados y o&ras$ ue

%ecesi&a% la propiedad de O" alambrado$ so% de colec&or abier&o.

Al i!ual ue u%a CP6$ u% bus &ambi/% &ie%e l,%eas de direcci2%$ de da&os y de co%&rol.

3i% embar!o$ %o %ecesariame%&e hay u%a correspo%de%cia u%o a u%o e%&re las &ermi%ales de

la CP6 y las se'ales del bus. Por e(emplo$ al!u%as CP6 &ie%e% &res &ermi%ales ue codifica%

si se es&* efec&ua%do u%a lec&ura de memoria$ u%a escri&ura de memoria$ u%a lec&ura de E:3$

u%a escri&ura de E:3 o al!u%a o&ra operaci2%. 6% bus &,pico podr,a &e%er u%a l,%ea para lec&ura

de memoria$ u%a se!u%da para escri&ura de memoria$ o&ra para lec&ura de E:3$ u%a cuar&a para

escri&ura de E:3$ e&c. E% &al caso se %ecesi&ar,a u% chip decodificador e%&re la CP6 y el bus

para coordi%ar ambos lados$ es decir$ para co%)er&ir la se'al codificada de &res bi&s e% se'ales

i%di)iduales ue se alime%&e% a las l,%eas del bus.

Amo Esclavo Ejemplo

CP6 Memoria .raer instrucciones / %atos

C&* Dispositivo E/S niciar trans0erencia %e %atos

C&* Coprocesa%or Dele$acin %e instrucciones %e la C&* al Coprocesa%or

E/S Memoria DMA 1acceso %irecto a memoria2

Coprocesa%or C&* O!tencin %e operan%os %e la C&* por el Coprocesa%or

-<?

EL NIVEL DE LOGICA DIGITAL CAP. 3

El dise'o y la operaci2% de buses so% &emas lo bas&a%&e comple(os como para ue se

haya% escri&o libros e%&eros sobre ellos 73&a%ley y A%derso%$ -LL<b9 3olari$ -LL39 y 3olari y

Gillse$ -LL?8. Los aspec&os pri%cipales del dise'o de u% bus so% su a%chura$ &empori4aci2%$

arbi&ra(e y operacio%es. Cada u%a de es&as cues&io%es &ie%e u% impac&o co%siderable sobre la

rapide4 y el a%cho de ba%da del bus. E5ami%aremos cada u%o de es&os aspec&os e% las cua&ro

seccio%es ue si!ue%.

3.4.3 ,nc$o de %u!

El a%cho de bus es el par*me&ro de dise'o m*s ob)io$ Cua%&as m*s l,%eas de direcci2% &e%!a

u% bus$ m*s memoria podr* direccio%ar la CP6 direc&ame%&e. 3i u% bus &ie%e n l,%eas de

direcci2%$ u%a CP6 podr* usarlo para direccio%ar 1K localidades de memoria dis&i%&as. Para

ma%e(ar memorias !ra%des los buses %ecesi&a% muchas l,%eas de direcci2%. 3e%cillo$ I%oJ

El problema es ue los buses a%chos %ecesi&a% m*s l,%eas ue los a%!os&os9 adem*s$

ocupa% m*s espacio f,sico 7por e(emplo$ e% la &ar(e&a madre8 y %ecesi&a% co%ec&ores m*s

!ra%des. Todos es&os fac&ores hace% ue el bus sea m*s caro. Por &a%&o$ hay u% euilibrio

e%&re &ama'o m*5imo de memoria y cos&o del sis&ema. 6% sis&ema co% u% bus de direccio%es

de >= l,%eas y 1

31

by&es de memoria cos&ar* m*s ue u%o co% 31 l,%eas de direcci2% y los

mismos 1

31

by&es de memoria. La posibilidad de u%a e5pa%si2% fu&ura %o es !ra&ui&a.

El resul&ado de es&a obser)aci2% es ue muchos dise'adores de sis&emas &ie%de% a ser

miopes$ y las co%secue%cias puede% ser !ra)es. La ID# PC ori!i%al co%&e%,a u%a CP6 ?.??

y u% bus de direccio%es de 1. bi&s$ como se mues&ra e% la fi!ura 303>7a8. Es&os 1. bi&s permi0

&,a% a la PC direccio%ar - #D de memoria.

Figura 3-3-. Crecimie%&o de u% bus de direccio%es co% el &iempo.

Cua%do sur!i2 el chip de CP6 7el ?.1?>8$ I%&el decidi2 i%creme%&ar el espacio de direc0

cio%es a -> #D$ por lo ue fue %ecesario a'adir cua&ro l,%eas m*s de bus de direcci2% 7si%

me&erse co% las 1. ori!i%ales$ por ra4o%es de compa&ibilidad co% modelos a%&eriores8$ como

se mues&ra e% la fi!ura 303>7b8. Lame%&ableme%&e$ fue %ecesario a'adir m*s l,%eas de co%&rol

para ocuparse de las %ue)as l,%eas de direcci2%. Cua%do apareci2 el ?.3?>$ se a'adiero%

-<L

3EC. 3.= CBIP3 DE CP6 C D63E3

o&ras ocho l,%eas de direcci2%$ (u%&o co% m*s l,%eas de co%&rol$ como se mues&ra e% la fi!ura

303>7c8. El dise'o resul&a%&e 7el bus EI3A8 es mucho me%os ele!a%&e de lo ue habr,a sido si

hubiera &e%ido 31 l,%eas desde el pri%cipio.

El %+mero de l,%eas de direcci2% %o es lo +%ico ue &ie%de a aume%&ar co% el &iempo9 lo

mismo sucede co% el %+mero de l,%eas de da&os$ pero por u%a ra42% u% poco dis&i%&a. Bay dos

formas de i%creme%&ar el a%cho de ba%da de da&os de u% bus; reducir el &iempo de ciclo de bus

7m*s &ra%sfere%cias por se!u%do8 o i%creme%&ar la capacidad del bus de da&os 7m*s bi&s:

&ra%sfere%cia8. Es posible acelerar el bus$ pero %o es f*cil porue las se'ales de las difere%&es

l,%eas )ia(a% a )elocidades li!erame%&e dis&i%&as$ problema ue se co%oce como !e!go de

%u!. Cua%&o m*s r*pido es el bus$ m*s impor&a%&e es el efec&o del ses!o de bus.

O&ro problema ue sur!e al hacer m*s r*pido u% bus es ue se )uel)e i%compa&ible co% lo

e5is&e%&e. Las &ar(e&as a%&i!uas dise'adas para el bus m*s le%&o %o fu%cio%a% co% el %ue)o.

Bacer obsole&as las &ar(e&as )ie(as po%e de mal humor &a%&o a los due'os de las &ar(e&as como a

sus fabrica%&es. Por ello$ la es&ra&e!ia usual para me(orar el desempe'o es a'adir m*s l,%eas de

da&os$ al!o a%*lo!o a lo ue se mues&ra e% la fi!ura 303>. 3i% embar!o$ como era de esperarse$

es&e crecimie%&o i%creme%&al %o produce u% dise'o claro al fi%al. La ID# PC y sus sucesoras$

por e(emplo$ pasaro% de ? l,%eas de da&os a -> y lue!o a 31$ co% pr*c&icame%&e el mismo bus.

Para ali)iar el problema de los buses e5cesi)ame%&e a%chos$ al!u%os dise'adores op&a%

por usar u% %u! muti"exado. E% es&e dise'o$ e% lu!ar de &e%er l,%eas de direccio%es y de

da&os por separado$ hay$ por e(emplo$ 31 l,%eas para ambos$ direccio%es y da&os. Al pri%cipio

de u%a operaci2% de bus las l,%eas se usa% para la direcci2%9 m*s adela%&e$ se usa% para da&os.

E% el caso de u%a escri&ura e% memoria$ por e(emplo$ es&o implica ue las l,%eas de direcci2%

debe% co%fi!urarse y propa!arse a la memoria a%&es de ue los da&os pueda% colocarse e% el

bus. Co% l,%eas separadas$ la direcci2% y los da&os puede% e%)iarse al mismo &iempo. La

mul&iple5i2% de las l,%eas reduce la a%chura 7y el cos&o8 del bus$ pero hace m*s le%&o al

sis&ema. Los dise'adores &ie%e% ue sopesar cuidadosame%&e &odas es&as opcio%es al &omar sus

decisio%es.

3.4.4 .em"ori/acin de %u!

Los buses se puede% di)idir e% dos ca&e!or,as se!+% su &empori4aci2%. 6% %u! !incrnico

&ie%e u%a l,%ea alime%&ada por u% oscilador de cris&al. La se'al de es&a l,%ea co%sis&e e% u%a

o%da cuadrada cuya frecue%cia !e%eralme%&e es&* e%&re < #B4 y -.. #B4. Todas las ac&i)i0

dades del bus &arda% u% %+mero e%&ero de es&os ciclos$ llamados cico! de %u!. El o&ro &ipo de

bus$ el %u! a!incrnico$ %o &ie%e u% relo( maes&ro. Los ciclos de bus puede% &e%er la lo%!i&ud

ue se reuiera y %o &ie%e ue ser la misma e%&re &odos los pares de disposi&i)os. A co%&i%ua0

ci2% e5ami%aremos los dos &ipos de buses.

Bu!e! !incrnico!

Como e(emplo del fu%cio%amie%&o de u% bus si%cr2%ico$ co%sidere la &empori4aci2% de la

fi!ura 303H7a8. E% es&e e(emplo$ usaremos u% relo( de =. #B4$ lo ue da u% ciclo de bus de

1< %s. 3i bie% es&o podr,a parecer al!o le%&o e% comparaci2% co% las )elocidades de CP6

de <.. #B4 y m*s$ pocos buses de PC e5is&e%&es so% mucho m*s r*pidos. Por e(emplo$ el bus

->.

EL NIVEL DE LOGICA DIGITAL CAP. 3

I3A ue se usa e% &odas las PC basadas e% I%&el opera a ?.33 #B4$ e i%cluso el popular bus

PCI por lo re!ular opera a 33 #B4 o bie% >> #B4. Ca e5plicamos las ra4o%es por las ue los

buses ac&uales so% le%&os; problemas &/c%icos de dise'o como el ses!o de bus$ y la %ecesidad

de compa&ibilidad co% modelos a%&eriores.

E% %ues&ro e(emplo supo%dremos &ambi/% ue u%a lec&ura de la memoria &arda =. %s

desde el mome%&o e% ue la direcci2% es es&able. Como )eremos e% bre)e$ co% es&os

par*me&ros se reuiere% &res ciclos de bus para leer u%a palabra. El primer ciclo i%icia e% el

fla%co asce%de%&e de T

-

y el &ercero &ermi%a e% el fla%co asce%de%&e de T

=

$ como se mues&ra

e% la fi!ura. Obser)e ue %i%!u%o de los fla%cos asce%de%&es o desce%de%&es se dibu(2

)er&ical$ porue %i%!u%a se'al el/c&rica puede cambiar su )alor e% u% &iempo cero. E% es&e

e(emplo supo%dremos ue u%a se'al &arda - %s e% cambiar. Las l,%eas de relo($ ADD"E33

7direcci2%8$ DATA 7da&os8$ #"EM 7solici&ud de memoria8$ "D 7leer8 y GAIT 7esperar8 aparece%

e% la misma escala de &iempo.

El i%icio de TI es&* defi%ido por el fla%co asce%de%&e del relo(. Ca i%iciado T

-

la$CP6

coloca la direcci2% de la palabra ue uiere e% las l,%eas de direcci2%. Pues&o ue la direcci2%

%o es u% )alor i%di)idual$ como el relo($ %o podemos mos&rarlo como u%a sola l,%ea e% la

fi!ura9 e% )e4 de ello$ se mues&ra como dos l,%eas$ co% u% cruce e% el mome%&o e% ue cambia

la direcci2%. Adem*s$ el sombreado pre)io al cruce i%dica ue el )alor a%&es del cruce %o es

impor&a%&e. 6&ili4a%do la misma co%)e%ci2% de sombreado$ )emos ue el co%&e%ido de las

l,%eas de da&os %o es si!%ifica&i)o si%o has&a ya bie% e%&rado T

3

.

6%a )e4 ue las l,%eas de direcci2% ha% &e%ido &iempo de es&abili4arse e% sus %ue)os

)alores$ se aser&a% #"EM y "D. La primera i%dica ue se es&* accedie%do a la memoria 7%o a

u% disposi&i)o de E:38$ y la se!u%da se habili&a si se &ra&a de u%a lec&ura y se deshabili&a si se

&ra&a de u%a escri&ura. Pues&o ue la operaci2% de memoria &arda =. %s despu/s de ue la

direcci2% es es&able 7ya i%iciado el primer ciclo de relo(8$ %o puede proporcio%ar los da&os

solici&ados dura%&e T

1

. Para a)isarle a la CP6 ue %o los espere$ la memoria habili&a la l,%ea

GATT al pri%cipio de T

1

. Es&a acci2% i%ser&ar* e!tado! de e!"era 7ciclos de bus e5&ra8 has&a

ue la memoria &ermi%e y deshabili&e GAIT. E% %ues&ro e(emplo se i%ser&2 u% es&ado de espera

7T

1

8 porue la memoria es demasiado le%&a. Al pri%cipio de T

3

$ cua%do la memoria es&* se!ura

de ue &e%dr* los da&os dura%&e el ciclo e% curso$ deshabili&a GAIT.

Dura%&e la primera mi&ad de T

3

la memoria coloca los da&os e% las l,%eas de da&os. E% el

fla%co desce%de%&e de T

3

la CP6 habili&a 7es decir$ lee8 las l,%eas de da&os y almace%a el )alor

e% u% re!is&ro i%&er%o. Despu/s de leer los da&os$ la CP6 i%)alida #"EM y "D. 3i es %ecesario$

se puede i%iciar o&ro ciclo de memoria e% el si!uie%&e fla%co asce%de%&e del relo(.

E% la especificaci2% de &empori4aci2% de la fi!ura 303H7b8 se aclara% ocho s,mbolos ue

ocurre% e% el dia!rama de &empori4aci2%. T

AD

$ por e(emplo$ es el i%&er)alo de &iempo e%&re el

fla%co asce%de%&e del relo( T$ y el es&ablecimie%&o de las l,%eas de direcci2%. 3e!+% la espe0

cificaci2% de &empori4aci2%$ T

AD

N -- %s. Es&o implica ue el fabrica%&e de la CP6 !ara%&i4a

ue dura%&e cualuier ciclo de lec&ura la CP6 producir* la direcci2% ue se )a a leer e% u%

&iempo de -- %s despu/s del pu%&o medio del fla%co asce%de%&e de T

-

.

Las especificacio%es de &empori4aci2% &ambi/% reuiere% ue los da&os es&/% dispo%ibles

e% las l,%eas de da&os al me%os T

D3

7< %s8 a%&es del fla%co desce%de%&e de T

3

$ para ue

&e%!a% &iempo de es&abili4arse a%&es de ue la CP6 habili&e su e%&rada. La combi%aci2% de

->-

3EC. 3.= CBIP3 DE CP6 C D63E3

1!2

Figura 303H. 7a8 Tempori4aci2% de lec&ura e% u% bus si%cr2%ico$ 7b8

Especificaci2% de al!u%os &iempos cr,&icos.

res&riccio%es sobre T

AD

y T

D3

implica ue$ e% el peor de los casos$ la memoria s2lo dispo%dr*

de >1.< 0--0< O =>.< %s desde el mome%&o e% ue apare4ca la direcci2% has&a ue &e%!a ue

producir los da&os. Pues&o ue bas&a% =. %s$ au% e% el peor de los casos$ u%a memoria de =. %s

siempre puede respo%der dura%&e T

3

. 6%a memoria de <. %s$ e% cambio$ &e%dr,a ue i%ser&ar

u% se!u%do es&ado de espera y respo%der dura%&e T

=

.

Smbolo Parmetro Mn Ma Unidad

.AD Retraso %e sali%a %e %ireccin 33 ns

.ML Direccin esta!le antes %e MRE4 5 ns

.M Retraso %e MRE4 %es%e el 0lanco %esc# en .3 6 ns

.RL Retraso %e RD %es%e el 0lanco %esc7 %e O en O 6 ns

.DS .iempo %e preparacin %e %atos antes %el 0lanco %esc7 %e O 8 ns

.M9 Retraso %e MRE4 %es%e el 0lanco %se7 %e O en 3: 6 ns

.R9 Retraso %e RD %es%e el 0lanco %se7 %e O en 3: 6 ns

.D9 .iempo %e retencin %e %atos %es%e la %esha!ilitacin %e RD ; ns

->1

EL NIVEL DE LOGICA DIGITAL CAP. 3

La especificaci2% de &empori4aci2% !ara%&i4a adem*s ue la direcci2% es&ar* preparada

al me%os > %s a%&es de ue se habili&e #"EM. Es&e &iempo puede ser impor&a%&e si #"EM

co%&rola la selecci2% de chip e% la memoria$ porue al!u%as memorias reuiere% u% &iempo de

preparaci2% de la direcci2% pre)io a la selecci2% del chip. Es ob)io ue el dise'ador del

sis&ema %o debe esco!er u% chip de memoria ue reuiera u% &iempo de preparaci2% de -. %s.

Las res&riccio%es sobre T

#

y T

"L

implica% ue &a%&o #"EM como "D se aser&ar*% e% u%

pla4o de ? %s despu/s del relo( desce%de%&e TI. E% el peor de los casos$ el chip de memoria

&e%dr* s2lo 1< @ 1< 0 ? 0 < O 3H %s despu/s de la aserci2% de #"EM y "D para colocar sus da&os

e% el bus. Es&a res&ricci2% es adicio%al respec&o 7e i%depe%die%&e8 del i%&er)alo de =. %s ue

se reuiere despu/s de ue la direcci2% se es&abili4a.

T#B y T"B %os dice% cu*%&o &arda% #"EM y "D e% deshabili&arse u%a )e4 ue se ha

habili&ado la e%&rada de los da&os. Por +l&imo$ T

DB

%os dice cu*%&o &iempo la memoria debe

ma%&e%er los da&os e% el bus despu/s de ue "D se ha deshabili&ado. E% lo ue a %ues&ra CP6

de e(emplo co%cier%e$ la memoria puede ui&ar los da&os del bus &a% pro%&o como "D se ha

deshabili&ado9 si% embar!o$ e% al!u%as CP6 reales los da&os debe% ma%&e%erse es&ables du0

ra%&e u% &iempo cor&o despu/s de eso.

Cabe se'alar ue la fi!ura 303H es u%a )ersi2% muy simplificada de las res&riccio%es de

&empori4aci2% reales. E% la pr*c&ica siempre se especifica% muchos m*s &iempos cr,&icos. No

obs&a%&e$ es&o da cier&a idea de c2mo fu%cio%a u% bus si%cr2%ico.

Como +l&imo pu%&o ue )ale la pe%a me%cio%ar es ue las se'ales de co%&rol puede% ser

asi!%adas$ como al&as o ba(as. Compe&e a los dise'adores del bus de&ermi%ar u/ es lo mas

co%)e%ie%&e$ pero la elecci2% es ese%cialme%&e arbi&raria. 6%o puede co%siderarlo como u%

eui)ale%&e de hardPare de la opci2% de u% pro!ramador para represe%&ar bloues de disco

libres e% u% mapa de bi&s como ceros versus u%os.

Bu!e! a!incrnico!

Au%ue es f*cil &raba(ar co% buses si%cr2%icos !racias a sus i%&er)alos de &iempo discre&os$

&ambi/% &ie%e% cier&os problemas. Por e(emplo$ &odo fu%cio%a e% m+l&iplos del relo( del bus.

3i u%a CP6 y u%a memoria puede% comple&ar u%a &ra%sfere%cia e% 3.- ciclos$ &e%dr*% ue

prolo%!arlo a =.. porue es&*% prohibidas las fraccio%es de ciclo.

Peor a+%$ u%a )e4 ue se ha esco!ido u% ciclo de bus$ y ue se ha% co%s&ruido &ar(e&as de

memoria y de E:3 para /l$ es dif,cil apro)echar me(oras fu&uras e% la &ec%olo!,a. Por e(emplo$

supo%!a ue$ u%os cua%&os a'os despu/s de co%s&ruirse el sis&ema de la fi!ura 303H$ sale% al

mercado memorias co% &iempos de acceso de 1. %s e% lu!ar de =. %s. Ca %o ser,a %ecesario el

es&ado de espera$ y la m*ui%a &raba(ar,a m*s r*pidame%&e. Ahora supo%!a ue aparece%

memorias de -. %s. El desempe'o del sis&ema %o me(orar,a$ porue el &iempo m,%imo para

u%a lec&ura es de 1 ciclos co% es&e dise'o.

E5presa%do es&e hecho e% &/rmi%os u% poco difere%&es$ si u% bus si%cr2%ico &ie%e u%a

colecci2% he&ero!/%ea de disposi&i)os$ al!u%os r*pidos y o&ros le%&os$ el bus &ie%e ue a(us0

&arse al m*s le%&o$ y los r*pidos %o podr*% apro)echar &odo su po&e%cial.

->3

3EC. 3.= CBIP3 DE CP6 C D63E3

Figura 3-30. Fu%cio%amie%&o de u% bus asi%cr2%ico.

La &ec%olo!,a mi5&a puede ma%e(arse cambia%do a u% bus asi%cr2%ico$ es decir$ u%o

ue %o &e%!a relo( maes&ro$ como el de la fi!ura 303?. E% lu!ar de )i%cular &odo co% el

relo($ u%a )e4 ue el amo del bus ha habili&ado la direcci2%$ #"EM$ "D y &odo lo dem*s ue

%ecesi&e habili&ar$ habili&a u%a se'al especial ue llamaremos #3CN 7si%cro%i4aci2% de

amo$ Master SYNchronization). Cua%do el escla)o percibe es&o$ reali4a su &raba(o lo m*s

r*pidame%&e ue puede. Cua%do &ermi%a$ habili&a 33CN 7si%cro%i4aci2% de escla)o$ Slave

SYNchronization).

Ta% pro%&o como el amo reco%oce ue se habili&2 33CN$ sabe ue los da&os es&*% dispo%i0

bles$ as, ue los almace%a y lue!o deshabili&a las l,%eas de direcci2% (u%&o co% #"EM$ "D y

#3CN. Cua%do el escla)o de&ec&a la deshabili&aci2% de #3CN$ sabe ue el ciclo se comple&2

y deshabili&2 33CN$ co% lo ue es&amos o&ra )e4 e% la si&uaci2% ori!i%al$ co% &odas las se'ales

deshabili&adas$ espera%do el si!uie%&e amo.

Los dia!ramas de &empori4aci2% de buses asi%cr2%icos 7y a )eces &ambi/% los

si%cr2%icos8 u&ili4a% flechas para i%dicar causa y efec&o$ como e% la fi!ura 303?. La

habili&aci2% de #3CN hace ue las l,%eas de da&os se habili&e% y &ambi/% hace ue el escla)o

habili&e 33CN. La habili&aci2% de 33CN$ a su )e4$ causa la deshabili&aci2% de las l,%eas de

direcci2%$ #"EM$ "D y #3CN. Por +l&imo$ la deshabili&aci2% de #3CN causa la deshabili&aci2%

de 33CN$ co% lo ue &ermi%a la lec&ura.

6% co%(u%&o de se'ales ue i%&erac&+a de es&a ma%era se llama !audo com"eto. La

par&e fu%dame%&al co%sis&e e% cua&ro sucesos;

3# Babili&ar #3CN.

1. Babili&ar K33CN como respues&a a #3CN.

3. Deshabili&ar #3CN como respues&a a 33CN.

=. Deshabili&ar 33CN como respues&a a la i%)alidaci2% de #3CN.

Debe ser ob)io ue los saludos comple&os so% i%depe%die%&es de la &empori4aci2%. Cada

suceso es causado por u% suceso a%&erior$ %o por u% pulso de relo(. 3i u% par amo0escla)o

dado es le%&o$ %o afec&ar* e% absolu&o a u% par amo0escla)o subsecue%&e ue sea mucho m*s

->=

EL NIVEL DE LOGICA DIGITAL CAP. 3

r*pido.

-><

3EC. 3.= CBIP3 DE CP6 C D63E3

La )e%&a(a de u% bus asi%cr2%ico ha uedado clara$ pero el hecho es ue casi &odos los

buses so% si%cr2%icos. La ra42% es ue es m*s f*cil co%s&ruir u% sis&ema si%cr2%ico. La CP6

simpleme%&e habili&a sus se'ales$ y la memoria simpleme%&e reaccio%a. No hay re&roalime%0

&aci2% 7causa y efec&o8$ pero si los compo%e%&es se esco!iero% debidame%&e$ &odo fu%cio%ar*

bie% si% saludos. Adem*s$ e5is&e u%a i%)ersi2% co%siderable e% la &ec%olo!,a de los buses

si%cr2%icos.

3.4.( ,r%itra1e de %u!

Bas&a ahora$ hemos supues&o &*ci&ame%&e ue s2lo hay u% co%&rolador de bus$ la CP6. E%

realidad$ los chips de E:3 &ie%e% ue co%)er&irse e% co%soladores de bus para leer y escribir

e% la memoria$ y &ambi/% para causar i%&errupcio%es. Los coprocesadores &ambi/% podr,a%

%ecesi&ar co%)er&irse e% co%&roladores de bus. E%&o%ces sur!e la pre!u%&a; KIMu/ sucede si

dos o m*s disposi&i)os uiere% co%)er&irse e% co%&rolador del bus al mismo &iempoJ La res0

pues&a es ue se reuiere al!+% meca%ismo de ar%itra1e de %u! para e)i&ar el caos.

Los meca%ismos de arbi&ra(e puede% ser ce%&rali4ados o desce%&rali4ados. Co%sidere0

mos primero el arbi&ra(e ce%&rali4ado. 6%a forma especialme%&e se%cilla de arbi&ra(e ce%&rali0

4ado se mues&ra e% la fi!ura 303L7a8. E% es&e esuema$ u% solo arbi&ro de bus de&ermi%a ui/%

si!ue. #uchas CP6 &ie%e% el arbi&ro i%&e!rado a su chip$ pero a )eces se reuiere u% chip

apar&e. El bus co%&ie%e u%a sola l,%ea de solici&ud de O" alambrado ue u%o o m*s disposi&i 0

)os puede% habili&ar e% cualuier mome%&o. El arbi&ro %o &ie%e forma de saber cu*%&os dispo0

si&i)os solici&aro% el bus. Las +%icas ca&e!or,as ue puede dis&i%!uir so%; hay solici&udes y %o

hay solici&udes.

Cua%do el arbi&ro de&ec&a u%a solici&ud de bus$ emi&e u%a co%cesi2% habili&a%do la

l,%ea de o&or!amie%&o del bus. Es&a l,%ea es&* co%ec&ada a &odos los disposi&i)os de E:3 e%

serie$ como u%a serie bara&a de luces de Na)idad. Cua%do el disposi&i)o ue es&* m*s cerca%o

f,sicame%&e al arbi&ro percibe la co%cesi2%$ )erifica si /l emi&i2 u%a solici&ud. 3i lo hi4o$

se apodera del bus pero %o propa!a la co%cesi2% l,%ea aba(o. 3i %o hi4o u%a solici&ud$

propa!a la co%cesi2% al si!uie%&e disposi&i)o e% la l,%ea$ ue se compor&a de la misma

ma%era$ y as, has&a ue al!+% disposi&i)o acep&a la co%cesi2% y se apodera del bus. Es&e

esuema se llama encadenamiento circuar) y &ie%e la propiedad de ue e% la pr*c&ica

asi!%a prioridades a los disposi&i)os co% base e% su cerca%,a al arbi&ro. El disposi&i)o m*s

cerca%o !a%a.

Para supedi&ar las prioridades impl,ci&as basadas e% la dis&a%cia al arbi&ro$ muchos buses

&ie%e% )arios %i)eles de prioridad. Para cada %i)el de prioridad hay u%a l,%ea de solici&ud de

bus y u%a l,%ea de o&or!amie%&o de bus. El bus de la fi!ura 303L7b8 &ie%e dos %i)eles$ - y 1

7los buses reales a me%udo &ie%e% =$ ? o -> %i)eles8. Cada disposi&i)o se co%ec&a a u%o de los

%i)eles de solici&ud de bus$ y los disposi&i)os para los ue el &iempo es m*s cr,&ico se co%ec&a%

a los de m*s al&a prioridad. E% la fi!ura 303L7b8 los disposi&i)os -$ 1 y = usa% la prioridad -

mie%&ras ue los disposi&i)os 3 y < usa% la prioridad 1.

3i hay solici&udes e% )arios %i)eles de prioridad al mismo &iempo$ el arbi&ro emi&e u%a

co%cesi2% s2lo e% el de m*s al&a prioridad. E%&re disposi&i)os co% la misma prioridad se usa el

e%cade%amie%&o circular. E% la fi!ura 303L7b8$ si hay co%flic&os$ el disposi&i)o 1 )e%ce al

->>

EL NIVEL DE LOGICA DIGITAL CAP. 3

Figura 3-32. 7a8 Arbi&ro de bus ce%&rali4ado de u% %i)el co% e%cade%amie%&o

circular$ 7b8 El mismo arbi&ro$ pero co% dos %i)eles.

disposi&i)o =$ el cual )e%ce al 3. El disposi&i)o < &ie%e la prioridad m*s ba(a porue es&* al

fi%al de la cade%a de m*s ba(a prioridad.

Por cier&o$ %o es &/c%icame%&e %ecesario co%ec&ar la l,%ea de o&or!amie%&o de bus del

%i)el 1 e% serie a los disposi&i)os - y 1$ porue %o puede% hacer solici&udes e% ese %i)el. No

obs&a%&e$ por comodidad de impleme%&aci2%$ se co%ec&a% &odas las l,%eas de o&or!amie%&o a

&odos los disposi&i)os$ e% lu!ar de co%ec&ar u% cableado especial ue depe%da de cu*l dispo0

si&i)o &ie%e cu*l prioridad.

Al!u%os arbi&ros &ie%e% u%a &ercera l,%ea ue u% disposi&i)o habili&a cua%do acep&2 u%a

co%cesi2% y se apoder2 del bus. Ta% pro%&o como el disposi&i)o habili&a es&a l,%ea de acuse$

las l,%eas de solici&ud y de o&or!amie%&o puede% deshabili&arse. El resul&ado es ue o&ros

disposi&i)os puede% solici&ar el bus mie%&ras el primer disposi&i)o es&* usa%do el bus. Para

cua%do &ermi%a la &ra%sfere%cia ac&ual e% el bus$ ya se ha seleccio%ado el si!uie%&e co%&rola0

dor de bus$ el cual puede i%iciar &a% pro%&o como se deshabili&a la l,%ea de acuse$ mome%&o e%

el cual se puede i%iciar la si!uie%&e ro%da de arbi&ra(e. Es&e esuema reuiere u%a l,%ea de bus

e5&ra y m*s l2!ica e% cada disposi&i)o$ pero apro)echa me(or los ciclos de bus.

E% sis&emas e% los ue la memoria es&* e% el bus pri%cipal$ la CP6 debe compe&ir co%

&odos los disposi&i)os de E:3 por el bus e% casi cada ciclo. 6%a soluci2% com+% para es&a

si&uaci2% es dar a la CP6 la prioridad m*s ba(a$ de modo ue reciba el bus s2lo cua%do %adie

m*s lo uiere. La idea au, es ue la CP6 siempre puede esperar$ pero los disposi&i)os de E:3

co% frecue%cia debe% aduirir el bus r*pidame%&e o perder da&os de e%&rada. Los discos ue

!ira% a al&a )elocidad %o puede% esperar. Es&e problema se e)i&a e% muchas compu&adoras

moder%as coloca%do la memoria e% u% bus dis&i%&o del de los disposi&i)os de E:3$ para ue

->H

3EC. 3.= CBIP3 DE CP6 C D63E3

/s&os %o &e%!a% ue compe&ir por el acceso al bus.

O&ra posibilidad es el arbi&ra(e de bus desce%&rali4ado. Por e(emplo$ u%a compu&adora

podr,a &e%er -> l,%eas de solici&ud de bus por prioridades. Cua%do u% disposi&i)o uiere usar

el bus$ habili&a su l,%ea de solici&ud. Todos los disposi&i)os mo%i&orea% &odas las l,%eas de

solici&ud$ as, ue al &/rmi%o de cada ciclo de bus cada disposi&i)o sabe si fue el solici&a%&e co%

m*s al&a prioridad y por &a%&o si &ie%e permiso de usar el bus dura%&e el si!uie%&e ciclo. E%

comparaci2% co% el arbi&ra(e de bus ce%&rali4ado$ es&e m/&odo de arbi&ra(e reuiere m*s l,%eas

de bus pero e)i&a los posibles cos&os del arbi&ro9 adem*s$ limi&a el %+mero de disposi&i)os$

ue %o puede ser mayor ue el %+mero de l,%eas de solici&ud.

O&ro &ipo de arbi&ra(e de bus desce%&rali4ado$ ue se mues&ra e% la fi!ura 30=.$ s2lo usa

&res l,%eas$ por m*s disposi&i)os ue es&/% prese%&es. La primera l,%ea de bus es u%a de O"

alambrado para solici&ar el bus. La se!u%da se llama D63C 7ocupado8 y es aser&ada por el amo

de bus )i!e%&e. La &ercera l,%ea sir)e para arbi&rar el bus$ y se co%ec&a e% serie a &odos los

disposi&i)os. La cabe4a de es&a cade%a se ma%&ie%e habili&ada co%ec&*%dola a la fue%&e de

alime%&aci2% de < )ol&s.

Figura 3-43. Arbi&ra(e de bus desce%&rali4ado.

3i %i%!+% disposi&i)o uiere el bus$ la l,%ea de arbi&ra(e aser&ada se propa!a por &odos

los disposi&i)os. 3i u% disposi&i)o uiere aduirir el bus$ primero )e si el bus es&* i%ac&i)o y la

se'al de arbi&ra(e ue es&* recibie%do$ IN$ es&* aser&ada. 3i IN es&* i%)alidada$ el disposi&i)o %o

podr* co%)er&irse e% co%&rolador del bus e i%)alidar* our. E% cambio$ si IN es&* habili&ada$ el

disposi&i)o deshabili&ar* our. Es&o har* ue su )eci%o cade%a aba(o )ea IN deshabili&ado y

deshabili&e su O6T. As,$ &odos los disposi&i)os cade%a aba(o )e% IN deshabili&ado y por &a%&o

deshabili&a% O6T. Al fi%al$ s2lo u% disposi&i)o &e%dr* IN habili&ado y O6T deshabili&ado. Es&e

disposi&i)o se co%)er&ir* e% el co%&rolador del bus$ habili&ar* D63C y O6T$ e i%iciar* su

&ra%sfere%cia.

3i lo pe%samos$ )eremos ue el disposi&i)o m*s a la i4uierda ue uiera el bus lo reci0

bir*. As,$ es&e esuema es similar al arbi&ra(e de cade%a circular ori!i%al$ e5cep&o ue %o &ie%e

arbi&ro$ por lo ue es m*s eco%2mico$ m*s r*pido$ y %o es )ul%erable a u% fallo del arbi&ro.

3.4.- *"eracione! de %u!

Bas&a ahora$ s2lo hemos )is&o ciclos de bus ordi%arios$ e% los ue u% co%&rolador 7!e%eral0

me%&e la CP68 lee desde u% escla)o 7!e%eralme%&e la memoria8 o escribe e% /l. De hecho$

e5is&e% )arios &ipos de ciclos de bus. A co%&i%uaci2% )eremos al!u%os de ellos.

Normalme%&e$ s2lo se &ra%sfiere u%a palabra a la )e4. 3i% embar!o$ cua%do se usa cach/$

->?

EL NIVEL DE LOGICA DIGITAL CAP. 3

es deseable &raer &oda u%a l,%ea de cach/ 7por e(emplo$ -> palabras co%secu&i)as de 31 bi&s8 a

la )e4. E% muchos casos es posible efec&uar &ra%sfere%cias de bloues co% mayor eficie%cia

ue &ra%sfere%cias i%di)iduales sucesi)as. Cua%do se i%icia u%a lec&ura de bloue$ el co%&ro0

lador del bus le dice al escla)o cu*%&as palabras debe &ra%sferir$ por e(emplo$ coloca%do la

cue%&a de palabras e% las l,%eas de da&os dura%&e TQ. E% lu!ar de de)ol)er s2lo u%a palabra$ el

escla)o produce u%a palabra dura%&e cada ciclo has&a a!o&ar la cue%&a. La fi!ura 30=- mues&ra

u%a )ersi2% modificada de la fi!ura 303H7a8$ pero ahora co% u%a se'al adicio%al$ DLOCR$ ue

se habili&a para i%dicar ue se solici&a u%a &ra%sfere%cia de bloue. E% es&e e(emplo$ la lec&ura

de u% bloue de = palabras &arda > ciclos e% lu!ar de -1.

Figura 3-4#. Tra%sfere%cia de u% bloue.

Tambi/% e5is&e% o&ras clases de ciclos de bus. Por e(emplo$ e% u% sis&ema

mul&iprocesador ue &ie%e dos o m*s CP6 e% el mismo bus$ a me%udo es %ecesario ase!urarse

de ue s2lo u%a CP6 a la )e4 u&ilice al!u%a es&ruc&ura de da&os cr,&ica e% la memoria. 6%a

forma com+% de lo!rar es&o es &e%er u%a )ariable e% la memoria ue sea . cua%do %i%!u%a

CP6 es&/ usa%do la es&ruc&ura de da&os y - cua%do es&/ e% uso. 3i u%a CP6 uiere accesar a la

es&ruc&ura de da&os$ primero deber* leer la )ariable y si es .$ po%erla e% -. El problema es ue$

co% u% poco de mala suer&e$ dos CP6 podr,a% leerla e% ciclos de bus co%secu&i)os. 3i los dos

)e% ue la )ariable es .$ los dos la po%dr*% e% - y cada u%a creer* ue es la +%ica CP6 ue

es&* usa%do la es&ruc&ura de da&os. Es&a serie de sucesos lle)a al caos.

Para e)i&ar es&* si&uaci2%$ los sis&emas mul&iprocesador a me%udo &ie%e% u% ciclo de bus

especial de leer0modificar0escribir ue permi&e a cualuier CP6 leer u%a palabra de la memo0

ria$ i%speccio%arla y modificarla$ y escribirla de )uel&a e% la memoria$ &odo si% desocupar el

bus. Es&e &ipo de ciclo e)i&a ue las CP6 compe&idoras pueda% usar el bus y as, i%&erfiera% la

->L

3EC. 3.= CBIP3 DE CP6 C D63E3

operaci2% de la primera CP6.

O&ro &ipo impor&a%&e de ciclo de bus sir)e para ma%e(ar i%&errupcio%es. Cua%do la CP6

orde%a a u% disposi&i)o de E:3 hacer al!o$ !e%eralme%&e espera u%a i%&errupci2% u%a )e4 ue

se co%cluye el &raba(o. La se'ali4aci2% de la i%&errupci2% reuiere el bus.

Pues&o ue )arios disposi&i)os podr,a% uerer causar u%a i%&errupci2% simul&*%eame%&e$

sur!e% los mismos &ipos de problemas de arbi&ra(e ue &e%,amos co% los ciclos de bus ordi%a0

rios. La soluci2% usual es asi!%ar prioridades a los disposi&i)os$ y usar u% arbi&ro ce%&rali4ado

para dar prioridad a los disposi&i)os para los ue el &iempo es m*s cr,&ico. E5is&e% chips

co%&roladores de i%&errupcio%es es&*%dar y se usa% ampliame%&e. La ID# PC y &odas sus

sucesoras usa% el chip I%&el ?1<LA$ ue se ilus&ra e% la fi!ura 30=1.

Figura 3-42. 6so del co%&rolador de i%&errupcio%es ?1<LA.

Bas&a ocho chips co%&roladores de E:3 se puede% co%ec&ar direc&ame%&e a las ocho

e%&radas I"E 7solici&ud de i%&errupci2%$ Interrupt Request) del ?1<LA. Cua%do cualuiera de

es&os disposi&i)os desea causar u%a i%&errupci2%$ habili&a su l,%ea de e%&rada. Cua%do se

habili&a u%a o m*s e%&radas$ el ?1<LA habili&a INT 7INTerrupci2%8$ ue alime%&a direc&ame%&e

la &ermi%al de i%&errupci2% de la CP6. Cua%do la CP6 es&* e% co%dicio%es de a&e%der la

i%&errupci2%$ de)uel)e u% pulso al ?1<LA por INTA 7acuse de i%&errupci2%$ INTerrupt

Acknowlede). E% ese mome%&o el ?1<LA deber* especificar cu*l e%&rada caus2 la

i%&errupci2% coloca%do el %+mero de esa e%&rada e% el bus de da&os. Es&a operaci2% reuiere

u% ciclo de bus especial. Lue!o$ el hardPare de la CP6 u&ili4a ese %+mero como ,%dice de u%a

&abla de apu%&adores$ llamados )ec&ores de i%&errupci2%$ para e%co%&rar la direcci2% del

procedimie%&o ue debe e(ecu&ar para a&e%der la i%&errupci2%.

El ?1<LA co%&ie%e )arios re!is&ros ue la CP6 puede leer y escribir emplea%do ciclos

de bus ordi%arios y las l,%eas "D$ G" 7escribir$ G"i&e8$ C3 y Ao. 6%a )e4 ue el sof&Pare ha

ma%e(ado la i%&errupci2% y es&* lis&o para recibir la si!uie%&e$ escribe u% c2di!o especial e%

u%o de los re!is&ros$ y es&o hace ue el ?1<LA deshabili&e INT$ a me%os ue &e%!a o&ra

i%&errupci2% pe%die%&e. Es&os re!is&ros &ambi/% puede% modificarse para colocar el ?1<LA e%

u%o de )arios modos$ e%mascarar u% co%(u%&o de i%&errupcio%es y habili&ar o&ras fu%cio%es.

Cua%do es&*% prese%&es m*s de ocho disposi&i)os de E:3$ los ?1<LA puede% co%ec&arse

e% cascada. E% el caso m*s e5&remo$ las ocho e%&radas puede% co%ec&arse a las salidas de

-H.

EL NIVEL DE LOGICA DIGITAL CAP. 3

ocho ?1<LA adicio%ales$ lo ue permi&e &e%er has&a >= disposi&i)os de S:3 e% u%a red de

i%&errupcio%es de dos e&apas. El ?1<LA &ie%e u%as cua%&as l,%eas dedicadas a ma%e(ar es&a

co%e5i2% e% cascada$ ue hemos omi&ido para simplificar.

3i bie% es&amos muy le(os de a!o&ar el &ema del dise'o de buses$ el ma&erial a%&erior

deber* bas&ar para e%&e%der los fu%dame%&os del fu%cio%amie%&o de los buses y la i%&eracci2%

e%&re ellos y las CP6. Pasemos ahora de lo !e%eral a lo espec,fico y e5ami%emos al!u%os

e(emplos de CP6 reales y sus buses.

3.( E4E5P6*S DE CHIPS DE CPU

E% es&a secci2% e5ami%aremos los chips Pe%&ium II$ 6l&ra3PA"C II y picoAa)a II co% cier&o

de&alle e% el %i)el de hardPare.

3.(.# E Pentium II

El Pe%&ium II es u% desce%die%&e direc&o de la CP6 ?.?? ue se us2 e% la ID# PC ori!i%al.

Au%ue el Pe%&ium II co% sus H.< millo%es de &ra%sis&ores es&* muy le(os del ?.?? co% 1L$...

&ra%sis&ores$ es &o&alme%&e compa&ible co% el ?.?? y puede e(ecu&ar pro!ramas bi%arios para

el ?.?? si% modificaci2% 7adem*s de pro!ramas para &odos los procesadores i%&ermedios8.

Desde el pu%&o de )is&a del sof&Pare$ el Pe%&ium II es u%a m*ui%a de 31 bi&s comple&a.

Tie%e la misma I3A e% el %i)el de usuario ue los chips ?.3?>$ ?.=?>$ Pe%&ium y Pe%&ium

Pro$ i%cluidos los mismos re!is&ros$ las mismas i%s&ruccio%es y u%a impleme%&aci2% comple&a

e% el chip del es&*%dar de pu%&o flo&a%&e IEEE H<=.

Desde el pu%&o de )is&a del hardPare$ el Pe%&ium II es al!o m*s porue puede

direccio%ar >= GD de memoria f,sica y puede &ra%sferir da&os de y a la memoria e% u%idades

de >= bi&s. Au%ue el pro!ramador %o puede obser)ar es&as &ra%sfere%cias de >= bi&s$ hace%

ue la m*ui%a sea m*s r*pida ue u%a m*ui%a de 31 bi&s pura.

I%&er%ame%&e$ e% el %i)el de microarui&ec&ura$ el Pe%&ium II es b*sicame%&e u% Pe%&ium

Pro al ue se a'adiero% las i%s&ruccio%es ##E. Las i%s&ruccio%es e% el %i)el de I3A se

ob&ie%e% de la memoria co% mucha a%&icipaci2% y se descompo%e% e% microoperacio%es &ipo

"I3C. Es&as microoperacio%es se almace%a% e% u% buffer$ y &a% pro%&o como u%a dispo%e

de los recursos %ecesarios para e(ecu&arse$ puede i%iciarse. 3e puede% i%iciar )arias mi0

crooperacio%es e% el mismo ciclo$ lo ue co%)ier&e al Pe%&ium II e% u%a m*ui%a super0

escalar.

El Pe%&ium II &ie%e u%a cach/ de dos %i)eles. Bay u% par de caches e% el chip$ -> RD

para i%s&ruccio%es y -> RD para da&os$ adem*s de u%a cach/ u%ificada de se!u%do %i)el de

<-1 RD. El &ama'o de la l,%ea de cach/ es de 31 by&es. La cach/ de se!u%do %i)el se e(ecu&a a

la mi&ad de la frecue%cia de relo( de la CP6. Bay relo(es de CP6 de 133 #B4 o m*s.

3e usa% dos buses e5&er%os primarios e% los sis&emas Pe%&ium 6$ ambos si%cr2%icos. El

bus de memoria sir)e para accesar la D"A# pri%cipal9 el bus PCI se usa para comu%icarse

co% los disposi&i)os de E:3. A )eces se co%ec&a u% bus de le!ado 7o sea$ a%&i!uo8 al bus de PCI

para poder co%ec&ar a /l disposi&i)os perif/ricos de &ec%olo!,a a%&erior.

-H-

3EC. 3.< EAE#PLO3 DE CBIP3 DE CP6

6% sis&ema Pe%&ium II puede &e%er u%o o dos CP6 ue compar&e% u%a memoria com+%.

E% u% sis&ema de dos CP6$ e5is&e el peli!ro de ue si u%a palabra se lee y se coloca e% u%a

cach/$ y se modifica ah, si% ue se escriba de )uel&a e% la memoria$ si la o&ra CP6 &ra&a de

leer la palabra ob&e%dr* u% )alor i%correc&o. 3e i%cluye apoyo especial 7espio%a(e8 para e)i&ar

es&e problema.

6%a difere%cia impor&a%&e e%&re el Pe%&ium II y &odos sus predecesores es su

empaue&ado. Desde la ?.?? has&a el Pe%&ium Pro$ &odas las CP6 de I%&el era% chips

%ormales$ co% &ermi%ales e% los lados o la base ue se pod,a% co%ec&ar e% 42calos. E%

co%&ras&e$ el Pe%&ium II es&* pro)is&o de lo ue I%&el llama u% 3EC 7car&ucho de u%a sola

aris&a$ Sinle !de "artride). Como puede )erse e% la fi!ura 30=3$ u% 3EC es u%

e%capsulado de pl*s&ico rela&i)ame%&e !ra%de ue co%&ie%e la CP6$ la cach/ %i)el 1 y u%

co%ec&or de aris&a para e5por&ar las se'ales. El 3EC de Pe%&ium II &ie%e 1=1 co%ec&ores.

Figura 30=3. El paue&e 3EC del Pe%&ium II.

Au%ue si% duda I%&el &u)o sus mo&i)os para cambiar a es&e modelo de e%capsulado$

produ(o u% problema e% u%a dime%si2% ue (am*s pre)io. Al parecer$ muchos clie%&es &ie%e%

la cos&umbre de abrir sus compu&adoras para buscar el chip de CP6. E% los primeros Pe%&ium

II ue saliero% a la )e%&a$ los clie%&es %o pod,a% e%co%&rar la CP6 y se ue(aro% a !ra%des

)oces 7KQ#i compu&adora %o &ie%e CP6TK8. I%&el resol)i2 es&e problema pe!a%do u%a ima!e%

del chip de CP6 7e% realidad$ u% holo!rama8 e% la par&e dela%&era de &odos los 3EC ue se

dis&ribuyero% pos&eriorme%&e.

El co%&rol de e%er!,a es u% aspec&o impor&a%&e del Pe%&ium II. La ca%&idad de calor ue

se despre%de depe%de de la frecue%cia de relo($ pero es del orde% de 3.0<. Pa&&s. Es&a

ca%&idad es e%orme cua%do se &ra&a de u% chip de compu&adora. Para &e%er u%a idea de

c2mo se sie%&e% <. Pa&&s$ acerue su ma%o a u%a bombilla de <. Pa&&s 7si% &ocarla8 ue ha

es&ado e%ce%dida dura%&e u% ra&o. Por co%si!uie%&e$ el 3EC es&* co%fi!urado para acep&ar u%

-H1

EL NIVEL DE LOGICA DIGITAL CAP. 3

radiador de calor$ ue es %ecesario para disipar el calor !e%erado. Es&o implica ue cua%do

u% Pe%&ium II haya de(ado de ser +&il como CP6 siempre podr* usarse como es&ufa para

acampar.

3e!+% las leyes de la f,sica$ cualuier cosa ue emi&a !ra% ca%&idad de calor deber*

co%sumir mucha e%er!,a. E% u%a compu&adora por&*&il e% la ue la car!a de la ba&er,a es

limi&ada %o es deseable co%sumir mucha e%er!,a. Para subsa%ar es&e problema$ I%&el ha hecho

posible po%er a la CP6 a dormir cua%do es&* ociosa y e% u%a %arcolepsia profu%da cua%do

parece ue )a a es&ar ociosa dura%&e mucho &iempo. Cua%do la CP6 es&* e% el sue'o

profu%do$ los )alores de la cach/ y los re!is&ros se co%ser)a%$ pero el relo( y &odas las

u%idades i%&er%as se desac&i)a%. No se sabe si u% Pe%&ium II sue'a cua%do es&* profu%dame%&e

dormido.

6a conexin gica de terminae! de Pentium II

Los 1=1 co%ec&ores de aris&a del 3EC se usa% para -H. se'ales$ 1H co%e5io%es de po&e%cia 7a

difere%&es )ol&a(es8$ 3< &ierras y -. repues&os para uso fu&uro. Al!u%as de las se'ales l2!icas

emplea% dos o m*s &ermi%ales 7como la direcci2% de memoria solici&ada8$ as, ue s2lo hay <3

se'ales dis&i%&as. E% la fi!ura 30== se mues&ra la co%fi!uraci2% de co%e5i2% l2!ica de &ermi0

%ales #pinout) u% &a%&o simplificada. E% el lado i4uierdo de la fi!ura es&*% los seis !rupos

pri%cipales de se'ales del bus de memoria9 e% el lado derecho es&*% se'ales de di)ersos &ipos.

Los %ombres ue es&*% &o&alme%&e e% may+sculas so% los %ombres reales dados por I%&el a las

se'ales. Los dem*s so% %ombres colec&i)os de )arias se'ales relacio%adas.

I%&el emplea u%a co%)e%ci2% para asi!%ar %ombres ue es impor&a%&e e%&e%der. Dado

ue &odos los chips ac&uales se dise'a% co% compu&adoras$ es %ecesario poder represe%&ar los

%ombres de las se'ales como &e5&o A3CII. Es demasiado dif,cil usar &es&as para i%dicar las

se'ales ue se habili&a% e% %i)el ba(o$ por lo ue e% )e4$ de ello I%&el coloca el s,mbolo U

despu/s del %ombre. As,$ DP"I se e5presa como DP"IU. Como puede )erse e% la fi!ura$ casi

&odas las se'ales de Pe%&ium II se habili&a% e% %i)el ba(o.

E5ami%emos las se'ales$ come%4a%do co% las de bus. El primer !rupo de se'ales sir)e

para solici&ar el bus 7es decir$ efec&uar arbi&ra(e8. DP"IU permi&e a u% disposi&i)o hacer u%a

solici&ud de al&a prioridad$ ue &ie%e precede%cia respec&o a u%a %ormal. LOCRU permi&e a

u%a CP6 blouear el bus para e)i&ar ue la o&ra lo use a%&es de ue la primera &ermi%e.

6%a )e4 ue u%a CP6 u o&ro co%&rolador de bus se ha apropiado del bus$ puede prese%0

&ar u%a solici&ud u&ili4a%do el si!uie%&e !rupo de se'ales. Las direccio%es so% de 3> bi&s$

pero los &res bi&s de orde% ba(o siempre debe% ser O y por &a%&o %o se les asi!%a% l,%eas. Por

&a%&o$ AU s2lo &ie%e 33 l,%eas. Todas las &ra%sfere%cias so% de ? by&es$ ali%eadas a u%a

fro%&era de ? by&es. Co% 3> bi&s de direcci2%$ el m*5imo de memoria direccio%able es 1

3>

$ ue

es >= GD.

Cua%do u%a direcci2% se coloca e% el bus$ la se'al AD3U se habili&a para i%dicar al

ob(e&i)o 7o sea$ la memoria8 ue las l,%eas de direcci2% so% )*lidas. El &ipo de ciclo de bus

7por e(emplo$ leer u%a palabra o escribir u% bloue8 se coloca e% las l,%eas "EMU. Dos de las

se'ales de paridad pro&e!e% a AU y u%a pro&e!e a AD3U y "EMU. Las ci%co l,%eas de error so%

u&ili4adas por el escla)o para i%formar errores de paridad y por &odos los dem*s disposi&i)os

-H3

3EC. 3.< EAE#PLO3 DE CBIP3 DE CP6

para i%formar de o&ros errores.

Figura 3-44. Co%e5i2% l2!ica de &ermi%ales del Pe%&ium II. Los %ombres e%

may+sculas so% los %ombres oficiales de I%&el para se'ales i%di)iduales. Los %ombres

e% may+sculas y mi%+sculas so% !rupos de se'ales relacio%adas o descripcio%es de

se'ales.

El !rupo de Espio%a(e se usa e% sis&emas mul&iprocesador para ue u%a CP6 pueda

a)eri!uar si u%a palabra ue %ecesi&a es&* e% la cach/ de la o&ra CP6. Describiremos la forma

de espiar del Pe%&ium II e% el cap,&ulo ?.

El !rupo "espues&a co%&ie%e se'ales ue el escla)o u&ili4a para e%)iar i%formes al amo

7co%&rolador8. "3U co%&ie%e el c2di!o de si&uaci2%. T"DCU i%dica ue el escla)o 7el ob(e&i)o8

es&* lis&o para acep&ar da&os del amo. Es&as se'ales &ambi/% &ie%e% )erificaci2% de paridad.

El +l&imo !rupo del bus sir)e para &ra%sferir realme%&e los da&os. DU sir)e para colocar

? by&es de da&os e% el bus. 6%a )e4 ue es&*% ah,$ s/ aser&a D"DCU para a%u%ciar su prese%cia.

D3DCU sir)e para decirle al mu%do ue el bus es&* ocupado.

"E3ETU sir)e para res&ablecer la CP6 e% caso de ocurrir u%a calamidad. El Pe%&ium II

puede co%fi!urarse de modo ue use las i%&errupcio%es i!ual ue el ?.?? 7para fi%es de com0

pa&ibilidad co% lo e5is&e%&e8 pero &ambi/% puede usar u% %ue)o sis&ema de i%&errupcio%es co%

u% disposi&i)o llamado ,PIC 7controador de interru"cione! "rograma%e a'an/ado$

Advanced $roramma%le Interrupt "ontroller).

-H=

EL NIVEL DE LOGICA DIGITAL CAP. 3

El Pe%&ium II puede operar a )arios )ol&a(es$ pero %ecesi&a saber cu*l. Las se'ales VID

sir)e% para seleccio%ar au&om*&icame%&e el )ol&a(e de la fue%&e de po&e%cia. Las se'ales de

Compa&ibilidad sir)e% para e%!a'ar a disposi&i)os a%&i!uos e% el bus ue pie%sa% ue es&*%

habla%do co% u% ?.??. El !rupo de Dia!%2s&ico co%&ie%e se'ales para probar y depurar sis&e0

mas .se!+% la %orma de prueba IEEE --=L.- ATAG. El !rupo de I%iciali4aci2% se ocupa de

arra%car el sis&ema #%ootin). El !rupo de Co%&rol de e%er!,a permi&e po%er a dormir a la

CP6 %ormal y profu%dame%&e. Por +l&imo$ el !rupo #iscel*%eo es u%a re)ol&ura de se'ales

ue i%cluye u%a ue la CP6 habili&a si su &empera&ura i%&er%a lle!a a -3.VC 71>>VF8. 3i u%a

CP6 alca%4a al!u%a )e4 es&a &empera&ura$ probableme%&e es&* so'a%do e% re&irarse y co%)er0

&irse e% u%a es&ufa para acampar.

Fia! de "roce!amiento en e %u! de memoria de Pentium II

Las CP6 moder%as como el Pe%&ium II so% mucho m*s r*pidas ue las memorias D"A#

moder%as. Para e)i&ar ue la CP6 muera de i%a%ici2% por fal&a de da&os$ es i%dispe%sable

ob&e%er u% re%dimie%&o m*5imo de la memoria. Por es&a ra42%$ el bus de memoria del

Pe%&ium II usa las filas de procesamie%&o$ y se puede% es&ar e(ecu&a%do has&a ocho

&ra%saccio%es de bus al mismo &iempo. Ca )imos el co%cep&o de filas de procesamie%&o e% el

cap,&ulo 1 e% el co%&e5&o de u%a CP6 co% filas de procesamie%&o 7)ea la fi!ura 10=8$ pero las

memorias &ambi/% puede% usarlos.

Para ello$ las solici&udes de memoria del Pe%&ium II$ llamadas &ra%saccio%es$ &ie%e% seis

e&apas;

-. La fase de arbi&ra(e de bus.

1. La fase de solici&ud.

3. La fase de i%formar errores.

=. La fase de espio%a(e.

<. La fase de respues&a

>. La fase de da&os.

No &odas las fases se %ecesi&a% e% &odas las &ra%saccio%es. La fase de arbi&ra(e de bus de&ermi0

%a cu*l de los posibles co%soladores de bus &oma su &ur%o. La fase de solici&ud permi&e

colocar la direcci2% e% el bus y hacer la solici&ud. La fase de i%formar errores permi&e al

escla)o a%u%ciar ue la direcci2% &u)o u% error de paridad o ue al!o m*s a%da mal. La fase

de espio%a(e permi&e a u%a CP6 espiar a la o&ra$ al!o ue s2lo se %ecesi&a e% u% sis&ema

mul&iprocesador. La fase de respues&a es auella do%de el co%&rolador se e%&era de si es&* a

pu%&o de ob&e%er los da&os ue uiere o %o. Por +l&imo$ la fase de da&os permi&e de)ol)er los

da&os.

El secre&o del bus de memoria co% co%duc&os del Pe%&ium II es ue cada fase u&ili4a

difere%&es se'ales de bus$ de modo ue cada u%a es &o&alme%&e i%depe%die%&e de las dem*s.

Los seis !rupos de se'ales reueridas so% los ue se mues&ra% e% la fi!ura 30== a la i4uierda.

-H<

3EC. 3.< EAE#PLO3 DE CBIP3 DE CP6

Por e(emplo$ u%a CP6 puede &ra&ar de ob&e%er el bus u&ili4a%do las se'ales de arbi&ra(e. 6%a

)e4 ue aduiri2 el derecho a ser el si!uie%&e$ libera es&as l,%eas del bus y comie%4a a usar las

l,%eas del !rupo de 3olici&ud. #ie%&ras &a%&o$ la o&ra CP6 o al!+% disposi&i)o de E:3 puede

i%!resar e% la fase de arbi&ra(e del bus$ y as, sucesi)ame%&e. La fi!ura 30=< mues&ra c2mo

)arias &ra%saccio%es de bus puede% es&ar pe%die%&es al mismo &iempo.

Figura 3-4(. Colocaci2% de solici&udes e% filas de procesamie%&o e% el bus de

memoria del Pe%&ium II.

E% la fi!ura 30=< %o se mues&ra la fase de arbi&ra(e de bus porue %o siempre se

%ecesi&a. Por e(emplo$ si el due'o ac&ual del bus 7por lo re!ular la CP68 uiere e(ecu&ar o&ra

&ra%sacci2%$ %o &ie%e ue readuirir el bus9 s2lo &ie%e ue pedir el bus o&ra )e4 despu/s de

ceder la propiedad del bus a o&ro disposi&i)o solici&a%&e. Las &ra%saccio%es - y 1 so% se%cillas;

ci%co fases e% ci%co ciclos de bus. La &ra%sacci2% 3 i%&roduce u%a fase de da&os m*s lar!a$ por

e(emplo$ porue es u%a &ra%sfere%cia de bloue o porue la memoria direccio%ada i%ser&2 u%

es&ado de espera. Por co%si!uie%&e$ la &ra%sacci2% = %o puede i%iciar su fase de da&os cua%do

uisiera hacerlo. La &ra%sacci2% = obser)a ue la se'al DD3CU &oda),a es&* habili&ada y sim0

pleme%&e espera ue la deshabili&e%. E% la &ra%sacci2% < )emos ue la fase de respues&a

&ambi/% puede &ardar )arios ciclos de bus$ lo ue re&arda la &ra%sacci2% >. Por +l&imo$ e% la

&ra%sacci2% H obser)amos ue u%a )e4 ue se ha i%&roducido u%a burbu(a e% la fila de proce0

samie%&o perma%ece ah, si se si!ue% i%icia%do co%secu&i)ame%&e %ue)as &ra%saccio%es. 3i%

embar!o$ e% la pr*c&ica es poco probable ue la CP6 i%&e%&e i%iciar u%a %ue)a &ra%sacci2% e%

cada ciclo de bus$ as, ue las burbu(as %o dura% &a%&o.

-H>

EL NIVEL DE LOGICA DIGITAL CAP. 3

3.(.2 E UtraSP,+C II

Como se!u%do e(emplo de chip de CP6$ e5ami%aremos la familia 6l&ra3PA"C de 3u%. Es&a

familia es la l,%ea de las CP6 3PA"C de >= bi&s de 3u%. La familia 6l&ra3PA"C se a(us&a

cabalme%&e a la arui&ec&ura 3PA"C )ersi2% L$ ue &ambi/% es para las CP6 de >= bi&s$ y se

usa e% es&acio%es de &raba(o y ser)idores 3u%$ as, como e% )arias aplicacio%es m*s. Es&a

familia i%cluye el 6l&ra3PA"C I$ el 6l&ra3PA"C II y el 6l&ra3PA"C III$ cuya arui&ec&ura es

muy similar9 difiere% pri%cipalme%&e e% la fecha de i%&roducci2% y la rapide4 del relo(. Para

ue la e5plicaci2% ue si!ue sea m*s co%cre&a$ %os referiremos al 6l&ra3PA"C II$ pero casi

&odo aplica &ambi/% a los dem*s 6l&ra3PA"C.

El 6l&ra3PA"C II es u%a m*ui%a "I3C &radicio%al y es ple%ame%&e compa&ible e%

lo bi%ario co% la arui&ec&ura 3PA"C V? de 31 bi&s. Puede e(ecu&ar pro!ramas bi%arios para

3PA"C V? de 31 bi&s si% modificaci2% porue la arui&ec&ura 3PA"C VL es compa&ible co%

la arui&ec&ura 3PA"C V?. El +%ico aspec&o e% ue el 6l&ra3PA"C II se des),a de la

arui&ec&ura 3PA"C VL es e% la adici2% del co%(u%&o de i%s&ruccio%es para mul&imedia VI3$

ue se dise'2 para aplicacio%es !r*ficas$ decodificaci2% #PEG e% &iempo real$ e&c/&era.

El 6l&ra3PA"C II se dise'2 para co%s&ruir mul&iprocesadores de cua&ro %odos co%

memoria compar&ida si% la adici2% de circui&os e5&er%os$ y mul&iprocesadores m*s !ra%des

co% u% m,%imo de circui&os e5&er%os. E% o&ras palabras$ !ra% par&e del Kadhesi)oK ue se

%ecesi&a para co%s&ruir u% mul&iprocesador ya es&* i%cluido e% cada chip 6l&ra3PA"C II.

A difere%cia del 3EC del Pe%&ium II$ la CP6 6l&ra3PA"C II es u% chip au&2%omo$ au%0

ue moderadame%&e !ra%de$ co% <.= millo%es de &ra%sis&ores. Tie%e H?H &ermi%ales e% su

base$ dispues&as como se mues&ra e% la fi!ura 30=>. Es&a !ra% ca%&idad de &ermi%ales se e5pli0

ca e% par&e por el uso de >= bi&s para las direccio%es y -1? bi&s para los da&os$ pero &ambi/% se

debe e% par&e a la forma como fu%cio%a% las caches. Adem*s$ muchas de las &ermi%ales %o

se usa% o so% redu%da%&es. 3e esco!i2 el %+mero H?H para poder usar u% e%capsulado es&*%dar

e% la i%dus&ria. La i%dus&ria probableme%&e co%sidera ue es de bue%a suer&e &e%er u% %+mero

primo de &ermi%ales.

El 6lfra3PA"C II &ie%e dos caches i%&er%as; -> RD para i%s&ruccio%es y -> RD para

da&os. Al i!ual ue el Pe%&ium II$ &ambi/% usa u%a cach/ de %i)el 1 e5&er%o al chip$ pero a

difere%cia del Pe%&ium II esa cach/ %o )ie%e empaue&ada co% el 6l&ra3PA"C II e% u% car&u0

cho pa&e%&ado. Los dise'adores de sis&emas es&*% e% liber&ad de esco!er cualuier chip de

cach/ comercial ue desee% para la cach/ de %i)el 1.

La decisi2% de i%&e!rar la cach/ %i)el 1 e% el Pe%&ium II y separarlo e% el 6l&ra3PA"C

II se debe e% par&e a las opcio%es &/c%icas y e% par&e a los difere%&es modelos comerciales ue

I%&el y 3u% usa%. E% el aspec&o &/c%ico$ u%a cach/ e5&er%a es m*s fle5ible 7las caches del

6l&ra3PA"C II puede% ir de <-1 RD a -> #D9 las del Pe%&ium II es&*% fi(as e% <-1 RD8$ pero

podr,a ser m*s le%&o a causa de su mayor dis&a%cia de la CP6. Adem*s$ se reuiere% m*s

se'ales )isibles para direccio%ar la cach/ 7los 1=1 co%ec&ores del car&ucho 3EC del Pe%&ium II

%o i%cluye% se'ales para la cach/$ ya ue la i%&eracci2% CP60cach/ es i%&er%a al car&ucho8$

pero las H?H &ermi%ales del 6l&ra3PA"C II s, i%cluye% co%&rol de cach/.

-HH

3EC. 3.< EAE#PLO3 DE CBIP3 DE CP6

Figura 3-4-. El chip de CP6 6l&ra3PA"C II.

E% el aspec&o comercial$ I%&el es u% fabrica%&e de semico%duc&ores y puede dise'ar y

fabricar su propio chip de cach/ de %i)el 1 y co%ec&arlo a la CP6 co% u%a i%&erfa4 pa&e%&ada

de al&o desempe'o. 3u%$ e% cambio$ es u% fabrica%&e de compu&adoras$ %o de chips. 3, dise'a

al!u%os de sus chips 7como los 6l&ra3PA"C8$ pero subco%&ra&a fabrica%&es de

semico%duc&ores como Te5as I%s&rume%&s y Fu(i&su. Cua%do puede$ 3u% prefiere usar chips

comerciales ue ha% sido depurados por el mercado &a% compe&i&i)o. Las 3"A# ue se usa%

e% las caches de %i)el 1 se puede% co%se!uir de muchos pro)eedores de chips$ por lo ue 3u%

%o si%&i2 u%a %ecesidad especial de dise'ar su propia 3"A#. Es&a decisi2% implica hacer la

cach/ de %i)el 1 i%depe%die%&e del chip de la CP6.

Casi &odas las es&acio%es de &raba(o 3u% &ie%e% u% bus asi%cr2%ico de 1< #B4 llamado

SBu!. Los disposi&i)os de E:3 se puede% co%ec&ar al 3Dus$ pero /s&e es demasiado le%&o para

la memoria$ as, ue 3u% cre2 u% meca%ismo difere%&e para ue u%a o m*s CP6 6l&ra3PA"C

se comu%iue% co% u%a o m*s memorias; la UP, 7ar8uitectura de utra"uerto$ <ra

$on Architecture). La 6PA se puede impleme%&ar como u% bus$ u% co%mu&ador$ o u%a

combi%aci2% de las dos cosas. Difere%&es modelos de es&acio%es de &raba(o y ser)idores usa%

difere%&es impleme%&acio%es de la 6PA. A la CP6 %o le impor&a u/ impleme%&aci2% de la

6PA se usa porue la i%&erfa4 co% la 6PA es&* perfec&ame%&e defi%ida$ y es es&a i%&erfa4 la ue

el chip de la CP6 debe reco%ocer 7y reco%oce8.

E% la fi!ura 30=H )emos el cora42% de u% sis&ema 6l&ra3PA"C II$ ue mues&ra el chip

de CP6$ la i%&erfa4 6PA y la cach/ de %i)el 1 7dos 3"A# comerciales8. La fi!ura &ambi/%

i%cluye u% chip UDB II 7UtraSP,+C Data Bu99er II:$ cuya fu%ci2% se e5plicar* m*s ade0

la%&e. Cua%do la CP6 %ecesi&a u%a palabra de la memoria$ primero la busca e% u%a de sus

caches i%&er%as 7%i)el -8. 3i la e%cue%&ra$ co%&i%+a su e(ecuci2% a &oda )elocidad9 si %o e%0

cue%&ra la palabra e% la cach/ de %i)el -$ prueba e% la de %i)el 1.

f

Au%ue a%ali4aremos el uso de caches co% de&alle e% el cap,&ulo =$ co%)ie%e hablar u%

poco al respec&o au,. Toda la memoria pri%cipal es&* di)idida e% l,%eas de cach/ 7bloues8 de

-H?

EL NIVEL DE LOGICA DIGITAL CAP. 3

Figura 3-4;. Pri%cipales carac&er,s&icas del cora42% de u% sis&ema 6l&ra3PA"C II.

>= by&es. Las 1<> l,%eas de i%s&ruccio%es ue m*s se usa% y las 1<> l,%eas de da&os ue m*s

se usa% es&*% e% la cach/ %i)el -. Las l,%eas de cach/ ue se usa% mucho pero ue %o cabe% e%

la cach/ de %i)el - se !uarda% e% la cach/ de %i)el 1. Ss&e co%&ie%e l,%eas de da&os y de

i%s&ruccio%es me4cladas alea&oriame%&e$ y se almace%a% e% el rec&*%!ulo ro&ulado KDa&os de

cach/ de %i)el 1K. El sis&ema &ie%e ue saber cu*les l,%eas es&*% e% la cach/ de %i)el 1. Es&a

i%formaci2% se !uarda e% u%a se!u%da 3"A#$ ro&ulada KE&iue&as de cach/ de %i)el 1K.

Cua%do %o se e%cue%&ra u%a l,%ea e% la cach/ de %i)el -$ la CP6 e%),a su ide%&ificador

7direcci2% de e&iue&a8 a la cach/ de %i)el 1. La respues&a 7da&os de e&iue&a8 proporcio%a la

i%formaci2% ue permi&e a la CP6 saber si la l,%ea es&* o %o e% la cach/ de %i)el 1 y$ si es&*$

e% u/ es&ado es&*. 3i la l,%ea es&* !uardada ah,$ la CP6 la &rae. Las &ra%sfere%cias de da&os

&ie%e% u%a a%chura de -> by&es$ por lo ue se %ecesi&a% cua&ro ciclos para &raer &oda u%a l,%ea

a la cach/ de %i)el -.

3i la l,%ea de cach/ %o es&* e% la cach/ de %i)el 1$ deber* &raerse de la memoria

pri%cipal ),a la i%&erfa4 6PA. La 6PA del 6l&ra3PA"C II se impleme%&a co% u% co%&rolador

ce%&rali4ado. Las se'ales de direcci2% y co%&rol de la CP6 7de &odas las CP6 si hay m*s de

u%a8 lle!a% ah,. Para accesar la memoria$ la CP6 debe usar primero las l,%eas de arbi&ra(e de

bus para ob&e%er permiso de co%&i%uar. 6%a )e4 co%cedido el permiso$ la CP6 e%),a la

direcci2% de memoria$ especifica el &ipo de solici&ud$ y habili&a la l,%ea de direcci2% )*lida.

7Es&as l,%eas so% bidireccio%ales porue o&ras CP6 de u% mul&iprocesador 6l&ra3PA"C II

%ecesi&a% &e%er acceso a las caches remo&as para ma%&e%er la cohere%cia de &odas las caches.8

La direcci2% y el &ipo de ciclo de bus se coloca% e% las l,%eas de Direcci2% e% dos ciclos; el

re%!l2% e% el primer ciclo y la colum%a e% el se!u%do$ como )imos e% la fi!ura 303-.

-HL

3EC. 3.< EAE#PLO3 DE CBIP3 DE CP6

#ie%&ras espera los resul&ados$ la CP6 bie% podr,a co%&i%uar co% o&ros &raba(os. Por

e(emplo$ u%a cach/ %o i%hibe la e(ecuci2% de u%a o m*s i%s&ruccio%es ue ya se ob&u)iero%

mie%&ras se preob&ie%e u%a i%s&rucci2% $ las cuales podr,a% hacer refere%cia a da&os ue %o

es&*% e% %i%!u%a cach/. As,$ podr,a haber )arias &ra%saccio%es co% la 6PA pe%die%&es e% u%

mome%&o dado. La 6PA puede ma%e(ar dos flu(os de &ra%sacci2% i%depe%die%&es 7por lo

re!ular lec&uras y escri&uras8$ cada u%o co% m+l&iples &ra%saccio%es pe%die%&es. Correspo%de

al co%&rolador ce%&rali4ado se!uir la pis&a a &odo es&o y efec&uar las solici&udes de memoria

propiame%&e dichas e% el orde% m*s eficie%&e.

Cua%do por fi% lle!a% los da&os de la memoria$ podr,a% )e%ir e% !rupos de ? by&es$ y

co% u% c2di!o de correcci2% de errores de -> bi&s para mayor co%fiabilidad. 6%a &ra%sacci2%

podr,a pedir &odo u% bloue de cach/$ u%a palabra cu*druple 7? by&es8 o i%cluso me%os by&es.

Todos los da&os ue lle!a% se coloca% e% buffers e% el 6DD. El prop2si&o del 6DD es

desacoplar au% m*s la CP6 del sis&ema de memoria$ de modo ue pueda% operar

asi%cr2%icame%&e. Por e(emplo$ si la CP6 &ie%e ue escribir u%a palabra o l,%ea de cach/ e% la

memoria$ e% lu!ar de esperar para accesarla 6PA puede escribir los da&os e% el 6DD de

i%media&o y de(ar ue el 6DD se e%car!ue de hacerlos lle!ar a la memoria pos&eriorme%&e. El

6DD &ambi/% !e%era y )erifica el c2di!o de correcci2% de errores. Cabe se'alar ue la

descripci2% del 6l&ra3PA"C II ue acabamos de prese%&ar$ al i!ual ue la del Pe%&ium II ue

la precedi2$ se ha simplificado co%siderableme%&e$ au%ue se describi2 la ese%cia del

fu%cio%amie%&o.

3.(.3 E "ico4a'a II

Ta%&o el Pe%&ium II como el 6l&ra3PA"C II so% e(emplos de CP6 de al&o desempe'o dise'a0

das para co%s&ruir PC y es&acio%es de &raba(o e5&remadame%&e r*pidas. Cua%do la !e%&e pie%sa

e% las compu&adoras$ /s&e es el &ipo de sis&emas e% el ue &ie%de% a co%ce%&rarse. 3i% embar!o$

e5is&e &odo u% mu%do de compu&adoras dis&i%&o ue e% realidad es mucho m*s !ra%de;

los sis&emas i%corporados. E% es&a secci2% daremos u% )is&a4o a ese mu%do.

Es probable ue %o e5a!eremos mucho si decimos ue cualuier disposi&i)o el/c&rico

ue cues&e m*s de -.. d2lares probableme%&e i%cluye u%a compu&adora. 3i% duda los &ele)i0

sores$ &el/fo%os celulares$ or!a%i4adores perso%ales elec&r2%icos$ hor%os de microo%das$ c*0

maras de )ideo$ )ideo!rabadoras$ impresoras l*ser$ alarmas co%&ra robo$ adi&ame%&os para la

sordera$ (ue!os elec&r2%icos y o&ros disposi&i)os es&*% co%&rolados por compu&adoras. Las

compu&adoras co%&e%idas e% es&os ar&,culos suele% es&ar op&imadas para &e%er u% precio ba(o

m*s ue para &e%er u% bue% desempe'o$ lo ue da lu!ar a co%cesio%es difere%&es de las ue se

hace% e% las CP6 de al&a &ec%olo!,a ue hemos es&ado es&udia%do has&a ahora.

Tradicio%alme%&e$ los procesadores i%corporados se ha% pro!ramado e% le%!ua(e

e%samblador$ pero a medida ue los apara&os se )uel)e% m*s complicados y las co%secue%cias

de los errores de sof&Pare se hace% m*s se)eros$ o&ros e%foues se ha% )uel&o compe&i&i)os.

E% par&icular$ el uso de Aa)a como le%!ua(e de pro!ramaci2% para sis&emas i%corporados es

a&rac&i)o e% )ir&ud de su rela&i)a facilidad de pro!ramaci2%$ el &ama'o reducido del c2di!o y

su i%depe%de%cia de la pla&aforma. La pri%cipal des)e%&a(a de usar Aa)a e% aplicacio%es

i%corporadas es la %ecesidad de &e%er u% i%&/rpre&e !ra%de e% sof&Pare ue e(ecu&e el c2di!o

AV# producido por el compilador de Aa)a$ y la le%&i&ud del proceso de i%&erpre&aci2%.

-?.

EL NIVEL DE LOGICA DIGITAL CAP. 3

3u% y o&ras compa',as ha% a&acado es&e problema dise'a%do y co%s&ruye%do chips de

CP6 ue &ie%e% AV# como su co%(u%&o de i%s&ruccio%es %a&i)o. Es&e e%foue combi%a las

)e%&a(as de usar Aa)a como le%!ua(e de pro!ramaci2%$ la &ra%spor&abilidad y el &ama'o com0

pac&o del c2di!o AV# bi%ario producido por el compilador de Aa)a$ y la rapide4 de e(ecuci2%

por hardPare especiali4ado. E% es&a secci2% e5ami%aremos u%a arui&ec&ura de CP6 moder%a

basada e% Aa)a dise'ada espec,ficame%&e para el mercado de los sis&emas i%corporados.

La CP6 es la picoAa)a II de 3u% e% ue se basa el chip microAa)a H.- de 3u%$ au%ue

3u% &ambi/% ha o&or!ado lice%cias para el dise'o a o&ras compa',as. Es u%a CP6 de u% solo

chip co% dos i%&erfaces de bus$ u%a para el bus de memoria ue &ie%e u%a a%chura de >= bi&s

y u%a para el bus PCI ue &ie%e u%a a%chura de 31 bi&s$ como se mues&ra e% la fi!ura 30=?. Al

i!ual ue el Pe%&ium II y el 6l&ra3PA"C II$ el picoAa)a II &ie%e u%a cach/ %i)el - 7opcio%al8

di)idida e% el chip$ co% has&a -> RD para i%s&ruccio%es y has&a -> RD para da&os. 3i% embar 0

!o$ a difere%cia de esas dos CP6$ el picoAa)a II %o &ie%e u%a cach/ %i)el 1 porue u%o de los

par*me&ros de dise'o fu%dame%&ales de los sis&emas i%corporados es el ba(o cos&o. A co%&i0

%uaci2% describiremos la impleme%&aci2% del picoAa)a II hecha por 3u%; el microAa)a H.-.

El chip es peue'o se!+% los cri&erios ac&uales; s2lo dos millo%es de &ra%sis&ores para el

%+cleo m*s o&ro mill2% y medio para las dos caches de -> RD (u%&as.

Figura 3-40. 6% sis&ema microAa)a H.-.

Tres carac&er,s&icas de la fi!ura 30=? sal&a% a la )is&a. Primera$ el microAa)a H.- u&ili4a

el bus PCI 7a 33 #B4 o bie% >> #B48. Es&e bus fue creado por I%&el para usarse e% los

sis&emas Pe%&ium del e5&remo superior$ pero es i%depe%die%&e del procesador. La )e%&a(a de

usar el bus PCI es ue es u% es&*%dar$ y as, se e)i&a &e%er ue dise'ar u% bus %ue)o. Adem*s$

ya e5is&e% muchas &ar(e&as hechas para i%ser&arse e% /l. Au%ue la e5is&e%cia de &ar(e&as para

PCI %o es !ra% )e%&a(a cua%do se es&*% co%s&ruye%do &el/fo%os celulares$ e% el caso de

&ele)isores de Geb y o&ros apara&os m*s !ra%des s, es u% pu%&o e% fa)or.

3e!u%da$ u% sis&ema microAa)a H.- %ormalme%&e i%cluye u%a P"O# flash. La cues&i2%

au, es ue e% el caso de u% apara&o u%a bue%a par&e del pro!rama$ si %o es ue &odo$ &ie%e

ue es&ar i%cluido ya e% el disposi&i)o. 6%a P"O# flash es u% bue% lu!ar para almace%ar el

pro!rama$ as, ue es +&il &e%er u%a i%&erfa4 para u%a de ellas. O&ro chip ue se puede a'adir al

sis&ema 7%o se mues&ra8 co%de%e las i%&erfaces de E:3 serial y paralela ue se e%cue%&ra% e%

u%a PC.

-?-

3EC. 3.< EAE#PLO3 DE CBIP3 DE CP6

Tercera$ el microAa)a H.- &ie%e -> l,%eas de E:3 pro!ramable ue puede% co%ec&arse a

bo&o%es$ i%&errup&ores y l*mparas del apara&o. Por e(emplo$ u% hor%o de microo%das suele

&e%er u% &eclado %um/rico y al!u%os o&ros bo&o%es ue podr,a% co%ec&arse direc&ame%&e al

chip de CP6. Te%er l,%eas de E:3 pro!ramable direc&ame%&e e% la CP6 hace i%%ecesario

i%cluir chips co%soladores de E:3 pro!ramables$ as, ue el dise'o es m*s simple y me%os

cos&oso. El chip &ambi/% &ie%e &res &empori4adores pro!ramables i%cluidos$ lo cual &ambi/%

es +&il porue los apara&os a me%udo opera% e% &iempo real.

El microAa)a H.- se )e%de e% u% e%capsulado DGA 7Ba <rid ,rra=: de 3-> &ermi0

%ales ue es u% es&*%dar de la i%dus&ria. De es&as &ermi%ales$ <L es&*% co%ec&adas al bus

PCI. Es&udiaremos es&e bus e% u%a secci2% pos&erior del cap,&ulo. O&ras -13 &ermi%ales

so% para el bus de memoria$ i%cluidas >= &ermi%ales de da&os bidireccio%ales as, como

&ermi%ales de direcci2% apar&e. O&ras &ermi%ales se usa% para co%&rol 7H8$ &empori4adores 738$

i%&errupcio%es 7--8$ pruebas 7-.8 y E:3 pro!ramable 7->8. Al!u%as de las &ermi%ales res&a%&es

se usa% 7co% redu%da%cia8 para la alime%&aci2% y la &ierra$ pero o&ras %o se usa%. O&ros

fabrica%&es del picoAa)a II es&*% e% liber&ad de esco!er u% bus dis&i%&o$ o&ro paue&e$ e&c/&era.

El chip &ambi/% &ie%e )arias carac&er,s&icas de hardPare m*s$ como u% modo i%ac&i)o

para ahorrar e%er!,a de ba&er,as$ u% co%&rolador de i%&errupcio%es e% el chip y apoyo ple%o

para el es&*%dar de prueba IEEE --=L.- ATAG.

3.- E4E5P6*S DE BUSES

Los buses so% el &e(ido co%ec&i)o de los sis&emas de compu&aci2%. E% es&a secci2% e5ami%a0

remos de cerca al!u%os buses muy u&ili4ados; el bus I3A$ el bus PCI y el Dus 3erial 6%i)er0

sal. El bus I3A es u%a e5pa%si2% del bus ori!i%al de la ID# PC. Por ra4o%es de

compa&ibilidad hacia a&r*s$ se si!ue i%cluye%do e% &odas las PC basadas e% I%&el$ au%ue &odas

es&as m*ui%as &ie%e% &ambi/% u% se!u%do bus$ m*s r*pido; el PCI. El bus PCI es m*s a%cho

ue el I3A y opera co% u%a &asa de relo( m*s al&a. El Dus 3erial 6%i)ersal es u% bus de E:3

cada )e4 m*s popular para perif/ricos de ba(a )elocidad$ como los ra&o%es y los &eclados. E%

las seccio%es

f

ue si!ue% e5ami%aremos cada u%o de es&os buses.

3.-.# E %u! IS,

El bus de la ID# PC era de hecho el es&*%dar e% los sis&emas basados e% el ?.?? porue casi

&odos los fabrica%&es de clo%es de la PC lo copiaro% para poder usar e% sus sis&emas las

muchas &ar(e&as de E:3 e5is&e%&es hechas por o&ros fabrica%&es. Ese bus &e%,a >1 l,%eas de

se'al$ i%cluidas 1. para u%a direcci2% de memoria$ ? para da&os y u%a e% cada caso para

habili&ar lec&ura de memoria$ escri&ura de memoria$ lec&ura de E:3 y escri&ura de E:3. Tambi/%

hab,a se'ales para solici&ar y co%ceder i%&errupcio%es y usar D#A$ y %ada m*s. Era u% bus

muy se%cillo.

F,sicame%&e$ el bus es&aba !rabado e% la &ar(e&a madre de la PC$ co% u%a media doce%a de

co%ec&ores si&uados a i%&er)alos de 1 cm para i%ser&ar e% ellos &ar(e&as #plu'ins). Cada &ar(e&a

-?1

EL NIVEL DE LOGICA DIGITAL CAP. 3

&e%,a u%a pes&a'a ue embo%aba e% el co%ec&or. La pes&a'a &e%,a 3- &iras chapeadas e% oro e%

cada lado ue hac,a% co%&ac&o el/c&rico co% el co%ec&or.

Cua%do ID# i%&rodu(o la PC:AT basada e% el ?.1?>$ e%fre%&2 u% problema !ra)e. 3i