Escolar Documentos

Profissional Documentos

Cultura Documentos

74AHC259 74AHCT259: 1. General Description

Enviado por

greentea601Título original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

74AHC259 74AHCT259: 1. General Description

Enviado por

greentea601Direitos autorais:

Formatos disponíveis

1.

General description

The 74AHC259; 74AHCT259 is a high-speed Si-gate CMOS device and is pin compatible

with Low-power Schottky TTL (LSTTL). It is specied in compliance with JEDEC standard

No. 7-A.

The 74AHC259; 74AHCT259 is a high-speed 8-bit addressable latch designed for general

purpose storage applications in digital systems. It is a multifunctional device capable of

storing single-line data in eight addressable latches and providing a 3-to-8 decoder and

multiplexer function with active HIGH outputs (Q0 to Q7). It also incorporates an active

LOW common reset (MR) for resetting all latches as well as an active LOW enable input

(LE).

The 74AHC259; 74AHCT259 has four modes of operation:

In the addressable latch mode, data on the data line (D) is written into the addressed

latch. The addressed latch will follow the data input with all non-addressed latches

remaining in their previous states.

In the memory mode, all latches remain in their previous states and are unaffected by

the data or address inputs.

In the 3-to-8 decoding or demultiplexing mode, the addressed output follows the state

of the data input (D) with all other outputs in the LOW state.

In the reset mode, all outputs are LOW and unaffected by the address inputs

(A0 to A2) and data input (D).

When operating the 74AHC259; 74AHCT259 as an address latch, changing more than

one bit of the address could impose a transient-wrong address. Therefore, this should

only be done while in the memory mode.

2. Features

I Balanced propagation delays

I All inputs have Schmitt-trigger actions

I Combines demultiplexer and 8-bit latch

I Serial-to-parallel capability

I Output from each storage bit available

I Random (addressable) data entry

I Easily expandable

I Common reset input

I Useful as a 3-to-8 active HIGH decoder

I Inputs accept voltages higher than V

CC

74AHC259; 74AHCT259

8-bit addressable latch

Rev. 02 15 May 2008 Product data sheet

74AHC_AHCT259_2 NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 02 15 May 2008 2 of 17

NXP Semiconductors 74AHC259; 74AHCT259

8-bit addressable latch

I Input levels:

N For 74AHC259: CMOS level

N For 74AHCT259: TTL level

I ESD protection:

N HBM EIA/JESD22-A114E exceeds 2000 V

N MM EIA/JESD22-A115-A exceeds 200 V

N CDM EIA/JESD22-C101C exceeds 1000 V

I Multiple package options

I Specied from 40 C to +85 C and from 40 C to +125 C

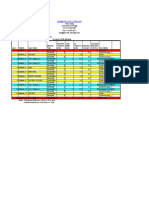

3. Ordering information

4. Functional diagram

Table 1. Ordering information

Type number Package

Temperature range Name Description Version

74AHC259

74AHC259D 40 C to +125 C SO16 plastic small outline package; 16 leads;

body width 3.9 mm

SOT109-1

74AHC259PW 40 C to +125 C TSSOP16 plastic thin shrink small outline package; 16 leads;

body width 4.4 mm

SOT403-1

74AHCT259

74AHCT259D 40 C to +125 C SO16 plastic small outline package; 16 leads;

body width 3.9 mm

SOT109-1

74AHCT259PW 40 C to +125 C TSSOP16 plastic thin shrink small outline package; 16 leads;

body width 4.4 mm

SOT403-1

Fig 1. Logic symbol Fig 2. IEC logic symbol

mna573

D

A0

A1

A2

MR

LE

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

14

15

12

11

10

9

7

6

5

4

3

2

1

13

mna572

1

9,10D

Z9

G8

G10

C10

8R

13

15

14

0

1

2

3

1

2

0

DX

0

7

2

3

4

5

4

6

7

9

10

11

12

5

6

7

G

74AHC_AHCT259_2 NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 02 15 May 2008 3 of 17

NXP Semiconductors 74AHC259; 74AHCT259

8-bit addressable latch

5. Pinning information

5.1 Pinning

5.2 Pin description

Fig 3. Functional diagram

mna571

8 LATCHES

1-of-8

DECODER

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7 12

11

10

9

7

6

5

4

A0

A1

A2

LE

MR

D 13

15

14

3

2

1

Fig 4. Pin conguration

74AHC259

74AHCT259

A0 V

CC

A1 MR

A2 LE

Q0 D

Q1 Q7

Q2 Q6

Q3 Q5

GND Q4

001aai126

1

2

3

4

5

6

7

8

10

9

12

11

14

13

16

15

Table 2. Pin description

Symbol Pin Description

A0 1 address input

A1 2 address input

A2 3 address input

Q0 4 latch output

Q1 5 latch output

Q2 6 latch output

Q3 7 latch output

GND 8 ground (0 V)

Q4 9 latch output

Q5 10 latch output

74AHC_AHCT259_2 NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 02 15 May 2008 4 of 17

NXP Semiconductors 74AHC259; 74AHCT259

8-bit addressable latch

6. Functional description

[1] H = HIGH voltage level;

L = LOW voltage level;

X = dont care;

d = HIGH or LOW data one set-up time prior to the LOW-to-HIGH LE transition;

q = lower case letter indicates the state of the referenced input one set-up time prior to the LOW-to-HIGH transition.

Q6 11 latch output

Q7 12 latch output

D 13 data input

LE 14 latch enable input (active LOW)

MR 15 conditional reset input (active LOW)

V

CC

16 supply voltage

Table 2. Pin description continued

Symbol Pin Description

Table 3. Function table

[1]

Operating mode Input Output

MR LE D A0 A1 A2 Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

Reset (clear) L H X X X X L L L L L L L L

Demultiplexer

(active HIGH 8-channel)

decoder (when D = H)

L L d L L L Q = d L L L L L L L

d H L L L Q = d L L L L L L

d L H L L L Q = d L L L L L

d H H L L L L Q = d L L L L

d L L H L L L L Q = d L L L

d H L H L L L L L Q = d L L

d L H H L L L L L L Q = d L

d H H H L L L L L L L Q = d

Memory (no action) H H X X X X q

0

q

1

q

2

q

3

q

4

q

5

q

6

q

7

Addressable latch H L d L L L Q = d q

1

q

2

q

3

q

4

q

5

q

6

q

7

d H L L q

0

Q = d q

2

q

3

q

4

q

5

q

6

q

7

d L H L q

0

q

1

Q = d q

3

q

4

q

5

q

6

q

7

d H H L q

0

q

1

q

2

Q = d q

4

q

5

q

6

q

7

d L L H q

0

q

1

q

2

q

3

Q = d q

5

q

6

q

7

d H L H q

0

q

1

q

2

q

3

q

4

Q = d q

6

q

7

d L H H q

0

q

1

q

2

q

3

q

4

q

5

Q = d q

7

H H H H q

0

q

1

q

2

q

3

q

4

q

5

q

6

Q = d

74AHC_AHCT259_2 NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 02 15 May 2008 5 of 17

NXP Semiconductors 74AHC259; 74AHCT259

8-bit addressable latch

[1] H = HIGH voltage level; L = LOW voltage level.

7. Limiting values

[1] The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

[2] For SO16 packages: above 70 C the value of P

tot

derates linearly at 8 mW/K.

For TSSOP16 packages: above 60 C the value of P

tot

derates linearly at 5.5 mW/K.

8. Recommended operating conditions

Table 4. Operating mode select table

[1]

LE MR Mode

L H addressable latch

H H memory

L L active HIGH 8-channel demultiplexer

H L reset

Table 5. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V).

Symbol Parameter Conditions Min Max Unit

V

CC

supply voltage 0.5 +7.0 V

V

I

input voltage 0.5 +7.0 V

I

IK

input clamping current V

I

< 0.5 V

[1]

20 - mA

I

OK

output clamping current V

O

< 0.5 V or V

O

> V

CC

+ 0.5 V

[1]

20 +20 mA

I

O

output current V

O

= 0.5 V to (V

CC

+ 0.5 V) 25 +25 mA

I

CC

supply current - +75 mA

I

GND

ground current 75 - mA

T

stg

storage temperature 65 +150 C

P

tot

total power dissipation T

amb

= 40 C to +125 C

[2]

- 500 mW

Table 6. Operating conditions

Symbol Parameter Conditions Min Typ Max Unit

74AHC259

V

CC

supply voltage 2.0 5.0 5.5 V

V

I

input voltage 0 - 5.5 V

V

O

output voltage 0 - V

CC

V

T

amb

ambient temperature 40 +25 +125 C

t/V input transition rise and fall rate V

CC

= 3.0 V to 3.6 V - - 100 ns/V

V

CC

= 4.5 V to 5.5 V - - 20 ns/V

74AHCT259

V

CC

supply voltage 4.5 5.0 5.5 V

V

I

input voltage 0 - 5.5 V

V

O

output voltage 0 - V

CC

V

T

amb

ambient temperature 40 +25 +125 C

t/V input transition rise and fall rate V

CC

= 4.5 V to 5.5 V - - 20 ns/V

74AHC_AHCT259_2 NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 02 15 May 2008 6 of 17

NXP Semiconductors 74AHC259; 74AHCT259

8-bit addressable latch

9. Static characteristics

Table 7. Static characteristics

At recommended operating conditions; voltages are referenced to GND (ground = 0 V).

Symbol Parameter Conditions 25 C 40 C to +85 C 40 C to +125 C Unit

Min Typ Max Min Max Min Max

74AHC259

V

IH

HIGH-level

input voltage

V

CC

= 2.0 V 1.5 - - 1.5 - 1.5 - V

V

CC

= 3.0 V 2.1 - - 2.1 - 2.1 - V

V

CC

= 5.5 V 3.85 - - 3.85 - 3.85 - V

V

IL

LOW-level

input voltage

V

CC

= 2.0 V - - 0.5 - 0.5 - 0.5 V

V

CC

= 3.0 V - - 0.9 - 0.9 - 0.9 V

V

CC

= 5.5 V - - 1.65 - 1.65 - 1.65 V

V

OH

HIGH-level

output voltage

V

I

= V

IH

or V

IL

I

O

= 50 A; V

CC

= 2.0 V 1.9 2.0 - 1.9 - 1.9 - V

I

O

= 50 A; V

CC

= 3.0 V 2.9 3.0 - 2.9 - 2.9 - V

I

O

= 50 A; V

CC

= 4.5 V 4.4 4.5 - 4.4 - 4.4 - V

I

O

= 4.0 mA; V

CC

= 3.0 V 2.58 - - 2.48 - 2.40 - V

I

O

= 8.0 mA; V

CC

= 4.5 V 3.94 - - 3.80 - 3.70 - V

V

OL

LOW-level

output voltage

V

I

= V

IH

or V

IL

I

O

= 50 A; V

CC

= 2.0 V - 0 0.1 - 0.1 - 0.1 V

I

O

= 50 A; V

CC

= 3.0 V - 0 0.1 - 0.1 - 0.1 V

I

O

= 50 A; V

CC

= 4.5 V - 0 0.1 - 0.1 - 0.1 V

I

O

= 4.0 mA; V

CC

= 3.0 V - - 0.36 - 0.44 - 0.55 V

I

O

= 8.0 mA; V

CC

= 4.5 V - - 0.36 - 0.44 - 0.55 V

I

I

input leakage

current

V

I

= 5.5 Vor GND;

V

CC

= 0 V to 5.5 V

- - 0.1 - 1.0 - 2.0 A

I

CC

supply current V

I

= V

CC

or GND; I

O

= 0 A;

V

CC

= 5.5 V

- - 4.0 - 40 - 80 A

C

I

input

capacitance

V

I

= V

CC

or GND - 3 10 - 10 - 10 pF

C

O

output

capacitance

- 4 - - - - - pF

74AHCT259

V

IH

HIGH-level

input voltage

V

CC

= 4.5 V to 5.5 V 2.0 - - 2.0 - 2.0 - V

V

IL

LOW-level

input voltage

V

CC

= 4.5 V to 5.5 V - - 0.8 - 0.8 - 0.8 V

V

OH

HIGH-level

output voltage

V

I

= V

IH

or V

IL

; V

CC

= 4.5 V

I

O

= 50 A 4.4 4.5 - 4.4 - 4.4 - V

I

O

= 8.0 mA 3.94 - - 3.80 - 3.70 - V

V

OL

LOW-level

output voltage

V

I

= V

IH

or V

IL

; V

CC

= 4.5 V

I

O

= 50 A - 0 0.1 - 0.1 - 0.1 V

I

O

= 8.0 mA - - 0.36 - 0.44 - 0.55 V

74AHC_AHCT259_2 NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 02 15 May 2008 7 of 17

NXP Semiconductors 74AHC259; 74AHCT259

8-bit addressable latch

10. Dynamic characteristics

I

I

input leakage

current

V

I

= 5.5 Vor GND;

V

CC

= 0 V to 5.5 V

- - 0.1 - 1.0 - 2.0 A

I

CC

supply current V

I

= V

CC

or GND; I

O

= 0 A;

V

CC

= 5.5 V

- - 4.0 - 40 - 80 A

I

CC

additional

supply current

per input pin; V

I

= V

CC

2.1 V;

other pins at V

CC

or GND;

I

O

= 0 A; V

CC

= 4.5 V to 5.5 V

- - 1.35 - 1.5 - 1.5 mA

C

I

input

capacitance

V

I

= V

CC

or GND - 3 10 - 10 - 10 pF

C

O

output

capacitance

- 4 - - - - - pF

Table 7. Static characteristics continued

At recommended operating conditions; voltages are referenced to GND (ground = 0 V).

Symbol Parameter Conditions 25 C 40 C to +85 C 40 C to +125 C Unit

Min Typ Max Min Max Min Max

Table 8. Dynamic characteristics

Voltages are referenced to GND (ground = 0 V); for test circuit see Figure 11.

Symbol Parameter Conditions 25 C 40 C to +85 C 40 C to +125 C Unit

Min Typ

[1]

Max Min Max Min Max

74AHC259

t

pd

propagation

delay

D to Qn; see Figure 5

[2]

V

CC

= 3.0 V to 3.6 V

C

L

= 15 pF - 5.8 11.5 1.0 13.5 1.0 15.0 ns

C

L

= 50 pF - 7.3 14.5 1.0 17.0 1.0 18.5 ns

V

CC

= 4.5 V to 5.5 V

C

L

= 15 pF - 4.1 7.5 1.0 9.0 1.0 10.0 ns

C

L

= 50 pF - 5.3 9.5 1.0 11.0 1.0 12.0 ns

An to Qn; see Figure 6

[2]

V

CC

= 3.0 V to 3.6 V

C

L

= 15 pF - 7.5 14.5 1.0 17.0 1.0 18.5 ns

C

L

= 50 pF - 9.1 18.0 1.0 21.0 1.0 23.0 ns

V

CC

= 4.5 V to 5.5 V

C

L

= 15 pF - 5.3 9.5 1.0 11.5 1.0 12.5 ns

C

L

= 50 pF - 6.5 11.5 1.0 13.5 1.0 15.0 ns

LE to Qn; see Figure 7

[2]

V

CC

= 3.0 V to 3.6 V

C

L

= 15 pF - 6.2 12.0 1.0 14.0 1.0 15.2 ns

C

L

= 50 pF - 7.7 15.5 1.0 17.5 1.0 19.0 ns

V

CC

= 4.5 V to 5.5 V

C

L

= 15 pF - 4.3 8.0 1.0 9.5 1.0 10.5 ns

C

L

= 50 pF - 5.5 10.0 1.0 11.5 1.0 12.5 ns

74AHC_AHCT259_2 NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 02 15 May 2008 8 of 17

NXP Semiconductors 74AHC259; 74AHCT259

8-bit addressable latch

t

pd

propagation

delay

MR to Qn; see Figure 8

[3]

V

CC

= 3.0 V to 3.6 V

C

L

= 15 pF - 5.4 10.5 1.0 12.5 1.0 13.5 ns

C

L

= 50 pF - 7.0 13.5 1.0 15.5 1.0 17.0 ns

V

CC

= 4.5 V to 5.5 V

C

L

= 15 pF - 3.9 7.0 1.0 8.5 1.0 9.5 ns

C

L

= 50 pF - 5.1 9.0 1.0 10.5 1.0 11.5 ns

t

W

pulse width LE HIGH or LOW;

see Figure 7

V

CC

= 3.0 V to 3.6 V 5.0 - - 5.0 - 5.0 - ns

V

CC

= 4.5 V to 5.5 V 5.0 - - 5.0 - 5.0 - ns

MR LOW; see Figure 8

V

CC

= 3.0 V to 3.6 V 5.0 - - 5.0 - 5.0 - ns

V

CC

= 4.5 V to 5.5 V 5.0 - - 5.0 - 5.0 - ns

t

su

set-up time D, An to LE; see Figure 9

and Figure 10

V

CC

= 3.0 V to 3.6 V 4.0 - - 4.0 - 4.0 - ns

V

CC

= 4.5 V to 5.5 V 4.0 - - 4.0 - 4.0 - ns

t

h

hold time D, An to LE; see Figure 9

and Figure 10

V

CC

= 3.0 V to 3.6 V 1.0 - - 1.0 - 1.0 - ns

V

CC

= 4.5 V to 5.5 V 1.0 - - 1.0 - 1.0 - ns

C

PD

power

dissipation

capacitance

f

i

= 1 MHz; V

I

= GND to V

CC

[4]

- 13 - - - - - pF

74AHCT259; V

CC

= 4.5 V to 5.5 V

t

pd

propagation

delay

D to Qn; see Figure 5

[2]

C

L

= 15 pF - 4.1 7.5 1.0 9.0 1.0 10.0 ns

C

L

= 50 pF - 5.4 9.5 1.0 11.0 1.0 12.0 ns

An to Qn; see Figure 6

[2]

C

L

= 15 pF - 5.5 9.5 1.0 11.5 1.0 12.5 ns

C

L

= 50 pF - 6.6 12.0 1.0 14.0 1.0 15.5 ns

LE to Qn; see Figure 7

[2]

C

L

= 15 pF - 4.3 8.0 1.0 9.5 1.0 10.4 ns

C

L

= 50 pF - 5.5 10.0 1.0 12.0 1.0 13.0 ns

MR to Qn; see Figure 8

[3]

C

L

= 15 pF - 3.9 7.0 1.0 8.5 1.0 9.5 ns

C

L

= 50 pF - 5.1 9.0 1.0 10.5 1.0 11.5 ns

t

W

pulse width LE HIGH or LOW;

see Figure 7

5.0 - - 5.0 - 5.0 - ns

MR LOW; see Figure 8 5.0 - - 5.0 - 5.0 - ns

Table 8. Dynamic characteristics continued

Voltages are referenced to GND (ground = 0 V); for test circuit see Figure 11.

Symbol Parameter Conditions 25 C 40 C to +85 C 40 C to +125 C Unit

Min Typ

[1]

Max Min Max Min Max

74AHC_AHCT259_2 NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 02 15 May 2008 9 of 17

NXP Semiconductors 74AHC259; 74AHCT259

8-bit addressable latch

[1] Typical values are measured at nominal supply voltage (V

CC

= 3.3 V and V

CC

= 5.0 V).

[2] t

pd

is the same as t

PLH

and t

PHL

.

[3] t

pd

is the same as t

PHL

only.

[4] C

PD

is used to determine the dynamic power dissipation (P

D

in W).

P

D

= C

PD

V

CC

2

f

i

N + (C

L

V

CC

2

f

o

) where:

f

i

= input frequency in MHz;

f

o

= output frequency in MHz;

C

L

= output load capacitance in pF;

V

CC

= supply voltage in V;

N = number of inputs switching;

(C

L

V

CC

2

f

o

) = sum of the outputs.

11. Waveforms

t

su

set-up time D, An to LE; see Figure 9

and Figure 10

4.0 - - 4.0 - 4.0 - ns

t

h

hold time D, An to LE; see Figure 9

and Figure 10

1.0 - - 1.0 - 1.0 - ns

C

PD

power

dissipation

capacitance

f

i

= 1 MHz; V

I

= GND to V

CC

[4]

- 17 - - - - - pF

Table 8. Dynamic characteristics continued

Voltages are referenced to GND (ground = 0 V); for test circuit see Figure 11.

Symbol Parameter Conditions 25 C 40 C to +85 C 40 C to +125 C Unit

Min Typ

[1]

Max Min Max Min Max

Measurement points are given in Table 9.

V

OL

and V

OH

are typical voltage output levels that occur with the output load.

Fig 5. Data input to output propagation delays

001aah123

D input

Qn output

t

PHL

t

PLH

GND

V

CC

V

M

V

M

V

OH

V

OL

74AHC_AHCT259_2 NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 02 15 May 2008 10 of 17

NXP Semiconductors 74AHC259; 74AHCT259

8-bit addressable latch

Measurement points are given in Table 9.

V

OL

and V

OH

are typical voltage output levels that occur with the output load.

Fig 6. Address input to output propagation delays

001aah122

An input

Qn output

t

PHL

t

PLH

GND

V

CC

V

M

V

M

V

OH

V

OL

Measurement points are given in Table 9.

V

OL

and V

OH

are typical voltage output levels that occur with the output load.

Fig 7. Enable input to output propagation delays and pulse width

001aah121

LE input

Qn output

t

PHL

t

PLH

t

W

V

M

V

OH

V

CC

GND

V

CC

GND

V

OL

V

M

D input

Measurement points are given in Table 9.

V

OL

and V

OH

are typical voltage output levels that occur with the output load.

Fig 8. Conditional reset input to output propagation delays

001aah124

MR input

Qn output

t

PHL

t

W

V

M

V

OH

V

CC

GND

V

OL

V

M

74AHC_AHCT259_2 NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 02 15 May 2008 11 of 17

NXP Semiconductors 74AHC259; 74AHCT259

8-bit addressable latch

Measurement points are given in Table 9.

The shaded areas indicate when the input is permitted to change for predictable output performance.

V

OL

and V

OH

are typical voltage output levels that occur with the output load.

Fig 9. Data input to latch enable input set-up and hold times

001aah125

GND

GND

t

h

t

su

t

h

t

su

V

M

V

M

V

M

V

CC

V

OH

V

OL

V

CC

Qn output Q = D Q = D

LE input

D input

Measurement points are given in Table 9.

The shaded areas indicate when the input is permitted to change for predictable output performance.

V

OL

and V

OH

are typical voltage output levels that occur with the output load.

Fig 10. Address input to latch enable input set-up and hold times

001aah126

V

M

ADDRESS STABLE

V

M

t

h

t

su

V

CC

GND

V

CC

GND

LE input

An input

Table 9. Measurement points

Type Input Output

V

M

V

M

74AHC259 0.5 V

CC

0.5 V

CC

74AHCT259 1.5 V 0.5 V

CC

74AHC_AHCT259_2 NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 02 15 May 2008 12 of 17

NXP Semiconductors 74AHC259; 74AHCT259

8-bit addressable latch

Test data is given in Table 10.

Denitions test circuit:

R

T

= termination resistance should be equal to output impedance Z

o

of the pulse generator.

C

L

= load capacitance including jig and probe capacitance.

Fig 11. Load circuitry for measuring switching times

001aah768

t

W

t

W

t

r

t

r

t

f

V

M

V

I

negative

pulse

GND

V

I

positive

pulse

GND

10 %

90 %

90 %

10 %

V

M

V

M

V

M

t

f

V

CC

DUT

R

T

V

I

V

O

C

L

G

Table 10. Test data

Type Input Load Test

V

I

t

r

, t

f

C

L

74AHC259 V

CC

3.0 ns 15 pF, 50 pF t

PLH

, t

PHL

74AHCT259 3.0 V 3.0 ns 15 pF, 50 pF t

PLH

, t

PHL

74AHC_AHCT259_2 NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 02 15 May 2008 13 of 17

NXP Semiconductors 74AHC259; 74AHCT259

8-bit addressable latch

12. Package outline

Fig 12. Package outline SOT109-1 (SO16)

X

w M

A

A

1

A

2

b

p

D

H

E

L

p

Q

detail X

E

Z

e

c

L

v M A

(A )

3

A

8

9

1

16

y

pin 1 index

UNIT

A

max.

A

1

A

2

A

3

b

p

c D

(1)

E

(1) (1)

e H

E

L L

p

Q Z y w v

REFERENCES

OUTLINE

VERSION

EUROPEAN

PROJECTION

ISSUE DATE

IEC JEDEC JEITA

mm

inches

1.75

0.25

0.10

1.45

1.25

0.25

0.49

0.36

0.25

0.19

10.0

9.8

4.0

3.8

1.27

6.2

5.8

0.7

0.6

0.7

0.3

8

0

o

o

0.25 0.1

DIMENSIONS (inch dimensions are derived from the original mm dimensions)

Note

1. Plastic or metal protrusions of 0.15 mm (0.006 inch) maximum per side are not included.

1.0

0.4

SOT109-1

99-12-27

03-02-19

076E07 MS-012

0.069

0.010

0.004

0.057

0.049

0.01

0.019

0.014

0.0100

0.0075

0.39

0.38

0.16

0.15

0.05

1.05

0.041

0.244

0.228

0.028

0.020

0.028

0.012

0.01

0.25

0.01 0.004

0.039

0.016

0 2.5 5 mm

scale

SO16: plastic small outline package; 16 leads; body width 3.9 mm SOT109-1

74AHC_AHCT259_2 NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 02 15 May 2008 14 of 17

NXP Semiconductors 74AHC259; 74AHCT259

8-bit addressable latch

Fig 13. Package outline SOT403-1 (TSSOP16)

UNIT A

1

A

2

A

3

b

p

c D

(1)

E

(2) (1)

e H

E

L L

p

Q Z y w v

REFERENCES

OUTLINE

VERSION

EUROPEAN

PROJECTION

ISSUE DATE

IEC JEDEC JEITA

mm

0.15

0.05

0.95

0.80

0.30

0.19

0.2

0.1

5.1

4.9

4.5

4.3

0.65

6.6

6.2

0.4

0.3

0.40

0.06

8

0

o

o

0.13 0.1 0.2 1

DIMENSIONS (mm are the original dimensions)

Notes

1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

2. Plastic interlead protrusions of 0.25 mm maximum per side are not included.

0.75

0.50

SOT403-1 MO-153

99-12-27

03-02-18

w M

b

p

D

Z

e

0.25

1 8

16 9

A

A

1

A

2

L

p

Q

detail X

L

(A )

3

H

E

E

c

v M A

X

A

y

0 2.5 5 mm

scale

TSSOP16: plastic thin shrink small outline package; 16 leads; body width 4.4 mm SOT403-1

A

max.

1.1

pin 1 index

74AHC_AHCT259_2 NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 02 15 May 2008 15 of 17

NXP Semiconductors 74AHC259; 74AHCT259

8-bit addressable latch

13. Abbreviations

14. Revision history

Table 11. Abbreviations

Acronym Description

CDM Charged Device Model

CMOS Complementary Metal-Oxide Semiconductor

DUT Device Under Test

ESD ElectroStatic Discharge

HBM Human Body Model

LSTTL Low-power Schottky Transistor-Transistor Logic

MM Machine Model

Table 12. Revision history

Document ID Release date Data sheet status Change notice Supersedes

74AHC_AHCT259_2 20080515 Product data sheet - 74AHC_AHCT259_1

Modications: The format of this data sheet has been redesigned to comply with the new identity guidelines

of NXP Semiconductors.

Legal texts have been adapted to the new company name where appropriate.

Table 6: the conditions for input leakage current have been changed.

74AHC_AHCT259_1 20000314 Product specication - -

74AHC_AHCT259_2 NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 02 15 May 2008 16 of 17

NXP Semiconductors 74AHC259; 74AHCT259

8-bit addressable latch

15. Legal information

15.1 Data sheet status

[1] Please consult the most recently issued document before initiating or completing a design.

[2] The term short data sheet is explained in section Denitions.

[3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status

information is available on the Internet at URL http://www.nxp.com.

15.2 Denitions

Draft The document is a draft version only. The content is still under

internal review and subject to formal approval, which may result in

modications or additions. NXP Semiconductors does not give any

representations or warranties as to the accuracy or completeness of

information included herein and shall have no liability for the consequences of

use of such information.

Short data sheet A short data sheet is an extract from a full data sheet

with the same product type number(s) and title. A short data sheet is intended

for quick reference only and should not be relied upon to contain detailed and

full information. For detailed and full information see the relevant full data

sheet, which is available on request via the local NXP Semiconductors sales

ofce. In case of any inconsistency or conict with the short data sheet, the

full data sheet shall prevail.

15.3 Disclaimers

General Information in this document is believed to be accurate and

reliable. However, NXP Semiconductors does not give any representations or

warranties, expressed or implied, as to the accuracy or completeness of such

information and shall have no liability for the consequences of use of such

information.

Right to make changes NXP Semiconductors reserves the right to make

changes to information published in this document, including without

limitation specications and product descriptions, at any time and without

notice. This document supersedes and replaces all information supplied prior

to the publication hereof.

Suitability for use NXP Semiconductors products are not designed,

authorized or warranted to be suitable for use in medical, military, aircraft,

space or life support equipment, nor in applications where failure or

malfunction of an NXP Semiconductors product can reasonably be expected

to result in personal injury, death or severe property or environmental

damage. NXP Semiconductors accepts no liability for inclusion and/or use of

NXP Semiconductors products in such equipment or applications and

therefore such inclusion and/or use is at the customers own risk.

Applications Applications that are described herein for any of these

products are for illustrative purposes only. NXP Semiconductors makes no

representation or warranty that such applications will be suitable for the

specied use without further testing or modication.

Limiting values Stress above one or more limiting values (as dened in

the Absolute Maximum Ratings System of IEC 60134) may cause permanent

damage to the device. Limiting values are stress ratings only and operation of

the device at these or any other conditions above those given in the

Characteristics sections of this document is not implied. Exposure to limiting

values for extended periods may affect device reliability.

Terms and conditions of sale NXP Semiconductors products are sold

subject to the general terms and conditions of commercial sale, as published

at http://www.nxp.com/prole/terms, including those pertaining to warranty,

intellectual property rights infringement and limitation of liability, unless

explicitly otherwise agreed to in writing by NXP Semiconductors. In case of

any inconsistency or conict between information in this document and such

terms and conditions, the latter will prevail.

No offer to sell or license Nothing in this document may be interpreted

or construed as an offer to sell products that is open for acceptance or the

grant, conveyance or implication of any license under any copyrights, patents

or other industrial or intellectual property rights.

15.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks

are the property of their respective owners.

16. Contact information

For more information, please visit: http://www.nxp.com

For sales ofce addresses, please send an email to: salesaddresses@nxp.com

Document status

[1][2]

Product status

[3]

Denition

Objective [short] data sheet Development This document contains data from the objective specication for product development.

Preliminary [short] data sheet Qualication This document contains data from the preliminary specication.

Product [short] data sheet Production This document contains the product specication.

NXP Semiconductors 74AHC259; 74AHCT259

8-bit addressable latch

NXP B.V. 2008. All rights reserved.

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 15 May 2008

Document identifier: 74AHC_AHCT259_2

Please be aware that important notices concerning this document and the product(s)

described herein, have been included in section Legal information.

17. Contents

1 General description. . . . . . . . . . . . . . . . . . . . . . 1

2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

3 Ordering information. . . . . . . . . . . . . . . . . . . . . 2

4 Functional diagram . . . . . . . . . . . . . . . . . . . . . . 2

5 Pinning information. . . . . . . . . . . . . . . . . . . . . . 3

5.1 Pinning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

5.2 Pin description . . . . . . . . . . . . . . . . . . . . . . . . . 3

6 Functional description . . . . . . . . . . . . . . . . . . . 4

7 Limiting values. . . . . . . . . . . . . . . . . . . . . . . . . . 5

8 Recommended operating conditions. . . . . . . . 5

9 Static characteristics. . . . . . . . . . . . . . . . . . . . . 6

10 Dynamic characteristics . . . . . . . . . . . . . . . . . . 7

11 Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

12 Package outline . . . . . . . . . . . . . . . . . . . . . . . . 13

13 Abbreviations. . . . . . . . . . . . . . . . . . . . . . . . . . 15

14 Revision history. . . . . . . . . . . . . . . . . . . . . . . . 15

15 Legal information. . . . . . . . . . . . . . . . . . . . . . . 16

15.1 Data sheet status . . . . . . . . . . . . . . . . . . . . . . 16

15.2 Denitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

15.3 Disclaimers . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

15.4 Trademarks. . . . . . . . . . . . . . . . . . . . . . . . . . . 16

16 Contact information. . . . . . . . . . . . . . . . . . . . . 16

17 Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Você também pode gostar

- Multi Threading PDFDocumento48 páginasMulti Threading PDFShweta Nikhar67% (3)

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsAinda não há avaliações

- Demonstration of Software-Defined Packet-Optical Network Emulation With Mininet-Optical and ONOSDocumento8 páginasDemonstration of Software-Defined Packet-Optical Network Emulation With Mininet-Optical and ONOSCamilo SamboniAinda não há avaliações

- Connecting TOPServerV5 To Wonderware InTouchDocumento10 páginasConnecting TOPServerV5 To Wonderware InTouchtsuoscaradrianAinda não há avaliações

- ERAN Troubleshooting Guide (V100R010C10 - Draft A) (PDF) - enDocumento225 páginasERAN Troubleshooting Guide (V100R010C10 - Draft A) (PDF) - enAhmed Ali EmaraAinda não há avaliações

- Data Sheet: 74AHC74 74AHCT74Documento20 páginasData Sheet: 74AHC74 74AHCT74Kang JadiJaya OtodidakAinda não há avaliações

- 74HC HCT574Documento19 páginas74HC HCT574huypiggyAinda não há avaliações

- 74AHC125 74AHCT125: 1. General DescriptionDocumento15 páginas74AHC125 74AHCT125: 1. General Descriptionkitt354Ainda não há avaliações

- MC74ACT564 Octal D Type Flip Flop With 3 State Outputs: PDIP 20 N Suffix CASE 738Documento8 páginasMC74ACT564 Octal D Type Flip Flop With 3 State Outputs: PDIP 20 N Suffix CASE 738greentea601Ainda não há avaliações

- 74AHC1G86 74AHCT1G86: 1. General DescriptionDocumento12 páginas74AHC1G86 74AHCT1G86: 1. General DescriptionKushalSwamyAinda não há avaliações

- 74AHC1G32 74AHCT1G32: 1. General DescriptionDocumento12 páginas74AHC1G32 74AHCT1G32: 1. General DescriptionnevdullAinda não há avaliações

- 74AHC1G02 74AHCT1G02: 1. General DescriptionDocumento11 páginas74AHC1G02 74AHCT1G02: 1. General DescriptionMarcu Andrei StefanAinda não há avaliações

- 74HC10-Q100 74HCT10-Q100: 1. General DescriptionDocumento13 páginas74HC10-Q100 74HCT10-Q100: 1. General DescriptionNelson RodriguezAinda não há avaliações

- 74LS174Documento3 páginas74LS174Raul Sedano Lau100% (1)

- 74HC257 74HCT257: 1. General DescriptionDocumento17 páginas74HC257 74HCT257: 1. General DescriptionMadou JohnAinda não há avaliações

- 74LS75 PDFDocumento4 páginas74LS75 PDFDeni KhanAinda não há avaliações

- 74HC4040 74HCT4040: 1. General DescriptionDocumento24 páginas74HC4040 74HCT4040: 1. General Descriptiontt884211Ainda não há avaliações

- 74LVC08A: 1. General DescriptionDocumento15 páginas74LVC08A: 1. General DescriptionWalterAinda não há avaliações

- 74HC08 74HCT08: 1. General DescriptionDocumento16 páginas74HC08 74HCT08: 1. General DescriptionCesar VilledaAinda não há avaliações

- 74HC573Documento21 páginas74HC573ric_napigkitAinda não há avaliações

- General Description: Quad Bistable Transparant LatchDocumento20 páginasGeneral Description: Quad Bistable Transparant LatchCesar VilledaAinda não há avaliações

- 74HC107 74HCT107: 1. General DescriptionDocumento20 páginas74HC107 74HCT107: 1. General DescriptionDistribuidorIBoolPedregalDeSantoDomingoAinda não há avaliações

- 74HC00 74HCT00: 1. General DescriptionDocumento16 páginas74HC00 74HCT00: 1. General DescriptionvanlongsportAinda não há avaliações

- 74HC02 74HCT02: 1. General DescriptionDocumento16 páginas74HC02 74HCT02: 1. General DescriptionCesar VilledaAinda não há avaliações

- General Description: Quad Bilateral SwitchDocumento23 páginasGeneral Description: Quad Bilateral Switchtotal4321Ainda não há avaliações

- 74LVC14APWDHDocumento11 páginas74LVC14APWDHIlie GrecuAinda não há avaliações

- 74HC03 74HCT03: 1. General DescriptionDocumento16 páginas74HC03 74HCT03: 1. General DescriptionDistribuidorIBoolPedregalDeSantoDomingoAinda não há avaliações

- 8-Bit Shift Register With Input Storage Registers (3-State) : Integrated CircuitsDocumento14 páginas8-Bit Shift Register With Input Storage Registers (3-State) : Integrated CircuitsskiziltoprakAinda não há avaliações

- 74 LV 00Documento10 páginas74 LV 00Brzata PticaAinda não há avaliações

- 74ahc Ahct1g14Documento15 páginas74ahc Ahct1g14Ignacio ScalisiAinda não há avaliações

- 8-Bit Serial-Input/Serial or Parallel-Output Shift Register With Latched 3-State OutputsDocumento11 páginas8-Bit Serial-Input/Serial or Parallel-Output Shift Register With Latched 3-State OutputsLưu TinhAinda não há avaliações

- Datasheet 74153Documento17 páginasDatasheet 74153Ingga Permana0% (1)

- 74164Documento4 páginas74164milkyway69Ainda não há avaliações

- 74 HC 138Documento5 páginas74 HC 138dlbplbAinda não há avaliações

- 74 HC 245Documento22 páginas74 HC 245Vương QuýAinda não há avaliações

- 74HC02 74HCT02: 1. General DescriptionDocumento15 páginas74HC02 74HCT02: 1. General DescriptionAnonymous xTGQYFrAinda não há avaliações

- General Description: Quad Buffer/line Driver 3-StateDocumento15 páginasGeneral Description: Quad Buffer/line Driver 3-Statesinner86Ainda não há avaliações

- 47HC00 NandDocumento17 páginas47HC00 NandWilliams Paredes CAinda não há avaliações

- DM 74 Ls 90Documento6 páginasDM 74 Ls 90Clesio MichaelAinda não há avaliações

- 74HC14 74HCT14: 1. General DescriptionDocumento21 páginas74HC14 74HCT14: 1. General DescriptionDao Nguyen Trong TinAinda não há avaliações

- Data Sheet: 74HC14 74HCT14Documento23 páginasData Sheet: 74HC14 74HCT14Miguel LamborghiniAinda não há avaliações

- 74HC04 74HCT04: 1. General DescriptionDocumento18 páginas74HC04 74HCT04: 1. General DescriptionDistribuidorIBoolPedregalDeSantoDomingoAinda não há avaliações

- 74LS74 PDFDocumento3 páginas74LS74 PDFDeni KhanAinda não há avaliações

- 74 Alvc 164245Documento13 páginas74 Alvc 164245roozbehxoxAinda não há avaliações

- Octal 3-State Noninverting D Flip-Flop: KK74HC574ADocumento6 páginasOctal 3-State Noninverting D Flip-Flop: KK74HC574Ajksb100Ainda não há avaliações

- 4 X 4 Register File Open-Collector SN54/74LS170: Low Power SchottkyDocumento4 páginas4 X 4 Register File Open-Collector SN54/74LS170: Low Power Schottkydistrict19Ainda não há avaliações

- 74HC08 74HCT08: 1. General DescriptionDocumento15 páginas74HC08 74HCT08: 1. General DescriptionFlavio KwiecinskiAinda não há avaliações

- 9-Bit Odd/Even Parity Generators/Checkers SN54/74LS280: Low Power SchottkyDocumento2 páginas9-Bit Odd/Even Parity Generators/Checkers SN54/74LS280: Low Power Schottkydistrict19Ainda não há avaliações

- 74HC573 Octal LatchDocumento13 páginas74HC573 Octal LatchWonzAinda não há avaliações

- 74HC245 74HCT245: 1. General DescriptionDocumento18 páginas74HC245 74HCT245: 1. General Descriptionnadeem hameedAinda não há avaliações

- 1-Of-10 Decoder/Driver Open-Collector SN54/74LS145: Low Power SchottkyDocumento3 páginas1-Of-10 Decoder/Driver Open-Collector SN54/74LS145: Low Power SchottkyShyamsundar JenaAinda não há avaliações

- CD74HC238Documento7 páginasCD74HC238roozbehxoxAinda não há avaliações

- 74LVC1G04: 1. General DescriptionDocumento20 páginas74LVC1G04: 1. General DescriptionnevdullAinda não há avaliações

- DM74LS164 8-Bit Serial In/Parallel Out Shift Register: General Description FeaturesDocumento5 páginasDM74LS164 8-Bit Serial In/Parallel Out Shift Register: General Description FeaturesRoby Adi WibowoAinda não há avaliações

- DatasheetDocumento8 páginasDatasheetMaizatul Hanisah RoziAinda não há avaliações

- 74HC74 74HCT74: 1. General DescriptionDocumento21 páginas74HC74 74HCT74: 1. General DescriptionGermán BergerAinda não há avaliações

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Ainda não há avaliações

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1No EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Nota: 2.5 de 5 estrelas2.5/5 (3)

- IDT54/74FCT373T/AT/CT Fast Cmos Octal Transparent Latch: Features: DescriptionDocumento7 páginasIDT54/74FCT373T/AT/CT Fast Cmos Octal Transparent Latch: Features: Descriptiongreentea601Ainda não há avaliações

- Nc7Sz373 Tinylogic Uhs D-Type Latch With 3-State Output: General Description FeaturesDocumento9 páginasNc7Sz373 Tinylogic Uhs D-Type Latch With 3-State Output: General Description Featuresgreentea601Ainda não há avaliações

- MC14099B 8-Bit Addressable Latches: Marking DiagramsDocumento8 páginasMC14099B 8-Bit Addressable Latches: Marking Diagramsgreentea601Ainda não há avaliações

- MC10E155, MC100E155 5VECL 6 Bit 2:1 Mux Latch: DescriptionDocumento8 páginasMC10E155, MC100E155 5VECL 6 Bit 2:1 Mux Latch: Descriptiongreentea601Ainda não há avaliações

- 3-BIT 4:1 Mux-Latch: Features DescriptionDocumento4 páginas3-BIT 4:1 Mux-Latch: Features Descriptiongreentea601Ainda não há avaliações

- MC14042B Quad Transparent Latch: Marking DiagramsDocumento7 páginasMC14042B Quad Transparent Latch: Marking Diagramsgreentea601Ainda não há avaliações

- Laser Distributor Pte LTD: 1 Rochor Canal Road #05-58, Sim Lim Square Tel:63362806, 63362510, Fax: 63397008Documento9 páginasLaser Distributor Pte LTD: 1 Rochor Canal Road #05-58, Sim Lim Square Tel:63362806, 63362510, Fax: 63397008greentea601Ainda não há avaliações

- International Pte LTD: Asus R9 290 4GB GDDR5Documento6 páginasInternational Pte LTD: Asus R9 290 4GB GDDR5greentea601Ainda não há avaliações

- NL17SG373 Low-Power D-Type Transparent Latch With 3-State OutputDocumento10 páginasNL17SG373 Low-Power D-Type Transparent Latch With 3-State Outputgreentea601Ainda não há avaliações

- Cymax Zbox Ci320 Nano PC CYMAX I3 NUC-D34010WYK Compact PC: PRO PRODocumento2 páginasCymax Zbox Ci320 Nano PC CYMAX I3 NUC-D34010WYK Compact PC: PRO PROgreentea601Ainda não há avaliações

- Prices Are Subject To Change Without Prior Notice.: Mediapro TechnologyDocumento25 páginasPrices Are Subject To Change Without Prior Notice.: Mediapro Technologygreentea601100% (1)

- Flash Memory TestingDocumento75 páginasFlash Memory Testinggreentea601Ainda não há avaliações

- 2468 V 33 StackupDocumento1 página2468 V 33 Stackupgreentea601Ainda não há avaliações

- ADC Driver Selection Guide FinalDocumento2 páginasADC Driver Selection Guide Finalgreentea601Ainda não há avaliações

- IPC 4101 B Slash Sheet MatrixDocumento4 páginasIPC 4101 B Slash Sheet Matrixgreentea601Ainda não há avaliações

- SAF1562Documento97 páginasSAF1562greentea601Ainda não há avaliações

- Chapter 1 Introduction To Internet ProgrammingDocumento4 páginasChapter 1 Introduction To Internet ProgrammingchetraTEP100% (1)

- Install VSAScannerNinjaDocumento33 páginasInstall VSAScannerNinjaOmar CendronAinda não há avaliações

- Au Python PDFDocumento8 páginasAu Python PDFIsmael Ferreras HerreraAinda não há avaliações

- Vrealize Automation Load BalancingDocumento24 páginasVrealize Automation Load BalancingIan CarterAinda não há avaliações

- 01 IntroductiontoNW31314INETIIDocumento9 páginas01 IntroductiontoNW31314INETIISunday PakpahanAinda não há avaliações

- Reverse Engineering 101Documento109 páginasReverse Engineering 101redrumz100% (3)

- The Osi Model: Layered ArchitectureDocumento3 páginasThe Osi Model: Layered ArchitectureViren KathiriyaAinda não há avaliações

- Ftalk Pp011 en PDocumento4 páginasFtalk Pp011 en PTeddy HariyantoAinda não há avaliações

- Transport Phenomena Fundamentals PDFDocumento2 páginasTransport Phenomena Fundamentals PDFAnonymous RDOwEc0% (2)

- MP 3Documento24 páginasMP 3Sebastian Cipriano FelipeAinda não há avaliações

- PDFDocumento28 páginasPDFMiraAinda não há avaliações

- Cisco 3800 SeriesDocumento12 páginasCisco 3800 Seriessankifko100% (1)

- HTML5 and CSS3: Develop With Tomorrow's Standards TodayDocumento7 páginasHTML5 and CSS3: Develop With Tomorrow's Standards Todaylakshmiescribd100% (1)

- Design Review ChecklistDocumento2 páginasDesign Review Checklistjijo1234567Ainda não há avaliações

- Types of Addressing ModeDocumento14 páginasTypes of Addressing ModeMukesh Mushya0% (1)

- 3GPP Network ArchitectureDocumento18 páginas3GPP Network ArchitectureRmkumars100% (1)

- Lab Manual Web EngineeringDocumento44 páginasLab Manual Web Engineeringvijay ghagreAinda não há avaliações

- Tribhuvan University Institute of Engineering Pulchowk CampusDocumento21 páginasTribhuvan University Institute of Engineering Pulchowk Campus150T GameAinda não há avaliações

- RBS 3000Documento3 páginasRBS 3000mintoissacAinda não há avaliações

- After Effects Notes and Animation ProductionDocumento17 páginasAfter Effects Notes and Animation ProductionSundara Rami ReddyAinda não há avaliações

- S8 - S16 Datasheet PDFDocumento2 páginasS8 - S16 Datasheet PDFagungcomlAinda não há avaliações

- Survey QuestionnaireDocumento3 páginasSurvey QuestionnaireHenricson O. HiraoAinda não há avaliações

- 1.2a Timing - Sense - Timing Arc inDocumento5 páginas1.2a Timing - Sense - Timing Arc inSudheer GangisettyAinda não há avaliações

- WCC Advanced V13 SP1 enUS en-US PDFDocumento7.942 páginasWCC Advanced V13 SP1 enUS en-US PDFDajana100% (1)

- Generating Optimizing and Verifying HDL Code With Matlab and Simulink PDFDocumento46 páginasGenerating Optimizing and Verifying HDL Code With Matlab and Simulink PDFvishwasAinda não há avaliações

- 6.1.1.1 Video Tutorial - The Purpose of QoSDocumento1 página6.1.1.1 Video Tutorial - The Purpose of QoSCao Chi KienAinda não há avaliações