Escolar Documentos

Profissional Documentos

Cultura Documentos

Nc7Sz373 Tinylogic Uhs D-Type Latch With 3-State Output: General Description Features

Enviado por

greentea601Descrição original:

Título original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Nc7Sz373 Tinylogic Uhs D-Type Latch With 3-State Output: General Description Features

Enviado por

greentea601Direitos autorais:

Formatos disponíveis

2004 Fairchild Semiconductor Corporation DS500157 www.fairchildsemi.

com

June 1998

Revised August 2004

N

C

7

S

Z

3

7

3

T

i

n

y

L

o

g

i

c

U

H

S

D

-

T

y

p

e

L

a

t

c

h

w

i

t

h

3

-

S

T

A

T

E

O

u

t

p

u

t

NC7SZ373

TinyLogic UHS D-Type Latch with 3-STATE Output

General Description

The NC7SZ373 is a single positive edge-triggered D-type

CMOS Latch with 3-STATE output from Fairchilds Ultra

High Speed Series of TinyLogic in the space saving

SC70 6-lead package. The device is fabricated with

advanced CMOS technology to achieve ultra high speed

with high output drive while maintaining low static power

dissipation over a very broad V

CC

operating range. The

device is specified to operate over the 1.65V to 5.5V range.

The inputs and output are high impedance when V

CC

is 0V.

Inputs tolerate voltages up to 7V independent of V

CC

oper-

ating voltage. The latch appears transparent to the data

when Latch Enable (LE) is HIGH. When LE is LOW, the

data that meets the setup time is latched. The output toler-

ates voltages above V

CC

in the 3-STATE condition.

Features

I Space saving SC70 6-lead package

I Ultra small MicroPak leadless package

I Ultra High Speed; t

PD

2.6 ns Typ into 50 pF at 5V V

CC

I High Output Drive; 24 mA at 3V V

CC

I Broad V

CC

Operating Range; 1.65V to 5.5V

I Matches the performance of LCX when operated at

3.3V V

CC

I Power down high impedance inputs/output

I Overvoltage tolerant inputs facilitate 5V to 3V translation

I Patented noise/EMI reduction circuitry implemented

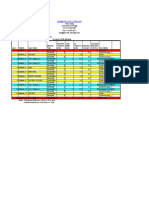

Ordering Code:

TinyLogic is a registered trademark of Fairchild Semiconductor Corporation.

MicroPak is a trademark of Fairchild Semiconductor Corporation.

Order Package Product Code

Package Description Supplied As

Number Number Top Mark

NC7SZ373P6X MAA06A Z73 6-Lead SC70, EIAJ SC88, 1.25mm Wide 3k Units on Tape and Reel

NC7SZ373L6X MAC06A D4 6-Lead MicroPak, 1.0mm Wide 5k Units on Tape and Reel

www.fairchildsemi.com 2

N

C

7

S

Z

3

7

3

Logic Symbol

IEEE/IEC

Pin Descriptions

Function Table

H = HIGH Logic Level X = Immaterial

L = LOW Logic Level Z = HIGH Impedance

Q

n-1

= Previous state prior to HIGH-to-LOW transition of latch enable

Connection Diagrams

Pin Assignments for SC70

(Top View)

Pin One Orientation Diagram

AAA = Product Code Top Mark - see ordering code

Note: Orientation of Top Mark determines Pin One location. Read the top

product code mark left to right, Pin One is the lower left pin.(see diagram).

Pad Assignments for MicroPak

(Top Thru View)

Pin Names Description

D Data Input

LE Latch Enable Input

OE Output Enable Input

Q Latch Output

Inputs Output

LE D OE Q

H L L L

H H L H

L X L Q

n-1

X X H Z

3 www.fairchildsemi.com

N

C

7

S

Z

3

7

3

Absolute Maximum Ratings(Note 1) Recommended Operating

Conditions (Note 2)

Note 1: The Absolute Maximum Ratings: are those values beyond which

the safety of the device cannot be guaranteed. The device should not be

operated at these limits. The parametric values defined in the Electrical

Characteristics tables are not guaranteed at the absolute maximum ratings.

The Recommended Operating Conditions table will define the conditions

for actual device operation.

Note 2: Unused inputs must be held HIGH or LOW. They may not float.

DC Electrical Characteristics

Supply Voltage (V

CC

) 0.5V to +7.0V

DC Input Voltage (V

IN

) 0.5V to +7.0V

DC Output Voltage (V

OUT

) 0.5V to +7.0V

DC Input Diode Current (I

IK

)

V

IN

< 0V 50 mA

DC Output Diode Current (I

OK

)

V

OUT

< 0V 50 mA

DC Output (I

OUT

) Source/Sink Current 50 mA

DC V

CC

/GND Current (I

CC

/I

GND

) 50 mA

Storage Temperature Range (T

STG

) 65C to +150C

Junction Temperature under Bias (T

J

) 150C

Junction Lead Temperature (T

L

)

(Soldering, 10 seconds) 260C

Power Dissipation (P

D

) @+85C 180 mW

Power Supply

Operating (V

CC

) 1.65V to 5.5V

Data Retention 1.5V to 5.5V

Input Voltage (V

IN

) 0V to 5.5V

Output Voltage (V

OUT

)

Active State 0V to V

CC

3-STATE 0V to 5.5V

Input Rise and Fall Time (t

r

, t

f

)

V

CC

= 1.8V, 2.5V 0.2V 0 to 20 ns/V

V

CC

= 3.3V 0.3V 0 to 10 ns/V

V

CC

= 5.5V 0.5V 0 to 5 ns/V

Operating Temperature (T

A

) 40C to +85C

Thermal Resistance (

JA

) 350 C/W

Symbol Parameter

V

CC

T

A

= +25C T

A

= 40C to +85C

Unit Conditions

(V) Min Typ Max Min Max

V

IH

HIGH Level Control 1.65 to 1.95 0.75 V

CC

0.75 V

CC

V

Input Voltage 2.3 to 5.5 0.7 V

CC

0.7 V

CC

V

IL

LOW Level Control 1.65 to 1.95 0.25 V

CC

0.25 V

CC

V

Input Voltage 2.3 to 5.5 0.3 V

CC

0.3 V

CC

V

OH

HIGH Level Control 1.65 1.55 1.65 1.55

V V

IN

= V

IH

I

OH

= 100 A

Output Voltage 1.8 1.7 1.8 1.7

2.3 2.2 2.3 2.2

3.0 2.9 3.0 2.9

4.5 4.4 4.5 4.4

1.65 1.24 1.52 1.29 I

OH

= 4 mA

2.3 1.9 2.15 1.9 I

OH

= 8 mA

3.0 2.4 2.8 2.4 I

OH

= 16 mA

3.0 2.3 2.68 2.3 I

OH

= 24 mA

4.5 3.8 4.2 3.8 I

OH

= 32 mA

V

OL

LOW Level Control 1.65 0.0 0.08 0.0

V V

IN

= V

IL

I

OL

= 100 A

Output Voltage 1.8 0.0 0.1 0.1

2.3 0.0 0.1 0.1

3.0 0.0 0.1 0.1

4.5 0.0 0.1 0.1

1.65 0.08 0.24 0.24 I

OL

= 4 mA

2.3 0.10 0.3 0.3 I

OL

= 8 mA

3.0 0.15 0.4 0.4 I

OL

= 16 mA

3.0 0.22 0.55 0.55 I

OL

= 24 mA

4.5 0.22 0.55 0.55 I

OL

= 32 mA

I

IN

Input Leakage Current 0 to 5.5 0.1 1.0 A 0 V

IN

5.5V

I

OZ

3-STATE

1.65 to 5.5 0.5 5.0 A

V

IN

= V

IL

or V

IH

Output Leakage 0 V

OUT

5.5V

I

OFF

Power-Off Leakage Current 0.0 1.0 10 A V

IN

or V

OUT

= 5.5V

I

CC

Quiescent Supply Current 1.65 to 5.5 1.0 10 A V

IN

= 5.5V, GND

www.fairchildsemi.com 4

N

C

7

S

Z

3

7

3

AC Electrical Characteristics

Capacitance (Note 3)

Note 3: T

A

= +25C, f = 1 MHz.

Note 4: C

PD

is defined as the value of the internal equivalent capacitance which is derived from dynamic operating current consumption (I

CCD

) at no output

loading and operating at 50% duty cycle. (See Figure 2) C

PD

is related to I

CCD

dynamic operating current by the expression:

I

CCD

= (C

PD

)(V

CC

)(f

IN

) + (I

CC

static).

Symbol Parameter

V

CC

T

A

= +25C T

A

= 40C to +85C

Units Conditions

Figure

Number (V) Min Typ Max Min Max

t

PLH

Propagation Delay 1.65 2.0 9.0 15.0 2.0 16.0

ns

Figures

1, 3

t

PHL

D to Q 1.8 2.0 6.1 10.0 2.0 10.5

2.5 0.2 1.5 3.6 6.5 1.6 6.8 C

L

= 15 pF

3.3 0.3 1.0 2.7 4.6 1.2 5.0 R

D

= 1 M

5.0 0.5 1.0 2.0 3.4 1.0 3.7 S

1

= Open

3.3 0.3 1.5 3.3 5.5 1.5 6.2 C

L

= 50 pF

Figures

1, 3

5.0 0.5 1.0 2.6 4.3 1.3 4.8 R

D

= 500, S

1

= Open

t

PLH

Propagation Delay 1.65 2.0 9.0 1.45 2.0 15.0

ns

Figures

1, 3

t

PHL

LE to Q 1.8 2.0 6.0 9.6 2.0 10.0

2.5 0.2 1.8 3.5 6.1 1.5 6.6 C

L

= 15 pF

3.3 0.3 1.3 2.6 4.4 1.0 4.8 R

D

= 1 M

5.0 0.5 1.0 2.0 3.2 0.8 3.5 S

1

= Open

3.3 0.3 1.5 3.3 5.3 1.5 6.2 C

L

= 50 pF

Figures

1, 4

5.0 0.5 1.3 2.6 4.2 1.2 4.6 R

D

= 500, S

1

= Open

t

PZL

Output Enable Time 1.65 2.0 9.0 13.5 2.0 14.6

ns

Figures

1, 4

t

PZH

1.8 2.0 6.0 9.0 2.0 9.5 C

L

= 50 pF, V

I

= 2x V

CC

2.5 0.2 2.0 3.7 6.0 1.8 6.6 R

U

, R

D

= 500

3.3 0.3 1.5 2.8 5.0 1.4 5.3 S1 = GND for t

PZH

5.0 0.5 1.0 2.2 3.7 1.0 3.9 S1 = V

I

for t

PZL

t

PLZ

Output Disable Time 1.65 2.0 7.7 12.0 2.0 13.0

ns

Figures

1, 4

t

PHZ

1.8 2.0 5.1 8.0 2.0 8.5 C

L

= 50 pF, V

I

= 2x V

CC

2.5 0.2 2.0 3.5 6.0 1.8 6.3 R

U

, R

D

= 500

3.3 0.3 1.5 2.8 4.5 1.4 4.7 S

1

= GND for t

PHZ

5.0 0.5 1.0 2.3 3.7 1.0 3.9 S

1

= V

I

for t

PLZ

t

S

Setup Time, 2.5 0.2 2.0

ns

C

L

= 50 pF

Figures

1, 5

D to LE 3.3 0.3 1.5 R

D

= 500 , S

1

= Open

5.0 0.5 1.5

t

H

Hold Time, 2.5 0.2 1.5

ns

C

L

= 50 pF

Figures

1, 5

D to LE 3.3 0.3 1.5 R

D

= 500 , S

1

= Open

5.0 0.5 1.5

t

W

Pulse Width, LE 2.5 0.2 3.0

ns

Figures

1, 5

3.3 0.3 3.0 C

L

= 50 pF

5.0 0.5 3.0 R

D

= 500 , S

1

= Open

Symbol Parameter Typ Max Units Conditions

C

IN

Input Capacitance 3 pF V

CC

= Open, V

IN

= 0V or V

CC

C

OUT

Output Capacitance 4 pF V

CC

= 3.3V, V

IN

= 0V or V

CC

C

PD

Power Dissipation Capacitance 14

pF

V

CC

= 3.3V

(Note 4) 17 V

CC

= 5.0V

5 www.fairchildsemi.com

N

C

7

S

Z

3

7

3

AC Loading and Waveforms

C

L

includes load and stray capacitance

Input PRR = 1.0 MHz, t

w

= 500 ns

FIGURE 1. AC Test Circuit

D Input = AC Waveform; t

r

= t

f

= 1.8 ns;

D Input PRR = 10 MHz; Duty Cycle = 50%

FIGURE 2. I

CCD

Test Circuit

FIGURE 3. AC Waveforms

FIGURE 4. AC Waveforms FIGURE 5. AC Waveforms

www.fairchildsemi.com 6

N

C

7

S

Z

3

7

3

Tape and Reel Specification

TAPE FORMAT for SC70

TAPE DIMENSIONS inches (millimeters)

Package Tape Number Cavity Cover Tape

Designator Section Cavities Status Status

Leader (Start End) 125 (typ) Empty Sealed

P6X Carrier 3000 Filled Sealed

Trailer (Hub End) 75 (typ) Empty Sealed

Package Tape Size DIM A DIM B DIM F DIM K

o

DIM P1 DIM W

SC70-6 8 mm

0.093 0.096 0.138 0.004 0.053 0.004 0.157 0.315 0.004

(2.35) (2.45) (3.5 0.10) (1.35 0.10) (4) (8 0.1)

7 www.fairchildsemi.com

N

C

7

S

Z

3

7

3

Tape and Reel Specification (Continued)

TAPE FORMAT for MicroPak

REEL DIMENSIONS inches (millimeters)

Package Tape Number Cavity Cover Tape

Designator Section Cavities Status Status

Leader (Start End) 125 (typ) Empty Sealed

L6X Carrier 3000 Filled Sealed

Trailer (Hub End) 75 (typ) Empty Sealed

Tape

Size

A B C D N W1 W2 W3

8 mm

7.0 0.059 0.512 0.795 2.165 0.331 + 0.059/0.000 0.567 W1 + 0.078/0.039

(177.8) (1.50) (13.00) (20.20) (55.00) (8.40 + 1.50/0.00) (14.40) (W1 + 2.00/1.00)

www.fairchildsemi.com 8

N

C

7

S

Z

3

7

3

Physical Dimensions inches (millimeters) unless otherwise noted

6-Lead SC70, EIAJ SC88, 1.25mm Wide

Package Number MAA06A

9 www.fairchildsemi.com

N

C

7

S

Z

3

7

3

T

i

n

y

L

o

g

i

c

U

H

S

D

-

T

y

p

e

L

a

t

c

h

w

i

t

h

3

-

S

T

A

T

E

O

u

t

p

u

t

Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

6-Lead MicroPak, 1.0mm Wide

Package Number MAC06A

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and

Fairchild reserves the right at any time without notice to change said circuitry and specifications.

LIFE SUPPORT POLICY

FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD

SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or systems

which, (a) are intended for surgical implant into the

body, or (b) support or sustain life, and (c) whose failure

to perform when properly used in accordance with

instructions for use provided in the labeling, can be rea-

sonably expected to result in a significant injury to the

user.

2. A critical component in any component of a life support

device or system whose failure to perform can be rea-

sonably expected to cause the failure of the life support

device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

Você também pode gostar

- Redseer Consulting Report On Vernacular LanguagesDocumento36 páginasRedseer Consulting Report On Vernacular LanguagesMalavika SivagurunathanAinda não há avaliações

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsAinda não há avaliações

- Features: Single Bilateral SwitchDocumento15 páginasFeatures: Single Bilateral SwitchGaryTechAinda não há avaliações

- 74LVC08A: Low Voltage Cmos Quad 2-Input and Gate High PerformanceDocumento11 páginas74LVC08A: Low Voltage Cmos Quad 2-Input and Gate High PerformanceFernando QueirozAinda não há avaliações

- Single Bilateral Switch: Order CodesDocumento11 páginasSingle Bilateral Switch: Order CodesGaryTechAinda não há avaliações

- 7Z14Documento7 páginas7Z14André Frota PaivaAinda não há avaliações

- 74LCX125 Low Voltage Quad Buffer With 5V Tolerant Inputs and OutputsDocumento13 páginas74LCX125 Low Voltage Quad Buffer With 5V Tolerant Inputs and Outputsfenixtec1Ainda não há avaliações

- 7Z08Documento7 páginas7Z08André Frota PaivaAinda não há avaliações

- MC74ACT564 Octal D Type Flip Flop With 3 State Outputs: PDIP 20 N Suffix CASE 738Documento8 páginasMC74ACT564 Octal D Type Flip Flop With 3 State Outputs: PDIP 20 N Suffix CASE 738greentea601Ainda não há avaliações

- MC74HC541A Octal 3-State Non-Inverting Buffer/Line Driver/ Line ReceiverDocumento8 páginasMC74HC541A Octal 3-State Non-Inverting Buffer/Line Driver/ Line ReceivernandobnuAinda não há avaliações

- Octal 3-State Noninverting D Flip-Flop: KK74HC574ADocumento6 páginasOctal 3-State Noninverting D Flip-Flop: KK74HC574Ajksb100Ainda não há avaliações

- 74FST3251 8:1 Multiplexer/ Demultiplexer Bus Switch: SOIC 16 D Suffix CASE 751BDocumento7 páginas74FST3251 8:1 Multiplexer/ Demultiplexer Bus Switch: SOIC 16 D Suffix CASE 751BRishabh PariharAinda não há avaliações

- 74LCX374 Low Voltage Octal D-Type Flip-Flop With 5V Tolerant Inputs and OutputsDocumento11 páginas74LCX374 Low Voltage Octal D-Type Flip-Flop With 5V Tolerant Inputs and OutputsRicardo MercadoAinda não há avaliações

- MC74VHC1GT125 Noninverting Buffer / CMOS Logic Level ShifterDocumento6 páginasMC74VHC1GT125 Noninverting Buffer / CMOS Logic Level ShifterCh SamirAinda não há avaliações

- DatasheetDocumento8 páginasDatasheetMaizatul Hanisah RoziAinda não há avaliações

- MM74HC245A Octal 3-STATE Transceiver: General DescriptionDocumento7 páginasMM74HC245A Octal 3-STATE Transceiver: General DescriptionMubarak CeAinda não há avaliações

- 74LVC08A: 1. General DescriptionDocumento15 páginas74LVC08A: 1. General DescriptionWalterAinda não há avaliações

- DatasheetDocumento5 páginasDatasheetIonut SimaAinda não há avaliações

- Low Voltage Cmos Dual 2 To 4 Decoder/Demultiplexer: Table 1: Order CodesDocumento13 páginasLow Voltage Cmos Dual 2 To 4 Decoder/Demultiplexer: Table 1: Order CodesMohammad SoltanmohammadiAinda não há avaliações

- 74HC374Documento13 páginas74HC374jnax101Ainda não há avaliações

- 74LVC1G11: 1. General DescriptionDocumento14 páginas74LVC1G11: 1. General DescriptionnevdullAinda não há avaliações

- 74HC373Documento13 páginas74HC373jnax101Ainda não há avaliações

- 74LVC1G04: 1. General DescriptionDocumento20 páginas74LVC1G04: 1. General DescriptionnevdullAinda não há avaliações

- 74AHC1G02 74AHCT1G02: 1. General DescriptionDocumento11 páginas74AHC1G02 74AHCT1G02: 1. General DescriptionMarcu Andrei StefanAinda não há avaliações

- Nc7Sbu3157 - Fsau3157 Tinylogic Low Voltage Uhs SPDT Analog Switch With 2V Undershoot ProtectionDocumento11 páginasNc7Sbu3157 - Fsau3157 Tinylogic Low Voltage Uhs SPDT Analog Switch With 2V Undershoot ProtectionAgus TabraniAinda não há avaliações

- ADC0820 NationalDocumento23 páginasADC0820 NationalePotyAinda não há avaliações

- Data SheetDocumento6 páginasData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣAinda não há avaliações

- Octal 3-State Noninverting Transparent Latch: SL74HC573Documento5 páginasOctal 3-State Noninverting Transparent Latch: SL74HC573Prayu GarnurmAinda não há avaliações

- Quad 2-Input AND Gate: KK74HC08ADocumento5 páginasQuad 2-Input AND Gate: KK74HC08Acatsoithahuong84Ainda não há avaliações

- 74HC10-Q100 74HCT10-Q100: 1. General DescriptionDocumento13 páginas74HC10-Q100 74HCT10-Q100: 1. General DescriptionNelson RodriguezAinda não há avaliações

- Octal Bus Buffer With 3 State Outputs (Non Inverted) : M B Order CodesDocumento8 páginasOctal Bus Buffer With 3 State Outputs (Non Inverted) : M B Order CodesStevenAinda não há avaliações

- IC-ON-LINE - CN In74hc164a 4331941Documento6 páginasIC-ON-LINE - CN In74hc164a 4331941enriquevagoAinda não há avaliações

- Synchronous Presettable 4-Bit Counter: M B Order CodesDocumento12 páginasSynchronous Presettable 4-Bit Counter: M B Order CodesMarimuthu RajAinda não há avaliações

- 74HC138Documento10 páginas74HC138jnax101Ainda não há avaliações

- CBT3257AD I-St Mixer Elecraft 3Documento16 páginasCBT3257AD I-St Mixer Elecraft 3verd leonardAinda não há avaliações

- 74HC573Documento21 páginas74HC573ric_napigkitAinda não há avaliações

- 74HC27Documento9 páginas74HC27jnax101Ainda não há avaliações

- 74AHC1G32 74AHCT1G32: 1. General DescriptionDocumento12 páginas74AHC1G32 74AHCT1G32: 1. General DescriptionnevdullAinda não há avaliações

- 74AHC1G86 74AHCT1G86: 1. General DescriptionDocumento12 páginas74AHC1G86 74AHCT1G86: 1. General DescriptionKushalSwamyAinda não há avaliações

- 74HC08 74HCT08: 1. General DescriptionDocumento16 páginas74HC08 74HCT08: 1. General DescriptionCesar VilledaAinda não há avaliações

- MC34151 DDocumento12 páginasMC34151 DMladen MuskinjaAinda não há avaliações

- C.I 74HC175Documento7 páginasC.I 74HC175DOMINGOS ALADIRAinda não há avaliações

- 4-Channel Secondary Monitoring IC With 4-Channel OCP and An Additional OTPDocumento11 páginas4-Channel Secondary Monitoring IC With 4-Channel OCP and An Additional OTPDanniel Martin0% (1)

- 74HC373Documento13 páginas74HC373hugodjacobAinda não há avaliações

- General Description: Quad Bilateral SwitchDocumento23 páginasGeneral Description: Quad Bilateral Switchtotal4321Ainda não há avaliações

- 74LS374Documento8 páginas74LS374Bechtel LanutanAinda não há avaliações

- Elevador VoltajeDocumento10 páginasElevador VoltajeFernando AugustoAinda não há avaliações

- ST 232Documento11 páginasST 232Negru P. PlantatieAinda não há avaliações

- 74HC14Documento9 páginas74HC14jnax101Ainda não há avaliações

- MCP 3201Documento28 páginasMCP 3201Nacer MezghicheAinda não há avaliações

- 74HC151Documento11 páginas74HC151jnax101Ainda não há avaliações

- Datasheet 7400Documento9 páginasDatasheet 7400gab50Ainda não há avaliações

- 74HC00Documento9 páginas74HC00jnax101Ainda não há avaliações

- Datasheet 74HC32Documento8 páginasDatasheet 74HC32Lưu Chung KiênAinda não há avaliações

- Tda7266sa PDFDocumento11 páginasTda7266sa PDFerju10Ainda não há avaliações

- 74cx16839 U18 PDFDocumento7 páginas74cx16839 U18 PDFMarcos AurélioAinda não há avaliações

- 54ABT240 Octal Buffer/Line Driver With TRI-STATE Outputs: General DescriptionDocumento8 páginas54ABT240 Octal Buffer/Line Driver With TRI-STATE Outputs: General Descriptionmeroka2000Ainda não há avaliações

- mc14518bcp en PDFDocumento8 páginasmc14518bcp en PDFdellcoAinda não há avaliações

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Ainda não há avaliações

- 110 Waveform Generator Projects for the Home ConstructorNo Everand110 Waveform Generator Projects for the Home ConstructorNota: 4 de 5 estrelas4/5 (1)

- IDT54/74FCT373T/AT/CT Fast Cmos Octal Transparent Latch: Features: DescriptionDocumento7 páginasIDT54/74FCT373T/AT/CT Fast Cmos Octal Transparent Latch: Features: Descriptiongreentea601Ainda não há avaliações

- MC10E155, MC100E155 5VECL 6 Bit 2:1 Mux Latch: DescriptionDocumento8 páginasMC10E155, MC100E155 5VECL 6 Bit 2:1 Mux Latch: Descriptiongreentea601Ainda não há avaliações

- MC14099B 8-Bit Addressable Latches: Marking DiagramsDocumento8 páginasMC14099B 8-Bit Addressable Latches: Marking Diagramsgreentea601Ainda não há avaliações

- MC74ACT564 Octal D Type Flip Flop With 3 State Outputs: PDIP 20 N Suffix CASE 738Documento8 páginasMC74ACT564 Octal D Type Flip Flop With 3 State Outputs: PDIP 20 N Suffix CASE 738greentea601Ainda não há avaliações

- MC14042B Quad Transparent Latch: Marking DiagramsDocumento7 páginasMC14042B Quad Transparent Latch: Marking Diagramsgreentea601Ainda não há avaliações

- NL17SG373 Low-Power D-Type Transparent Latch With 3-State OutputDocumento10 páginasNL17SG373 Low-Power D-Type Transparent Latch With 3-State Outputgreentea601Ainda não há avaliações

- 3-BIT 4:1 Mux-Latch: Features DescriptionDocumento4 páginas3-BIT 4:1 Mux-Latch: Features Descriptiongreentea601Ainda não há avaliações

- Prices Are Subject To Change Without Prior Notice.: Mediapro TechnologyDocumento25 páginasPrices Are Subject To Change Without Prior Notice.: Mediapro Technologygreentea601100% (1)

- Laser Distributor Pte LTD: 1 Rochor Canal Road #05-58, Sim Lim Square Tel:63362806, 63362510, Fax: 63397008Documento9 páginasLaser Distributor Pte LTD: 1 Rochor Canal Road #05-58, Sim Lim Square Tel:63362806, 63362510, Fax: 63397008greentea601Ainda não há avaliações

- International Pte LTD: Asus R9 290 4GB GDDR5Documento6 páginasInternational Pte LTD: Asus R9 290 4GB GDDR5greentea601Ainda não há avaliações

- SAF1562Documento97 páginasSAF1562greentea601Ainda não há avaliações

- 74AHC259 74AHCT259: 1. General DescriptionDocumento17 páginas74AHC259 74AHCT259: 1. General Descriptiongreentea601Ainda não há avaliações

- Cymax Zbox Ci320 Nano PC CYMAX I3 NUC-D34010WYK Compact PC: PRO PRODocumento2 páginasCymax Zbox Ci320 Nano PC CYMAX I3 NUC-D34010WYK Compact PC: PRO PROgreentea601Ainda não há avaliações

- IPC 4101 B Slash Sheet MatrixDocumento4 páginasIPC 4101 B Slash Sheet Matrixgreentea601Ainda não há avaliações

- ADC Driver Selection Guide FinalDocumento2 páginasADC Driver Selection Guide Finalgreentea601Ainda não há avaliações

- Flash Memory TestingDocumento75 páginasFlash Memory Testinggreentea601Ainda não há avaliações

- 2468 V 33 StackupDocumento1 página2468 V 33 Stackupgreentea601Ainda não há avaliações

- Boiler Safety ProgramDocumento8 páginasBoiler Safety ProgramHussain KhanAinda não há avaliações

- Lorentz Ps4000 Manual enDocumento9 páginasLorentz Ps4000 Manual encorazto100% (1)

- Thermal PrinterDocumento15 páginasThermal Printergadacz111Ainda não há avaliações

- CFRD 05 - BayardoDocumento23 páginasCFRD 05 - BayardodiegofernandodiazsepAinda não há avaliações

- Instrument Transformer Fuses Types WBP and BRT: Catalogue B12/06/01/EDocumento8 páginasInstrument Transformer Fuses Types WBP and BRT: Catalogue B12/06/01/EivanramljakAinda não há avaliações

- Review On Application of Drone in Agriculture Field: XXX-X-XXXX-XXXX-X/XX/$XX.00 ©20XX IEEEDocumento6 páginasReview On Application of Drone in Agriculture Field: XXX-X-XXXX-XXXX-X/XX/$XX.00 ©20XX IEEESagar PatilAinda não há avaliações

- Klauke - Bi-Metal Lugs & ConnectorsDocumento6 páginasKlauke - Bi-Metal Lugs & ConnectorsBiplab PaulAinda não há avaliações

- Tak Company Profile - 1Documento28 páginasTak Company Profile - 1zacky100% (1)

- Zener DiodeDocumento3 páginasZener DiodeAde MurtalaAinda não há avaliações

- Harsh's ResumeDocumento1 páginaHarsh's ResumeNavin J PomsonAinda não há avaliações

- Lab 31Documento8 páginasLab 31net fliAinda não há avaliações

- Gogostemcells StudentpagesDocumento2 páginasGogostemcells Studentpagesapi-356824125Ainda não há avaliações

- KNS2163 Week1Documento32 páginasKNS2163 Week1Nurul QurratuAinda não há avaliações

- A2 Accu-Flo Clamped Metal Pump: Engineering Operation MaintenanceDocumento28 páginasA2 Accu-Flo Clamped Metal Pump: Engineering Operation MaintenanceThanh Nghị BùiAinda não há avaliações

- Datalogic Gryphon GM4100 User GuideDocumento52 páginasDatalogic Gryphon GM4100 User Guidebgrabbe92540% (1)

- 1 5 1Documento5 páginas1 5 1daemsalAinda não há avaliações

- Inside A Gamma SterilizerDocumento5 páginasInside A Gamma SterilizerckanesanAinda não há avaliações

- BME Joining ProcessesDocumento11 páginasBME Joining ProcessesalysonmicheaalaAinda não há avaliações

- Technical Catalogue eSV-SpecialVersion 50-60HzDocumento264 páginasTechnical Catalogue eSV-SpecialVersion 50-60HzRichard Marco Antonio Obando LopezAinda não há avaliações

- AcetophenoneDocumento1 páginaAcetophenoneDinda Melissa ArdiAinda não há avaliações

- MetamterialsDocumento3 páginasMetamterialsdhruba88Ainda não há avaliações

- 2015 USMW HD WebDocumento47 páginas2015 USMW HD WebAlexis Sanchez100% (1)

- LAPORAN PRAKTIK KERJA LAPANGAN - Id.enDocumento25 páginasLAPORAN PRAKTIK KERJA LAPANGAN - Id.enAhmad JupriAinda não há avaliações

- Large Volume PoursDocumento7 páginasLarge Volume PoursgordonAinda não há avaliações

- Gujarat Technological University: A Project Report On:-Automatic Water Purification SystemDocumento11 páginasGujarat Technological University: A Project Report On:-Automatic Water Purification SystemJay KakadiyaAinda não há avaliações

- Lect-6 - Economics of Chemical PlantsDocumento36 páginasLect-6 - Economics of Chemical Plantsmaged1998Ainda não há avaliações

- Movi NandDocumento2 páginasMovi NandAinda não há avaliações

- Sub Test Mole Concept PDFDocumento7 páginasSub Test Mole Concept PDFVIKAS GARGAinda não há avaliações

- DC Coding and Decoding With Convolutional CodesDocumento28 páginasDC Coding and Decoding With Convolutional CodesARAVINDAinda não há avaliações