Escolar Documentos

Profissional Documentos

Cultura Documentos

Eletrônica IV - Amplificadores de Potência e Modulação AM

Enviado por

Arsenyo Boaventura DollarTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Eletrônica IV - Amplificadores de Potência e Modulação AM

Enviado por

Arsenyo Boaventura DollarDireitos autorais:

Formatos disponíveis

Eletrnica IV

Fernando Antnio Pinto Barqui

Departamento de Eletrnica

Escola Politcnica

Universidade Federal do Rio de Janeiro

Material no disponvel para publicao

2

ndice

Introduo .............................................................................................................................................. 6

Amplificadores de Potncia .................................................................................................................. 7

1.1 Amplificador Classe A ............................................................................................................... 7

1.1.1 Eficincia ............................................................................................................................. 8

1.2 Amplificador Classe B ............................................................................................................. 10

1.2.1 Eficincia ........................................................................................................................... 11

1.2.2 Distoro Harmnica ......................................................................................................... 12

1.3 Amplificador Classe AB .......................................................................................................... 13

1.4 Amplificador Classe C ............................................................................................................. 13

1.5 Amplificador Push-Pull ............................................................................................................ 14

1.5.1 Distoro de Crossover ...................................................................................................... 14

1.6 Dissipadores de Calor ............................................................................................................... 15

1.6.1 Resistncia Trmica ........................................................................................................... 15

1.6.2 Regio de Trabalho do Transistor em Funo da Temperatura ......................................... 16

1.6.3 Segundo Breakdown .......................................................................................................... 17

1.7 Circuitos Para Polarizao Classe AB ...................................................................................... 17

1.7.1 Polarizao Com Diodos ................................................................................................... 17

1.7.2 Multiplicador de V

BE

......................................................................................................... 18

1.8 Exemplo de Projeto .................................................................................................................. 20

Amplificador Sintonizado ................................................................................................................... 26

2.1 Circuito RLC de Segunda Ordem ............................................................................................ 26

2.2 Amplificadores com Sintonia Sncrona .................................................................................... 28

2.3 Amplificador de Banda Plana................................................................................................... 30

2.4 Fator de Qualidade ................................................................................................................... 30

2.4.1 Fator de Qualidade dos Indutores ...................................................................................... 30

2.4.2 Fator de Qualidade dos Capacitores .................................................................................. 31

2.5 Indutores Acoplados ................................................................................................................. 32

2.5.1 Modelos Equivalentes Para Indutores Acoplados .............................................................. 32

2.5.2 Autotransformador ............................................................................................................. 33

2.5.3 Mltiplos Indutores Acoplados .......................................................................................... 33

2.5.4 Relao de Impedncias no Transformador ....................................................................... 34

Amplificadores Classe C ..................................................................................................................... 39

3.1 Eficincia do Amplificador em Classe C ................................................................................. 40

Redes de Casamento de Impedncias ................................................................................................ 43

4.1 Transformaes de Impedncias .............................................................................................. 43

4.1.1 Transformao Indutor Srie-Paralelo Com Resistor ........................................................ 43

Material no disponvel para publicao

3

4.1.2 Transformao Capacitor Paralelo-Srie com Resistor ..................................................... 45

4.2 Rede Com T de Capacitores e Indutor ..................................................................................... 46

4.3 Rede em t ................................................................................................................................. 48

4.4 Rede em t Modificada ............................................................................................................. 48

4.5 Resumo das Redes de Casamento de Impedncias .................................................................. 49

4.6 Redes de Casamento com Zeros de Transmisso ..................................................................... 51

4.6.1 Zeros de Transmisso com circuito LC Paralelo ............................................................... 51

4.6.2 Zeros de Transmisso com Circuito LC Srie ................................................................... 51

4.7 Exemplos .................................................................................................................................. 52

4.7.1 Casamento de Impedncias de Uma Antena ...................................................................... 52

4.7.2 Eliminao do 2 Harmnico, com Zero de Transmisso ................................................. 53

4.8 Impedncia para Grandes Sinais .............................................................................................. 54

4.9 Parmetros Y ............................................................................................................................ 56

4.10 Exemplo de Projeto .............................................................................................................. 57

Osciladores Senoidais .......................................................................................................................... 61

5.1 Osciladores LC ......................................................................................................................... 62

5.1.1 Oscilador Colpitts em Base Comum .................................................................................. 62

5.1.2 Oscilador Colpitts em Emissor Comum ............................................................................ 65

5.1.3 Oscilador Hartley em Base Comum .................................................................................. 66

5.1.4 Oscilador Hartley em Emissor Comum ............................................................................. 67

5.1.5 Ajuste da Frequncia de Oscilao .................................................................................... 67

5.2 Exemplo de Projeto .................................................................................................................. 68

5.3 Oscilador a Cristal .................................................................................................................... 70

5.3.1 Cristal Oscilador ................................................................................................................ 70

5.3.2 Oscilador Colpitts a Cristal ................................................................................................ 72

5.3.3 Exemplo de Projeto ............................................................................................................ 74

5.3.4 Oscilador Colpitts com Cristal em Ressonncia Srie ....................................................... 76

5.3.5 Oscilador Pierce com Porta Lgica ................................................................................... 76

Modulao de Amplitude .................................................................................................................... 79

6.1 Modulador AM de Alto Nvel .................................................................................................. 81

6.1.1 Consideraes de Projeto ................................................................................................... 83

6.2 Modulador AM de Alto Nvel com Amplificador Classe C ..................................................... 86

6.3 Modulador Chopper ................................................................................................................. 87

6.3.1 Exemplo de Circuito .......................................................................................................... 88

6.4 Modulao AM por Dispositivo No Linear ............................................................................ 90

6.4.1 Implementao com JFET ................................................................................................. 91

6.5 Multiplicador Analgico - Clula de Gilbert ........................................................................... 92

Demodulao AM ................................................................................................................................ 96

7.1 Demodulador por Deteco de Pico de Envoltria .................................................................. 96

Material no disponvel para publicao

4

7.2 Demodulador AM por Deteco de Valor Mdio de Envoltria.............................................. 98

7.3 Detector Sncrono ................................................................................................................... 100

Modulao de Frequncia e Fase ..................................................................................................... 102

8.1 Modulao de Fase (PM) ....................................................................................................... 102

8.2 Modulao de Frequncia (FM) ............................................................................................. 102

8.2.1 Modulador de Armstrong................................................................................................. 105

8.2.2 Modulador com VCO (Voltage-Controlled-Oscillator) ................................................... 106

8.2.3 Modulador de FM com Frequncia Estabilizada por Cristal ........................................... 108

8.3 Demodulao de FM .............................................................................................................. 110

8.3.1 Demodulador no Domnio da Frequncia ........................................................................ 111

8.3.2 Demodulador com Detector de Quadratura ..................................................................... 112

8.4 Interferncia no Sinal de FM .................................................................................................. 115

8.4.1 Circuito de Pr-nfase ..................................................................................................... 116

8.4.2 Circuito de De-nfase ...................................................................................................... 116

Fontes Chaveadas .............................................................................................................................. 118

9.1 Conversor Boost ..................................................................................................................... 118

9.2 Conversor Buck ...................................................................................................................... 123

9.3 Conversor Buck-Boost ........................................................................................................... 126

9.4 Conversor Flyback ................................................................................................................. 129

9.5 Conversor Forward ................................................................................................................. 134

9.6 Dimensionamento do Ncleo ................................................................................................. 137

9.7 Fonte de Tenso V

CC

............................................................................................................... 138

Conversores Digital-Analgico e Analgico-Digital ....................................................................... 140

10.1 Conversor Digital-Analgico com Rede R-2R .................................................................. 140

10.2 Circuito Sample-Hold ........................................................................................................ 141

10.3 Conversor Analgico-Digital Com Rampa Digital ............................................................ 142

10.4 Conversor Analgico-Digital Por Aproximaes Sucessivas ............................................ 143

10.5 ADC de Rampa Simples .................................................................................................... 144

10.6 ADC de Rampa Dupla ....................................................................................................... 145

10.7 Conversor Flash ................................................................................................................. 146

10.8 Conversor EA ..................................................................................................................... 148

10.8.1 Implementao do Conversor EA a Capacitor Chaveado ................................................ 150

Phase Locked Loop (PLL) ................................................................................................................ 153

11.1 Funo de Transferncia do PLL ....................................................................................... 154

11.2 Loop-Filter ......................................................................................................................... 154

11.3 Erro em Regime Permanente para um Degrau de Fase ...................................................... 156

11.4 Erro em Regime Permanente para um Degrau de Frequncia ........................................... 156

11.5 VCO com Offset ................................................................................................................ 157

11.6 Parmetros Caractersticos do PLL .................................................................................... 157

Material no disponvel para publicao

5

11.6.1 Hold-in Range .................................................................................................................. 157

11.6.2 Lock-in Range ................................................................................................................. 158

11.6.3 Pull-in Range ................................................................................................................... 159

11.7 Aplicaes do PLL ............................................................................................................. 159

11.7.1 Demodulao de Frequncia ............................................................................................ 159

11.7.2 Modulador de Frequncia e Fase ..................................................................................... 161

11.7.3 Modulador FM com Multiplicador de Frequncia ........................................................... 163

11.7.4 Sintetizador de Frequncias ............................................................................................. 163

11.7.5 Sintetizador de Frequncias com Prescaler ...................................................................... 164

11.7.6 Sintetizador de Frequncias com Prescaler de Mdulo P+Q ........................................... 164

11.8 Detectores de Fase ............................................................................................................. 166

11.8.1 Detector de Fase por Multiplicao Analgica ................................................................ 166

11.8.2 Detector de Fase com Ou-Exclusivo ............................................................................... 167

11.8.3 Detector de Fase Sequencial com Flip-Flop .................................................................... 168

Material no disponvel para publicao

6

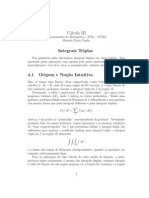

Introduo

Esta apostila abrange a ementa da disciplina Eletrnica IV, ministrada no Departamento de

Eletrnica da Universidade Federal do Rio de Janeiro.

Quando iniciei minhas atividades como professor da cadeira Eletrnica IV, tive muita dificuldade

em selecionar um nmero reduzido de material bibliogrfico, necessrio ao acompanhamento do

curso. Isto se deve grande diversidade dos assuntos abordados.

Tendo acumulado a experincia de alguns anos no exerccio desta disciplina, senti-me motivado a

produzir este material, e fornecer aos alunos uma fonte de consulta concisa, mas ao mesmo tempo

detalhada em muitos aspectos, e de fcil aquisio.

Neste texto so abordados aspectos tericos e prticos para o projeto de amplificadores de potncia

para udio e radio frequncia; moduladores e demoduladores de amplitude, fase e frequncia; fontes

chaveadas; conversores analgico-digitais; circuitos com PLL.

Material no disponvel para publicao

7

Captulo 1

Amplificadores de Potncia

Os amplificadores tm como objetivo alterar o nvel de um sinal. Por exemplo, consideremos um

amplificador de udio que recebe um sinal tnue de um microfone, eleva seu nvel por um fator A, e

aplica-o a um alto-falante. Alm do ganho A, a resistncia da carga (alto-falante) uma componente

que deve ser cuidadosamente considerada no projeto do amplificador.

Muitos parmetros foram definidos para caracterizao dos amplificadores, cujos principais so: o

ganho de tenso (ou corrente) A; a frequncia de corte; a potncia de sada, o slew-rate; a distoro

harmnica total (THD); a distoro por intermodulao; a eficincia.

Um parmetro muito importante a eficincia q, que relaciona a potncia mdia

CC

V

P que a fonte de

alimentao d ao circuito e a potncia mdia

L

P que o amplificador d carga, conforme a equao

1.1.

CC

L

V

P

P

q = (1.1)

A eficincia nos mostra quanta potncia

A

P foi desperdiada no amplificador, normalmente sob

forma de calor, conforme a equao 1.2.

1

1

CC

A V L L

P P P P

q

| |

= =

|

\ .

(1.2)

Portanto, um amplificador com potncia de sada de 100W e eficincia de 50%, desperdia

100

A

P W = sob forma de calor, obrigando a fonte ser capaz de gerar 200W. Quanto maior for a

eficincia melhor ser o amplificador, sendo o limite fsico 1 q = .

Muitas configuraes foram desenvolvidas para implementao dos amplificadores, mais

especificamente para o estgio de sada, das quais estudaremos as principais que so as classes A, B,

AB e C. A definio de cada classe depende do tipo de polarizao do estgio de sada, e para cada

uma temos uma caracterstica prpria de eficincia.

1.1 Amplificador Classe A

Tomemos como exemplo o circuito da Fig. 1.1, onde ( )

in

v t uma fonte senoidal. A classe de

operao depende da regio de trabalho do transistor.

Material no disponvel para publicao

8

Q1

Vcc

Vo(t)

RL

0

Vin(t)

Ic(t)

Vbq

Fig. 1.1: Amplificador de tenso.

Quando o transistor est sempre na regio ativa, o amplificador opera em classe A, e a corrente de

coletor comporta-se como na Fig. 1.2.

Fig. 1.2: Operao em classe A.

1.1.1 Eficincia

Sabemos que

( ) ( ) ( ) sin

o CC C L CC Cq L m L

V t V I t R V I R I t R e = =

e podemos considerar que a tenso de sada , de forma geral, dada por

( ) ( ) ( ) ( ) sin

o CC C L Cq o Cq m

V t V I t R V v t V V t e = = + = (1.3)

A corrente que circula pela fonte de tenso a mesma do coletor, e pode ser calculada por

( )

( ) ( ) sin

CC

CC Cq m CC o

V

L L

V V V t V V t

I t

R R

e +

= = (1.4)

e a potncia instantnea entregue pela fonte

( ) ( )

( )

2

sin

CC CC

CC CC Cq CC m

V V CC

L

V V V V V t

P t I t V

R

e +

= = (1.5)

Podemos calcular a potncia mdia

CC

V

P pelo valor mdio da equao 1.5, ou seja:

( )

2 2

0

sin

1

CC

T

CC CC Cq CC m CC CC Cq

V

L L

V V V V V t V V V

P dt

T R R

e +

= =

}

(1.6)

A potncia instantnea entregue carga R

L

dada por

Material no disponvel para publicao

9

( )

( ) ( ) ( ) ( )

2

2 2

2

CC o CC CC o o

L

L L

V V t V V V t V t

P t

R R

+

= =

e cujo valor mdio

( ) ( )

2 2 2 2 2

0

2 2 2 1

T

CC CC Cq Cq m CC CC o o

L

L L

V V V V V V V V t V t

P dt

T R R

+ + +

= =

}

(1.7)

Da equao 1.7 notamos que a parcela de potncia relacionada ao sinal de entrada (por exemplo o

som)

2

2

m L

V R e portanto, podemos considerar que efetivamente a potncia mdia til na carga

2

2

m

L

L

V

P

R

= (1.8)

Consideremos tambm que o circuito opera com excurso de sada simtrica e mxima amplitude

de sinal. Desta forma, temos que a tenso mxima de sada

CC

V e a mnima

CEsat

V , ou seja:

( )

( )

max

min

CC o Cq m

CEsat o Cq m

V V t V V

V V t V V

= = +

= =

(1.9)

Pela soluo do sistema de equaes 1.9, obtemos

2

2

CC CEsat

Cq

CC CEsat

m

V V

V

V V

V

+

=

(1.10)

Substituindo 1.10 em 1.6 e 1.8, obtemos

2

2 2

2

2

8

CC

CC CC CEsat

V

L

CC CC CEsat CEsat

L

L

V V V

P

R

V V V V

P

R

=

(1.11)

Finalmente, temos para a eficincia mxima terica do amplificador classe A a expresso

( )

4

CC CEsat

CC

V V

V

q

= (1.12)

Quando

CEsat

V suficientemente pequeno para ser desprezado, a equao 1.12 reduz-se a 1 4 q = .

Isto significa que somente 25% da potncia entregue pela fonte considerada til. Se fossemos

projetar um amplificador de udio para 100W de sada, desperdiaramos 300W sob forma de calor no

transistor.

Uma forma alternativa de implementao de um amplificador classe A com eficincia superior

pode ser vista na Fig. 1.3. O indutor L

1

e o capacitor C

1

so suficientemente elevados, para que nas

frequncias de trabalho, L

1

seja um circuito aberto e C

1

um curto-circuito. A tenso DC armazenada no

capacitor

CC

V , pois o indutor no oferece resistncia passagem da corrente contnua. Temos ento

que a tenso de sada no coletor ( )

C

V t est deslocada de V

CC

em relao a ( )

o

V t . Assumindo que

CEsat

V seja zero, ( )

C

V t pode ser no mnimo zero, obrigando uma excurso de sinal negativa igual a

V

CC

. Portanto, para excurso de sinal simtrica, devemos ter

( ) ( ) ( ) sin sin

o m CC

v t V t V t e e = = (1.13)

Com o mximo de tenso na sada, o transistor est cortado e toda corrente que passa pelo indutor

direcionada para a carga. Sabemos que o indutor, neste caso, funciona como fonte de corrente, e sua

corrente a prpria I

Cq

. Portanto temos que

Material no disponvel para publicao

10

CC

Cq

L

V

I

R

= (1.14)

Utilizando as equaes 1.13 e 1.14, podemos calcular as potncias mdias entregues pela fonte e a

consumida pela carga, ou seja:

2

CC

CC

V CC Cq

L

V

P V I

R

= = (1.15)

e

2

2

CC

L

L

V

P

R

= (1.16)

A eficincia obtida das equaes 1.15 e 1.16, ou seja:

0.5

CC

L

V

P

P

q = = (1.17)

Este valor consideravelmente melhor que o anterior, mas a implementao do indutor no

prtica. Este circuito dificilmente usado para grandes potncias de sada.

Q1

0

Vcc

C1

Vbq

RL

L1

Vc(t)

Vin(t)

+

_ Vcc

Ic(t)

Vo(t)

Fig. 1.3: Amplificador classe A com indutor.

Um fato interessante que podemos observar que a tenso no coletor ( )

C

V t pode ser mais elevada

que a da fonte. Isto possvel pois o indutor atua como fonte de corrente, e acumula energia.

1.2 Amplificador Classe B

Considere o seguidor de emissor da Fig. 1.4. O transistor no possui polarizao DC, estando a

base conectada diretamente fonte sinal. Somente quando ( )

in

v t exceder a tenso de juno V

BE

,

haver corrente de coletor e tenso de sada, conforme a Fig. 1.5.

Ic(t)

Vo(t)

Vin(t)

0

Q1

RL

Vcc

Fig. 1.4: Amplificador classe B.

Material no disponvel para publicao

11

Fig. 1.5: Corrente e tenso na carga do amplificador classe B.

Podemos observar que somente o ciclo positivo do sinal de entrada aplicado carga, e tambm

com desconto de V

BE

. A queda de V

BE

pode ser compensada com o circuito da Fig. 1.6.

Q1

RL

Vo(t)

Ic(t)

Vcc

0

Vbe

Vin(t)

Fig. 1.6: Amplificador classe B com compensao para V

BE

.

1.2.1 Eficincia

Podemos calcular a potncia mdia da fonte e da carga considerando que a corrente de coletor a

mesma que circula por R

L

. Desta forma temos que

( )

2

2 2 2

0

sin

1

4

T

m m

L

L L

V t V

P dt

T R R

e

= =

}

(1.18)

e

( )

( )

2 2

0 0

sin 1 1

CC

T T

CC m CC m

V CC C

L L

V V t V V

P V I t dt dt

T T R R

e

t

= = =

} }

(1.19)

De posse das equaes 1.18 e 1.19 obtemos a eficincia

4

CC

m L

V CC

V P

P V

t

q = = (1.20)

Considerando o caso ideal, onde a tenso de pico na sada pode chegar a V

CC

, temos para eficincia

mxima terica do amplificador classe B

78.5%

4

t

q = ~ (1.21)

Entretanto, devemos considerar a possibilidade de

m CC

V V < , devido ao V

CEsat

e a outros fatores.

Ao contrrio dos amplificadores classe A, no classe B a potncia dissipada pela fonte dependente

do nvel mximo da sada. interessante observarmos que a potncia mdia dissipada

Q

P no transistor

dada pela equao 1.22, e cujo grfico o da Fig. 1.7.

Material no disponvel para publicao

12

2

4

CC

CC m m

Q V L

L L

V V V

P P P

R R t

= = (1.22)

Derivando a equao 1.22 em relao a V

m

e igualando a zero, conclumos que a potncia mxima

dissipada no transistor ocorre para 2

m CC

V V t = e com valor dado pela equao 1.23. Este valor deve

ser considerado no clculo dos dissipadores de potncia, conforme ser mostrado mais frente.

Observamos que o ponto de maior aquecimento do transistor no coincide com a condio de potncia

mxima de sada, conforme mostrado na Fig. 1.7.

2

max 2

CC

Q

L

V

P

R t

= (1.23)

Fig. 1.7: Potncia mdia dissipada no transistor.

1.2.2 Distoro Harmnica

A distoro harmnica total (THD) mede a quantidade relativa de harmnicos produzidos pelo

amplificador. Se aplicarmos um sinal senoidal entrada do amplificador, a sada ser de forma geral

uma onda peridica, que pode ser representada pela srie de Fourier, conforme a equao 1.24.

( ) ( ) ( ) ( )

0 1 0 1 2 0 2 0

sin sin 2 ... sin ...

o n n

v t V V t V t V n t e | e | e | = + + + + + + + + (1.24)

A THD calculada pela equao 1.25.

2

2

1

n

n

V

THD

V

=

=

(1.25)

No caso do amplificador classe B, ( )

o

v t pode ser expresso pela srie de Fourier como

( ) ( ) ( )

0 0 0

1

sin cos

o n n

n

v t V A n t B n t e e

=

= + + (

(1.26)

onde

( )

( ) ( )

( ) ( )

0

0

0

0

0

0

1

2

sin

2

cos

T

o

T

n o

T

n o

V v t dt

T

A v t n t dt

T

B v t n t dt

T

e

e

}

}

}

(1.27)

Desconsiderando o nvel DC, temos

2 2

2

2 2

1 1

n n

n

A B

THD

A B

=

( +

=

+

(1.28)

Material no disponvel para publicao

13

No amplificador em questo, temos que

( )

2

0 0

0

1

sin

T

m

m

V

V V t dt

T

e

t

= =

}

(1.29)

( ) ( )

2

0 0

0

2, 1

2

sin sin

0, 1

T

m

n m

V n

A V t n t dt

n T

e e

=

= =

>

}

(1.30)

e

( ) ( )

( )

2

0 0

2

0

0, para mpar

2

2

sin cos

, para par

1

T

m

n m

n

V

B V t n t dt

n

T

n

e e

t

= =

}

(1.31)

Segundo a equao 1.26 temos

( ) ( )

( )

( )

( )

0 0

2

1

2

sin cos 2

2

2 1

m m m

o

n

V V V

v t t n t

n

e e

t

t

=

= +

(1.32)

Pela equao 1.28, a THD

( )

( )

2

2

1

2

2 1

43.52%

2

m

n

m

V

n

THD

V

t

=

(

(

(

(

= =

(1.33)

Para sistemas de udio de alta fidelidade, este valor de THD muito elevado, tornando este tipo de

amplificador inapropriado.

1.3 Amplificador Classe AB

Conforme vimos, o amplificador classe B deve ser compensado para queda de V

BE

. Isto feito

simplesmente colocando uma fonte DC de valor V

BE

na base do transistor. Entretanto, cada transistor

possui um V

BE

ligeiramente diferente e que varia com a temperatura. Torna-se difcil fazer esta

compensao com exatido. Normalmente, aplicamos uma fonte de tenso na base, ligeiramente maior

que V

BE

, para estabelecer uma pequena corrente de polarizao no transistor. Esta corrente no

suficiente para coloc-lo em classe A, mas garante a compensao de V

BE

. Este tipo de operao

chamado classe AB, e ser melhor explorado nos amplificadores push-pull.

1.4 Amplificador Classe C

As correntes de coletor nos amplificadores classe A e B conduzem com ngulos de 360 e 180,

respectivamente. Nos circuitos classe C a conduo se d com ngulos menores que 180, conforme a

Fig. 1.8. Este tipo de configurao tem sua principal aplicao nos circuito de rdio frequncia (RF), e

ser melhor estudado mais frente.

Fig. 1.8: Conduo da corrente no amplificador classe C.

Material no disponvel para publicao

14

1.5 Amplificador Push-Pull

Os amplificadores push-pull so compostos por dois circuitos classe B em oposio de fase.

Enquanto um amplificador conduz no ciclo positivo, o outro o faz no ciclo negativo. Isto ajuda a

reduzir drasticamente a THD.

A configurao mais empregada atualmente o estgio de sada com par complementar, que utiliza

transistores NPN e PNP, conforme a Fig. 1.9.

RL

-VCC

VCC

Vin(t)

Vo(t)

QP

QN

Fig. 1.9: Estgio de sada em push-pull.

A configurao da Fig. 1.9 emprega duas fontes simtricas. Entretanto, podemos implementar o

circuito com fonte unipolar, ao custo de um capacitor de desacoplamento a mais, conforme a Fig. 1.10.

O capacitor C calculado, segundo a especificao de frequncia de corte inferior f

CI

, pela equao

1.34, onde r

o

uma estimativa da resistncia de sada dos transistores. Normalmente, r

o

desprezado.

( )

1

2

CI L o

C

f R r t

=

+

(1.34)

VCC

QP

Vo(t)

Vin(t)

RL

C

QN

Vbb

Vcc/2

+

_

Vcc/2

Fig. 1.10: Estgio de sada em push-pull, com fonte unipolar.

1.5.1 Distoro de Crossover

Tomemos como exemplo o circuito da Fig. 1.9. Para uma fonte de sinal ( ) ( ) sin

in m

v t V t e = , haver

conduo do transistor NPN quando ( )

N

in BE

v t V > , e no transistor PNP quando ( )

in BEp

v t V < .

Quando o transistor NPN est em conduo, o PNP encontra-se cortado, pois a tenso entre base e

emissor maior que

P

BE

V . O Mesmo ocorre com o transistor NPN quando o PNP est em conduo,

pois a tenso entre base e emissor menor que

N

BE

V . Portanto, os dois transistores trabalhando em

conjunto permitem ao circuito operar nos ciclos positivo e negativo do sinal, conforme a Fig. 1.11a.

Podemos observar um desnvel no sinal de sada, tanto no ciclo positivo quanto no negativo, que

corresponde a

N

BE

V e

P

BE

V . Isto chamado de crossover e provoca distoro harmnica.

O crossover pode ser eliminado com o uso de fortes realimentaes negativas ou atravs de pr-

polarizao do estgio de sada, levando o amplificador a operar em classe AB. Com este

procedimento obtemos baixssima THD, conforme a Fig. 1.11b.

Material no disponvel para publicao

15

(a) (b)

Fig. 1.11: Sinal de sada do estgio push-pull: a) com crossover; b) sem crossover.

O circuito da Fig. 1.12 representa a forma esquemtica para compensao do crossover.

VCC

-VCC

RL

Vben

QN

Vo(t)

Vin(t)

| Vbep|

QP

Fig. 1.12: Compensao do crossover.

1.6 Dissipadores de Calor

Os amplificadores de potncia, como todos os dispositivos eletrnicos, por exemplo, os

microprocessadores, dissipam energia sob forma de calor. Esta energia deve ser retirada do

encapsulamento dos componentes que esto aquecendo, para evitar danos s junes semicondutoras.

Em geral, uma juno semicondutora suporta temperaturas na faixa de 150C. Os componentes

eletrnicos para aplicaes em potncia possuem uma rea destinada dissipao trmica, onde se

acopla um dissipador de calor.

1.6.1 Resistncia Trmica

O dimensionamento dos dissipadores torna-se muito simples, se considerarmos o sistema em

equilbrio trmico e as fontes de potncia constantes. O mecanismo de transferncia de calor pode ser

simplificado como na Fig. 1.13. A fonte de calor corresponde fonte de potncia, por exemplo uma

juno PN, e o material um obstculo que separa dois meios, por exemplo a carcaa do transistor.

Em equilbrio trmico, a equao que relaciona a diferena de temperatura (

1 2

T T ) e a potncia

transferida pelo material

( )

1 2

T T R P

u

= (1.35)

onde R

u

a resistncia trmica do material em C W

. A resistncia trmica depende de vrios fatores

como, por exemplo: a composio do material; a cor (o preto dissipa mais calor); rea ( R

u

inversamente proporcional a rea); o meio refrigerante (ar, gua, etc).

Umas das especificaes dos dispositivos de potncia so as resistncias trmicas da juno (ou

ncleo) para a carcaa

JC

R

u

e da carcaa para o ar

CA

R

u

. Um dispositivo isolado, sem dissipador de

calor, apresenta uma resistncia trmica da juno (ou ncleo) para o ar

JA

R

u

dada por

Material no disponvel para publicao

16

JA JC CA

R R R

u u u

= + (1.36)

Fig. 1.13: Mecanismo de transferncia de calor.

Quando temos uma sequncia de materiais acoplados mecanicamente, conforme a Fig. 1.14, a

diferena de temperatura nas interfaces calculada simplesmente por

0

1

N

N n

n

T T P R

u

=

=

(1.37)

onde

n

R

u

a resistncia trmica de cada corpo.

Fig. 1.14: Transferncia de calor por mltiplos obstculos.

1.6.2 Regio de Trabalho do Transistor em Funo da Temperatura

Os dispositivos semicondutores suportam uma temperatura limite na juno, que limita a potncia

mxima dissipada. Considerando que o transistor suporta uma corrente de coletor mxima I

Cmax

e uma

temperatura de juno T

Jmax

, temos que a potncia dissipada no transistor P

Qmax

deve respeitar s

inequaes 1.38, onde T

A

a temperatura do ar e

JA JC CA

R R R

u u u

= + .

( )

max

max

Q C CC

J A

Q

JA

P I V

T T

P

R

u

s

(1.38)

Das inequaes 1.38, conclumos que o transistor deve operar dentro da regio hachurada do

grfico da Fig. 1.15a. Entretanto, quando acoplamos um dissipador de calor ao transistor, o termo

CA

R

u

substitudo por ( )

CD DA

R R

u u

+ , que a soma das resistncias trmicas da carcaa para o

dissipador e do dissipador para o ar. Mas

CD

R

u

muito menor que

DA

R

u

, de forma que podemos

considerar a nova resistncia trmica total como sendo

JA JC DA

R R R

u u u

' ~ + , e muito menor que

JA

R

u

.

A curva de operao segura torna-se a da Fig. 1.15b, onde podemos observar que, para mesma

temperatura, o transistor pode dissipar mais potncia.

Material no disponvel para publicao

17

(a) (b)

Fig. 1.15: Curva de operao segura do transistor: a) ao ar livre; b) com dissipador.

1.6.3 Segundo Breakdown

Imagens de infravermelho obtidas de transistores de potncia em operao mostram que a

distribuio de calor na juno no uniforme, criando pontos quentes. O aparecimento destes pontos

est relacionado com a intensidade de corrente. Os pontos quentes destroem a juno aos poucos,

reduzindo a vida til do transistor. Este efeito conhecido como segundo breakdown (o primeiro

breakdown devido tenso de ruptura da juno). Normalmente, os fabricantes de transistores

fornecem uma famlia de curvas, para cada valor de temperatura na juno, relacionando a corrente

mxima de coletor e a tenso V

CE

, como exemplo a Fig. 1.16.

Fig. 1.16: Curva de operao segura, com segundo breakdown.

1.7 Circuitos Para Polarizao Classe AB

A compensao de crossover mostrada na Fig. 1.12 no prtica, pois implica no uso de duas

fontes de tenso alm da alimentao. Estas tenses devem ser geradas atravs de elementos passivos.

1.7.1 Polarizao Com Diodos

O circuito da Fig. 1.17 mostra um estgio de sada push-pull em classe AB, polarizado com diodos.

A fonte de corrente I

B

fora uma queda de tenso em cada diodo, que aproximadamente igual a V

BE

.

Desta forma as junes base-emissor dos transistores encontram-se pr-polarizadas. Sabemos que a

tenso da juno semicondutora varia com a temperatura, tipicamente 2mV C

, e a compensao

deve acompanhar esta variao, para ser efetiva. Caso contrrio, com o aquecimento, os transistores

reduziriam seus V

BEs

e ficariam excessivamente polarizados, a corrente em excesso nos coletores

aumentaria a temperatura, e foraria uma reduo ainda maior dos V

BEs

. Este processo, que

conhecido como colapso trmico, continuaria at a destruio do transistor.

Para realizarmos uma compensao dinmica, basta colocarmos os diodos em contato com os

dissipadores de calor pois desta forma, a temperatura ser aproximadamente a mesma dos transistores.

Com isto, as tenses nas junes dos diodos variam junto com os V

BEs

, e as correntes de coletor

permanecem estveis.

Material no disponvel para publicao

18

QP

QN

Rb

D1

C1

D2

Ib

-VCC

C1

RL

VCC

Vin(t)

Vo(t)

Fig. 1.17: Polarizao classe AB com diodos.

1.7.2 Multiplicador de V

BE

A compensao com diodos muito empregada, mas possui o inconveniente de no ser possvel

ajustar a tenso entre as bases. Isto somado ao fato das junes dos diodos no serem exatamente

iguais s dos transistores, torna este circuito inapropriado para algumas aplicaes, principalmente s

de elevada potncia.

O circuito da Fig. 1.18, conhecido com multiplicador de V

BE

, permite ajustar uma tenso V

o

proporcional ao V

BE

de um transistor. Se acoplarmos o transistor Q ao dissipador do estgio de sada,

temos uma polarizao compensada para variao de temperatura, e com ajuste de tenso.

R2

Vo

+

R1

Ix

_

Q

Fig. 1.18: Multiplicador de V

BE

.

Para analisarmos o circuito, consideremos a Fig. 1.19.

Material no disponvel para publicao

19

1

Vo

_

Ix 2

Ib

R1

Ic

Q

R2

Vbe

+

+

_

Fig. 1.19: Circuito para anlise do multiplicador de V

BE

.

Extraindo as equaes nodais, temos o sistema 1.39.

2

2 1

0

o BE

C x

BE o BE

B

C B

V V

I I

R

V V V

I

R R

I I |

+ =

+ + =

(1.39)

Do sistema de equaes 1.39 obtemos

2 2

1

1

1 1

o BE x

R R

V V I

R

|

| |

| |

= + +

|

+ +

\ .

(1.40)

Considerando | muito grande, de forma que ( ) 1 1 | | + ~ , temos que

2 2

1

1

1

o BE x

R R

V V I

R |

| |

= + +

|

+

\ .

(1.41)

Da equao 1.41, se considerarmos que

2 2

1

1

1

BE x

R R

V I

R |

| |

+

|

+

\ .

temos que

2

2

1

1

1

BE

x

R

R V

R I

| | | +

+

|

\ .

(1.42)

Temos finalmente que

2

1

1

o BE

R

V V

R

| |

= +

|

\ .

(1.43)

Aplicando a equao 1.43 em 1.42, obtemos como forma alternativa para estabelecer o valor

mximo dos resistores a expresso

1

1

1 1

x

BE o

R

I

V V

| +

| |

|

\ .

(1.44)

Material no disponvel para publicao

20

Devemos ter em mente tambm que o transistor tem que estar em condies de ser polarizado, isto

limita o menor valor de R

1

, ou seja,

1 x BE

R I V > (1.45)

Na Fig. 1.20 temos um estgio de sada em push- pull, polarizado em classe AB, com multiplicador

de V

BE

. Este circuito muito prtico, pois permite gerar qualquer diferena de potencial proporcional a

um V

BE

. Se acoplarmos termicamente o transistor Q

1

ao dissipador de calor, temos que V

BE

de Q

1

varia

junto com os V

BE

dos transistores de potncia, permitindo um ajuste dinmico da polarizao. Outro

fator a ser considerado, o melhor casamento entre as caractersticas da juno base-emissor de Q

1

com as dos transistores de potncia.

-VCC

R2

Vin(t)

C1

Vo(t)

Rb

R1

QN

C1

Q1

QP

Ib

VCC

RL

Fig. 1.20: Polarizao em classe AB com multiplicador de V

BE

.

1.8 Exemplo de Projeto

Como exemplo, consideremos um amplificador de potncia para udio, na configurao push-pull,

com as especificaes abaixo:

1. Carga de 8O (alto-falante).

2. Potncia de 4W na sada.

3. Eficincia melhor que 50%.

4. Frequncia de corte inferior menor que 50Hz.

Dados dos transistores:

1.

min

150 | = para Q

3

, Q

4

, Q

5

e Q

6

.

2.

min

15 | = para Q

1

, e Q

2

.

3. 0.7

BE

V V = para Q

3

, Q

4

, Q

5

e Q

6.

4. 0.7

BE

V V = para Q

1

, e Q

2

, para I

C

na faixa dos mA, e 1

BE

V V = para I

C

prximo a 1A.

5. 90

CEsat

V mV = para todos os transistores.

6. 4.17

JC

R C W

u

=

7.

max

150

J

T C =

O circuito empregado o da Fig. 1.21, onde temos os transistores de sada na configurao

Darlington, para aumentar o ganho de corrente, e um multiplicador de V

BE

para a polarizao em

classe AB. O transistor Q

5

funciona como fonte de corrente controlada por tenso, gerando sinal e

Material no disponvel para publicao

21

polarizao para o estgio de sada. Os resistores R

1

e R

2

tm a funo de controlar qualquer

descasamento do circuito de polarizao classe AB, atuando como uma degenerao de emissor. Caso

haja um pequeno aumento nas correntes de polarizao de emissor dos transistores de sada, devido ao

aumento da temperatura, as quedas de potenciais em R

1

e R

2

aumentam e consequentemente reduzem

as tenses entre base e emissor, forando a corrente de polarizao diminuir. Este um processo de

realimentao negativa que, em conjunto com o multiplicador de V

BE

, garante a estabilidade trmica

do amplificador. Os valores de R

1

e R

2

so empricos e normalmente escolhidos bem pequenos, por

exemplo,

1 2

0.5 R R = = O.

0

Q1

TIP30C

RL

Vin(t)

R5

Q6

BC558C

0

P2

R2

R3

Q5

BC548C

P1

-Vcc C1

0

Q3

BC548C

+Vcc

R1

R6

C2

Q4

BC548C

0

Vo(t)

Q2

TIP29C

0

R4

Fig. 1.21: Amplificador de potncia push-pull.

O dimensionamento do amplificador segue os passos abaixo.

Passo 1: Clculo da tenso e corrente mxima na carga.

2 2

max max

max max

4 8

2 2 8

o o

L o

L

V V

P W V V

R

= = = =

max

max max

8

1

8

o

L L

L

V

I I A

R

= = =

Passo 2: Eficincia mxima.

8

0.5 12.56

4 4

om

CC

CC CC

V

V V

V V

t t

q

= = > s (1.46)

Passo 3: Ciclo positivo.

Vamos considerar que no pico de sinal positivo na sada, o transistor Q

5

est no limite entre o corte

e a conduo, de forma que temos o circuito abaixo.

Material no disponvel para publicao

22

+

_

VR4

Vomax=8V

0

+Vcc

Ib2

+

_

VR1

Ib3

1A

Q3

BC548C

Q2

TIP29C

0

R1

R4

RL

Temos pela equao de malha que

4 3 3 2 1

8

CC B BE BE R

V R I V V V = + + + +

( )( )

max

4 3 2 max 1

3 2

8

1 1

L

CC BE BE L

I

V R V V I R

| |

= + + + +

+ +

( )( )

3 3

4 4

1

0.7 1 0.5 8 2.416 10 24.64 10

150 1 15 1

CC CC

V R R V = + + + + =

+ +

(1.47)

Mas sabemos que R

4

deve ser positivo, e aplicando esta condio equao 1.47 temos

3 3

2.416 10 24.64 10 0 10.2

CC CC

V V V > > (1.48)

Escolhemos V

CC

de forma a atender s inequaes 1.46 e 1.48, por exemplo 12

CC

V V = , e com a

equao 1.47 calculamos o valor comercial de R

4

ou seja,

3 3

4 4

2.416 10 12 24.64 10 4.35 3.9 R k R k = = O = O

Passo 4: Ciclo negativo.

Vamos considerar o pico de sinal negativo na carga, ou seja,

min

8

o

V V = . Neste momento, a tenso

no coletor de Q

5

atinge o menor nvel, e assumiremos que o transistor est saturado neste instante. Para

a anlise temos o circuito abaixo.

+

_

VR3

Vomin=-8V

1A

RL

R2

-Vcc

R3

0

0

C2

Q1

TIP30C

Q6

BC558C

+

_

VCEsat

0

Q5

BC548C

+

_

VR2

Vin(t)max

Pela equao de malha temos

Material no disponvel para publicao

23

min 2 1 6 3

0

o R BE BE CEsat R CC

V V V V V V V + + + + + =

3 3

8 0.5 1 0.7 0.09 12 0 1.71

R R

V V V + + + + + = =

Descobrimos o valor de V

R3

, e sabemos que R

3

est bypassado por C

2

. Isto significa que a tenso

V

R3

uma constante.

Passo 5: Corrente de polarizao de Q

5

.

Quando o amplificador est em repouso (sem sinal de entrada), a tenso na carga zero e os

transistores de sada esto polarizados com uma corrente de coletor muito baixa. Desta forma temos

V

R1

e V

R2

desprezveis e

2 3 1 6

0.7

BE BE BE BE

V V V V V = = = = . Portanto, a tenso na base de Q

3

3

1.4

B

V V = . A corrente de polarizao I

CQ5

do transistor Q

5

passa quase totalmente por R

4

, de forma

que

4 4 5 R CQ

V R I = . Podemos ento calcular a corrente I

CQ5

e o valor comercial de R

3

, ou seja,

4

1.4 12 1.4 10.6

R CC

V V V = = =

4 4 5 5 5

10.6 3900 2.72

R CQ CQ CQ

V R I I I mA = = =

3

5

5 5

5

2.72 10

18.1

150

CQ

B B

I

I I A

|

= = =

3

3 3 5 3 3 3

1.71 2.72 10 628.7 560

R CQ

V R I R R R

= = = O = O

Neste momento, a tenso V

R3

deve ser recalculada por causa da aproximao feita para R

3

.

3

3 3 5 3

560 2.72 10 1.52

R Cq R

V R I V V

= = =

Passo 6: Clculo de R

6

e P

1

.

Vamos considerar a corrente que circula por R

6

e P

1

pelo menos vinte vezes maior que a da base de

Q

5

, e desta forma podemos desprezar I

B5

. Isolando a malha de polarizao de Q

5

temos o circuito

abaixo.

0

R3

IR6

0

0

-Vcc

R6

C2

P1

Q5

BC548C

Da equao de malha obtemos

6 6 6 1

6 1 3

6 5

0

0.7 2.22

20

R R CC

R R

R B

I R I P V

I P V V

I I

+ =

= + =

>

(1.49)

Solucionando o sistema de duas equaes e uma inequao 1.49 temos

Material no disponvel para publicao

24

6 6

1 6 1

27.01 27

0.23 6.13

R k R k

P R P k

< O = O

= = O

Passo 7: Clculo dos capacitores.

Para o clculo de C

2

, consideraremos que C

1

seja um bypassing. A impedncia vista por C

2

3

2 3 5

5 3

// 9.04

1 40

in e

CQ

R

R R r

I R

= ~ = O

+

O capacitor calculado segundo a frequncia de corte inferior.

2 2

2

1

352 390

2

CI in

C F C F

f R

t

= = =

Para o clculo de C

1

, consideraremos que C

2

seja um bypassing. A impedncia vista por C

1

1 6 1

5

6 1 5

1

/ / / / 1.09

40

1 1

in ie

CQ

R R P h k

I

R P |

= ~ = O

+ +

Pela frequncia de corte inferior temos que

1

1

1

2.9

2

CI in

C F

f R

t

= =

Escolhemos o menor capacitor, no caso C

1

, e multiplicamos por dez.

6

1 1

10 2.9 10 29 27 C F C F

= = =

Passo 8: Dimensionamento do multiplicador de V

BE

.

Sabemos que na polarizao, o multiplicador de V

BE

deve gerar uma diferena de potencial de

4 0.7V . Das equaes 1.43, 1.44 e 1.45 temos

5 5 5

0.7 257

CQ

R I V R > > O

4

5 5

5

1

51.8

1 1

CQ

BE o

R R k

I

V V

| +

O

| |

|

\ .

5 5

257 51.8 3.9 R k R k O s O = O

2 2

2 3

5

1 4 0.7 1 0.7 11.7

3.9 10

o BE

P P

V V P k

R

| |

| |

= + = + = O

| |

\ .

\ .

Passo 9: Clculo do ganho de tenso.

Para o clculo do ganho de tenso, vamos considerar o estgio de sada como sendo um

amplificador de ganho unitrio, mas com impedncia de entrada dependente da carga. O multiplicador

de V

BE

atua como fonte de tenso, e no aparece no modelo AC. Com as consideraes acima, temos o

circuito abaixo para a anlise. Temos ento que

( )( )( ) ( )( )( )

3,6 1,2

1 1 150 1 15 1 0.5 8 20.54

ref L

R R R k | | = + + + = + + + = O

( ) ( )

4 5 4

// 40 // 336

o L L

v ref CQ ref v

in L L

V R R

A gm R R I R R A

V R R R R

= = = =

+ +

Material no disponvel para publicao

25

Vin

0

1

gmVin

hie P1

R=(R1 ou R2)

Vo

R4

RL

R6 Rref

Passo 10: Ganho de potncia.

O ganho de potncia A

p

dado por

L

p

in

P

A

P

= (1.50)

Sabemos que

( )

2

in

in

in

v t

P

R

=

e

( )

2

o

L

L

v t

P

R

=

mas

( ) ( )

2 2

2

o v in

v t A v t =

Substituindo as equaes acima, finalmente temos

2 in

p v

L

R

A A

R

= (1.51)

No circuito, o ganho de potncia

3 3

3

2 2 6 6 1

150 1

27 10 // 6.21 10 //

// // 40 2.72 10

336 15.4 10

8

ie

p v p

L

R P h

A A A

R

+ | |

|

\ .

= = =

O valor extremamente elevado de A

p

comum para os amplificadores de potncia. Caso o estgio

de entrada fosse implementado com MOSFET, o ganho de potncia seria virtualmente infinito.

Passo 11: Dissipador de calor.

A potncia mxima dissipada em cada transistor dada pela equao 1.23, e vale

2 2

max 2 2

12

1.82

8

CC

Q

L

V

P W

R t t

= = =

Dada a temperatura mxima da juno

max

150

J

T C =

, e considerando a temperatura do ar nas

proximidades do dissipador igual a 50C, para existir o equilbrio trmico devemos ter

( ) ( )

max max JC DA Q J A

R R P T T

u u

+ =

( ) ( ) 4.17 1.82 150 50 50.8

DA DA

R R C W

u u

+ = =

Cada transistor deve ser acoplado a um dissipador de calor com resistncia trmica igual a

50.8 C W

.

Material no disponvel para publicao

26

Captulo 2

Amplificador Sintonizado

Os amplificadores sintonizados so empregados quando desejamos separar e amplificar uma faixa

de frequncias de um sinal. Suponha que o grfico da Fig. 2.1 seja uma faixa de transmisso de rdio,

e desejamos separar (sintonizar) e amplificar o canal centrado na frequncia

0

e . Devemos usar um

amplificador com funo de transferncia ( ) A je passa-banda.

Fig. 2.1: Espectro de rdio frequncia.

A seletividade Q do amplificador definida como sendo a razo entre a frequncia de sintonia

0

e

e a faixa onde o ganho cai 3dB (faixa de passagem), ou meia potncia, conforme a equao 2.1 e a Fig.

2.2.

0

2 1

Q

e

e e

=

(2.1)

Fig. 2.2: Curva de resposta em frequncia do amplificador sintonizado.

2.1 Circuito RLC de Segunda Ordem

Normalmente utilizam-se circuitos RLC de segunda ordem, como o da Fig. 2.3, para a realizao

do filtro. fcil verificar que a funo de transferncia do ganho de tenso dada por

Material no disponvel para publicao

27

( )

2

1

o

in

V gm s

A s

s

V C

s

RC LC

= =

+ +

(2.2)

Substituindo s por je na equao 2.2, temos

( )

2

1

gm j

A j

j

C

RC LC

e

e

e

e

=

+ +

(2.3)

Calculando o mdulo ao quadrado de ( ) A je , temos

( ) ( ) ( )

( )

2 2

2 *

2 2

2

2

2

1

gm

A j A j A j

C

LC

RC

e

e e e

e

e

= =

| |

+

|

\ .

(2.4)

Verificamos que ( )

2

A je mximo quando

( )

2

1 0 LC e = , ou seja, a frequncia de sintonia

corresponde ressonncia do circuito RLC, e dada por

0

1

LC

e = (2.5)

O ganho na frequncia de sintonia calculado fazendo 1 LC e = na equao 2.4, ou seja,

( )

0

A gmR e = (2.6)

L R

VCC

Vo

C

Vbeq

Vin

Vo

R

Vin

C

L

hie gmVin

(a) (b)

Fig. 2.3: Circuito RLC de segunda ordem: a) circuito com transistor; b) modelo AC.

Os pontos de queda de 3dB, so calculados resolvendo a equao ( ) ( )

0

2 A j A j e e = ou, de

forma melhor,

( )

( )

( )

2

2 2 2 2

2

0

2 2

2

2

2

2 2

1

A j

gm gm R

A j

C

LC

RC

e

e

e

e

e

= =

| |

+

|

\ .

(2.7)

Desenvolvendo a equao 2.7, temos

Material no disponvel para publicao

28

2 2 2

2 2 4 2

2

2

1 0

C R R

C R

LC L

e e

| |

+ + =

|

\ .

(2.8)

A soluo da equao 2.8 para

2

e

2 2 2 2

2

2 2

2 4

1 1

2

C R C R

LC LC

C R

e

+ +

= (2.9)

Tomando como referncia o grfico da Fig. 2.2, fcil concluir que

2 2 2 2

1 2 2 2 2

2 2 2 2

2 2 2 2 2

4 2

1 1

2 2

4 2

1 1

2 2

C R C R

LC LC

C R C R

C R C R

LC LC

C R C R

e

e

| |

| |

+ | +

|

|

= |

|

|

| |

\ .

\ .

| |

| |

+ | +

|

|

= + |

|

|

| |

\ .

\ .

(2.10)

Para encontrarmos

2 1

e e , consideremos o sistema de equaes 2.11.

x a b

y a b

= +

(2.11)

Por manipulao algbrica temos que

( )

2

2 2 2 2

2 2 2 2 y x a a b y x a a b = = (2.12)

Comparando o sistema de equaes 2.11 com 2.10, termo a termo, e atravs da equao 2.12,

temos finalmente que

2 1

1

RC

e e = (2.13)

Pela equao 2.1, temos que a seletividade do circuito

0

Q RC e = (2.14)

Considerando a equao 2.5, temos que a seletividade tambm pode ser expressa por

0

R

Q

L e

= (2.15)

Substituindo as equaes 2.14 e 2.5 em 2.2, temos

( )

2 2 0

0

o

in

V gm s

A s

V C

s s

Q

e

e

= =

+ +

(2.16)

2.2 Amplificadores com Sintonia Sncrona

Filtros sintonizados de segunda ordem com sintonia muito elevada so difceis de realizar, devido

s imperfeies dos componentes, tipicamente as resistncias parasitas dos capacitores e indutores.

Normalmente, seletividades elevadas so obtidas pela associao em cascata de amplificadores

sintonizados com seletividades idnticas, conforme a Fig. 2.4.

Material no disponvel para publicao

29

Fig. 2.4: Cascata de amplificadores sintonizados.

As funes de transferncia ( )

k

A s diferem entre si somente por um fator de ganho, ou seja,

( )

2 2 0

0

k

k

a s

A s

s s

Q

e

e

=

+ +

(2.17)

Definindo

( )

2 2 0

0

s

T s

s s

Q

e

e

=

+ +

(2.18)

temos

( ) ( )

k k

A s a T s = (2.19)

Da equao 2.19, conclumos que funo de transferncia do filtro da Fig. 2.4 dada por

( )

( )

( ) ( )

1

N

N

o

k

k in

V s

H s T s a

V s

=

= =

[

(2.20)

Analisando ( )

N

T s separadamente, e substituindo s por je, temos que

( )

( )

2

2

2

2

2 2 2 0

0 2

N

N

N

T j

Q

e

e

e

e e e

=

(

+

(

(2.21)

Aplicando a transformao de varivel ( )

0 0 0

1 e e e e e e = + A = + A equao 2.21, temos

( ) ( )

( )

( )

( )

( )

2

2

2

0 0

0

2

2

2 2

2 2 2 0

0 0 0 0 0 2

1

1 1

N

N

N

N

T j

Q

e e e

e e

e

e e e e e e e

+ A

+ A =

(

+ A + + A

(

(2.22)

Considerando que a seletividade final do circuito muito maior que 1, temos que a frequncia de

queda de 3dB est muito prxima de e

0

, e lembrando que, para 1 x , vale a aproximao

( ) ( )

2

1 1 2 x x + ~ + , temos que ( ) ( )

2

0 0

1 1 2 e e e e + A ~ + A , e a equao 2.22 torna-se

( ) ( )

( )

( ) ( )

2

2

0 0

0

2

2

2 0

0 0 0 2

1 2

2 1 2

N

N

N

N

T j

Q

e e e

e e

e

e e e e e

+ A

+ A =

(

A + + A

(

(2.23)

Como estamos considerando variaes de frequncias em torno da faixa de passagem, razovel

assumir que

0

2 e e A da mesma ordem de grandeza que 1 Q, e como 1 1 Q , a equao 2.23 pode

ser aproximada por

( ) ( )

( )

2

2

0

0

2

2

2 0

0 0 2

2

N

N

N

T j

Q

e

e e

e

e e e

+ A =

(

A +

(

(2.24)

Para determinarmos a seletividade

ef

Q de ( )

N

T s , basta calcularmos e A de forma que

Material no disponvel para publicao

30

( ) ( )

( )

( )

2

2 2

2

0

0

0 2

2

0 2

2 0

0 0 2

2 2

2

N

N N

N

N N

T j

Q

T j

Q

e

e

e e

e

e

e e e

+ A = = =

(

A +

(

(2.25)

e fazermos ( )

0

2

ef

Q e e = A . Da equao 2.25 obtemos

1

0

2 1

2

N

Q

e

e

A = (2.26)

Finalmente, a seletividade do amplificador em cascata

1

2 1

ef

N

Q

Q =

(2.27)

2.3 Amplificador de Banda Plana

Em algumas aplicaes, necessrio que a faixa de passagem do amplificador sintonizado seja

quase plana. Uma aplicao tpica a sintonia de canais de televiso, cuja faixa de frequncias

aproximadamente 4MHz. Um filtro sintonizado de segunda ordem ou com sintonia sncrona, provoca

um desnvel progressivo de 3dB entre os extremos da faixa e a frequncia central. Isto gera uma

distoro inaceitvel para sinais de vdeo.

Uma forma simples, mas eficiente, de projetar filtros com banda quase plana consiste em uma

cascata de amplificadores sintonizados, mas com frequncias de ressonncia ligeiramente diferentes.

A Fig. 2.5 ilustra o procedimento. No exemplo, trs amplificadores sintonizados ( )

1

A je , ( )

2

A je e

( )

3

A je , com frequncias de ressonncia

1

e ,

2

e e

3

e respectivamente, compem o filtro ( ) A je .

Fig. 2.5: Filtro de banda plana.

2.4 Fator de Qualidade

O fator de qualidade Q mede o quo prximo o componente est do ideal. Este parmetro

normalmente usado para caracterizar indutores e capacitores, e em geral depende da frequncia.

2.4.1 Fator de Qualidade dos Indutores

Um indutor ideal deve possuir impedncia puramente reativa j L e . Entretanto, fatores como

resistncia do fio, efeito pelicular, irradiao eletromagntica e capacitncia parasita, alteram o valor

medido da reatncia e acrescentam uma componente resistiva. De forma geral, ao estabelecermos a

relao entre os fasores de tenso e corrente no indutor em uma frequncia e, estamos medindo uma

Material no disponvel para publicao

31

impedncia em funo de e. Esta impedncia pode ser representada pela associao srie ou paralelo

do indutor com resistor.

2.4.1.1 Indutor em Srie com Resistor

A impedncia de um indutor em srie com resistor, circuito da Fig. 2.6, ( )

s s

Z j L R e e = + . Se

definirmos o fator de qualidade como sendo a relao entre a componente ideal e a indesejvel, temos

s

s

L

s

L

Q

R

e

= (2.28)

Ls

Rs

Fig. 2.6: Indutor em srie com resistor.

2.4.1.2 Indutor Paralelo com Resistor

Calculando a admitncia do circuito da Fig. 2.7, temos ( ) 1 1

p p

Y j L R e e = + . A componente ideal

1

p

j L e , e da mesma forma que no item anterior, podemos definir o fator de qualidade como sendo a

razo entre a componente ideal e a indesejvel. Temos ento que

p

p

p

R

Q

L e

= (2.29)

Rp

Lp

Fig. 2.7: Indutor em paralelo com resistor.

2.4.2 Fator de Qualidade dos Capacitores

Da mesma forma que nos indutores, quando medimos um capacitor, relacionamos os fasores de

corrente e tenso, que nos fornece uma admitncia em funo da frequncia. As principais

imperfeies dos capacitores so: a resistncia finita do dieltrico, particularmente em frequncias

elevadas; a resistncia dos terminais; as indutncias parasitas dos terminais e do dieltrico.

2.4.2.1 Capacitor em Paralelo com Resistor

Calculando a admitncia do circuito da Fig. 2.8, temos ( ) 1

p p

Y j C R e e = + . A componente ideal

p

j C e , e consequentemente,

p p p

Q R C e = (2.30)

Rp

Cp

Fig. 2.8: Capacitor em paralelo com resistor.

2.4.2.2 Capacitor em Srie com Resistor

A impedncia do circuito da Fig. 2.9 ( ) 1

s s

Z j C R e e = + , e a componente ideal 1

s

j C e .

Seguindo o mesmo procedimento dos itens anteriores, temos para o fator de qualidade

Material no disponvel para publicao

32

1

s

s s

Q

R C e

= (2.31)

Cs Rs

Fig. 2.9: Capacitor em srie com resistor.

2.5 Indutores Acoplados

Os indutores acoplados so dois ou mais indutores que compartilham parte ou todo fluxo

magntico gerado pelo sistema. Como exemplo, considere o sistema de dois indutores da Fig. 2.10. As

correntes e tenses se relacionam segundo o sistema de equaes 2.32, onde M a indutncia mtua.

Podemos considerar o efeito do acoplamento, lembrando que

1 2

M k L L = , onde k o fator de

acoplamento. Desta forma, o sistema 2.32 pode ser melhor representado por 2.33.

1 1 1

2 2 2

V L M I

V M L I

( ( (

=

( ( (

(2.32)

1 1 2 1 1

2 2

1 2 2

L k L L V I

V I

k L L L

(

( (

= (

( (

(

(2.33)

+

_

V1

L2

I2

L1

I1

M

+

_

V2

Fig. 2.10: Dois indutores acoplados.

O valor de k varia entre zero e um. Para indutores com acoplamento fraco, temos k muito prximo

de zero, enquanto k tende para um quando o acoplamento forte.

2.5.1 Modelos Equivalentes Para Indutores Acoplados

O sistema de equaes 2.33 pode ser inapropriado para a anlise de alguns circuitos, devido

complexidade dos clculos. Podemos representar o circuito da Fig. 2.10 por um modelo equivalente,

composto por indutores desacoplados e transformador ideal. Os circuitos a seguir so formas

equivalentes de representao.

a)

+

_

V2

1:1

.

+

_

V1 La

I2

Lb

I1

Lc

.

( ) ( )

2

1 2 2 a

L L L M L M =

( )

2

1 2 b

L L L M M =

( ) ( )

2

1 2 1 c

L L L M L M =

b)

La

I2

+

_

V1

.

.

Lb

+

_

V2

Lc

I1

1:1

1 a

L L M =

b

L M =

2 c

L L M =

Material no disponvel para publicao

33

c)

.

.

I1 I2

La

+

_

V1

+

_

V2

a:1

Lb

( )

2

1

1

a

L k L =

2

1 b

L k L =

1 2

a k L L =

1 2

k M L L =

Para acoplamento unitrio, ou muito prximo, o circuito c) pode ser simplificado, e representado

pela Fig. 2.11. Esta forma de representao uma das mais usadas para a anlise dos amplificadores

sintonizados.

.

L1

+

_

V1

I2

+

_

V2

I1

.

a:1

1 1

2 2

N L

a

N L

= =

1 2

N N a relao de espiras

do transformador.

Fig. 2.11: Representao dos indutores acoplados com acoplamento unitrio.

2.5.2 Autotransformador

Consideremos os indutores acoplados, com 1 k = , da Fig. 2.12. Este circuito chamado de

autotransformador, pois os indutores formam um enrolamento contnuo. Da mesma forma que no item

anterior, podemos representar o sistema por um indutor e um transformador ideal, conforme a Fig.

2.13.

.

.

L1

L2

V3

V1

N2

V2

N1

Fig. 2.12: Autotransformador.

1 2 1 2

2 L L L L L = + +

3 1 2 N N N = +

( ) ( )

1 2 2 3

1 2 V V V V N N =

( ) ( ) ( )

1 3 2 3

1 2 2 3 2 V V V V N N N N N = + =

Fig. 2.13: Circuito equivalente do autotransformador.

2.5.3 Mltiplos Indutores Acoplados

Consideremos o sistema de trs indutores acoplados, com 1 k = , da Fig. 2.14. Podemos caracteriz-

lo, escolhendo um dos enrolamentos 1-2, 1-3, 2-3 ou 4-5, medindo a indutncia e o fator de qualidade.

Temos ento os circuitos equivalentes da Tabela 2.1. importante observar que, nos modelos

equivalentes, o indutor e o resistor devem estar representados em somente um dos enrolamentos do

transformador (nunca em mais de um ao mesmo tempo).

Material no disponvel para publicao

34

1

2

5

.

. .

L1

L2

L3

3

4

Fig. 2.14: Sistema de trs indutores acoplados.

Tabela 2.1: Circuito equivalente para os trs indutores acoplados.

3

1

5

2

L1

4

R1

3

2

5

.

. .

N1

N2

N3

4

.

. .

L1

L2

L3

1

1

1

R

Q

L e

=

R2

4

3

L2

.

. .

L1

L2

L3

1

3 5 5

1

2 2

.

. .

N1

N2

N3

4

2

2

R

Q

L e

=

5

.

. .

N1

N2

N3

R3

5

4

.

. .

L1

L2

L3

1

2

3

L3 2

4 1

3

3

3

R

Q

L e

=

1

.

. .

L1

L2

L3

1 4

5

.

. .

N1

N2

N3

3

L

3

2 R

5

4

2

R

Q

L e

=

( ) ( )

2 2

1 1 2 2

1 2 1 2

;

1 1

N N N N

L L R R

N N

+ +

= =

( ) ( )

2 2

2 2 2 2

1 2 1 2

;

2 2

N N N N

L L R R

N N

+ +

= =

( ) ( )

2 2

3 3 2 2

1 2 1 2

;

3 3

N N N N

L L R R

N N

+ +

= =

2.5.4 Relao de Impedncias no Transformador

Uma impedncia Z conectada a um dos acessos do transformador ideal, pode ser representada em

outro acesso segundo a relao de espiras ao quadrado, conforme a Fig. 2.15.

Material no disponvel para publicao

35

N2

Z1

N2

Z2 N1 N1

2

2 1

2

1

N

Z Z

N

| |

=

|

\ .

Fig. 2.15: Relao de impedncia no transformador.

Para o caso especfico dos resistores, indutores e capacitores, as relaes esto na Fig. 2.16.

R1

N2

N1 N1 R2

N2

2

2 1

2

1

N

R R

N

| |

=

|

\ .

N1 L2 N1 L1

N2 N2

2

2 1

2

1

N

L L

N

| |

=

|

\ .

C1

N1 N1

N2 N2 C2

2

2 1

1

2

N

C C

N

| |

=

|

\ .

Fig. 2.16: Relao dos resistores, indutores e capacitores no transformador ideal.

Exemplo 1: Considere o amplificador sintonizado abaixo. Calcule o ganho e a seletividade.

So dados: