Escolar Documentos

Profissional Documentos

Cultura Documentos

Lab2 VHDL Fluxo Quartus

Enviado por

shillaram0 notas0% acharam este documento útil (0 voto)

6 visualizações26 páginasDireitos autorais

© © All Rights Reserved

Formatos disponíveis

PDF, TXT ou leia online no Scribd

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato PDF, TXT ou leia online no Scribd

0 notas0% acharam este documento útil (0 voto)

6 visualizações26 páginasLab2 VHDL Fluxo Quartus

Enviado por

shillaramDireitos autorais:

© All Rights Reserved

Formatos disponíveis

Baixe no formato PDF, TXT ou leia online no Scribd

Você está na página 1de 26

EEL7020 Sistemas Digitais

Prof. Eduardo Augusto Bezerra

Eduardo.Bezerra@eel.ufsc.br

Florianpolis, maro de 2013.

Universidade Federal de Santa Catarina

Centro Tecnolgico CTC

Departamento de Engenharia Eltrica

http://gse.ufsc.br

EEL7020 Sistemas Digitais

2/26

Objetivos:

Apresentar uma viso geral de VHDL

Exemplo de descrio VHDL

Introduo ao Quartus II ferramentas de desenvolvimento

Estudo de caso / exerccio

Plano de Aula

Projeto de Sistemas Digitais com VHDL

EEL7020 Sistemas Digitais

3/26

VHDL - Viso Geral

VHDL - linguagem para descrio de hardware

VHDL = VHSIC Hardware Description Language

VHSIC = Very High Speed Integrated Circuits. Programa do governo

dos USA do incio dos anos 80.

No final da dcada de 80, VHDL se tornou um padro IEEE (Institute

of Electrical and Electronic Engineers).

Existem diversas ferramentas para simular e sintetizar (gerar

hardware) circuitos descritos em VHDL.

Outras linguagens de descrio de hardware: Verilog, SystemC,

AHDL, Handel-C, System Verilog, Abel, Ruby, ...

EEL7020 Sistemas Digitais

4/26

VHDL - Viso Geral

O projeto de um circuito digital pode ser descrito em VHDL em diversos

nveis de abstrao (estrutural, comportamental).

Descries no nvel de transferncia entre registradores (RTL, Register

Transfer Level) so bastante utilizadas.

VHDL NO uma linguagem de programao, e as ferramentas de sntese

(no so de compilao) no geram cdigos executveis a partir de uma

descrio VHDL.

Descries em VHDL podem ser simuladas (executadas em um simulador).

Descries em VHDL podem ser utilizadas para gerar um hardware (arquivo

para configurao de um FPGA, por exemplo).

A gerao de estmulos para simulao VHDL realizada por intermdio de

testbenches.

Um testbench define os estmulos externos a serem utilizados como entrada

para o circuito (definio do comportamento externo ao circuito sob teste).

O testbench pode ser escrito em VHDL ou em diversas outras linguagens

(ex. C, C++, ...).

EEL7020 Sistemas Digitais

5/26

Descrio de circuito digital em VHDL

A

B

F1

F2

0 0 0 0

0 1 1 0

1 0 1 0

1 1 0 1

F1 = A xor B

F2 = A and B

A

B

ENTITY define os pinos do circuito digital (sinais), ou seja,

a interface entre a lgica implementada e o mundo externo.

entity halfadd is

port (A: in std_logic;

B: in std_logic;

F1: out std_logic;

F2: out std_logic

);

end halfadd;

ENTITY

EEL7020 Sistemas Digitais

6/26

architecture circuito_logico of halfadd is

begin

F1 <= A xor B;

F2 <= A and B;

end circuito_logico;

ARCHITECTURE

Descrio de circuito digital em VHDL

F1 = A xor B

F2 = A and B

A

B

ARCHITECTURE define a funcionalidade do circuito digital,

utilizando os pinos de entrada e sada listados na ENTITY em

questo. Uma ENTITY pode possuir diversas implementaes

diferentes (diversas ARCHITECTURES).

EEL7020 Sistemas Digitais

7/26

Descrio completa do circuito em VHDL

(Entity e Architecture)

F1 = A xor B

F2 = A and B

A

B

library IEEE;

use IEEE.Std_Logic_1164.all;

entity halfadd is

port (A: in std_logic;

B: in std_logic;

F1: out std_logic;

F2: out std_logic

);

end halfadd;

architecture circuito_logico of halfadd is

begin

F1 <= A xor B;

F2 <= A and B;

end circuito_logico;

Para utilizar o tipo

std_logic necessrio

incluir um pacote da

biblioteca IEEE.

EEL7020 Sistemas Digitais

8/26

Plataforma de prototipao FPGA Altera - DE2

EEL7020 Sistemas Digitais

9/26

Kit DE2 da Altera

EEL7020 Sistemas Digitais

10/26

Interface com o usurio (entrada e sada)

Placa DE2 possui 18 LEDs vermelhos denominados LEDR17-0 e

18 chaves denominadas SW17-0

As conexes entre esses componentes e os pinos do FPGA da

placa esto definidas no arquivo DE2_pin_assignments.csv

So utilizados vetores para facilitar o acesso aos LEDs e

chaves da placa

Exemplo: SW[0] o elemento 0 do vetor SW, e est conectado

ao pino PIN_N25 do FPGA

No cdigo em VHDL, usar sempre os nomes definidos no

arquivo DE2_pin_assignments.csv (ver Pinos.csv no site da disciplina)

EEL7020 Sistemas Digitais

11/26

Cdigo VHDL para leitura das chaves e escrita nos LEDs

library ieee;

use ieee.std_logic_1164.all;

entity part1 is

port ( SW : in std_logic_vector(17 downto 0);

LEDR : out std_logic_vector(17 downto 0)

);

end part1;

architecture behavior of part1 is

begin

LEDR(7 downto 0) <= SW(15 downto 8);

LEDR(15 downto 8) <= 01010101;

LEDR(17) <= (SW(17) AND SW(0)) OR (SW(16) AND 1);

end behavior;

Interface com o usurio (entrada e sada)

EEL7020 Sistemas Digitais

12/26

Tarefa a ser realizada na aula prtica

EEL7020 Sistemas Digitais

13/26

Tarefa a ser realizada na aula prtica

1. Utilizando a ferramenta Quartus II da Altera, criar um projeto VHDL

que implemente o circuito apresentado no slide 7 (and e xor).

2. Realizar a simulao do circuito (VHDL) por intermdio de

diagramas de formas de onda, e obter a tabela verdade.

3. Visando fixar o conhecimento do fluxo de ferramentas de projeto,

seguir o tutorial descrito no livro texto, e detalhado na ltima aula.

4. Utilizando as dicas do slide 11, alterar o projeto de forma a realizar

a entrada dos dados A e B a partir das chaves SW(0) e SW(1), e a

apresentao dos resultados F1 e F2 no LEDR(0) e LEDR(1).

5. Testar o circuito no kit DE2, usando as chaves SW(0) e SW(1) para

entrar com os operandos, e observar os resultados nos LEDs.

EEL7020 Sistemas Digitais

14/26

1. [Quartus II] File -> New Project Wizard

2. No project wizard, seguir exatamente os passos do

tutorial da ltima aula.

3. File -> New -> VHDL File (Essa a principal diferena!).

Resumo do tutorial: Etapa 1 - Design Entry

4. Copiar o fonte VHDL do

slide 7 para o novo

arquivo, e salvar.

EEL7020 Sistemas Digitais

15/26

Resumo do tutorial: Etapa 2 - Simulao

5. [ModelSim] Simulao Funcional Teste do circuito

-> no considera informao de temporizao.

Seguir o tutorial de simulao da ltima aula.

6. Resultado esperado da simulao:

F1

F2

EEL7020 Sistemas Digitais

16/26

Resumo do tutorial: Etapa 3 prototipao FPGA

7. Adaptar o fonte para os nomes de sinais da DE2:

EEL7020 Sistemas Digitais

17/26

8. Assignments -> Import Assigments (procurar no site e usar o

arquivo DE2_pin_assignments.qsf ou Pinos.qsf)

9. Com isso, os pinos do FPGA foram associados aos sinais da

entity do VHDL

10. Compilar o VHDL (sntese)

11. ATENO!!! Verificar se o nome da entity o mesmo nome

do projeto, para evitar erros na sntese.

12. A compilao resulta em cerca de 400 warnings devido aos

pinos no conectados do arquivo .qsf

Resumo do tutorial: Etapa 3 prototipao FPGA

EEL7020 Sistemas Digitais

18/26

13. Programao FPGA carregado com circuito, configurando

fisicamente elementos de processamento e roteamento.

Tools Programmer. Hardware Setup USB-Blaster. Start!

Resumo do tutorial: Etapa 3 prototipao FPGA

EEL7020 Sistemas Digitais

19/26

Para ir alm: uso do LCD

EEL7020 Sistemas Digitais

20/26

Escrita no LCD da placa DE2 da Altera

library ieee;

use ieee.std_logic_1164.all;

entity LCD is

port (

LCD_DATA: out std_logic_vector(7 downto 0);

LCD_RW: out std_logic;

LCD_EN: out std_logic;

LCD_RS: out std_logic;

LCD_ON: out std_logic;

LCD_BLON: out std_logic;

SW : in std_logic_vector(17 downto 0)

);

end LCD;

architecture LCD_WR of LCD is

begin

LCD_ON <= SW(17);

LCD_BLON <= SW(16);

LCD_DATA <= SW(7 downto 0);

LCD_RS <= SW(8);

LCD_EN <= SW(9);

LCD_RW <= SW(10);

end LCD_WR;

EEL7020 Sistemas Digitais

21/26

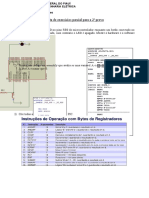

Passos para inicializar (CONFIGURAR) o LCD

- ligar LCD

- ativar cursor

e piscar

Chave (SW) Valor (posio da chave) Efeito

17 1 LCD_ON

16 1 LCD_BLON

7 .. 0 0011 1000 Comando

8 0 LCD_RS (0 = controle)

9 0 1 0 LCD_EN

10 0 LCD_RW

PASSO 1: envia comando 1 (38H).

Esse comando liga o LCD, liga o cursor, e faz o cursor piscar.

EEL7020 Sistemas Digitais

22/26

- ligar LCD

- ativar cursor

e piscar

Chave (SW) Valor (posio da chave) Efeito

17 1 LCD_ON

16 1 LCD_BLON

7 .. 0 0000 1111 Comando

8 0 LCD_RS (0 = controle)

9 0 1 0 LCD_EN

10 0 LCD_RW

Passos para inicializar (CONFIGURAR) o LCD

PASSO 2: envia comando 2 (0FH).

Esse comando liga o LCD, liga o cursor, e faz o cursor piscar.

EEL7020 Sistemas Digitais

23/26

- ligar LCD

- ativar cursor

e piscar

Chave (SW) Valor (posio da chave) Efeito

17 1 LCD_ON

16 1 LCD_BLON

7 .. 0 0000 0110 Comando

8 0 LCD_RS (0 = controle)

9 0 1 0 LCD_EN

10 0 LCD_RW

Passos para inicializar (CONFIGURAR) o LCD

PASSO 3: envia comando 3 (06H).

Esse comando liga o LCD, liga o cursor, e faz o cursor piscar.

EEL7020 Sistemas Digitais

24/26

Chave (SW) Valor (posio da chave) Efeito

17 1 LCD_ON

16 1 LCD_BLON

7 .. 0 0100 0001 Dado A

8 1 LCD_RS (1 = dados)

9 0 1 0 LCD_EN

10 0 LCD_RW

Procedimento de ESCRITA de caracteres no LCD

PASSO 4: envio de dados para o LCD

O LCD aceita caracteres da tabela ASCII (ver

http://asciitable.com). No exemplo a seguir est sendo

escrito o caracter A, ou seja, 41H, ou 01000001 em binrio.

EEL7020 Sistemas Digitais

25/26

Chave (SW) Valor (posio da chave) Efeito

17 1 LCD_ON

16 1 LCD_BLON

7 .. 0 0000 0001 Comando

8 0 LCD_RS (0 = controle)

9 0 1 0 LCD_EN

10 0 LCD_RW

Procedimento para limpar (apagar) o LCD

PASSO 5: comando para limpar (apagar) o LCD

EEL7020 Sistemas Digitais

26/26

Escrita no LCD da placa DE2 da Altera

Tutorial

http://www.feng.pucrs.br/~jbenfica/curso/tutorial_lcd.pdf

http://www.lisha.ufsc.br/~bezerra/disciplinas/Microprocessadores/tools/LCD/LCD_APLICATIVO.html

Você também pode gostar

- AB Funcoes Logicas Portas LogicasDocumento105 páginasAB Funcoes Logicas Portas LogicasTomas MouryAinda não há avaliações

- Apostila CLP CompletaDocumento87 páginasApostila CLP CompletaEvandro Duarte100% (1)

- Cont Adores V HDLDocumento10 páginasCont Adores V HDLKaciane MarquesAinda não há avaliações

- Projeto Simulacao Quartus2Documento48 páginasProjeto Simulacao Quartus2shillaramAinda não há avaliações

- Correção Do FP - WEGDocumento40 páginasCorreção Do FP - WEGGuilherme Villaça Mendes de OliveiraAinda não há avaliações

- Harmônicos e Fator de PotênciaDocumento161 páginasHarmônicos e Fator de PotênciashillaramAinda não há avaliações

- Wanderleycardoso-Apostila FPGADocumento79 páginasWanderleycardoso-Apostila FPGAshillaramAinda não há avaliações

- SEP 1 - Cap 3 Item 3.1-4 - Capacitancia e Susceptancia CapacitivaDocumento23 páginasSEP 1 - Cap 3 Item 3.1-4 - Capacitancia e Susceptancia CapacitivawaynemarquesAinda não há avaliações

- Comparativo Entre Transformadores A Óleo e A SecoDocumento5 páginasComparativo Entre Transformadores A Óleo e A SecoshillaramAinda não há avaliações

- Aula FPGA-VHDL 2009-2Documento24 páginasAula FPGA-VHDL 2009-2paulouchoa11Ainda não há avaliações

- Microcontroladores PIC para Iniciantes (Poluidor - Blogspot.com)Documento169 páginasMicrocontroladores PIC para Iniciantes (Poluidor - Blogspot.com)Felipe FadanniAinda não há avaliações

- CirdcDocumento72 páginasCirdcshillaramAinda não há avaliações

- UFSC - Fundamentos de Controle ClássicoDocumento210 páginasUFSC - Fundamentos de Controle ClássicoasdfgAinda não há avaliações

- Comandos ElétricosDocumento61 páginasComandos ElétricosshillaramAinda não há avaliações

- Apostila de Circuitos2Documento13 páginasApostila de Circuitos2shillaramAinda não há avaliações

- Esquemas AterramentoDocumento15 páginasEsquemas AterramentorobertoAinda não há avaliações

- Cap 12Documento11 páginasCap 12Claudemir Francisco BarbosaAinda não há avaliações

- Integral Definida e Calculo de CentroideDocumento13 páginasIntegral Definida e Calculo de CentroideshillaramAinda não há avaliações

- TransistoresDocumento50 páginasTransistoresdigaosylvaAinda não há avaliações

- Prova TeoriaDocumento3 páginasProva TeoriaDaniel BodrukAinda não há avaliações

- Matriz Computac A o 20181 Wmo4iirt7oblw5c11012018Documento1 páginaMatriz Computac A o 20181 Wmo4iirt7oblw5c11012018Silas SenaAinda não há avaliações

- Bancada Didática para Acionamento E Controle de Motores Ca Controlada Por DSC Programado em Ambiente Matlab / SimulinkDocumento12 páginasBancada Didática para Acionamento E Controle de Motores Ca Controlada Por DSC Programado em Ambiente Matlab / SimulinkMario MarcioAinda não há avaliações

- Registros e Arquivos (Aula 12)Documento14 páginasRegistros e Arquivos (Aula 12)torresdfAinda não há avaliações

- Aula 02 - Conceitos Linguagem C - Prog EstáticaDocumento36 páginasAula 02 - Conceitos Linguagem C - Prog EstáticaacauanAinda não há avaliações

- Dicas de Livros para ProgramadoresDocumento8 páginasDicas de Livros para Programadoreseduardocchagas2920Ainda não há avaliações

- Aula #03 - Programação - Tipos de Dados e VariáveisDocumento38 páginasAula #03 - Programação - Tipos de Dados e VariáveisHelena Batista LafayAinda não há avaliações

- Árvores Binárias - Slides IFRS Osório - Gabriel MoraesDocumento35 páginasÁrvores Binárias - Slides IFRS Osório - Gabriel MoraesGabriel MoraesAinda não há avaliações

- Aula 03 - Stored Procedures PDFDocumento13 páginasAula 03 - Stored Procedures PDFEnza Rafaela De Sampaio FerreiraAinda não há avaliações

- RobóticaDocumento21 páginasRobóticaPriscila ComparsiAinda não há avaliações

- C# - Avançado 2Documento18 páginasC# - Avançado 2ped.carangolaAinda não há avaliações

- Cap 5Documento14 páginasCap 5gustavo.bitencourtAinda não há avaliações

- TCC - EngenhariaDocumento52 páginasTCC - EngenhariaCaroline MaulAinda não há avaliações

- Apostila - Linguagem de Programação IDocumento106 páginasApostila - Linguagem de Programação Ibruno queirozAinda não há avaliações

- STEP 7 - Trabalhando Com o Parameter DataDocumento9 páginasSTEP 7 - Trabalhando Com o Parameter DataEvando PereiraAinda não há avaliações

- 1 Introdução A Programação PDFDocumento103 páginas1 Introdução A Programação PDFruca_m_noronhaAinda não há avaliações

- Apostila LinuxDocumento67 páginasApostila LinuxsilbezeAinda não há avaliações

- Atividade Objetiva 3 - Estrutura e Modelagem de DadosDocumento9 páginasAtividade Objetiva 3 - Estrutura e Modelagem de Dadoswinrar online100% (2)

- Tutorial ARMDocumento92 páginasTutorial ARMNikolas LibertAinda não há avaliações

- Lista de Exercícios para A 2 ResolvidaDocumento3 páginasLista de Exercícios para A 2 ResolvidaLuis Otavio TrindadeAinda não há avaliações

- FORTRAN ApostilaDocumento99 páginasFORTRAN ApostilaJonathan TeixeiraAinda não há avaliações

- HdlsDocumento48 páginasHdlsCarlos BraiaAinda não há avaliações

- Plantadeiras: Código: 0501091731Documento61 páginasPlantadeiras: Código: 0501091731Lojão dos LedsAinda não há avaliações

- Vetores Matrizes StringsDocumento8 páginasVetores Matrizes Stringsnossa cenaAinda não há avaliações

- 13 InterfacesDocumento25 páginas13 InterfacesRonaldo MeloAinda não há avaliações

- Teste de Desenvolvimento - MobileDocumento6 páginasTeste de Desenvolvimento - MobileGildo RodriguesAinda não há avaliações

- Matriz SimetricaDocumento2 páginasMatriz SimetricaPaolaGomezAinda não há avaliações

- Teste Aula 05Documento8 páginasTeste Aula 05Marcelo CaramAinda não há avaliações

- Fovat GroupDocumento102 páginasFovat GroupJerciley PontesAinda não há avaliações

- Treinamento Oracle 1Z0-071Documento209 páginasTreinamento Oracle 1Z0-071Claudio CamargoAinda não há avaliações