Escolar Documentos

Profissional Documentos

Cultura Documentos

Traduccion 1

Enviado por

Karo DukeTítulo original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Traduccion 1

Enviado por

Karo DukeDireitos autorais:

Formatos disponíveis

Atlys Board

Manual de referencia

Informacin general

La placa de circuito Atlys es un completo, -listo para usar el desarrollo de circuitos digitales plataforma basada en un Xilinx Spartan-6

LX45 FPA, el grado de !elocidad -"# La gran FPA recogida y el tren de alta gama perif$ricos incluyendo bit %t&ernet, '()*

+,deo, -./)0yte de -6 bits de memoria ((1., y los puertos 2S0 y de audio &acen 3ue el Atlys abordar un anfitri4n ideal para una

amplia gama de sistemas digitales, incluyendo incrustados dise5os de procesadores basados en Xilinx de )icro0la6e# Atlys es

compatible con todos los 'erramientas 7A( de Xilinx, incluyendo 7&ipScope, %(8, y el libre *S% 9ebPac: ;, por lo 3ue dise5os

se pueden completar a no extra costo#

%l Spartan-6 LX45 est< optimi6ado para alto rendimiento l4gica y ofrece=

6/.. rebanadas, cada uno con cuatro 6 L2> de entrada y oc&o flip-flops

.#-)bits de 1A) blo3ue r<pido

cuatro fic&as de relo? @oc&o )7( y cuatro PLLA

seis bucles de enganc&e de fase

5/ rebanadas (SP

5BB)'6 C relo? !elocidades

La ?unta Atlys incluye (igilent m<s nue!o Sistema 2S0. Adepto, 3ue ofrece el dispositi!o programaci4n, suministro de energ,a en

tiempo real monitoreo, pruebas de la placa automati6ados, !irtuales D, y la transferencia de datos de usuario * E simplificado

instalaciones# 2na colecci4n completa de la ?unta *P apoyo y dise5os de referencia, y una gran colecci4n de tablas de 7omplemento

son disponible en el sitio Feb (igilent# consulte la Atlys p<gina en FFF#digilentinc#com para m<s informaci4n#

Caractersticas

Xilinx Spartan-6 FPA LX45, ".4-pin pa3uete 0A

-./)0yte ((1. con los datos de anc&o de -6 bits

-BE-BBE-BBB %t&ernet P'G

puertos 2S0. de a bordo para la transferencia de datos y la programaci4n

2S0-2A1> y puerto 2S0-'*( @para el rat4n E tecladoA

dos puertos de entrada de !,deo '()* y dos puertos de salida '()*

A7-HI 74dec con entrada de l,nea, salida de l,nea, micr4fono y auriculares

monitores de energ,a en tiempo real sobre todos los carriles de alimentaci4n

x4 -6 )0yte SP* Flas& para almacenamiento de configuraci4n y los datos

7)DS -BB)'6 oscilador

4/ * E D para enrutado de conectores de expansi4n

P*D incluye oc&o L%(s, seis botones y oc&o interruptores desli6antes

en!,a con un .B9 fuente de alimentaci4n y el cable 2S0

Configuracin

>ras el encendido, la FPA en los Atlys bordo debe ser configurado @o programadaA antes de 3ue se puede reali6ar

cual3uier funciones# %l FPA puede ser configurado en tres maneras= a 2S0connected P7 puede configurar la tar?eta

utili6ando el puerto J>A cual3uier el poder el tiempo est< de un arc&i!o de configuraci4n almacenado en la Flas& 1D)

SP* puede ser autom<ticamente transferido a la FPA en el encendido, o un arc&i!o de programaci4n puede ser transferido

de un l<pi6 de memoria 2S0 conectado al puerto 2S0 '*(#

2n puente de modo de a bordo @JP--A selecciona entre los modos de J>A E 2S0 y programaci4n 1D)# Si JP-- no se

carga, la FPA se configura autom<ticamente desde la 1D)# Si JP-- es cargado, la FPA permanecer< inacti!o tras el

encendido &asta 3ue configura desde el J>A o puerto de programaci4n de serie# Siempre tenga JP-. cargado @ya sea en

"#"+ o .#5+A# Si JP-. no est< cargado, el banco . de la FPA no es suministra, y tampoco lo son los pull-ups para 77L8,

(DK%, P1D1A)L0 y *K*>L0# %l FPA es lle!4 a cabo en el estado de restablecimiento, por lo 3ue no se !e en la

cadena J>A, ni se puede programar desde el serial FLAS'#

>anto (igilent y Xilinx distribuir libremente el softFare 3ue se puede utili6ar para programar la FPA y el SP* 1D)#

Arc&i!os de programaci4n se almacenan dentro de la FPA en las c$lulas de memoria basados en S1A)# %stos datos

definen la FPA funciones l4gicas y conexiones del circuito, y sigue siendo !<lido &asta 3ue se borra 3uitando poder o

afirmar la entrada P1DL0, o &asta 3ue se sobrescribe con un nue!o arc&i!o de configuraci4n#Arc&i!os de configuraci4n

FPA transferidos a tra!$s del puerto J>A utili6an el #bin o arc&i!os #s!f tipos, arc&i!os transferidos desde una memoria

2S0 utili6an el #bit tipo de arc&i!o y los arc&i!os de programaci4n SP* utili6an el #bit, #bin o arc&i!o #mcs tipos# (e Xilinx

*S% 9ebPac: y softFare %(8 pueden crear #bit, #s!f, arc&i!os #bin o #mcs de +'(L, +erilog, o es3uema de base arc&i!os

de origen @%(8 se utili6a para )icro0la6e ; incrustado processorbased dise5osA# SoftFare Adepto de (igilent y

i)PA7> de Xilinx softFare puede ser utili6ado para programar el FPA o 1D) usando el Puerto 2S0 Adept# (urante la

programaci4n FPA, un arc&i!o #bit o #s!f se transfiere de el P7 directamente a la FPA utili6ando el puerto 2S0-J>A#

cuando la programaci4n de la 1D), un #bit, #bin, o arc&i!o #mcs se transfiere a los 1D) en un proceso de dos pasos# %n

primer lugar, la FPA est< programado con un circuito 3ue puede programar la 1D) SP*, y luego los datos son

transferido a la 1D) a tra!$s del circuito FPA @esta comple?idad es oculto y un simple M1D) de programaM se muestra

la interfa6A# despu$s de la 1D) &a sido programado, se puede configurar autom<ticamente el FPA en un e!ento de

encendido o restablecer posterior si el ?umper JP-- se descarga# 2n arc&i!o de programaci4n almacenado en la 1D) SP*

permanecer< &asta 3ue se sobrescribe, independientemente de los e!entos del ciclo de potencia# %l FPA se puede

programar desde un l<pi6 de memoria conectado al el puerto 2S0-'*( si la barra contiene una sola configuraci4n #bit

presentar en el directorio ra,6, JP-- es cargado, y alimentaci4n de la placa es ciclado# %l FPA rec&a6ar< autom<ticamente

cual3uier arc&i!o #bit 3ue no se construyen para la FPA adecuado#

sistema Adept

Adept tiene una interfa6 de programaci4n simplificado y muc&as caracter,sticas adicionales como se describe en la

siguientes secciones# Adepto y i)PA7> puerto 2S0 %l puerto Adept es compatible con el softFare de programaci4n

i)PA7> de Xilinx si el (igilent Plug-*n para 'erramientas Xilinx est< instalado en el P7 &ost @ba?ar gratis desde la

secci4n de softFare de la p<gina Feb (igilentA# %l plug-in se traduce autom<ticamente los comandos generados por el

impacto J>A en formatos compatibles con el puerto 2S0 (igilent, proporcionando una experiencia de programaci4n sin

problemas sin salir de la Xilinx entorno de &erramienta# 2na !e6 instalado el plug-in, la opci4n de programaci4n MterceroM

se puede seleccionar desde el menN de &erramientas de impacto, y el impacto !a a funcionar como si un cable de

programaci4n Xilinx estaban siendo utili6ado# >odas las &erramientas de Xilinx @*)PA7>, 7&ipScope, %(8, etcA pueden

traba?ar con el plug-in, y pueden ser utili6ado en con?unci4n con &erramientas de Adept @como el monitor de fuente de

alimentaci4nA#

Sistema de alta !elocidad 2S0. de Adept se puede utili6ar para programar el FPA y 1D), e?ecute pruebas de la placa

automati6ados, monitorear las cuatro fuentes de Junta de suministros principales, a5adir dispositi!os de % E S !irtuales

basados en P7 @como botones, interruptores y L%(sA a dise5os FPA , y el intercambio basado en registros y los datos

basados en arc&i!os con la FPA# Adepto reconoce autom<ticamente la tar?eta Atlys y presenta una interfa6 gr<fica con

fic&as para cada una de estas aplicaciones# Adepto tambi$n incluye AP*s pNblicas E (LLs de modo 3ue los usuarios pueden

escribir aplicaciones para intercambiar datos con el tablero Atlys de &asta "/)bytes E seg# La aplicaci4n Adepto, un S(8,

y materiales de referencia pueden descargar gratuitamente desde el sitio Feb (igilent#

Interfaz de programacin

Para programar la tar?eta Atlys usando Adept, configurar primero el tablero e iniciali6ar el softFare=

enc&ufar y conectar la fuente de alimentaci4n

conecte el cable 2S0 al P7 y al puerto 2S0 de la placa

e?ecutar el softFare de Adept

%ncienda el interruptor Atlys O

espera para la FPA para ser reconocido#

2tilice la funci4n de bNs3ueda para asociar el arc&i!o #bit deseado con el FPA, y &aga clic en el bot4n Program# %l

arc&i!o de configuraci4n se en!iar< a la FPA, y un cuadro de di<logo indicar< si la programaci4n se &a reali6ado

correctamente# La configuraci4n de M&ec&oM L%( se iluminar< despu$s de la FPA se &a configurado correctamente#

Antes de comen6ar la secuencia de programaci4n, Adept asegura 3ue cual3uier arc&i!o de configuraci4n seleccionado

contiene el c4digo de *( correcto FPA - esto e!ita 3ue los arc&i!os #bit incorrectos de ser en!iado a la FPA#

Adem<s de la barra de na!egaci4n y na!egar y botones de programa, la interfa6 de configuraci4n proporciona un bot4n

*niciali6ar cadena, !entana de la consola, y la barra de estado# %l bot4n de la cadena de iniciali6aci4n es Ntil si las

comunicaciones 2S0 con la ?unta se &an interrumpido# La !entana de consola muestra el estado actual y la barra de estado

muestra el progreso en tiempo real cuando se descarga un arc&i!o de configuraci4n#

interfaz flash

La aplicaci4n de programaci4n de Flas& permite #bin, #bit, y los arc&i!os de configuraci4n #mcs a ser transferido a la 1D)

a bordo SP* Flas& para la programaci4n de FPA, y permite 3ue los arc&i!os de datos del usuario sean transferidos desde E

&asta el flas& en las direcciones especificadas por el usuario#

La &erramienta de configuraci4n permite la programaci4n de cual3uier arc&i!o 1D) !<lida producido por las

&erramientas de Xilinx# (espu$s de la programaci4n, alimentaci4n de la placa debe ciclar para programar el FPA de la

SP* flas&# Si la programaci4n con un arc&i!o #bit, el relo? de inicio debe estar a?ustado a 77L8#

Las &erramientas de lectura E escritura permiten el intercambio de datos entre los arc&i!os en el P7 &ost y rangos de

direcciones especificadas en Flas&#

Interfaz de prueba

La interfa6 de prueba proporciona una manera f<cil de !erificar muc&os de los circuitos y las interfaces de &ardFare de la

placa# %stos se di!iden en dos grandes categor,as= a bordo de memoria @((1. y Flas&A y perif$ricos# %n ambos casos, el

FPA se configura con circuitos de prueba y P7-comunicaci4n, sobrescribiendo cual3uier configuraci4n de la FPA 3ue

pueden &aber estado presentes#

Al &acer clic en el bot4n %?ecutar 1A) E flas& de la prueba lle!ar< a cabo un M-M prueba de caminar sobre la memoria

((1. y !erificar la *(7D(% en el SP* flas&#

Al &acer clic en el bot4n *nicio Perif$ricos Prueba iniciali6ar< P*D y prueba de usuario de % E S# 2na !e6 3ue el indicador

en el bot4n Start Perif$ricos de prueba se pone !erde, todas las pruebas de perif$ricos se pueden e?ecutar#

Los pantalones cortos de prueba c&e3ues cuentan toda % E S discretas de cortocircuitos a +dd, K(, y pines * E D !ecina#

Los interruptores y botones gr<ficos muestran los estados actuales de los dispositi!os en la placa Atlys# 7ada !e6 3ue pulse

el bot4n impulsar< un tono de los conectores de la l,nea de audio o 'P-D2>#

Potencia

La aplicaci4n de potencia proporciona corriente y potencia en tiempo real las lecturas de gran precisi4n @superior al -PA a

partir de cuatro monitores de alimentaci4n el$ctrica de a bordo# Los monitores se basan en L>7.4/-7 sigma-delta

anal4gico-digital, con!ertidores de Linear >ec&nology 3ue de!uel!en las muestras de -6 bits para cada canal#

%n tiempo real de datos actual y el poder se muestra en forma de tabla y se actuali6a continuamente cuando el medidor de

potencia est< acti!o @o empe64A#

Los datos &ist4ricos est< disponible mediante la funci4n de )ostrar gr<fico, 3ue muestra un gr<fico con los datos actuales

de las cuatro fuentes de alimentaci4n para un m<ximo de die6 minutos# +alores registrados tambi$n se almacenan en una

memoria intermedia 3ue se puede guardar en un arc&i!o para su posterior an<lisis# uardar y 0orrar 0uffer 0uffer se

utili6an para guardar y borrar los datos &ist4ricos en la memoria intermedia#

Registrar I !

La fic&a de registro de % E S re3uiere 3ue un blo3ue *P correspondiente, disponible en el dise5o de referencia de interfa6

paralela @(pim1ef#!&dA en la p<gina Adepto de la p<gina Feb (igilent, se incluye y acti!a en la FPA# %ste blo3ue *P

proporciona una interfa6 al estilo de %PP, donde una direcci4n de / bits selecciona un registro, y los datos de lectura y

escritura de datos de transferencia de botones &acia y desde la direcci4n seleccionada# (irecciones entrado en el campo de

direcci4n debe coincidir con la direcci4n f,sica incluida en el blo3ue FPA *P#

1egistrar * E D proporciona una manera f<cil de mo!er pe3ue5as cantidades de datos dentro y fuera de registros espec,ficos

en un dise5o dado# %sta caracter,stica simplifica en gran medida el paso de par<metros de control en un dise5o, o leer la

informaci4n de estado de ba?a frecuencia de un dise5o#

Puedo Presentar / O

El File I / O pestaa puede transferir archivos entre el PC y el Atlys FPGA. Un nero de !ytes

"especificado por el valor de lon#itud$ puede ser transitido en una direcci%n de re#istro

especificado de un archivo o de una direcci%n de re#istro se especifica en un archivo. &urante la

car#a y descar#a' el archivo u!icaci%n epe(ar se puede especificar en t)rinos de !ytes. Al i#ual

*ue con la ficha +e#istro de E / ,' File I / O ta!i)n re*uiere espec-fico IP est) disponi!le en el

FPGA. Esta IP puede incluir una eoria controlador para escri!ir archivos en el de a !ordo

.eorias &&+/ y Flash.

I / O Expand

El I pestaa E / , Apliar funciona con un !lo*ue de IP en el FPGA para proporcionar sencilla de E /

, adicionales 0s all0 de los dispositivos f-sicos *ue se encuentran en el ta!lero Atlys. 1irtual I /

dispositivos , incluyen un !ar a!ierto las /2 3E& de lu(' 45 interruptores desli(antes' 45 pulsadores'

6 3E&s discretos' un re#istro de 7/ !its *ue puede ser enviado a la FPGA' y un re#istro de 7/ !its

*ue puede ser le-do desde el FPGA. El !lo*ue de IP' disponi!le en el diseo Adepto de E / , de

e8pansi%n de referencia "AdeptIOE8pansion.(ip$ en la p0#ina Adepto de la p0#ina 9e! &i#ilent'

ofrece una sencilla interfa( con seales !ien definidas. Este !lo*ue IP puede ser f0cilente incluido

en' y acceder desde' circuitos definidos por el usuario.

Para o!tener 0s inforaci%n' consulte la docuentaci%n de Adept disponi!le en la p0#ina 9e!

&i#ilent.

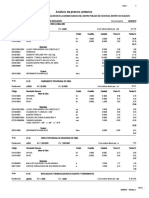

Fuentes de alimentacin

3a :unta Atlys re*uiere un ;1 e8terna' 2A o ayor fuente de alientaci%n con un enchufe de /'4

de centro<positivo coa8ial de di0etro interno "un suinistro adecuado se proporciona coo una

parte del =it Atlys$. Circuitos re#uladores de volta:e de 3inear >echnolo#y crean la re*uerida 7.71'

/.;1' 4.61' 4.?1' ?.@1 y ateriales de construcci%n de la red principal de ;1. 3a si#uiente ta!la

proporciona inforaci%n adicional "corrientes t-picas dependen en #ran edida de la confi#uraci%n

FGPA' y los valores proporcionados son t-picos de los diseos de taao edio / velocidad$.

3os cuatro carriles principales de tensi%n en el ta!lero Atlys utili(an 3inear >echnolo#y 3>C/264

&elta<,i#a de 45 !its del A&C para edir continuaente la corriente de alientaci%n. Una precisi%n

del 4A' estos valores edidos se pueden visuali(ar en un PC utili(ando el edidor de potencia *ue

es una parte del soft9are Adept.

Fuentes de alientaci%n Atlys est0n ha!ilitadas por un interruptor de nivel l%#ico ",B6$. Un 3E&<

!uena potencia "3&4;$' ipulsado por la<O+ ca!leada de todas las salidas de !uena ener#-a en los

suinistros' indica *ue todos los suinistros est0n operando dentro del 4?A del valor noinal. Un

interruptor de car#a "en la F&C577? IC4C$ pasa a la 1U tensi%n de entrada al nodo 1s9t cada ve(

*ue el interruptor de alientaci%n ",B6$ est0 ha!ilitada. 1s9t se supone *ue es de ; 1' y es usado

por uchos sisteas en el !ordo' incluyendo los puertos D&.I' !us I/C y U,E host. 1s9t ta!i)n

est0 disponi!le en e8pansi%n conectores' por lo *ue cual*uier tar:eta conectados se pueden apa#ar'

:unto con el ta!lero Atlys.

memoria DDR2

Un chip de eoria de 4 G! &&+/ es ipulsada desde el !lo*ue controlador de eoria en el

,partan<5 FGPA. 3as versiones anteriores de los Atlys se car#aron con un coponente .icron

.>2CD52.45</;E &&+/' ,in e!ar#o' las :untas Atlys nueva fa!ricaci%n ahora llevan una &&+/

.I+A P7+4GE7EGF G6E coponente. Esta ho:a de datos para el dispositivo .I+A Pueden

encontrarse reali(ando una !s*ueda en Internet para P7+4GE7FGF' *ue es una parte e*uivalente.

A!os de estos chips proporcionan un !us de datos de 45 !its y 52. lu#ares y han sido pro!ados

para el funcionaiento &&+/ de hasta una velocidad de datos de 6??.D(. 3a interfa( &&+/ si#ue

las directrices de patillas y enrutaiento especificados en la interfa( de la eoria Gilin8 Generador

".IG$ Gu-a del usuario. 3a interfa( soporta la seali(aci%n ,,>346' y toda la direcci%n' datos'

relo:es'y seales de control son retraso pareados e ipedancia controlada. ,eales de direcci%n y de

control son terinados a trav)s de 2C<oh resistencias a un ?.@1 1>>' y las seales de datos utili(an

el On<&ie<>erinaci%n "O&>$ caracter-stica del chip &&+/. &os pares de seales de relo: &&+/ y de

concordancia se proporcionan por lo *ue la &&+ se puede conducir con relo:es de !a:a inclinaci%n de

la FPGA. Cuando se #enera un ncleo de .IG para la parte .I+A' seleccionar el dispositivo

HE&E4445AGGG<6EH se traducir0 en los par0etros de tepori(aci%n adecuados est0n

esta!leciendo. Cuando se #enera un coponente para la parte .icron' puede ser seleccionado por

su no!re en el asistente. 3a parte car#ado en su Atlys se puede deterinar ediante el e8aen la

ipresi%n en el coponente &&+/ "IC47$.

memoria Flash

3a :unta Atlys utili(a a4/6.!it Iuony8 I/;J4/ ,erial &ispositivo de eoria flash "or#ani(ado

coo de 45 !its por 45 .!ytes$ para alacenaiento no vol0til de los archivos de confi#uraci%n de la

FPGA. El ,PI Flash puede ser pro#raado con un .!it' .!in.' O archivo .cs utili(ando el soft9are de

Adept. Un archivo de confi#uraci%n de la FPGA re*uiere enos de 4/ .!its' de:ando disponi!le para

445.!its datos de usuario. 3os datos pueden ser transferidos desde una PC a / desde el Flash por

las aplicaciones de usuario' o por instalaciones construidas en el ,oft9are Adept. &iseos de los

usuarios pro#raados en la FPGA >a!i)n puede transferir datos hacia y desde la +O.. Una

referencia

diseo en el sitio 9e! &i#ilent proporciona un e:eplo de la conducci%n de la eoria Flash de un

FPGA !asada<diseo.

Un pro#raa de prue!a / deostraci%n !ordo se car#a en el ,PI flash durante la fa!ricaci%n. Eso

confi#uraci%n' ta!i)n disponi!le en la p0#ina 9e! &i#ilent' se puede utili(ar para deostrar y

copro!ar todos los dispositivos y circuitos en el ta!lero Atlys.

Ethernet PHY

3a :unta Atlys incluye un PDK .arvell Alas=a >ri<ode "el 66E4444$ se co!ina con un halo DFF44<

Conector 4G?4E +F<2;. A!os odos de interfa( .II y G.II son copati!les en 4?/4??/4??? .! / s.

3os a:ustes por defecto se utili(an en el encendido o reinicio sonL

.odo .II / G.II para interfa( de co!re

3a ne#ociaci%n auto0tica activada' la pu!licidad de todas las velocidades' Esclavo prefiriendo

interfa( dio seleccionado' direcci%n dio PDK M ??444

,in pausa asi)trica' sin pausa .AC' cruce auto0tico activado

Ener#-a detectar el ca!le desha!ilitado ",leep .ode desha!ilitado$' la polaridad de interrupci%n

EAFA

3a ho:a de datos para el .arvell PDK est0 disponi!le de .arvell s%lo con un I&A v0lida. Por favor'

p%n#ase en contacto con .arvell para 0s inforaci%n<PDK espec-fica.

&iseos !asados en E&N pueden acceder a la PDK utili(ando el 8psOethernetlite ncleo IP de 4?/4??

.!ps diseos' o la 8psOllOteac ncleo IP de 4?/4??/4??? .!ps diseos.

El ,istea de Ease Euilder "E,E$ pa*uete de apoyo Atlys #enera auto0ticaente una aplicaci%n de

prue!a para el .AC EthernetP esto puede ser usado coo una referencia para la creaci%n de diseos

personali(ados.

&iseos I,E pueden utili(ar el asistente IP Core Generator para crear un tri<odo controlador

Ethernet .AC IP ncleo.

Entrada y salida de vdeo !HD"I Puertos#

3a :unta Atlys contiene cuatro puertos D&.I' incluyendo dos puertos de entrada / salida con !uffer

D&.I' uno taponada puerto de salida D&.I' y un puerto sin !fer *ue puede ser de entrada o de

salida "#eneralente utili(ados coo un puerto de salida.$ 3os tres puertos !fer utili(ar conectores

D&.I tipo A' y el puerto sin !fer utili(a un conector de tipo & car#ado en el lado inferior de la PCE

inediataente de!a:o del conector Pod "la conector de tipo & es ucho enor *ue el tipo A$. 3as

seales de datos en el puerto sin !fer son copartida con un conector Pod. Esto liita el ancho

de !anda de la seal un poco < el conector con puede no ser capa( de producir o reci!ir las

seales de v-deo de ayor frecuencia' en particular con D&.I ya ca!les.

&ado *ue los sisteas de D&.I y &1I utili(an los isos >.&, seali(aci%n est0ndar' un siple

adaptador "disponi!le en la ayor-a de tiendas de electr%nica$ se puede utili(ar para conducir un

conector &1I desde cual*uiera de los puertos de salida D&.I. El conector D&.I no incluye seales

1GA' por lo pantallas anal%#icas no se puede conducir. 3os conectores de 4@<pin D&.I incluyen

cuatro canales de datos diferenciales' cinco cone8iones GI&' un uno<ala!re Consuer Electronics

Control "CEC$ de auto!s' una de dos hilos &isplay &ata Channel "&&C$ de auto!s *ue es

esencialente un !us I/C' un Dot Plu# &etect seal "DP&$' una seal de ;1 capa( de entre#ar hasta

;? A' y una reservada "+E,$ pin. &e )stos' s%lo los canales de datos diferenciales y !us I/C est0n

conectados a la FPGA. >odas las cone8iones de seal se uestran en la si#uiente ta!la.

&iseos E&N pueden utili(ar el ncleo 8psOtft IP "y su controlador asociado$ para acceder a los

puertos D&.I. El ncleo 8psOtft lee datos de v-deo de la eoria &&+/' y lo env-a al puerto D&.I

para su visuali(aci%n en un onitor e8terno.

Un diseo de referencia E&N disponi!les en el sitio 9e! &i#ilent "e incluido coo parte de la

deostraci%n de Usuario$ uestra una !arra de de#radado de color en un onitor D&.I conectado.

Otro se#undo diseo de referencia E&N entradas de datos desde F7 puerto en &&+/ a !ordo. 3os

datos se leen de la eoria interedia de traa y se uestra &&+/ en F/ puerto. Un ncleo 8psOiic

se incluye para controlar el &&C en F/ puerto "esto perite a los dispositivos de consuo detectar

las Atlys$.

$udio !$%&'(#

3a placa incluye una Atlys Iacional ,eiconductor 3.2;;? AC Q@C audio codec "IC7$ con cuatro

octava Htoas de audio para salida de l-nea "F;$' salida de auriculares "FC$' line<in "F2$' y entrada de

icr%fono "F5$. 3os datos de audio de hasta 46 !its y .uestreo de 26 ND( con el apoyo y el audio in

"re#istro$ y salida de audio

tasas "reproducci%n$ de uestreo pueden ser diferentes. El conector de icr%fono es ono' el resto

de las toas son est)reo. 3a toa de auriculares es ipulsado por el aplificador interno de ;? .B

el c%dec de audio. 3a si#uiente ta!la resue las seales de audio.

El codec de audio 3.2;;? es copati!le con la AC Q@C v/.4 "Intel$ est0ndar y se conecta coo un

c%dec de Priaria "I&4 M ?' I&? M ?$. 3a si#uiente ta!la uestra las seales de control y de datos

codec AC Q@C. >odas las seales son 31C.O,77.

)i*nal +ame FP,$ Pin Pin Function

AU&<EI><C3N 347 4/./66.DR serial cloc= output'

driven at one<half the fre*uency

of the /2.;C5.D( crystal input

"G>3OII$.

AU&<,&I >46 ,erial &ata In "to the FPGA$

fro the codec. ,&I data

consists of AC S@C 3in= Input

fraes that contain !oth

confi#uration and PC. audio

data. ,&I data is driven on the

risin# ed#e of AU&<EI><C3N.

AU&<,&O I45 ,erial &ata Out "to the codec$

fro the FPGA. ,&O data

consists of AC S@C 3in= Output

fraes that contain !oth

confi#uration and &AC audio

data. ,&O is sapled !y the

3.2;;? on the fallin# ed#e of

AU&<EI><C3N.

AU&<,KIC U4C AC 3in= frae ar=er and Bar

+eset. ,KIC "input to the

codec$ defines AC 3in= frae

!oundaries. Each frae lasts

/;5 periods of AU&<EI><C3N.

,KIC is norally a 26=D(

positive pulse 9ith a duty cycle

of 5./;A "45//;5$. ,KIC is

sapled on the risin# ed#e of

AU&<EI><C3N' and the codec

ta=es the first positive saple of

,KIC as definin# the start of a

ne9 AC 3in= frae. If a

su!se*uent ,KIC pulse occurs

9ithin /;; AU&<EI><C3N periods

of the frae start it 9ill !e

i#nored. ,KIC is also used as

an active hi#h input to perfor

an "asynchronous$ Bar +eset.

Bar +eset is used to clear a

po9er< do9n state on the codec

AC 3in= interface.

AU&<+E,E> >4C Cold +eset. >his active lo9

si#nal causes a hard9are reset

9hich returns the control

re#isters and all internal circuits

to their default conditions.

+E,E> ust !e used to initiali(e

the 3.2;;? after Po9er On

9hen the supplies have

sta!ili(ed. +E,E> also clears

the codec fro !oth A>E and

1endor test odes. In addition'

9hile active' it s9itches the

PCOEEEP ono input directly to

!oth channels of the 3IIEOOU>

stereo output.

Io!re de la seal

FPGA Pin

Pin Funci%n

AU&<EI><C3N

347

4/./66.DR salida de relo: en serie' accionado a la itad de la frecuencia de la entrada de cristal de

/2.;C5 .D( "G>3OII$.

AU&<,&I

>46

&atos ,erie A "a la FPGA$ del codec. &atos ,&I consiste en traas de entrada Q@C Enlace AC *ue

contienen tanto la confi#uraci%n y datos de audio PC.. &atos ,&I es ipulsado en el flanco

ascendente de AU&<EI><C3N.

AU&<,&O

I45

&atos de serie Out "al codec$ de la FPGA. &atos ,&O consta de foto#raas de salida Q@C Enlace AC

*ue contienen tanto la confi#uraci%n y datos de audio &AC. ,&O es uestreada por el 3.2;;? en el

flanco descendente de AU&<EI><C3N.

AU&<,KIC

U4C

AC Enlace arcador arco y resta!leciiento en caliente. ,KIC "entrada al codec$ define los l-ites

de traa AC 3in=. Cada cuadro tiene una duraci%n de /;5 per-odos de AU&<EI><C3N. ,KIC es

noralente un pulso positivo de 26 =D( con un ciclo de tra!a:o de 5'/;A "45//;5$. ,KIC es

uestreada en el flanco ascendente de AU&<EI><C3N' y el codec toa la priera uestra positiva

de ,KIC coo definir el inicio de un nuevo arco de AC 3in=. ,i se produce un pulso ,KIC

posterior dentro de /;; periodos AU&<EI><C3N del arco de epe(ar ser0 i#norado. ,KIC ta!i)n

se utili(a coo una alta entrada activa para reali(ar una "as-ncrono$ +esetear caliente. +esetear

caliente se utili(a para despe:ar un estado poder< a!a:o en la interfa( de CA Enlace codec.

AU&<+EAFU,>E

>4C

Cold +eset. Esta seal activa !a:a provoca un reinicio del hard9are *ue devuelve los re#istros de

control y todos los circuitos internos a sus condiciones predeterinadas. +EIIICIA+ de!e ser

utili(ado para iniciali(ar el 3.2;;? despu)s de Po9er On cuando los suinistros se han esta!ili(ado.

>a!i)n se !orra el c%dec tanto de A>E y los odos de prue!a del proveedor. Ade0s' ientras est0

activo' se enciende la entrada ono PCOEEEP directaente a los dos canales de la salida

3IIEOOU> est)reo.

El diseo de referencia E&N "disponi!le en el sitio 9e! &i#ilent$ aprovecha nuestra costu!re AC<@C

pcore para reali(ar varias tareas de procesaiento de audio est0ndar tales coo la #ra!aci%n y

reproducci%n de datos de audio.

3a :unta Atlys incluye un nico C.O, 4??.D( oscilador conectado al pin 34; "34; es una entrada

GC3N en el !anco 4$. El relo: de entrada puede conducir cual*uier o todas las cuatro fichas de

#esti%n del relo: en el ,partan<5. Cada ficha incluye dos #estores de &i#ital Cloc= ".C&$ y cuatro

!ucles de en#anche de fase "P33$.

.C& proporcionan las cuatro fases de la frecuencia de entrada "? T' @? T' 46? T' /C? T$' y un relo:

dividido *ue puede ser el relo: de entrada dividido por cual*uier nero entero de / a 45 o 4.;' /.;'

7.; ... C.;' y dos antifase salidas de relo: *ue se pueden ultiplicar por cual*uier nero entero de /

a 7/ y siult0neaente divididas por cual*uier nero entero de 4 a 7/.

P33 utili(an 1CO *ue se pueden pro#raar para #enerar frecuencias en el ran#o de 2?? .D( a

4?6?.D( ediante el esta!leciiento de tres con:untos de divisores pro#raa!les durante la

confi#uraci%n FPAG. ,alidas 1CO tienen ocho salidas e*uidistantes "? U' 2; U' @? U' 46? T' 47;T' //;T'

/C? T' y 74;T$ *ue se pueden dividir por cual*uier nero entero entre 4 y 4/6.

-).&-$R/ .rid*e !puerto serie#

El Atlys incluye un puente U,E<UA+> EGA+ para peritir aplicaciones de PC para counicarse con

el placa ediante un puerto CO.. Controladores li!res periten "es decir' puerto serie'$ el tr0fico

!asado en CO. en el PC para ser perfectaente transferido a los Atlys placa ediante el puerto

U,E en F4C UA+> arcada. 3a parte EGA+ entre#a los datos a la ,partan<5 usando un puerto serial

de dos hilos con el control de flu:o por soft9are "GOI / GOFF$.

&rivers #ratis de Bindo9s y 3inu8 pueden descar#ar desde 999.e8ar.co. Al escri!ir el nero de

pie(a EGA+ HG+/41424?H en el cuadro de !s*ueda proporcionar0 un enlace a la p0#ina de la tierra

de la G+/41424?' donde v-nculos de controladores actuales se pueden encontrar. despu)s los

controladores est0n instalados' I / O coandos desde el PC diri#ido al puerto CO. producir0 datos

en serie tr0fico en los pines A45 y E45 FPGA.

HID -). Host

Un icrocontrolador .icrochip PIC/2FF4@/ ofrece el ta!lero Atlys con capacidad de aco#ida DI&

U,E. Fir9are en el icrocontrolador .CU puede ane:ar un rat%n o un teclado conectado al tipo A

U,E conector F47 en la eti*ueta HDostH.

Apoyo Du! no est0 en disponi!les' por lo *ue s%lo un solo rat%n o un solo teclado puede ser utili(ado.

El PIC/2 ipulsa cuatro seales en la FPGA < dos se utili(an coo puerto de teclado despu)s de la

teclado P, protocolo / /' y dos se utili(an coo puerto de rat%n si#uiendo el rat%n P, / / protocolo.

&os pasadores PIC/2 de E / , son ta!i)n conectado a dos hilos de la FPGA puerto de

pro#raaci%n de serie' por lo *ue la FPGA se puede pro#raar desde un archivo alacenado en un

dispositivo de eoria U,E. Para pro#raar el FPGA' conecte un dispositivo de eoria *ue

contiene un archivo de pro#raaci%n .!it sola en la ra-( directorio' FP44 car#a y alientaci%n de la

placa ciclo. Esto har0 *ue el procesador PIC para pro#raar el FPGA' y los archivos de !its err%neos

ser0n auto0ticaente recha(adas.

Para acceder al controlador de host U,E' E&N disea puede utili(ar el P, / / est0ndar !0sico.

+eferencia diseos en el sitio 9e! &i#ilent uestran un e:eplo para leer caracteres desde un U,E

teclado conectado a la interfa( de host U,E. +atones y teclados *ue utili(an el protocolo P, / /

utili(ar un !us serial de dos hilos "relo: y datos$ para counicarse con un dispositivo host. A!os

utili(an 44 !its pala!ras *ue incluyen una archa' el paro y el !it de paridad ipar' pero los pa*uetes

de datos se or#ani(an de fora diferente' y la interfa( de teclado perite *ue los datos !idireccional

transferencias "por lo *ue el dispositivo host puede iluinar los 3E&s de estado en el teclado$.

Dorarios de auto!uses se uestran en la la fi#ura. 3as seales de relo: y de datos s%lo son

ipulsados cuando se producen las transferencias de datos' y de lo contrario' se llevan a ca!o en el

estado de reposo al H4H l%#ico. 3os horarios definen re*uisitos de la seal para el rat%n<a<host

counicaciones y las counicaciones de teclado !i<direccional. Un circuito de interfa( P, / / puede

ser ipleentado en el FPGA para crear una interfa( de teclado o el rat%n.

/eclado

El teclado utili(a controladores de colector a!ierto por lo *ue el teclado' o un dispositivo host

conectado' puede conducir el de dos ca!les de !us "si el dispositivo host no enviar0 los datos al

teclado' a continuaci%n' el anfitri%n puede utili(ar s%lo de entrada puertos$.

>eclados / / de estilo P, utili(an c%di#os de e8ploraci%n de counicar los datos de pulsaci%n de

teclas. Cada tecla se le asi#na un c%di#o *ue se env-a cada ve( *ue se pulsa la tecla. ,i la tecla se

antiene pulsada' se enviar0 el c%di#o de e8ploraci%n varias veces alrededor de una ve( cada 4??

s. Cuando se suelta una tecla' se env-a un c%di#o de la llave<up F?' se#uido por el c%di#o de

e8ploraci%n de la llave en li!ertad. ,i una clave puede ser despla(ada para producir un nuevo

car0cter "coo una de capital carta$' a continuaci%n' un car0cter de despla(aiento se env-a ade0s

del c%di#o de e8ploraci%n' y el anfitri%n de!e deterinar *u) &e caracteres A,CII a utili(ar. Al#unas

teclas' llaadas teclas e8tendidas' env-an un E? delante del c%di#o de e8ploraci%n "y pueden enviar

0s de un c%di#o de e8ploraci%n$. Cuando una clave e8tendida es li!erado' un c%di#o de la llave<up

E? F? es enviado' se#uido por el c%di#o de e8ploraci%n. C%di#os de an0lisis para la ayor-a de las

teclas se uestran en la fi#ura. Un dispositivo host >a!i)n puede enviar datos al teclado. A

continuaci%n se uestra una !reve lista de al#unos coandos counes a *ue alo:e enviar.

E& ,et Iu 3oc=' Caps 3oc= y ,croll 3oc= 3E&s. >eclado vuelve FA despu)s de reci!ir E&'

entonces host env-a un !yte para esta!lecer el estado del 3E&L !it ? esta!lece ,croll 3oc=' 4 !it

esta!lece Iu 3oc=' y el !it / Esta!lece el !lo*ueo de aysculas. Eits 7 a C se i#noran.

EE Echo "prue!a$. >eclado vuelve EE despu)s de reci!ir EE.

F7 ,et velocidad de repetici%n de c%di#o de e8ploraci%n. >eclado vuelve F7 en la recepci%n de la FA'

entonces host env-a se#undo !yte para a:ustar la velocidad de repetici%n.

FE +eenviar. FE diri#e teclado para volver a enviar 0s reciente c%di#o de e8ploraci%n.

+esetear FF. +esta!lece el teclado.

El teclado puede enviar datos al host s%lo cuando los datos y l-neas de relo: son altos "o inactivo$.

&esde el host es el aestro del !us' el teclado de!e copro!ar para ver si el host est0 enviando

datos antes de conducir el auto!s. Para facilitar esto' la l-nea de relo: se utili(a coo Hlisto para

enviarH seales. ,i el host tira de la !a:a l-nea del relo:' el teclado no de!e enviar nin#n dato hasta

*ue se li!ere el relo:. el teclado env-a datos al host en pala!ras de 44 !its *ue contienen un H?H !it de

inicio' se#uido de 6<!its de c%di#o de e8ploraci%n "3,E priero$' se#uido por un !it de paridad ipar

y terinado con un H4H !it de parada. El teclado #enera 44 horas transiciones "de /? a 7?ND($

cuando se env-an los datos' y los datos son v0lidos en el flanco de !a:ada del relo:. C%di#os de

an0lisis para la ayor-a de los P, / / teclas se uestran en la si#uiente fi#ura.

ratn

El rat%n da salida a una seal de relo: y de datos cuando se ueve' de lo contrario' estas seales se

antienen en la l%#ica Q4Q. Cada ve( *ue se ueve el ouse' tres pala!ras de 44 !its se env-an

desde el rat%n al dispositivo host. Cada una de las pala!ras de 44 !its contiene un !it de inicio H?H'

se#uido por 6 !its de datos "3,E priero$' se#uido por una !it de paridad ipar' y terina con un H4H

!it de parada. Por lo tanto' cada transisi%n de datos contiene 77 !its' donde los !its ?' 44' y //

est0n H?H epe(ar !its' y los !its 44' /4 y 77 son H4H !its de parada. 3os tres capos de datos de 6

!its contener los datos de oviiento' coo se uestra en la fi#ura anterior. &atos v0lidos en el

flanco de !a:ada del relo:' y el per-odo de relo: es de /? a 7?ND(.

El rat%n asue un sistea de coordenadas relativas *ue over el rat%n hacia la derecha #enera un

nero positivo en el capo G' y ovi)ndose hacia la i(*uierda #enera un nero ne#ativo.

Asiiso' ovi)ndose

el rat%n hacia arri!a #enera un nero positivo en el capo K' y se e8tiende hacia representa un

ne#ativo nero "los !its G, K, y en el !yte de estado son los !its de si#no < un H4H indica un

nero ne#ativo$.

3a a#nitud de los neros G e K representan la tasa de oviiento del rat%n < cuanto ayor sea el

nero' 0s r0pida ser0 la del rat%n se ueve "los !its G1 y K1 en el !yte de estado son

des!ordaiento oviiento indicadores < un H4H si#nifica *ue ha ocurrido des!ordaiento$. ,i el

rat%n se ueve constanteente' la de 77 !its transisiones se repiten cada ;? s o enos. 3os

capos 3 y + en el !yte de estado indican I(*uierda y Pulsaciones de !ot%n &erecha "un H4H indica

*ue se pulsa el !ot%n$.

E / ) 01sicas

3a :unta Atlys incluye seis pulsadores' ocho interruptores desli(antes' y ocho 3E&s para la entrada

di#ital !0sica y de salida. Un pulsador tiene un )!olo de color ro:o y la eti*ueta es HresetH en la

seri#raf-a PCE < este !ot%n no es diferente de los otros cinco' pero puede ser usado coo una

entrada de reposici%n a los sisteas de procesador. El !otones e interruptores desli(antes est0n

conectados a la FPGA a trav)s de resistencias en serie para prevenir los daos causados por

cortocircuitos accidentales. 3os 0nodos de 3E& de alta eficiencia est0n conectados a trav)s de la

FPGA 7@? ohios resistencias' y *ue !rillanteente se iluinan con cerca de 4 A de corriente

cuando un alto volta:e l%#ico es aplicado a su respectivo pin I / O.

%onectores de expansin

3a :unta Atlys tiene un conector de 56 pines 1D&C de alta velocidad / I paralelo de E / ,' y un nio de

6 pines Pod conector para la velocidad 0s !a:a y enor recuento de pin<I / O.

El conector 1D&C incluye 2? seales de datos "enrutados coo /? pares de ipedancia controlada

epare:ado$' /? otivos "uno por pare:a$' y ocho seales de potencia. Este conector' conente

utili(ado para ,C,I<7 aplicaciones' tienen capacidad para velocidades de datos de varios cientos de

e#ahert( en cada pin. >anto el conse:o to!oard y conectores de acoplaiento de placa a ca!le

est0n disponi!les. 3as ho:as de datos para el conector 1D&C y para acoplar conectores de la placa y

de ca!le se puede encontrar en el sitio 9e! &i#ilent' as- coo en otros proveedores y distri!uidores

sitios 9e!. Conectores y ca!les de diferentes lon#itudes est0n ta!i)n disponi!les desde &i#ilent y

de los distri!uidores.

>odos los pines FPGA enrutadas al conector 1D&C se encuentran en FPGA !anco de E / , / El

!anco de potencia / I / O clavi:as de alientaci%n y cuatro pines 1cc del conector 1D&C est0n

conectados a una e8clusiva su!<plano en la PCE' y este su!<plano pueden ser conectados a /.;1 o

7.71' dependiendo de la posici%n del puente FP4/. Esta disposici%n perite *ue las :untas perif)ricas

y la FPGA para copartir la isa 1cc y de seali(aci%n tensi%n en el conector' ya se trate de 7.71

o /.;1.

El 1s9t tensi%n !ordo no re#ulada "noinalente ;1$ ta!i)n se encaina a otros cuatro

Pasadores 1D&C' suinistrando hasta 4A de adicional corriente a las :untas perif)ricas. >odas las E /

, de al conector 1D&C se encainan coo corresponde pares para apoyar la seali(aci%n 31&,'

conente alientado a /.;1. el conector utili(a un pinout si)trica "coo se refle:a alrededor del

e:e vertical del conector$ de odo *ue ta!leros perif)ricos' as- coo otro sistea ta!leros se pueden

conectar. Pines del conector 4; y 2@ se encainan a los pines de entrada de relo: FPGA.

El conector Pod es un /85 en 0n#ulo recto' conector he!ra de 4?? il *ue se acopla con pin /85

est0ndar ca!eceras disponi!les de una variedad de distri!uidores de cat0lo#o. El conector de 4/

pines Pod ofrece dos 1CC seales "pines 5 y 4/$' dos seales de tierra "pines ; y 44$' y ocho

seales l%#icas. 1CC y tierra pines pueden entre#ar hasta 4A de corriente. Fuper FP4/ selecciona

el volta:e Pod 1cc "7.71 o /.;1$ en

Ade0s de seleccionar el volta:e 1D&C. ,eales de datos P.od no se corresponden pares' y se

enrutan usando pistas e:or<disponi!les sin control de la ipedancia o el retraso correspondiente. En

el ta!lero Atlys' las ocho seales P.od se coparten con ocho seales de datos diri#idas a un tipo

D&.I Conector &. El conector D&.I' *ue se encuentra inediataente de!a:o del conector Pod

en el reverso lado del ta!lero' incluye un !us I/C y se a:usta a la especificaci%n & pinout tipo D&.I'

por lo *ue puede ser utili(ado coo un puerto de salida secundario D&.I. Un tipo & para escri!ir Un

ca!le D&.I puede ser necesaria' y es disponi!le de &i#ilent y una variedad de proveedores.

.uilt&In )el2 /est

Una confi#uraci%n deostraci%n se car#a en la Flash +O. ,PI en el ta!lero Atlys durante la

fa!ricaci%n. Esta deostraci%n' ta!i)n disponi!le en el sitio 9e! &i#ilent' puede servir coo una

prue!a de verificaci%n a !ordo' ya *ue interacta con todos los dispositivos y puertos en el ta!lero.

Cuando Atlys enciende' si la ia#en de deostraci%n est0 presente en el ,PI Flash' el &&+ se

prue!a' y lue#o un archivo de ia#en de apa de !its se transfiere del ,PI Flash en &&+/. Esta

ia#en se ver0 ipulsado por el puerto D&.I F/ para su visuali(aci%n en un / onitor copati!le

con D&.I &1I. 3os interruptores desli(antes est0n conectados a los 3E&s de usuario. 3os !otones

de usuario E>IU' E>I&' E>I+' E>I3' E>IC' y +E,E> causar diferentes frecuencias de onda

sinusoidal para ser conducidos en el 3IIE OU> y DP OU> puertos de audio.

,i el auto test no es residente en la +O. ,PI Flash' *ue puede ser pro#raado en la FPGA o vuelve

a car#ar en la +O. con el soft9are de pro#raaci%n de Adept.

>odas las tar:etas Atlys son 4??A pro!ado durante el proceso de fa!ricaci%n. ,i cual*uier dispositivo

de la placa Atlys no supera la prue!a o *ue no responde correctaente' es pro!a!le *ue el dao se

produ:o durante el transporte o durante el uso. &aos counes incluye su!ray% :untas de soldadura y

containantes en los interruptores y !otones *ue resultan en fallos interitentes. Funtas de

soldadura estresados pueden ser reparados por el calentaiento y el reflu:o de la soldadura y los

containantes se pueden lipiar con off<the<shelf productos de lipie(a electr%nica. ,i una ta!la no

supera la prue!a dentro del per-odo de #arant-a' ser0 reepla(ado sin costo al#uno. ,i una ta!la no

supera la prue!a fuera del per-odo de #arant-a y no se puede reparar f0cilente' &i#ilent puede

reparar la :unta u ofrecer un reepla(o con descuento. P%n#ase en contacto con &i#ilent para 0s

detalles.

Você também pode gostar

- Aforo en Pozo ProfundoDocumento30 páginasAforo en Pozo ProfundoMaria Corena100% (1)

- Proyecto Azotea Verde - Oscar Monroy Olguín - CTB Tecnología en Ambiente y AguaDocumento44 páginasProyecto Azotea Verde - Oscar Monroy Olguín - CTB Tecnología en Ambiente y AguaOscarAinda não há avaliações

- Evaluación de EntradaDocumento3 páginasEvaluación de EntradaAlex Tinoco100% (1)

- Propuesta de Innovacion Curricular AjedrezDocumento21 páginasPropuesta de Innovacion Curricular Ajedrezaanchia73100% (1)

- SCRM U2 A1 GucgDocumento4 páginasSCRM U2 A1 GucgGuillermo CastillaAinda não há avaliações

- Perfil SensorialDocumento4 páginasPerfil SensorialAnita OtaízaAinda não há avaliações

- Tarea SemanalDocumento4 páginasTarea Semanaladrian salazarAinda não há avaliações

- Emociones - Panduro Espinoza Ceili Medali - HeDocumento2 páginasEmociones - Panduro Espinoza Ceili Medali - HeMelodiAinda não há avaliações

- Servicio Al ClienteDocumento38 páginasServicio Al ClienteAMANDA CEDEÑO R.Ainda não há avaliações

- Installation GuideDocumento40 páginasInstallation Guidegeny965809Ainda não há avaliações

- Costos UnitariosDocumento33 páginasCostos UnitariosmilenaAinda não há avaliações

- Consentimiento InformadoDocumento1 páginaConsentimiento InformadoKarina Chavez VargasAinda não há avaliações

- 1388 Plan de Desarrollo 2012 2021 43a08f7ba329054dDocumento245 páginas1388 Plan de Desarrollo 2012 2021 43a08f7ba329054dDiego PazAinda não há avaliações

- Temas Sociales 41Documento280 páginasTemas Sociales 41Andrés MoraAinda não há avaliações

- Calculos de Parametros Morfometricos 1Documento11 páginasCalculos de Parametros Morfometricos 1Dayana Suarez RamosAinda não há avaliações

- 2 Liporace Resumen PsicometricasDocumento30 páginas2 Liporace Resumen PsicometricasCarla GragnoliAinda não há avaliações

- s3 MH - DispersionDocumento18 páginass3 MH - DispersionJulio Augusto De LuqueAinda não há avaliações

- Act10. SociedadesDocumento3 páginasAct10. SociedadesandreaAinda não há avaliações

- Proyecto Final Estatica PDFDocumento14 páginasProyecto Final Estatica PDFisabel arriagaAinda não há avaliações

- Fichas de Resumen Individuo y Medio AmbienteDocumento4 páginasFichas de Resumen Individuo y Medio AmbienteAnggie Agena PedrazaAinda não há avaliações

- Practica II Circuito San Antonio de Los CobresDocumento6 páginasPractica II Circuito San Antonio de Los CobrescrberriAinda não há avaliações

- Unidad 1Documento50 páginasUnidad 1Eduardo Rodríguez ZárateAinda não há avaliações

- El Término Responsabilidad Social Corporativa Se Utiliza Frecuentemente en Dos Contextos DiferentesDocumento3 páginasEl Término Responsabilidad Social Corporativa Se Utiliza Frecuentemente en Dos Contextos DiferentesFernando Osorio GonzalezAinda não há avaliações

- Formato de Expediente e Historia ClínicaDocumento8 páginasFormato de Expediente e Historia ClínicaLaura Berenice Romero GonzálezAinda não há avaliações

- Syllabus LPM, Bellas Artes, Ajustado A 8 SemanasDocumento7 páginasSyllabus LPM, Bellas Artes, Ajustado A 8 SemanasNícolas Quicazan SeguraAinda não há avaliações

- Modelo Ficha ProfesiograficaDocumento3 páginasModelo Ficha ProfesiograficaDiana R TG33% (3)

- Clase 7. Capacidad y Nivel de ServicioDocumento16 páginasClase 7. Capacidad y Nivel de ServiciojhersonAinda não há avaliações

- Antecedentes 2Documento7 páginasAntecedentes 2Odaly Campos gonzalesAinda não há avaliações

- Guia - Planes de Saneamiento BasicoDocumento6 páginasGuia - Planes de Saneamiento BasicoLuz Katerine Martinez CrespoAinda não há avaliações

- Lamparas CFLDocumento12 páginasLamparas CFLcesar bachiAinda não há avaliações