Escolar Documentos

Profissional Documentos

Cultura Documentos

Hef4066bf 4 Bilateral Switch

Enviado por

huvillamilDireitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

Hef4066bf 4 Bilateral Switch

Enviado por

huvillamilDireitos autorais:

Formatos disponíveis

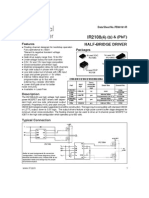

INTEGRATED CIRCUITS

DATA SHEET

For a complete data sheet, please also download:

The IC04 LOCMOS HE4000B Logic

Family Specifications HEF, HEC

The IC04 LOCMOS HE4000B Logic

Package Outlines/Information HEF, HEC

HEF4066B

gates

Quadruple bilateral switches

Product specification

File under Integrated Circuits, IC04

January 1995

Philips Semiconductors

Product specification

HEF4066B

gates

Quadruple bilateral switches

disabled and a high impedance between Y and Z is

established (OFF condition).

DESCRIPTION

The HEF4066B has four independent bilateral analogue

switches (transmission gates). Each switch has two

input/output terminals (Y/Z) and an active HIGH enable

input (E). When E is connected to VDD a low impedance

bidirectional path between Y and Z is established (ON

condition). When E is connected to VSS the switch is

The HEF4066B is pin compatible with the HEF4016B but

exhibits a much lower ON resistance. In addition the ON

resistance is relatively constant over the full input signal

range.

Fig.1 Functional diagram.

Fig.2 Pinning diagram.

PINNING

HEF4066BP(N): 14-lead DIL; plastic (SOT27-1)

E0 to E3

enable inputs

HEF4066BD(F): 14-lead DIL; ceramic (cerdip)

(SOT73))

Y0 to Y3

input/output terminals

Z0 to Z3

input/output terminals

HEF4066BT(D): 14-lead SO; plastic (SOT108-1)

( ): Package Designator North America

APPLICATION INFORMATION

An example of application for the HEF4066B is:

Analogue and digital switching

Fig.3 Schematic diagram (one switch).

January 1995

Philips Semiconductors

Product specification

HEF4066B

gates

Quadruple bilateral switches

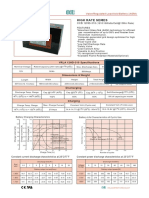

RATINGS

Limiting values in accordance with the Absolute Maximum System (IEC 134)

Power dissipation per switch

max.

100

mW

For other RATINGS see Family Specifications

DC CHARACTERISTICS

Tamb = 25 C

VDD

V

SYMBOL

5

ON resistance

ON resistance

MIN.

TYP. MAX.

CONDITIONS

350

2500

En at VDD

80

245

Vis = VSS to VDD

15

60

175

see Fig.4

115

340

En at VDD

10

RON

50

160

Vis = VSS

15

40

115

see Fig.4

120

365

En at VDD

10

RON

65

200

Vis = VDD

15

50

155

see Fig.4

ON resistance

25

En at VDD

between any two

10

10

Vis = VSS to VDD

channels

15

see Fig.4

nA

nA

ON resistance

OFF state leakage

10

RON

RON

IOZ

current, any

10

channel OFF

15

200 nA

2,25

1 V

4,50

2 V

6,75

2 V

En input voltage

LOW

VIL

10

15

VDD

V

SYMBOL

+25

MAX. MAX.

Quiescent device

current

5

10

IDD

15

Input leakage current at En

January 1995

15

IIN

Iis = 10 A

see Fig.9

Tamb (c)

40

En at VSS

CONDITIONS

+85

MAX.

1,0

1,0

7,5 A

2,0

2,0

15,0 A

input combinations;

4,0

4,0

30,0 A

VI = VSS or VDD

300

1000 nA

En at VSS or VDD

VSS = 0; all valid

Philips Semiconductors

Product specification

HEF4066B

gates

Quadruple bilateral switches

Fig.4 Test set-up for measuring RON.

En at VDD

Iis = 200 A

VSS = 0 V

Fig.5 Typical RON as a function of input voltage.

NOTE

To avoid drawing VDD current out of terminal Z, when switch current flows into terminals Y, the voltage drop across the

bidirectional switch must not exceed 0,4 V. If the switch current flows into terminal Z, no VDD current will flow out of

terminals Y, in this case there is no limit for the voltage drop across the switch, but the voltages at Y and Z may not

exceed VDD or VSS.

January 1995

Philips Semiconductors

Product specification

HEF4066B

gates

Quadruple bilateral switches

AC CHARACTERISTICS (1), (2)

VSS = 0 V; Tamb = 25 C; input transition times 20 ns

VDD

V

SYMBOL

TYP.

MAX.

Propagation delays

Vis Vos

HIGH to LOW

5

10

tPHL

15

5

LOW to HIGH

10

tPLH

15

10

20

ns

10

ns

10

ns

10

20

ns

10

ns

10

ns

note 3

note 3

Output disable times

En Vos

HIGH

10

80

160

ns

65

130

ns

60

120

ns

80

160

ns

70

140

ns

15

70

140

ns

En Vos

40

80

ns

HIGH

10

20

40

ns

15

15

30

ns

45

90

ns

20

40

ns

15

15

30

ns

0,25

10

0,04

15

0,04

tPHZ

15

5

LOW

10

tPLZ

note 4

note 4

Output enable times

LOW

Distortion, sine-wave

response

Crosstalk between

any two channels

Crosstalk; enable

input to output

OFF-state

feed-through

ON-state frequency

response

January 1995

10

tPZH

tPZL

MHz

10

MHz

15

MHz

mV

10

50

mV

15

mV

MHz

10

MHz

15

MHz

MHz

10

90

MHz

15

MHz

note 4

note 4

note 5

note 6

note 7

note 8

note 9

Philips Semiconductors

Product specification

HEF4066B

gates

Quadruple bilateral switches

VDD

V

Dynamic power

dissipation per

package (P)

TYPICAL FORMULA FOR P (W)

800 fi + (foCL) VDD 2

10

3 500 fi + (foCL) VDD

15

10 100 fi + (foCL) VDD

where

fi = input freq. (MHz)

fo = output freq. (MHz)

CL = load capacitance (pF)

(foCL) = sum of outputs

VDD = supply voltage (V)

Notes

1. Vis is the input voltage at a Y or Z terminal, whichever is assigned as input.

2. Vos is the output voltage at a Y or Z terminal, whichever is assigned as output.

3. RL = 10 k to VSS; CL = 50 pF to VSS; En = VDD; Vis = VDD (square-wave); see Figs 6 and 10.

4. RL = 10 k; CL = 50 pF to VSS; En = VDD (square-wave);

Vis = VDD and RL to VSS for tPHZ and tPZH;

Vis = VSS and RL to VDD for tPLZ and tPZL; see Figs 6 and 11.

5. RL = 10 k; CL = 15 pF; En = VDD; Vis = 12 VDD(p-p) (sine-wave, symmetrical about 12 VDD); fis = 1 kHz; see Fig.7.

6. RL = 1 k; Vis = 12 VDD(p-p) (sine-wave, symmetrical about 12 VDD);

V os (B)

20 log ------------------- = -50 dB; E n (A) = V SS ; E n ( B ) = V DD ; see Fig. 8.

V is ( A )

7. RL = 10 k to VSS; CL = 15 pF to VSS; En = VDD (square-wave); crosstalk is Vos (peak value); see Fig.6.

8. RL = 1 k; CL = 5 pF; En = VSS; Vis = 12 VDD(p-p) (sine-wave, symmetrical about 12 VDD);

V os

20 log --------- = -50 dB; see Fig. 7.

V is

9. RL = 1 k; CL = 5 pF; En = VDD; Vis = 12 VDD(p-p) (sine-wave, symmetrical about 12 VDD);

V os

20 log --------- = -3 dB; see Fig. 7.

V is

Fig.6

January 1995

Fig.7

Philips Semiconductors

Product specification

HEF4066B

gates

Quadruple bilateral switches

Fig.8

Fig.9

January 1995

Philips Semiconductors

Product specification

HEF4066B

gates

Quadruple bilateral switches

Fig.10 Waveforms showing propagation delays from Vis to Vos.

(1) Vis at VDD

(2) Vis at VSS.

Fig.11 Waveforms showing output disable and enable times.

January 1995

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.

Você também pode gostar

- 4052Documento9 páginas4052Brzata PticaAinda não há avaliações

- Hef4053 PDFDocumento9 páginasHef4053 PDFSiêu Nhân Bụng MỡAinda não há avaliações

- HEF4052B: 1. General DescriptionDocumento22 páginasHEF4052B: 1. General DescriptionmasetampanAinda não há avaliações

- Data Sheet: 74HC/HCT4316Documento15 páginasData Sheet: 74HC/HCT4316alguien1972Ainda não há avaliações

- HEF40106B: 1. General DescriptionDocumento15 páginasHEF40106B: 1. General DescriptionyajujotosAinda não há avaliações

- Datasheet HFE4069 UBPDocumento7 páginasDatasheet HFE4069 UBPMarcos SouzaAinda não há avaliações

- Hef 4069Documento7 páginasHef 4069makkasiAinda não há avaliações

- 4051 PDFDocumento6 páginas4051 PDFyamaha640Ainda não há avaliações

- CD4051BCDocumento10 páginasCD4051BCBakhtiar TiarAinda não há avaliações

- Contador A Decadas HEF4040B PDFDocumento14 páginasContador A Decadas HEF4040B PDFAnonymous hp6KDLIxEAinda não há avaliações

- HEF4051B: 1. General DescriptionDocumento23 páginasHEF4051B: 1. General Descriptioninside121Ainda não há avaliações

- HEF4069UBDocumento17 páginasHEF4069UBMitchell CifuentesAinda não há avaliações

- HEF4044B: 1. General DescriptionDocumento14 páginasHEF4044B: 1. General DescriptionNarendra BholeAinda não há avaliações

- IR2110/IR2113: High and Low Side DriverDocumento16 páginasIR2110/IR2113: High and Low Side DriverguiknopAinda não há avaliações

- HCF4051B: Single 8-Channel Analog Multiplexer/DemultiplexerDocumento11 páginasHCF4051B: Single 8-Channel Analog Multiplexer/DemultiplexerInes Ben TibaAinda não há avaliações

- HEF4104B: 1. General DescriptionDocumento14 páginasHEF4104B: 1. General DescriptionvelizarkoAinda não há avaliações

- cd4066 DatasheetDocumento9 páginascd4066 DatasheetAbubakar SidikAinda não há avaliações

- Ir 2010Documento17 páginasIr 2010Naveed AhmedAinda não há avaliações

- 74HC HCT4066 NXPDocumento27 páginas74HC HCT4066 NXPprpabst8514Ainda não há avaliações

- Dual 3-Channel Analog MultiplexerDocumento12 páginasDual 3-Channel Analog MultiplexerLuis AlbertoAinda não há avaliações

- LF347n PDFDocumento13 páginasLF347n PDFDiego PeñuelaAinda não há avaliações

- Hef 4094Documento17 páginasHef 4094vasconcelosrvAinda não há avaliações

- Data Sheet: HEF4093B GatesDocumento7 páginasData Sheet: HEF4093B GatesEvelyn Soledad Perez PerezAinda não há avaliações

- AO4702 N-Channel Enhancement Mode Field Effect Transistor With Schottky DiodeDocumento5 páginasAO4702 N-Channel Enhancement Mode Field Effect Transistor With Schottky Diodedreyes3773Ainda não há avaliações

- 74HC4051 74HCT4051: 1. General DescriptionDocumento31 páginas74HC4051 74HCT4051: 1. General DescriptiondonghungstbAinda não há avaliações

- Data Sheet: HEF4514B MSIDocumento6 páginasData Sheet: HEF4514B MSIdattariderAinda não há avaliações

- Data Sheet: 74HC4052 74HCT4052Documento27 páginasData Sheet: 74HC4052 74HCT4052JoniAinda não há avaliações

- 74HC4052NDocumento25 páginas74HC4052NMizael Medeiros dos SantosAinda não há avaliações

- DS16F95, DS36F95 EIA-485/EIA-422A Differential Bus TransceiverDocumento14 páginasDS16F95, DS36F95 EIA-485/EIA-422A Differential Bus Transceivervsc2012Ainda não há avaliações

- Ir 2109Documento25 páginasIr 2109Chavi AlmeidaAinda não há avaliações

- El5120 - El5220 - El5420Documento13 páginasEl5120 - El5220 - El5420Cristina NistorAinda não há avaliações

- +5V, Fail-Safe, 40Mbps, Profibus RS-485/ RS-422 TransceiversDocumento15 páginas+5V, Fail-Safe, 40Mbps, Profibus RS-485/ RS-422 TransceiversJuan Carlos HernandezAinda não há avaliações

- Hef 4093BDocumento6 páginasHef 4093BCristiano BruschiniAinda não há avaliações

- MC 14052 DatasheetDocumento12 páginasMC 14052 DatasheetgrooyoAinda não há avaliações

- CD4007Documento8 páginasCD4007renegonzalesvasquezAinda não há avaliações

- 4027BDocumento14 páginas4027BMarian AldescuAinda não há avaliações

- Ir 2110Documento17 páginasIr 2110Nguyen KhangAinda não há avaliações

- Ir2181 Igbt Driver PDFDocumento21 páginasIr2181 Igbt Driver PDFismifaizulAinda não há avaliações

- Data Sheet: HEF4511B MSIDocumento11 páginasData Sheet: HEF4511B MSIBruno SouzaAinda não há avaliações

- IR2110/IR2113 : High and Low Side Driver SDocumento15 páginasIR2110/IR2113 : High and Low Side Driver SPandu Sandi PratamaAinda não há avaliações

- HCC4051B/52B/53B HCF4051B/52B/53B: Analog Multiplexers-DemultiplexersDocumento17 páginasHCC4051B/52B/53B HCF4051B/52B/53B: Analog Multiplexers-DemultiplexersJaiprasad ReddyAinda não há avaliações

- General Description: Quad Bilateral SwitchDocumento23 páginasGeneral Description: Quad Bilateral Switchtotal4321Ainda não há avaliações

- Ir 2184Documento24 páginasIr 2184buiphuoclaiAinda não há avaliações

- Ir 2108Documento23 páginasIr 2108robertofurlancriAinda não há avaliações

- HEF4021B: 1. General DescriptionDocumento15 páginasHEF4021B: 1. General DescriptionEdgar_2008Ainda não há avaliações

- Quad 2-Channel Analog Multiplexer / Demultiplexer: BU4551B / BU4551BF / BU4551BFVDocumento6 páginasQuad 2-Channel Analog Multiplexer / Demultiplexer: BU4551B / BU4551BF / BU4551BFVmaldomattAinda não há avaliações

- Ir 2113Documento18 páginasIr 2113rohitsingh2909Ainda não há avaliações

- CD4051B, CD4052B, CD4053B: CMOS Analog Multiplexers/Demultiplexers With Logic Level Conversion FeaturesDocumento15 páginasCD4051B, CD4052B, CD4053B: CMOS Analog Multiplexers/Demultiplexers With Logic Level Conversion Featuresmithrandir91Ainda não há avaliações

- DS75176B/DS75176BT Multipoint RS-485/RS-422 Transceivers: Features DescriptionDocumento14 páginasDS75176B/DS75176BT Multipoint RS-485/RS-422 Transceivers: Features DescriptionVũ TưởngAinda não há avaliações

- EL7585AILDocumento18 páginasEL7585AILsorintvrAinda não há avaliações

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsAinda não há avaliações

- Diode, Transistor & Fet Circuits Manual: Newnes Circuits Manual SeriesNo EverandDiode, Transistor & Fet Circuits Manual: Newnes Circuits Manual SeriesNota: 4.5 de 5 estrelas4.5/5 (7)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Ainda não há avaliações

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1No EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Nota: 2.5 de 5 estrelas2.5/5 (3)

- Passive and Discrete Circuits: Newnes Electronics Circuits Pocket Book, Volume 2No EverandPassive and Discrete Circuits: Newnes Electronics Circuits Pocket Book, Volume 2Ainda não há avaliações

- Potenciometro DigitalDocumento9 páginasPotenciometro DigitalhuvillamilAinda não há avaliações

- DM74LS174 - DM74LS175 Hex/Quad D-Type Flip-Flops With Clear: General Description FeaturesDocumento8 páginasDM74LS174 - DM74LS175 Hex/Quad D-Type Flip-Flops With Clear: General Description FeatureshuvillamilAinda não há avaliações

- Remote Khamis AR 2003 PsDocumento15 páginasRemote Khamis AR 2003 PshuvillamilAinda não há avaliações

- Potenciometro DigitalDocumento9 páginasPotenciometro DigitalhuvillamilAinda não há avaliações

- 74ls273 Flip Flop Dx8 BitsDocumento7 páginas74ls273 Flip Flop Dx8 BitshuvillamilAinda não há avaliações

- 74LS640 641 642 645 Bus-Transceiver-8bitsDocumento4 páginas74LS640 641 642 645 Bus-Transceiver-8bitshuvillamilAinda não há avaliações

- 74hc244 Tristate 8bitsDocumento10 páginas74hc244 Tristate 8bitshuvillamilAinda não há avaliações

- NPN ST 13002Documento1 páginaNPN ST 13002huvillamilAinda não há avaliações

- NPN CD 13001Documento3 páginasNPN CD 13001huvillamilAinda não há avaliações

- 74hc244 Tristate 8bitsDocumento10 páginas74hc244 Tristate 8bitshuvillamilAinda não há avaliações

- 2N3904 MMBT3904: NPN General Purpose AmplifierDocumento7 páginas2N3904 MMBT3904: NPN General Purpose AmplifierhuvillamilAinda não há avaliações

- PIC17C4XDocumento241 páginasPIC17C4XhuvillamilAinda não há avaliações

- Service Manual Type LFCB102 Digital Current Differential RelayDocumento211 páginasService Manual Type LFCB102 Digital Current Differential RelayRinda_RaynaAinda não há avaliações

- FRENIC-Ace Instruction ManualDocumento112 páginasFRENIC-Ace Instruction ManualGanesh YadavAinda não há avaliações

- Basic Op-Amp CircuitsDocumento58 páginasBasic Op-Amp CircuitsNuman khanAinda não há avaliações

- Basic Electrical EngineeringDocumento11 páginasBasic Electrical EngineeringJeffrey MintahAinda não há avaliações

- Syllabus Kelas Kemahiran Radio AmaturDocumento1 páginaSyllabus Kelas Kemahiran Radio Amatursahajap100% (1)

- Scarecrow and Digital LockDocumento5 páginasScarecrow and Digital Lockmiguelcali100% (1)

- Starting Methods of DC MotorsDocumento13 páginasStarting Methods of DC MotorsZealWolfAinda não há avaliações

- Lecture - 1 - Overview - Part ADocumento14 páginasLecture - 1 - Overview - Part Afahad zubairAinda não há avaliações

- Sir10sa ManualDocumento48 páginasSir10sa ManualsersehAinda não há avaliações

- 6.arteche CVT HVDocumento8 páginas6.arteche CVT HVRAPRATSINAinda não há avaliações

- Elements of Technology (Eot) : Assignment 3Documento38 páginasElements of Technology (Eot) : Assignment 3nikitaAinda não há avaliações

- Astrorex D22 CatlougeDocumento9 páginasAstrorex D22 CatlougeManisankar DhabalAinda não há avaliações

- Switching Diode: 1N4531 / 1N4148 / 1N4150 / 1N4448Documento3 páginasSwitching Diode: 1N4531 / 1N4148 / 1N4150 / 1N4448Mario BasileAinda não há avaliações

- Wave Propagation On Metallic Transmission LinesDocumento3 páginasWave Propagation On Metallic Transmission LinesAnkita AgarwalAinda não há avaliações

- Electrical Switchgear ProtectionDocumento6 páginasElectrical Switchgear ProtectionIrfan AhmedAinda não há avaliações

- Yas 106 - Ats 1060Documento30 páginasYas 106 - Ats 1060廖智辉Ainda não há avaliações

- Model P4480 Kill A Watt Graphic Timer Operation Manual: Safety InstructionsDocumento9 páginasModel P4480 Kill A Watt Graphic Timer Operation Manual: Safety Instructionspulse59Ainda não há avaliações

- PX4211 1Documento3 páginasPX4211 1kalpanaAinda não há avaliações

- Opt Encoder 62CDocumento2 páginasOpt Encoder 62CPeter BirdAinda não há avaliações

- User's Manual ACS800-304 and ACS800-704 Diode Supply ModulesDocumento130 páginasUser's Manual ACS800-304 and ACS800-704 Diode Supply Moduleswjdysu100% (3)

- Solar Renewable EneggyDocumento12 páginasSolar Renewable EneggysamyektapolAinda não há avaliações

- Sierra Sable PDFDocumento13 páginasSierra Sable PDFAndres AcostaAinda não há avaliações

- Networj Ananlysis Question Paper of NIT RourkelaDocumento2 páginasNetworj Ananlysis Question Paper of NIT RourkelaImran WahidAinda não há avaliações

- MX882 B SpecsDocumento5 páginasMX882 B SpecssimonAinda não há avaliações

- NPDCL New Connection Application FormDocumento3 páginasNPDCL New Connection Application FormSangameshwar LabhishettyAinda não há avaliações

- High Rate Series: CCB 12HD-310Documento1 páginaHigh Rate Series: CCB 12HD-310orunmila123Ainda não há avaliações

- LF72 - 74Documento122 páginasLF72 - 74andres felipe de avila blancoAinda não há avaliações

- Vector Group of Transformer - Electrical Notes & ArticlesDocumento22 páginasVector Group of Transformer - Electrical Notes & ArticlesManoj Kumar PadmanabanAinda não há avaliações

- 2806 01 PDFDocumento33 páginas2806 01 PDFAmitAinda não há avaliações

- AAMCS S-Band AmplifierDocumento14 páginasAAMCS S-Band AmplifierMazlum ÜnalAinda não há avaliações