Escolar Documentos

Profissional Documentos

Cultura Documentos

An3805 PDF

Enviado por

Smitha NageshDescrição original:

Título original

Direitos autorais

Formatos disponíveis

Compartilhar este documento

Compartilhar ou incorporar documento

Você considera este documento útil?

Este conteúdo é inapropriado?

Denunciar este documentoDireitos autorais:

Formatos disponíveis

An3805 PDF

Enviado por

Smitha NageshDireitos autorais:

Formatos disponíveis

Freescale Semiconductor

Application Note

Document Number: AN3805

Rev. 1, 08/2009

MPC5121e SDHC Controller

by: Peter Kardos

Ronov Czech System Center

Czech Republic

Introduction

Contents

1

The purpose of this application note is to describe the

Secure Digital Host Controller implemented on

Freescales MPC5121e microcontroller. It describes how

to configure and use the host controller with standard

Secure Digital (SD) cards, and how, through minor

modifications in the existing software, driver support for

High Capacity cards (SDHC) can be added.

Portions of this application note were adapted from

material found at the SD Association website,

www.sdcard.org.

1.1

Objective

The objective of this application note is to describe the

necessary steps needed to add support for SDHC cards.

Freescale Semiconductor, Inc., 20082009. All rights reserved.

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Objective . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.2 Definition of SDHC . . . . . . . . . . . . . . . . . . . . . . . . . 2

Description of Host . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

2.1 SD Host Controller in MPC5121e . . . . . . . . . . . . . . 2

2.2 SD Host Controller Register List . . . . . . . . . . . . . . . 3

2.3 Signal Description and Connection Scheme . . . . . . 3

2.4 Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Description of Card . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.1 Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.2 Read/Write Procedures . . . . . . . . . . . . . . . . . . . . . 10

SDA Host and Card Specifications . . . . . . . . . . . . . . . . 13

4.1 Environmental . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

4.2 Reliability and Durability . . . . . . . . . . . . . . . . . . . . 13

4.3 Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Description of Host

1.2

Definition of SDHC

The Secure Digital High Capacity card is the new Secure Digital memory card based on the version 2.00

specification (v. 2.0), released by the Secure Digital Association (SDA). This new specification introduces

the ability to support SD cards capable of reaching higher capacities than before. The earlier SD standard,

version 1.x, supported a memory size of up to 4 GB. The revised SDHC v.2.0 standard extends the

supported capacity up to 32 GB. The new SDHC v.2.0 standard operates differently than standard SD v.1.x

cards this new format is not backwards-compatible with legacy SD-format host devices.

Products designed exclusively to support previous SD specifications v.1.x are not able to utilize SDHC

format cards. (Note that the SD controller within the MPC5121e is designed according to SD specification

v.1.x).

The SDHC specification v.2.0 calls for the card to be classified according to the minimal sustained Data

Transfer Speed (DTS) as follows:

Class 2: minimum sustained DTS of 2 MB/sec

Class 4: minimum sustained DTS of 4 MB/sec

Class 6: minimum sustained DTS of 6 MB/sec

SDHC cards are classified to guarantee a specific sustained DTS. This potentially saves consumers money,

as flash cards are priced not only according to capacity, but also according to transfer speed. Devices that

can utilize the 4 MB/s or 6 MB/s data transfer rates will offer significantly better performance when used

with Class 4 or Class 6 SDHC cards.

The SDHC standard was developed by the Secure Digital Association (SDA) to address the requirement

to support the growth in storage capacity of memory cards. The Secure Digital name was chosen because

of the ability to protect copyright content through Digital Rights Management (DRM). As a result of this

capability, it is a favored flash memory format in the audiovisual industry.

Description of Host

2.1

SD Host Controller in MPC5121e

The Secure Digital host controller module in the MPC5121e is capable of controlling MultiMedia Cards

(MMC), Secure Digital cards (SD), and SD I/O cards.

MPC5121e SDHC Controller, Rev. 1

2

Freescale Semiconductor

Description of Host

Secure Digital Host Controller

DMA

Interface

Transceiver

I/O Memory

Card

IP Bus

IP Gasket

IP Bus

Figure 1. MPC5121e System Interconnection with the Secure Digital Host Controller

2.2

SD Host Controller Register List

The SD host controller available in the MPC5121e uses these registers for self-configuration and for

communication with the connected card.

Table 1. SD Host Controller Register List

Address

2.3

Register

Base Address

SDHC Clock Control register (STR_STP_CLK)

Base Address + 04

SDHC Status register (STATUS)

Base Address + 08

SDHC Card Clock Rate register (CLK_RATE)

Base Address + 0C

SDHC Command Data Control register (CMD_DAT_CONT)

Base Address + 10

SDHC Response Time-Out register (RES_TO)

Base Address + 14

SDHC Read Time-Out register (READ_TO)

Base Address + 18

SDHC Block Length register (BLK_LEN)

Base Address + 1C

SDHC Number of Block register (NOB)

Base Address + 20

SDHC Revision Number register (REV_NO)

Base Address + 24

SDHC Interrupt Control register (INT_CNTR)

Base Address + 28

SDHC Command Number register (CMD)

Base Address + 2C

SDHC Command Argument register (ARG)

Base Address + 34

SDHC Command Response FIFO Access register (RES_FIFO)

Base Address + 38

SDHC Data Buffer Access register (DBA)

Signal Description and Connection Scheme

The Secure Digital Host Controller has six external pins. These are shown in Table 2.

MPC5121e SDHC Controller, Rev. 1

Freescale Semiconductor

Description of Host

Table 2. Signal Description

Signal

MMC_SD_CLK

Description

This signal is the MMC/SD/SDIO card clock signal. The direction is from host to card. The

frequency is referenced to the system clock.

CMD

This is a bidirectional signal. It is for card initialization and data transfer commands.

DAT3

This is a bidirectional signal for data transmission in 4-bit mode. This signal is not used in

1-bit mode. This signal is also used for card detect in both 4-bit and 1-bit modes.

DAT2

This is a bidirectional signal for data transmission or read wait in 4-bit mode and is for

read/wait when SDHC works in 1-bit mode.

DAT1

This is a bidirectional signal for data transmission or interrupt signal in 4-bit mode and is for

interrupt signal when SDHC works in 1-bit mode.

DAT0

This is a bidirectional signal for data transmission in both 1-bit mode and 4-bit mode.

Figure 2 shows how the card is connected to host in 1-bit or 4-bit mode. The connection is the same for

standard SD cards (v.1.x) and SDHC cards (v.2.0) as well.

RDAT

RCMD RWP

Write Protect

SD

Memory

Card

Host

VSS

CMD

DAT03

CLK

C1 C2

C3

9

12345678

SD

Memory

Card

Figure 2. Connecting the SD/SDHC Card to the Host

2.4

Initialization

To assure proper host and card functionality, each module must be initialized before usage. When

initializing the Secure Digital host controller, the user must obey these instructions.

2.4.1

IPS_BUS

When setting up a system with the MPC5121e, proper clocking must be assured. One of the important

clock sources is the IPS_BUS clock. This clock can be as high as 83 MHz, but Freescales recommendation

is to use 66 MHz. Its used as a peripheral clock source. For example, it is used for the CAN, I2C, timers,

PCSs, SDH controller, etc.

MPC5121e SDHC Controller, Rev. 1

4

Freescale Semiconductor

Description of Card

2.4.2

MMC_SD_CLK

This clock is derived from the IPS_BUS clock. The default startup clock specified in the SD standard is

100 kHz. Depending on the card type, this clock can be set as high as 25 MHz according to the v.1.x

specification, and can be set up to 50 MHz according to the v.2.0 specification. The actual highest clock

rate has to be identified from the card configuration data. This data is stored in the card. The user must take

care not to overclock the card. To set this clock, proper prescaler and divide values must be stored in the

SDHC_CARD_CLOCK_RATE register. These values depend on the desired card clock and the host clock

speed.

2.4.3

Timeout

As a part of the host setup, the user must set the appropriate timeouts for card operation. These timeouts

are used to report problems while accessing the card. The highest and recommended values are:

Response timeout SDHC_ RES_TO = 0xFF

Read timeout SDHC_READ_TO = 0xFFFF

These values determine the interval which detects response and read timeout. The clock starts counting

when the last bit of the command is sent.

2.4.4

Interrupts

If the user wishes to use interrupts instead of polling mode, the user must enable external interrupts to be

passed to the core. The user must also enable interrupt from the SD host controller in the internal

programmable interrupt controller (IPIC). Specific interrupt sources must be enabled in the Interrupt

Control register (SDHC_INT_CNTR) in the SD host controller. These interrupts are used to acknowledge

the completion of the send command, for example, command done, read done, write done.

Interrupts are enabled by writing 1 to the proper position in the interrupt control register in the SD host

controller and IPIC as well.

For further information on how to set the bus clock, SD host controller clocks, timeouts, enable interrupts,

and handler interrupts refer to Freescale document MPC5121ERM, MPC5121e Microcontroller Reference

Manual:

Chapter 2, System Configuration and Memory Map

Chapter 5, Clocks and Low-Power Modes, Section 5.3: Clock Control Module

Chapter 20, Integrated Programmable Interrupt Controller

Chapter 34, Secure Digital Host Controller

Description of Card

Before any communication with the card is done, it is absolutely necessary that the Secure Digital host

controller be initialized. The SD host controller in the MPC5121e conforms to the SD specification v.1.x

but can be forced to act and work as an SDHC capable controller. This is done during the card

identification and initialization process, as shown in Figure 3 and Figure 4.

MPC5121e SDHC Controller, Rev. 1

Freescale Semiconductor

Description of Card

The main difference in the initialization compared to the old v.1.x standard is the use of CMD8. This

command is not supported in the v.1.x specification and was introduced in the v.2.0 specification. It is used

to identify SD/SDHC cards that conform to the Secure Digital v.2.0 specification. Cards that conform to

the v.1.x specification will generate a timeout condition, or will reply with an error. Along with this

command a new type of response was implemented, response R7. Although the SD host controller in the

MPC5121e does not support response R7, a different but similar response can be used, R3.

Aside from the different initialization, the new protocol did include minor changes. One change is that the

SDHC card uses physical sector addressing (similar to ATA disk drives), but the SD cards use memory

addressing (similar to RAM).

Also, the SECTOR_SIZE was set to 512 bytes, in contrast to the variable size as described in v.1.x. To

assure compatibility and ease of use, it is recommended to use the same sector size with each card type.

For more information see the complete specification from the Secure Digital Association (SDA) at

www.sdcard.org.

3.1

Initialization

The steps in the figures are numbered and correspond to the steps given after the figures.

MPC5121e SDHC Controller, Rev. 1

6

Freescale Semiconductor

Description of Card

Start

1

Reset Card (CMD0)

2

Voltage Check (CMD8)

3

No Response

Error Response

Check

Response

Set Flag F8 = 0

Good Response

4

Set Flag F8 = 1

Set Flag F8 = 0

Unusable Card

5

Get SDIO OCR (CMD5)

Voltage Window = 0

No Response

Response Error

Check OCR

OCR is OK

7

Initialization (CMD5)

Set Voltage WIndow

8

Error

Response OK?

Good Response

Busy 9

Timeout

Check Busy

Set Flag SDIO = 1

Set Flag SDIO = 0

10

Set Flag SDIO = 0

Good Response & MP = 0

Check MP

Error Response

or MP = 1

A

Figure 3. New Initialization Described in V.2.0 Specification Part 1 of 2

MPC5121e SDHC Controller, Rev. 1

Freescale Semiconductor

Description of Card

F8 = 0

11

Check F8 Flag

F8 = 1

19

12

Get OCR (ACMD41)

Voltage Window = 0

Get OCR (ACMD41)

Voltage Window = 0

13

Check OCR

OCR OK

14

Response OK?

Busy16

27

Check OCR

21

SDIO = 0

Check SDIO

OCR OK

SDIO = 1

Initialization (ACMD41 HCS = 1)

Set Voltage Window

Initialization (ACMD41)

Set Voltage Window

15

20

OCR Fails

Error

22

Error

Response OK?

Good Response

Good Response

Timeout Timeout

23

Check Busy

Check Busy

Busy

Ready

Ready

CSS = 1

24

Check CSS

17

Not SD

Card

25

18

Standard Capacity

Legacy Card

CSS = 0

Normal Capacity

V.2.00 Card

26

28

High Capacity

V.2.00 Card

SDIO Only

Card

29

Unusable

Card

30

Get CID (CMD2)

31

Get RCA (CMD3)

End

Figure 4. New Initialization Described in V.2.0 Specification Part 2 of 2

1. SD bus mode is selected by CMD0 (card reset).

2. New CMD8 shall be issued after CMD0 to support High Capacity SD memory card.

3. Voltage check command enables the hosts to support future low-voltage specification. However, at

this time only one voltage is defined. Legacy cards and non-SD cards do not respond to CMD8. In

this case, set F8 to 0 (F8 is CMD8 valid flag used in step 11) and go to step 5. Only version 2.00

or higher cards can respond to CMD8. The host needs to check whether CRC of the response is

valid, and whether host-supplied voltage range (VHS) and check pattern in the argument are equal

MPC5121e SDHC Controller, Rev. 1

8

Freescale Semiconductor

Description of Card

to card-accepted voltage range (VCA) and check pattern in the response. Passing all these checks

results in CMD8 response OK. In this case, set F8 to 1 and go to step 5. If one of the checks fails,

go to step 4.

4. Initialization is stopped if CMD8 fails. The host driver should retry steps 1 to 3 one more time.

(This is not described in Figure 3).

5. SDIO Operation Condition register (OCR) is available by issuing CMD5 and setting the voltage

window (bits 23 to 0) in the argument to 0. SDIO initialization is not started. The OCR contains

the information about the supported voltage and the cards condition, either active or inactive.

6. No response means the card does not have the SDIO function. Set SDIO flag to 0 and go to step

11. If the card responds to CMD5 and the response is OK, go to step 7. If the response indicates

error, set SDIO flag to 0 and go to step 10. The SDIO flag indicates whether SDIO functions are

initialized or not.

7. The SDIO portion starts initialization by CMD5 and sets the supply voltage to the voltage window.

If the supplied voltage does not match the voltage window of the card, the card goes into inactive

state and does not return the response.

8. If no response or error response is received, set SDIO flag to 0 and go to step 10. If a valid response

is received, go to step 9.

9. Check busy status in the response. If busy status is negative, set the SDIO flag to 1 and go to step

10. Repeat from step 7 while busy is indicated. Detecting a timeout of 1 second exits the loop. In

this case, set SDIO flag to 0 and go to step 10.

10. Good response in this step means that all responses received at (6) and (8) are valid. When response

is good, MP (memory present) flag in the response can be checked. If the response is valid and

MP = 0, go to step 28. Otherwise, go to step 11.

11. Check F8 flag that was set in step 3. If CMD8 is executed correctly (F8 = 1), go to step 19.

Otherwise, go to step 12.

12. OCR is available by issuing ACMD41 with the voltage window (bit 23 to 0) in the argument set

to 0. Memory initialization is not started. A response of CMD55 (ACMD41) may indicate illegal

command error, because some SD cards do not recognize CMD8. The host driver should ignore

this error or issue CMD0 before ACMD41 to clear this error status.

13. If a response of CMD55 is not received, the card is not an SD card and processing goes to step 17.

If the card responds to CMD55, it may also respond to CMD41. If the responses of ACMD41 are

OK, go to step 14. Otherwise, go to step 27. A locked card can be detected by the card status in the

response of CMD55.

14. The memory portion starts initialization by issuing ACMD41 and setting the supply voltage to the

voltage window. If the supplied voltage does not match the voltage window of the card, the card

goes into inactive state and does not return the response.

15. If no response or error response is received, go to step 27. If a good response is received, go to step

16.

16. Check busy status in the response. If busy is released, go to step 18. Repeat from step 14 while a

status of busy is indicated. The interval of ACMD41 must be less than 50 ms. Detecting a timeout

of 1 second exits the loop and goes to step 27.

17. The host recognizes that the card is not an SD memory card and quits SD card initialization.

MPC5121e SDHC Controller, Rev. 1

Freescale Semiconductor

Description of Card

18. The host recognizes that the card is a v.1.x Standard Capacity SD memory card. Go to step 30.

19. OCR is available by issuing ACMD41 and setting the voltage window (bits 23 to 0) in the argument

to 0. Memory initialization is not started. A setting of High Capacity Support (HCS) does not affect

this operation.

20. If the card responds to CMD55, it may also respond to CMD41. If the responses of ACMD41 are

OK, go to step 21. Otherwise, go to step 27. A locked card can be detected by the card status with

a response of CMD55.

21. The memory portion starts initialization by issuing ACMD41 and setting the supply voltage to the

voltage window. If the supplied voltage does not match the voltage window of the card, the card

goes into an inactive state and does not return the response. HCS in the argument is set to 1, which

indicates supporting High Capacity Memory Card. This is the part where we force the SD host

controller to identify itself as SDHC capable, even when it is not. The default should be 0.

22. If no response or an error response is received, go to step 27. If a good response is received, go to

step 23.

23. Check busy status in the response. If busy is released, go to step 24. Repeat from step 21 while a

status of busy is indicated. The interval of ACMD41 must be less than 50 ms. Detecting a timeout

of 1 second exits the loop and goes to step 27.

24. CCS in the response is valid after busy is released. If CCS = 0, it indicates the Standard Capacity

SD memory card and processing goes to step 25. If CSS = 1, it indicates the High Capacity SD

memory card and processing goes to step 26. This information is stored in the OCR.

25. The host recognizes that the card is a Standard Capacity SD memory card. Optimal functions

defined in v.2.0 or higher are available. Go to step 30.

26. The host recognizes that the card is a High Capacity SD memory card. Go to step 30.

27. Check SDIO flag. If SDIO=1, go to step 28. Otherwise, go to step 29.

28. The host recognizes that the card is an SDIO-only card. Go to step 31.

29. The host recognizes that the card is unusable.

30. In the case of a memory card, CMD2 is issued to get card identification (CID) and processing goes

to step 31. The CID contains information about the vendor, serial number, manufacturing date, etc.

31. CMD3 is issued to get Relative Card Address (RCA). If the RCA number is 0, the host should issue

CMD3 again.

3.2

Read/Write Procedures

Until the content of the Card Specific Data (CSD) register is known by the host, the card clock rate must

remain at 100 kHz, because some cards may have operating frequency restrictions. The host issues

SEND_CSD (CMD9) to obtain the CSD register, for example block length, card storage capacity, and

maximum clock rate. Figure 5 shows a block diagram of the Data Transfer mode.

MPC5121e SDHC Controller, Rev. 1

10

Freescale Semiconductor

Description of Card

Card Identification

Mode

CMD3

CMD15

CMD0

Sending-data

state (data)

Data Transfer

Mode

From all states in

data-transfer mode

CMD13, CMD55

No state transition

in data-transfer mode

CMD12

Operation

Complete

CMD17, 18, 30, 56(r)

ACMD51

CMD7

Standby state

(stby)

CMD7

CMD4,

9, 10

Operation

Complete

Disconnect

state (dis)

CMD28,

29, 38

Transfer

state (tran)

CMD16, 32...37

ACMD6, 13, 42

ACMD22, 23

CMD24, 25, 26,

27, 42, 56(w)

Operation

Complete

Receive-data

state (rcv)

CMD7

Programming

state (prg)

CMD12 or

transfer end

CMD7

Figure 5. Description of Card States

CMD7 is used to select one SD card and place it in the transfer state. Only one SD card can be in the

transfer state at a given time. If a previously selected SD card is in the transfer state, its connection with

the host is released and it will move back to the standby state. When CMD7 is issued with the reserved

relative card address 0x0000, all cards transfer back to standby state. (Note that it is the responsibility

of the host to reserve RCA = 0 for card deselection). This may be used before identifying new cards

without resetting other already registered cards. Cards that already have an RCA do not respond to

identification commands (ACMD41, CMD2, CMD3) in this state.

NOTE

The card deselection is done if a certain card gets CMD7 with unmatched

RCA. That happens automatically if selection is done to another card and

the CMD lines are common. So, in the SD card system, it will be the

responsibility of the host either:

To work with the common CMD line (after initialization is done); in this case the card

deselection will be done automatically (as in MultiMediaCard system).

Or if the CMD lines are separate, to be aware of the necessity to deselect cards.

All data communication in the data transfer mode is point-to-point between the host and the selected SD

card (using addressed commands). All addressed commands are acknowledged with a response on the

CMD line. The relationship between the various data transfer modes is summarized in Figure 5, and in the

following paragraphs:

MPC5121e SDHC Controller, Rev. 1

Freescale Semiconductor

11

Description of Card

All data read commands may be aborted any time by the stop command (CMD12). The data

transfer will terminate and the card will return to the transfer state. The read commands are: block

read (CMD17), multiple block read (CMD18), send write protect (CMD30), send SCR (ACMD51)

and general command in read mode (CMD56).

All data write commands can be aborted any time by the stop command (CMD12). The write

commands must be stopped prior to deselecting the card by CMD7. The write commands are: block

write (CMD24 and CMD25), write CID (CMD26), write CSD (CMD27), lock/unlock command

(CMD42), and general command in write mode (CMD56).

As soon as the data transfer is completed, the card will exit the data write state and move either to

the programming state (transfer is successful) or transfer state (transfer failed).

If a block write operation is stopped and the block length and CRC of the last block are valid, the

data will be programmed.

The card may provide buffering for block write. This means that the next block can be sent to the

card while the previous block is being programmed. If all write buffers are full, and as long as the

card is in programming state, the DAT0 line will be kept low (BUSY).

There is no buffering option for write CSD, write CID, write protection, or erase. This means that

while the card is busy servicing any one of these commands, no other data transfer commands will

be accepted. The DAT0 line will be kept low as long as the card is busy and in the programming

state. Note that if the CMD and DAT0 lines of the cards are kept separated and the host keeps the

busy DAT0 line disconnected from the other DAT0 lines (of the other cards), the host may access

the other cards while the card is busy. Parameter set commands are not allowed while the card is

programming. Parameter set commands are: set block length (CMD16), erase block start

(CMD32), and erase block end (CMD33).

Read commands are not allowed while the card is programming.

Moving another card from standby to transfer state (using CMD7) will not terminate erase and

programming operations. The card will switch to the disconnect state and will release the DAT line.

A card can be reselected while in the disconnect state using CMD7. In this case the card will move

to the programming state and reactivate the busy indication.

Resetting a card (using CMD0 or CMD15) will terminate any pending or active programming

operation. This may destroy the data contents on the card. It is the hosts responsibility to prevent

this.

MPC5121e SDHC Controller, Rev. 1

12

Freescale Semiconductor

SDA Host and Card Specifications

SDA Host and Card Specifications

4.1

Environmental

Table 3. Environmental Specification

Temperature

Operating

Non-operating

25 C to 85 C

40 C to 85 C

Humidity

Operating

Non-operating

25% to 95%, non-condensing

25% to 95%, non-condensing

Contact Pads

4k V, human body model

according to ANSI EOS/ESD-S5.1-1998

Non-Contact Pad Area

8k V (coupling plane discharge)

15k V (air discharge)

Human body model per IEC61000-4-2

ESD protection

4.2

Reliability and Durability

Table 4. Reliability and Durability Specification

4.3

Durability

10,000 mating cycles

Bending

10 N

Torque

0.15 N.m or 2.5 deg.

Drop Test

1.5 m free fall

UV Light Exposure

UV: 254 nm, 15Ws/cm2 according to ISO 7816-1

Visual Inspection/Shape and Form

No warpage; no mold skin; complete form; no cavities;

surface smoothness 0.1 mm/cm2 within contour; no

cracks; no pollution (oil, dust, etc.)

Minimum Moving Force of WP Switch

40 gf (ensures that the WP switch will not slide while it

is inserted in the connector)

WP Switch Cycles

Minimum 1,000 Cycles @ slide force 0.4 N to 5 N

Power Supply

Table 5. Power Supply Specification

Peak Voltage on All Lines

0.3

Supply voltage +0.3

Input Leakage Current

10

10

mA

All inputs

Output Leakage Current

10

10

mA

All outputs

Supply Voltage

2.0

3.6

CMD0, 15, 55, ACMD41 commands

Supply Voltage

2.7

3.6

Except CMD0, 15, 55, ACMD41 commands

250

ms

Power-Up Time

From 0 V to VDD min.

References

1. MPC5121ERM, MPC5121e Microcontroller Reference Manual

MPC5121e SDHC Controller, Rev. 1

Freescale Semiconductor

13

2. Secure Digital Association website www.sdcard.org

How to Reach Us:

Home Page:

www.freescale.com

Web Support:

http://www.freescale.com/support

USA/Europe or Locations Not Listed:

Freescale Semiconductor, Inc.

Technical Information Center, EL516

2100 East Elliot Road

Tempe, Arizona 85284

+1-800-521-6274 or +1-480-768-2130

www.freescale.com/support

Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH

Technical Information Center

Schatzbogen 7

81829 Muenchen, Germany

+44 1296 380 456 (English)

+46 8 52200080 (English)

+49 89 92103 559 (German)

+33 1 69 35 48 48 (French)

www.freescale.com/support

Japan:

Freescale Semiconductor Japan Ltd.

Headquarters

ARCO Tower 15F

1-8-1, Shimo-Meguro, Meguro-ku,

Tokyo 153-0064

Japan

0120 191014 or +81 3 5437 9125

support.japan@freescale.com

Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd.

Technical Information Center

2 Dai King Street

Tai Po Industrial Estate

Tai Po, N.T., Hong Kong

+800 2666 8080

support.asia@freescale.com

For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center

P.O. Box 5405

Denver, Colorado 80217

1-800-441-2447 or 303-675-2140

Fax: 303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

Document Number: AN3805

Rev. 1

08/2009

Information in this document is provided solely to enable system and software

implementers to use Freescale Semiconductor products. There are no express or

implied copyright licenses granted hereunder to design or fabricate any integrated

circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to

any products herein. Freescale Semiconductor makes no warranty, representation or

guarantee regarding the suitability of its products for any particular purpose, nor does

Freescale Semiconductor assume any liability arising out of the application or use of any

product or circuit, and specifically disclaims any and all liability, including without

limitation consequential or incidental damages. Typical parameters that may be

provided in Freescale Semiconductor data sheets and/or specifications can and do vary

in different applications and actual performance may vary over time. All operating

parameters, including Typicals, must be validated for each customer application by

customers technical experts. Freescale Semiconductor does not convey any license

under its patent rights nor the rights of others. Freescale Semiconductor products are

not designed, intended, or authorized for use as components in systems intended for

surgical implant into the body, or other applications intended to support or sustain life,

or for any other application in which the failure of the Freescale Semiconductor product

could create a situation where personal injury or death may occur. Should Buyer

purchase or use Freescale Semiconductor products for any such unintended or

unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and

its officers, employees, subsidiaries, affiliates, and distributors harmless against all

claims, costs, damages, and expenses, and reasonable attorney fees arising out of,

directly or indirectly, any claim of personal injury or death associated with such

unintended or unauthorized use, even if such claim alleges that Freescale

Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality

and electrical characteristics as their non-RoHS-compliant and/or non-Pb-free

counterparts. For further information, see http://www.freescale.com or contact your

Freescale sales representative.

For information on Freescales Environmental Products program, go to

http://www.freescale.com/epp.

Freescale and the Freescale logo are trademarks of Freescale Semiconductor, Inc.

All other product or service names are the property of their respective owners.

Freescale Semiconductor, Inc. 20082009. All rights reserved.

Você também pode gostar

- The Yellow House: A Memoir (2019 National Book Award Winner)No EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Nota: 4 de 5 estrelas4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNo EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceNota: 4 de 5 estrelas4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNo EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeNota: 4 de 5 estrelas4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingNo EverandThe Little Book of Hygge: Danish Secrets to Happy LivingNota: 3.5 de 5 estrelas3.5/5 (400)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNo EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaNota: 4.5 de 5 estrelas4.5/5 (266)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNo EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureNota: 4.5 de 5 estrelas4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItNo EverandNever Split the Difference: Negotiating As If Your Life Depended On ItNota: 4.5 de 5 estrelas4.5/5 (838)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNo EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryNota: 3.5 de 5 estrelas3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerNo EverandThe Emperor of All Maladies: A Biography of CancerNota: 4.5 de 5 estrelas4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyNo EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyNota: 3.5 de 5 estrelas3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNo EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersNota: 4.5 de 5 estrelas4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnNo EverandTeam of Rivals: The Political Genius of Abraham LincolnNota: 4.5 de 5 estrelas4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaNo EverandThe Unwinding: An Inner History of the New AmericaNota: 4 de 5 estrelas4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNo EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreNota: 4 de 5 estrelas4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)No EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Nota: 4.5 de 5 estrelas4.5/5 (121)

- Guidelines For The Management of Brain InjuryDocumento26 páginasGuidelines For The Management of Brain InjuryfathaAinda não há avaliações

- Thermoplastic Tubing: Catalogue 5210/UKDocumento15 páginasThermoplastic Tubing: Catalogue 5210/UKGeo BuzatuAinda não há avaliações

- Accuity: High Speed Automated 2D & 3D Optical Gauging Single Click Setup and InspectionDocumento4 páginasAccuity: High Speed Automated 2D & 3D Optical Gauging Single Click Setup and InspectionAPPLEAinda não há avaliações

- 1986 EMT Disruption of Microbial Cells For Intracellular ProductsDocumento11 páginas1986 EMT Disruption of Microbial Cells For Intracellular ProductsLezid CortesAinda não há avaliações

- Final TestDocumento10 páginasFinal TestbennyAinda não há avaliações

- HY-TB3DV-M 3axis Driver PDFDocumento10 páginasHY-TB3DV-M 3axis Driver PDFjoelgcrAinda não há avaliações

- Arts6,4, Week2, Module 2V4Documento24 páginasArts6,4, Week2, Module 2V4Loreen Pearl MarlaAinda não há avaliações

- Marketing Management 4th Edition Winer Test BankDocumento35 páginasMarketing Management 4th Edition Winer Test Bankapneaocheryzxs3ua100% (24)

- DNA Mutation and Its Effect To An Individual (w5)Documento6 páginasDNA Mutation and Its Effect To An Individual (w5)Cold CoockiesAinda não há avaliações

- Application of PCA-CNN (Principal Component Analysis - Convolutional Neural Networks) Method On Sentinel-2 Image Classification For Land Cover MappingDocumento5 páginasApplication of PCA-CNN (Principal Component Analysis - Convolutional Neural Networks) Method On Sentinel-2 Image Classification For Land Cover MappingIJAERS JOURNALAinda não há avaliações

- Material Requirement Planning (MRP)Documento55 páginasMaterial Requirement Planning (MRP)Lisa CarlsonAinda não há avaliações

- Vallarpadam Terminal ChallengesDocumento3 páginasVallarpadam Terminal Challengespriya rajeev100% (1)

- Sketchup-Rhino Cheat SheetDocumento1 páginaSketchup-Rhino Cheat Sheetxanext7Ainda não há avaliações

- 2 Contoh Narative TextDocumento9 páginas2 Contoh Narative TextRini RienzAinda não há avaliações

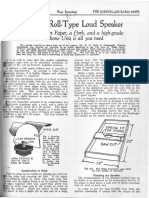

- Simple Roll-Type: A Loud SpeakerDocumento1 páginaSimple Roll-Type: A Loud SpeakerEudes SilvaAinda não há avaliações

- Trends in FoodDocumento3 páginasTrends in FoodAliAinda não há avaliações

- Cac de Luyen ThiDocumento18 páginasCac de Luyen ThiVinh Dao CongAinda não há avaliações

- Case StudyDocumento61 páginasCase StudyA GAinda não há avaliações

- Active Faults in MalaysiaDocumento52 páginasActive Faults in MalaysiaHazim HaAinda não há avaliações

- Rac Question PaperDocumento84 páginasRac Question PaperibrahimAinda não há avaliações

- Full Download Short Term Financial Management 3rd Edition Maness Test BankDocumento35 páginasFull Download Short Term Financial Management 3rd Edition Maness Test Bankcimanfavoriw100% (31)

- Chapter 04 Product and ServDocumento43 páginasChapter 04 Product and ServAlireza AlborziAinda não há avaliações

- Bolt Action Italian Painting GuideDocumento7 páginasBolt Action Italian Painting GuideTirmcdhol100% (2)

- LighthouseDocumento4 páginasLighthousejaneborn5345Ainda não há avaliações

- A Presentation On-: Dr. Nikhil Oza Intern BvdumcDocumento43 páginasA Presentation On-: Dr. Nikhil Oza Intern BvdumcMaheboob GanjalAinda não há avaliações

- Typical Section SC 10: Kerajaan MalaysiaDocumento1 páginaTypical Section SC 10: Kerajaan MalaysiaAisyah Atiqah KhalidAinda não há avaliações

- The Wilson Quarterly: The World's New Numbers by Martin WalkerDocumento13 páginasThe Wilson Quarterly: The World's New Numbers by Martin WalkerDavid WeekAinda não há avaliações

- Intumescent Paint For Steel NZ - Coating - Co.nzDocumento8 páginasIntumescent Paint For Steel NZ - Coating - Co.nzPeter ThomsonAinda não há avaliações

- Ge Fairchild Brochure PDFDocumento2 páginasGe Fairchild Brochure PDFDharmesh patelAinda não há avaliações

- St. John's Wort: Clinical OverviewDocumento14 páginasSt. John's Wort: Clinical OverviewTrismegisteAinda não há avaliações